Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                  |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 23                                                                        |

| Program Memory Size        | 32KB (16K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1.5K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f252t-e-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 DEVICE OVERVIEW

This document contains device specific information for the following devices:

| PIC18F242 | PIC18F442 |

|-----------|-----------|

| PIC18F252 | PIC18F452 |

These devices come in 28-pin and 40/44-pin packages. The 28-pin devices do not have a Parallel Slave Port (PSP) implemented and the number of Analog-to-Digital (A/D) converter input channels is reduced to 5. An overview of features is shown in Table 1-1.

### TABLE 1-1: DEVICE FEATURES

|                                    |                                                                                 | 1                                                                                 | 1                                                                               |                                                                                  |

|------------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Features                           | PIC18F242                                                                       | PIC18F252                                                                         | PIC18F442                                                                       | PIC18F452                                                                        |

| Operating Frequency                | DC - 40 MHz                                                                     | DC - 40 MHz                                                                       | DC - 40 MH                                                                      | z DC - 40 MHz                                                                    |

| Program Memory (Bytes)             | 16K                                                                             | 32K                                                                               | 16K                                                                             | 32K                                                                              |

| Program Memory (Instructions)      | 8192                                                                            | 16384                                                                             | 8192                                                                            | 16384                                                                            |

| Data Memory (Bytes)                | 768                                                                             | 1536                                                                              | 768                                                                             | 1536                                                                             |

| Data EEPROM Memory (Bytes)         | 256                                                                             | 256                                                                               | 256                                                                             | 256                                                                              |

| Interrupt Sources                  | 17                                                                              | 17                                                                                | 18                                                                              | 18                                                                               |

| I/O Ports                          | Ports A, B, C                                                                   | Ports A, B, C                                                                     | Ports A, B, C, D                                                                | , E Ports A, B, C, D, E                                                          |

| Timers                             | 4                                                                               | 4                                                                                 | 4                                                                               | 4                                                                                |

| Capture/Compare/PWM Module         | es 2                                                                            | 2                                                                                 | 2                                                                               | 2                                                                                |

| Serial Communications              | MSSP,<br>Addressable<br>USART                                                   | MSSP,<br>Addressable<br>USART                                                     | MSSP,<br>Addressable<br>USART                                                   | MSSP,<br>Addressable<br>USART                                                    |

| Parallel Communications            |                                                                                 |                                                                                   | PSP                                                                             | PSP                                                                              |

| 10-bit Analog-to-Digital Module    | 5 input chann                                                                   | els 5 input char                                                                  | nnels 8 input ch                                                                | annels 8 input chan                                                              |

| RESETS (and Delays)                | POR, BOR,<br>RESET Instruction<br>Stack Full,<br>Stack Underflow<br>(PWRT, OST) | POR, BOR,<br>, RESET Instruction<br>Stack Full,<br>Stack Underflow<br>(PWRT, OST) | POR, BOR,<br>RESET Instruction<br>Stack Full,<br>Stack Underflow<br>(PWRT, OST) | POR, BOR,<br>RESET Instruction,<br>Stack Full,<br>Stack Underflow<br>(PWRT, OST) |

| Programmable Low Voltage<br>Detect | Yes                                                                             | Yes                                                                               | Yes                                                                             | Yes                                                                              |

| Programmable Brown-out Rese        | Yes                                                                             | Yes                                                                               | Yes                                                                             | Yes                                                                              |

| Instruction Set                    | 75 Instruction                                                                  | s 75 Instructi                                                                    | ons 75 Instruc                                                                  | tions 75 Instructi                                                               |

| Packages                           | 28-pin DIP<br>28-pin SOIC                                                       | 28-pin DIP<br>28-pin SOIC                                                         | 40-pin DIP<br>44-pin PLCC<br>44-pin TQFP                                        | 40-pin DIP<br>44-pin PLCC<br>44-pin TQFP                                         |

The following two figures are device block diagrams sorted by pin count: 28-pin for Figure 1-1 and 40/44-pin for Figure 1-2. The 28-pin and 40/44-pin pinouts are listed in Table 1-2 and Table 1-3, respectively.

#### 4.3 Fast Register Stack

A fast interrupt return option is available for interrupts. The program counter (PC) specifies the address of the A Fast Register Stack is provided for the STATUS, WREG and BSR registers and are only one in depth.

The stack is not readable or writable and is loaded with the current value of the corresponding register when the processor vectors for an interrupt. The values in the registers are then loaded back into the working registers, if th€AST RETURN instruction is used to return from the interrupt.

A low or high priority interrupt source will push values into the stack registers. If both low and high priority interrupts are enabled, the stack registers cannot be The PC addresses bytes in the program memory. To used reliably for low priority interrupts. If a high priority prevent the PC from becoming misaligned with word interrupt occurs while servicing a low priority interrupt, instructions, the LSB of PCL is fixed to a value of 0. the stack register values stored by the low priority inter-The PC increments by 2 to address sequential rupt will be overwritten.

If high priority interrupts are not disabled during low pri- The CALL, RCALL, GOTO ority interrupts, users must save the key registers in software during a low priority interrupt.

If no interrupts are used, the fast register stack can be used to restore the STATUS, WREG and BSR registers at the end of a subroutine call. To use the fast register stack for a subroutine callFAST CALL instruction must be executed.

Example 4-1 shows a source code example that uses the fast register stack.

| EXAM | PLE 4-1:    | FAST REGISTER STACK<br>CODE EXAMPLE                     |

|------|-------------|---------------------------------------------------------|

| CALL | SUB1, FAST  | ;STATUS, WREG, BSR<br>;SAVED IN FAST REGISTER<br>;STACK |

| SUB1 |             |                                                         |

| F    | RETURN FAST | RESTORE VALUES SAVED                                    |

#### 44 PCL, PCLATH and PCLATU

instruction to fetch for execution. The PC is 21-bits wide. The low byte is called the PCL register. This register is readable and writable. The high byte is called the PCH register. This register contains the PC<15:8> bits and is not directly readable or writable. Updates to the PCH register may be performed through the PCLATH register. The upper byte is called PCU. This register contains the PC<20:16> bits and is not directly readable or writable. Updates to the PCU register may be performed through the PCLATU register.

instructions in the program memory.

and program branch instructions write to the program counter directly. For these instructions, the contents of PCLATH and PCLATU are not transferred to the program counter.

The contents of PCLATH and PCLATU will be transferred to the program counter by an operation that writes PCL. Similarly, the upper two bytes of the program counter will be transferred to PCLATH and PCLATU by an operation that reads PCL. This is useful for computed offsets to the PC (see Section 4.8.1).

#### 4.5 **Clocking Scheme/Instruction** Cycle

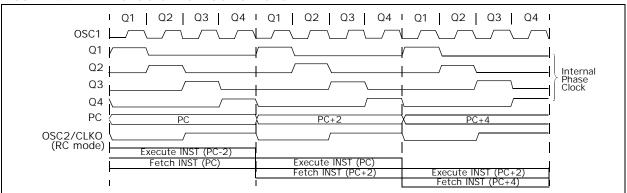

The clock input (from OSC1) is internally divided by four to generate four non-overlapping guadrature clocks, namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 4-4.

#### FIGURE 4-4: CLOCK/ INSTRUCTION CYCLE

IN FAST REGISTER STACK

# PIC18FXX2

### EXAMPLE 7-3: 16 x 16 UNSIGNED MULTIPLY ROUTINE

|   | MOVF     | ARG1L,  | W      |   |                  |

|---|----------|---------|--------|---|------------------|

|   | MULWF    | -       |        | ; | ARG1L * ARG2L -> |

|   |          |         |        | ' | PRODH: PRODL     |

|   | MOVFF    | PRODH,  | RES1   |   |                  |

|   | MOVFF    |         |        |   |                  |

|   | 110 111  | 110001, | ICED 0 | ' |                  |

| ' | MOVF     | ARG1H,  | W      |   |                  |

|   | MULWF    |         |        |   | ARG1H * ARG2H -> |

|   | пошл     | 1110211 |        |   | PRODH: PRODL     |

|   | MOVFF    | PRODH,  | PEGS   |   | TRODITIRODE      |

|   |          | PRODL,  |        |   |                  |

|   | 110 11 1 | IRODE,  | KH02   | ' |                  |

| ; | MOVF     | ARG1L,  | W      |   |                  |

|   | MULWF    |         |        |   | ARG1L * ARG2H -> |

|   | MUT      | ARGZII  |        | ' | PRODH: PRODL     |

|   | MOVF     | PRODL,  | TAT    | ; | FRODITERRODE     |

|   | ADDWF    |         |        |   | Add cross        |

|   |          | PRODH,  |        |   | products         |

|   |          | RES2,   |        | ; | produces         |

|   | CLRF     | -       | 1      | ; |                  |

|   |          | RES3,   | r.     |   |                  |

|   | ADDWIC   | кцор,   | Ľ      | ; |                  |

| ' | MOVF     | ARG1H,  | TAT    |   |                  |

|   | MULWF    |         | **     | ; | ARG1H * ARG2L -> |

|   | MOLWF    | AKGZL   |        | ' | PRODH:PRODL      |

|   | MOVF     | PRODL,  | TAT.   |   |                  |

|   | ADDWF    |         |        | ; | Add cross        |

|   | MOVF     |         |        |   | products         |

|   |          | RES2,   |        |   | products         |

|   | CLRF     |         | г      | ; |                  |

|   |          | RES3,   | r.     | ; |                  |

|   | ADDWFC   | керр,   | г      | ; |                  |

|   |          |         |        |   |                  |

Example 7-4 shows the sequence to do a 16 x 16 signed multiply. Equation 7-2 shows the algorithm used. The 32-bit result is stored in four registers, RES3:RES0. To account for the sign bits of the arguments, each argument pairs Most Significant bit (MSb) is tested and the appropriate subtractions are done.

### EQUATION 7-2: 16 x 16 SIGNED MULTIPLICATION ALGORITHM

| RES3:R | ESO                                                             |

|--------|-----------------------------------------------------------------|

| =      | ARG1H:ARG1L • ARG2H:ARG2L                                       |

| =      | $(ARG1H \bullet ARG2H \bullet 2^{16}) +$                        |

|        | $(ARG1H \bullet ARG2L \bullet 2^8) +$                           |

|        | $(ARG1L \bullet ARG2H \bullet 2^8) +$                           |

|        | $(ARG1L \bullet ARG2L) +$                                       |

|        | $(-1 \bullet ARG2H < 7 > \bullet ARG1H:ARG1L \bullet 2^{16}) +$ |

|        | $(-1 \bullet ARG1H < 7 > \bullet ARG2H:ARG2L \bullet 2^{16})$   |

### EXAMPLE 7-4: 16 x 16 SIGNED MULTIPLY ROUTINE

|     |        |         | -    |   |                  |

|-----|--------|---------|------|---|------------------|

|     | MOVF   | ARG1L,  | W    |   |                  |

|     | MULWF  | ARG2L   |      | ; | ARG1L * ARG2L -> |

|     |        |         |      |   | PRODH: PRODL     |

|     | MOVFF  | PRODH,  | RES1 | ; |                  |

|     | MOVFF  | PRODL,  |      |   |                  |

| ;   |        |         |      |   |                  |

|     | MOVF   | ARG1H,  | W    |   |                  |

|     | MULWF  | ARG2H   |      | ; | ARG1H * ARG2H -> |

|     |        |         |      | ; | PRODH: PRODL     |

|     | MOVFF  | PRODH,  | RES3 | ; |                  |

|     | MOVFF  | PRODL,  | RES2 | ; |                  |

| ;   |        |         |      |   |                  |

|     | MOVF   | ARG1L,  | W    |   |                  |

|     | MULWF  | ARG2H   |      | ; | ARG1L * ARG2H -> |

|     |        |         |      | ; | PRODH: PRODL     |

|     | MOVF   | PRODL,  | W    | ; |                  |

|     | ADDWF  |         | F    | ; | Add cross        |

|     | MOVF   | PRODH,  | W    | ; | products         |

|     | ADDWFC |         | F    | ; | -                |

|     | CLRF   | WREG    |      | ; |                  |

|     | ADDWFC | RES3,   | F    | ; |                  |

| ;   |        |         |      |   |                  |

|     | MOVF   | ARG1H,  | W    | ; |                  |

|     | MULWF  | ARG2L   |      | ; | ARG1H * ARG2L -> |

|     |        |         |      |   | PRODH: PRODL     |

|     | MOVF   | PRODL,  | W    | ; |                  |

|     | ADDWF  |         | F    |   | Add cross        |

|     | MOVF   | PRODH,  | W    |   | products         |

|     | ADDWFC |         | F    | ; | -                |

|     | CLRF   | WREG    |      | ; |                  |

|     | ADDWFC | RES3,   | F    | ; |                  |

| ;   |        |         |      |   |                  |

|     | BTFSS  | ARG2H,  | 7    | ; | ARG2H:ARG2L neg? |

|     | BRA    | SIGN AR | G1   | ; | no, check ARG1   |

|     | MOVF   | ARG1L,  | W    | ; |                  |

|     | SUBWF  | RES2    |      | ; |                  |

|     | MOVF   | ARG1H,  | W    | ; |                  |

|     | SUBWFB |         |      |   |                  |

| ;   |        |         |      |   |                  |

| SIG | N ARG1 |         |      |   |                  |

|     | BTFSS  | ARG1H,  | 7    | ; | ARG1H:ARG1L neg? |

|     | BRA    | CONT CC |      |   | no, done         |

|     | MOVF   | ARG2L,  | W    | ; |                  |

|     | SUBWF  | RES2    |      | ; |                  |

|     | MOVF   | ARG2H,  | W    | ; |                  |

|     | SUBWFB |         |      |   |                  |

| ;   |        |         |      |   |                  |

|     | T CODE |         |      |   |                  |

|     | -:     |         |      |   |                  |

|     |        |         |      |   |                  |

# REGISTER 15-3: SSPSTAT: MSSP STATUS REGISTER (I<sup>2</sup>C MODE)

|       | R/W-0                                                   | R/W-0                                              | R-0                                            | R-0          | R-0          | R-0                           | R-0             | R-0        |

|-------|---------------------------------------------------------|----------------------------------------------------|------------------------------------------------|--------------|--------------|-------------------------------|-----------------|------------|

|       | SMP                                                     | CKE                                                | D/A                                            | Р            | S            | R/W                           | UA              | BF         |

|       | bit 7                                                   |                                                    |                                                |              | •            |                               |                 | bit 0      |

| oit 7 | In Master of                                            | Rate Contr                                         | le:                                            | Standard Cn. | and mode (   | 100 kHz and                   | 1 MU-)          |            |

|       |                                                         |                                                    | nabled for H                                   |              |              |                               | I IVIFIZ)       |            |

| oit 6 | CKE: SMB                                                | sus Select bi                                      | t                                              | 0            | ,            |                               |                 |            |

|       |                                                         | e SMBus spe<br>e SMBus spe                         |                                                |              |              |                               |                 |            |

| oit 5 |                                                         | Address bit                                        |                                                |              |              |                               |                 |            |

|       |                                                         | es that the la                                     | ast byte recei<br>ast byte recei               |              |              |                               |                 |            |

| oit 4 |                                                         | es that a ST                                       | OP bit has be<br>letected last                 | een detecte  | d last       |                               |                 |            |

|       | Note:                                                   | This bit is cl                                     | eared on RE                                    | SET and w    | hen SSPEN    | is cleared.                   |                 |            |

| oit 3 |                                                         | es that a sta                                      | rt bit has bee<br>detected las                 |              | last         |                               |                 |            |

|       | Note:                                                   |                                                    | eared on RE                                    |              |              | is cleared.                   |                 |            |

| oit 2 | <b>R/W:</b> Read<br>In Slave m<br>1 = Read<br>0 = Write |                                                    | ormation (I <sup>2</sup> (                     | C mode only  | ()           |                               |                 |            |

|       | Note:                                                   |                                                    |                                                |              |              | ne last addres<br>bit, STOP b |                 |            |

|       |                                                         | <u>mode:</u><br>nit is in progr<br>nit is not in p |                                                |              |              |                               |                 |            |

|       | Note:                                                   | ORing this I in IDLE mod                           |                                                | RSEN, PE     | N, RCEN, o   | r ACKEN wil                   | l indicate if t | he MSSP is |

| oit 1 | 1 = Indicate                                            | es that the u                                      | 0-bit Slave r<br>ser needs to<br>need to be up | update the   | address in t | he SSPADD                     | register        |            |

| oit 0 | BF: Buffer                                              | Full Status b                                      | oit                                            |              |              |                               |                 |            |

|       |                                                         | e complete,                                        | SSPBUF is f<br>ete, SSPBUF                     |              |              |                               |                 |            |

|       |                                                         | ansmit in pro                                      |                                                |              |              | nd STOP bits<br>STOP bits),   |                 |            |

|       | Legend:                                                 |                                                    |                                                |              |              |                               |                 |            |

|       | R = Reada                                               | ble bit                                            | W = Writab                                     | le bit       | U = Unimp    | lemented bit                  | , read as '0'   |            |

|       | - n = Value                                             | at POR                                             | '1' = Bit is s                                 | et           | '0' = Bit is | cleared                       | x = Bit is ur   | hknown     |

| BAUD           | Fosc = 40 MHz |            | Fosc = 40 MHz SPBRG |         | G 33 MHz SPBRG |     | 25 MHz SPBRG |            | 20                 | SPBRG  |            |                    |

|----------------|---------------|------------|---------------------|---------|----------------|-----|--------------|------------|--------------------|--------|------------|--------------------|

| RATE<br>(Kbps) | KBAUD         | %<br>ERROR | value<br>(decimal)  | KBAUD   | %<br>ERROR     |     | KBAUD        | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) |

| 0.3            | NA            | -          | -                   | NA      | -              | -   | NA           | -          | -                  | NA     | -          | -                  |

| 1.2            | NA            | -          | -                   | NA      | -              | -   | NA           | -          | -                  | NA     | -          | -                  |

| 2.4            | NA            | -          | -                   | NA      | -              | -   | NA           | -          | -                  | NA     | -          | -                  |

| 9.6            | NA            | -          | -                   | 9.60    | -0.07          | 214 | 9.59         | -0.15      | 162                | 9.62   | +0.16      | 129                |

| 19.2           | 19.23         | +0.16      | 129                 | 19.28   | +0.39          | 106 | 19.30        | +0.47      | 80                 | 19.23  | +0.16      | 64                 |

| 76.8           | 75.76         | -1.36      | 32                  | 76.39   | -0.54          | 26  | 78.13        | +1.73      | 19                 | 78.13  | +1.73      | 15                 |

| 96             | 96.15         | +0.16      | 25                  | 98.21   | +2.31          | 20  | 97.66        | +1.73      | 15                 | 96.15  | +0.16      | 12                 |

| 300            | 312.50        | +4.17      | 7                   | 294.64  | -1.79          | 6   | 312.50       | +4.17      | 4                  | 312.50 | +4.17      | 3                  |

| 500            | 500           | 0          | 4                   | 515.63  | +3.13          | 3   | 520.83       | +4.17      | 2                  | 416.67 | -16.67     | 2                  |

| HIGH           | 2500          | -          | 0                   | 2062.50 | -              | 0   | 1562.50      | -          | 0                  | 1250   | -          | 0                  |

| LOW            | 9.77          | -          | 255                 | 8,06    | -              | 255 | 6.10         | -          | 255                | 4.88   | -          | 255                |

# TABLE 16-5: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

| BAUD           | Fosc = | Fosc = 16 MHz |                    | 10 MHz |            | SPBRG              | 7.1590 | 9 MHz      | SPBRG              | 5.068  | 8 MHz      | SPBRG              |

|----------------|--------|---------------|--------------------|--------|------------|--------------------|--------|------------|--------------------|--------|------------|--------------------|

| RATE<br>(Kbps) | KBAUD  | %<br>ERROR    | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) |

| 0.3            | NA     | -             | -                  | NA     | -          | -                  | NA     | -          | -                  | NA     | -          | -                  |

| 1.2            | NA     | -             | -                  | NA     | -          | -                  | NA     | -          | -                  | NA     | -          | -                  |

| 2.4            | NA     | -             | -                  | NA     | -          | -                  | 2.41   | +0.23      | 185                | 2.40   | 0          | 131                |

| 9.6            | 9.62   | +0.16         | 103                | 9.62   | +0.16      | 64                 | 9.52   | -0.83      | 46                 | 9.60   | 0          | 32                 |

| 19.2           | 19.23  | +0.16         | 51                 | 18.94  | -1.36      | 32                 | 19.45  | +1.32      | 22                 | 18.64  | -2.94      | 16                 |

| 76.8           | 76.92  | +0.16         | 12                 | 78.13  | +1.73      | 7                  | 74.57  | -2.90      | 5                  | 79.20  | +3.13      | 3                  |

| 96             | 100    | +4.17         | 9                  | 89.29  | -6.99      | 6                  | 89.49  | -6.78      | 4                  | 105.60 | +10.00     | 2                  |

| 300            | 333.33 | +11.11        | 2                  | 312.50 | +4.17      | 1                  | 447.44 | +49.15     | 0                  | 316.80 | +5.60      | 0                  |

| 500            | 500    | 0             | 1                  | 625    | +25.00     | 0                  | 447.44 | -10.51     | 0                  | NA     | -          | -                  |

| HIGH           | 1000   | -             | 0                  | 625    | -          | 0                  | 447.44 | -          | 0                  | 316.80 | -          | 0                  |

| LOW            | 3.91   | -             | 255                | 2.44   | -          | 255                | 1.75   | -          | 255                | 1.24   | -          | 255                |

| BAUD           | Fosc = | 4 MHz      | SPBRG              | <sup>3.579545 MHz</sup> S |            | 3.579545 MHz SPBRG |       | 1 N        | 1Hz                | SPBRG | 32.76      | 8 kHz              | SPBRG |

|----------------|--------|------------|--------------------|---------------------------|------------|--------------------|-------|------------|--------------------|-------|------------|--------------------|-------|

| RATE<br>(Kbps) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD                     | %<br>ERROR | value<br>(decimal) | KBAUD | %<br>ERROR | value<br>(decimal) | KBAUD | %<br>ERROR | value<br>(decimal) |       |

| 0.3            | NA     | -          | -                  | NA                        | -          | -                  | 0.30  | +0.16      | 207                | 0.29  | -2.48      | 6                  |       |

| 1.2            | 1.20   | +0.16      | 207                | 1.20                      | +0.23      | 185                | 1.20  | +0.16      | 51                 | 1.02  | -14.67     | 1                  |       |

| 2.4            | 2.40   | +0.16      | 103                | 2.41                      | +0.23      | 92                 | 2.40  | +0.16      | 25                 | 2.05  | -14.67     | 0                  |       |

| 9.6            | 9.62   | +0.16      | 25                 | 9.73                      | +1.32      | 22                 | 8.93  | -6.99      | 6                  | NA    | -          | -                  |       |

| 19.2           | 19.23  | +0.16      | 12                 | 18.64                     | -2.90      | 11                 | 20.83 | +8.51      | 2                  | NA    | -          | -                  |       |

| 76.8           | NA     | -          | -                  | 74.57                     | -2.90      | 2                  | 62.50 | -18.62     | 0                  | NA    | -          | -                  |       |

| 96             | NA     | -          | -                  | 111.86                    | +16.52     | 1                  | NA    | -          | -                  | NA    | -          | -                  |       |

| 300            | NA     | -          | -                  | 223.72                    | -25.43     | 0                  | NA    | -          | -                  | NA    | -          | -                  |       |

| 500            | NA     | -          | -                  | NA                        | -          | -                  | NA    | -          | -                  | NA    | -          | -                  |       |

| HIGH           | 250    | -          | 0                  | 55.93                     | -          | 0                  | 62.50 | -          | 0                  | 2.05  | -          | 0                  |       |

| LOW            | 0.98   | -          | 255                | 0.22                      | -          | 255                | 0.24  | -          | 255                | 0.008 | -          | 255                |       |