Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                               |

| Number of I/O              | 34                                                                       |

| Program Memory Size        | 16KB (8K x 16)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 768 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-VQFN Exposed Pad                                                      |

| Supplier Device Package    | 44-QFN (8x8)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f442-e-ml |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### PIC18F4X2 PINOUT I/O DESCRIPTIONS (CONTINUED) **TABLE 1-3:**

| Din Neme                              | Pi    | n Numb | ber            | Pin Buffer |                     | Description                                                                                                                                                                         |  |  |  |

|---------------------------------------|-------|--------|----------------|------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name                              | DIP   | PLCC   | TQFP           | Туре       | Туре                | Description                                                                                                                                                                         |  |  |  |

|                                       |       |        |                |            |                     | PORTD is a bi-directional I/O port, or a Parallel Slave<br>Port (PSP) for interfacing to a microprocessor port.<br>These pins have TTL input buffers when PSP module<br>is enabled. |  |  |  |

| RD0/PSP0                              | 19    | 21     | 38             | I/O        | ST<br>TTL           | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                           |  |  |  |

| RD1/PSP1                              | 20    | 22     | 39             | I/O        | ST<br>TTL           | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                           |  |  |  |

| RD2/PSP2                              | 21    | 23     | 40             | I/O        | ST<br>TTL           | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                           |  |  |  |

| RD3/PSP3                              | 22    | 24     | 41             | I/O        | ST<br>TTL           | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                           |  |  |  |

| RD4/PSP4                              | 27    | 30     | 2              | I/O        | ST<br>TTL           | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                           |  |  |  |

| RD5/PSP5                              | 28    | 31     | 3              | I/O        | ST<br>TTL           | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                           |  |  |  |

| RD6/PSP6                              | 29    | 32     | 4              | I/O        | ST<br>TTL           | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                           |  |  |  |

| RD7/PSP7                              | 30    | 33     | 5              | I/O        | ST<br>TTL           | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                           |  |  |  |

| RE0/RD/AN5<br>RE0<br>RD               | 8     | 9      | 25             | I/O        | ST<br>TTL           | PORTE is a bi-directional I/O port.<br>Digital I/O.<br>Read control for parallel slave port<br>(see also WR and CS pins).                                                           |  |  |  |

| AN5<br>RE1/WR/AN6<br><u>RE1</u><br>WR | 9     | 10     | 26             | I/O        | Analog<br>ST<br>TTL | Analog input 5.<br>Digital I/O.<br>Write control for parallel slave port                                                                                                            |  |  |  |

| AN6<br>RE2/ <del>CS</del> /AN7<br>RE2 | 10    | 11     | 27             | I/O        | Analog<br>ST        | (see CS and RD pins).<br>Analog input 6.<br>Digital I/O.                                                                                                                            |  |  |  |

| CS<br>AN7                             |       |        |                |            | TTL                 | Chip Select control for parallel slave port (see related $\overline{RD}$ and $\overline{WR}$ ).                                                                                     |  |  |  |

| Vss                                   | 12 21 | 13, 34 | 6 29           | Р          | Analog              | Analog input 7.<br>Ground reference for logic and I/O pins.                                                                                                                         |  |  |  |

| VDD                                   |       |        | 0, 29<br>7, 28 | г<br>Р     |                     | Positive supply for logic and I/O pins.                                                                                                                                             |  |  |  |

| Legend: TTL = TTL                     |       |        |                | l.         | L                   | CMOS = CMOS compatible input or output                                                                                                                                              |  |  |  |

ST = Schmitt Trigger input with CMOS levels

O = Output OD = Open Drain (no P diode to VDD) I = Input

P = Power

## TABLE 2-2:CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR

|             | Ranges Tested: |                 |          |  |  |  |  |  |  |  |  |

|-------------|----------------|-----------------|----------|--|--|--|--|--|--|--|--|

| Mode        | Freq           | C1              | C2       |  |  |  |  |  |  |  |  |

| LP          | 32.0 kHz       | 33 pF           | 33 pF    |  |  |  |  |  |  |  |  |

|             | 200 kHz        | 15 pF           | 15 pF    |  |  |  |  |  |  |  |  |

| XT          | 200 kHz        | 22-68 pF        | 22-68 pF |  |  |  |  |  |  |  |  |

|             | 1.0 MHz        | 1.0 MHz 15 pF   |          |  |  |  |  |  |  |  |  |

|             | 4.0 MHz        | 15 pF           | 15 pF    |  |  |  |  |  |  |  |  |

| HS          | 4.0 MHz        | 15 pF           | 15 pF    |  |  |  |  |  |  |  |  |

|             | 8.0 MHz        | 15-33 pF        | 15-33 pF |  |  |  |  |  |  |  |  |

|             | 20.0 MHz       | 15-33 pF        | 15-33 pF |  |  |  |  |  |  |  |  |

|             | 25.0 MHz       | 15-33 pF        | 15-33 pF |  |  |  |  |  |  |  |  |

| These value | es are for de  | sign guidance c | only.    |  |  |  |  |  |  |  |  |

These values are for design guidance only See notes following this table.

| Crystals Used |                        |          |  |  |  |  |  |  |  |

|---------------|------------------------|----------|--|--|--|--|--|--|--|

| 32.0 kHz      | Epson C-001R32.768K-A  | ± 20 PPM |  |  |  |  |  |  |  |

| 200 kHz       | STD XTL 200.000KHz     | ± 20 PPM |  |  |  |  |  |  |  |

| 1.0 MHz       | ECS ECS-10-13-1        | ± 50 PPM |  |  |  |  |  |  |  |

| 4.0 MHz       | ECS ECS-40-20-1        | ± 50 PPM |  |  |  |  |  |  |  |

| 8.0 MHz       | Epson CA-301 8.000M-C  | ± 30 PPM |  |  |  |  |  |  |  |

| 20.0 MHz      | Epson CA-301 20.000M-C | ± 30 PPM |  |  |  |  |  |  |  |

|               |                        |          |  |  |  |  |  |  |  |

- Note 1: Higher capacitance increases the stability of the oscillator, but also increases the start-up time.

- 2: Rs may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

- 3: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components., or verify oscillator performance.

An external clock source may also be connected to the OSC1 pin in the HS, XT and LP modes, as shown in Figure 2-2.

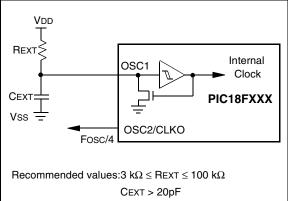

# FIGURE 2-2: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

Open -

OSC2

### 2.3 RC Oscillator

For timing-insensitive applications, the "RC" and "RCIO" device options offer additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 2-3 shows how the R/C combination is connected.

In the RC Oscillator mode, the oscillator frequency divided by 4 is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic.

| Note: | If the oscillator frequency divided by 4 sig- |

|-------|-----------------------------------------------|

|       | nal is not required in the application, it is |

|       | recommended to use RCIO mode to save          |

|       | current.                                      |

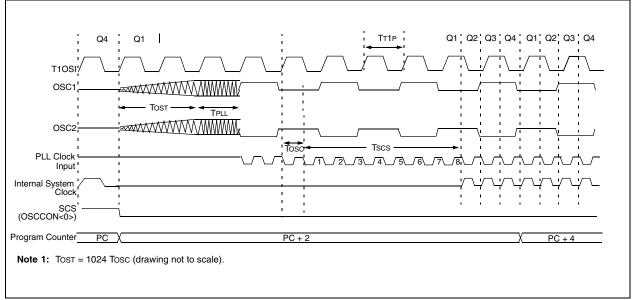

The RCIO Oscillator mode functions like the RC mode, except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6). If the main oscillator is configured for HS-PLL mode, an oscillator start-up time (TOST) plus an additional PLL time-out (TPLL) will occur. The PLL time-out is typically 2 ms and allows the PLL to lock to the main oscillator frequency. A timing diagram indicating the transition from the Timer1 oscillator to the main oscillator for HS-PLL mode is shown in Figure 2-10.

FIGURE 2-10: TIMING FOR TRANSITION BETWEEN TIMER1 AND OSC1 (HS WITH PLL)

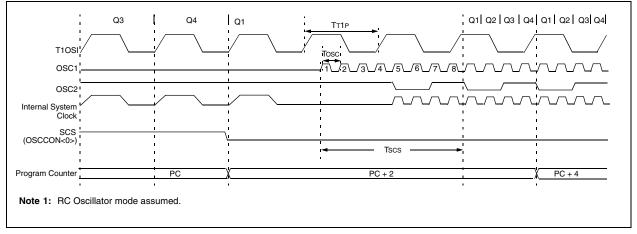

If the main oscillator is configured in the RC, RCIO, EC or ECIO modes, there is no oscillator start-up time-out. Operation will resume after eight cycles of the main oscillator have been counted. A timing diagram, indicating the transition from the Timer1 oscillator to the main oscillator for RC, RCIO, EC and ECIO modes, is shown in Figure 2-11.

### FIGURE 2-11: TIMING FOR TRANSITION BETWEEN TIMER1 AND OSC1 (RC, EC)

### 4.0 MEMORY ORGANIZATION

There are three memory blocks in Enhanced MCU devices. These memory blocks are:

- Program Memory

- Data RAM

- Data EEPROM

Data and program memory use separate busses, which allows for concurrent access of these blocks.

Additional detailed information for FLASH program memory and Data EEPROM is provided in Section 5.0 and Section 6.0, respectively.

### 4.1 Program Memory Organization

A 21-bit program counter is capable of addressing the 2-Mbyte program memory space. Accessing a location between the physically implemented memory and the 2-Mbyte address will cause a read of all '0's (a NOP instruction).

The PIC18F252 and PIC18F452 each have 32 Kbytes of FLASH memory, while the PIC18F242 and PIC18F442 have 16 Kbytes of FLASH. This means that PIC18FX52 devices can store up to 16K of single word instructions, and PIC18FX42 devices can store up to 8K of single word instructions.

The RESET vector address is at 0000h and the interrupt vector addresses are at 0008h and 0018h.

Figure 4-1 shows the Program Memory Map for PIC18F242/442 devices and Figure 4-2 shows the Program Memory Map for PIC18F252/452 devices.

### TABLE 4-2: REGISTER FILE SUMMARY

| File Name | Bit 7         | Bit 6                              | Bit 5                | Bit 4         | Bit 3         | Bit 2         | Bit 1           | Bit 0           | Value on<br>POR, BOR | Details<br>on page: |  |  |

|-----------|---------------|------------------------------------|----------------------|---------------|---------------|---------------|-----------------|-----------------|----------------------|---------------------|--|--|

| TOSU      | —             | —                                  | —                    | Top-of-Stack  | upper Byte (  | TOS<20:16>)   | )               |                 | 0 0000               | 37                  |  |  |

| TOSH      | Top-of-Stacl  | k High Byte (1                     | OS<15:8>)            | •             |               |               |                 |                 | 0000 0000            | 37                  |  |  |

| TOSL      | Top-of-Stacl  | k Low Byte (T                      | OS<7:0>)             |               |               |               |                 |                 | 0000 0000            | 37                  |  |  |

| STKPTR    | STKFUL        | STKUNF                             | _                    | Return Stack  | <pre></pre>   |               |                 |                 | 00-0 0000            | 38                  |  |  |

| PCLATU    | _             | — — Holding Register for PC<20:16> |                      |               |               |               |                 |                 |                      |                     |  |  |

| PCLATH    | Holding Reg   | Iolding Register for PC<15:8>      |                      |               |               |               |                 |                 |                      |                     |  |  |

| PCL       | PC Low Byt    | C Low Byte (PC<7:0>)               |                      |               |               |               |                 |                 |                      |                     |  |  |

| TBLPTRU   | _             | _                                  | bit21 <sup>(2)</sup> | Program Me    | mory Table P  | ointer Upper  | Byte (TBLPT     | R<20:16>)       | 00 0000              | 58                  |  |  |

| TBLPTRH   | Program Me    | emory Table F                      | ointer High E        | Byte (TBLPTF  | R<15:8>)      |               |                 |                 | 0000 0000            | 58                  |  |  |

| TBLPTRL   | Program Me    | emory Table F                      | ointer Low B         | yte (TBLPTR   | <7:0>)        |               |                 |                 | 0000 0000            | 58                  |  |  |

| TABLAT    | Program Me    | emory Table L                      | atch                 |               |               |               |                 |                 | 0000 0000            | 58                  |  |  |

| PRODH     | Product Reg   | gister High By                     | te                   |               |               |               |                 |                 | xxxx xxxx            | 71                  |  |  |

| PRODL     | Product Reg   | gister Low Byt                     | te                   |               |               |               |                 |                 | xxxx xxxx            | 71                  |  |  |

| INTCON    | GIE/GIEH      | PEIE/GIEL                          | TMR0IE               | INT0IE        | RBIE          | TMR0IF        | <b>INT0IF</b>   | RBIF            | 0000 000x            | 75                  |  |  |

| INTCON2   | RBPU          | INTEDG0                            | INTEDG1              | INTEDG2       | —             | TMR0IP        | _               | RBIP            | 1111 -1-1            | 76                  |  |  |

| INTCON3   | INT2IP        | INT1IP                             |                      | INT2IE        | INT1IE        |               | INT2IF          | INT1IF          | 11-0 0-00            | 77                  |  |  |

| INDF0     | Uses conter   | ts of FSR0 to                      | address data         | memory - val  | ue of FSR0 no | t changed (no | ot a physical r | egister)        | n/a                  | 50                  |  |  |

| POSTINC0  | Uses conten   | ts of FSR0 to                      | address data         | memory - val  | ue of FSR0 po | st-incremente | ed (not a phys  | sical register) | n/a                  | 50                  |  |  |

| POSTDEC0  | Uses conten   | ts of FSR0 to                      | address data         | memory - valı | ue of FSR0 po | st-decremente | ed (not a phys  | sical register) | n/a                  | 50                  |  |  |

| PREINC0   | Uses conten   | ts of FSR0 to                      | address data         | memory - val  | ue of FSR0 pr | e-incremented | d (not a physi  | cal register)   | n/a                  | 50                  |  |  |

| PLUSW0    |               | nts of FSR0 to<br>lue in WREG.     |                      | a memory - v  | alue of FSR0  | (not a physic | cal register).  |                 | n/a                  | 50                  |  |  |

| FSR0H     | —             | _                                  |                      | —             | Indirect Data | Memory Add    | dress Pointer   | 0 High Byte     | 0000                 | 50                  |  |  |

| FSR0L     | Indirect Date | a Memory Ad                        | dress Pointer        | r 0 Low Byte  |               |               |                 |                 | xxxx xxxx            | 50                  |  |  |

| WREG      | Working Re    | gister                             |                      |               |               |               |                 |                 | xxxx xxxx            | n/a                 |  |  |

| INDF1     | Uses conter   | nts of FSR1 to                     | address dat          | a memory - v  | alue of FSR1  | not changed   | (not a physi    | cal register)   | n/a                  | 50                  |  |  |

| POSTINC1  | Uses conten   | ts of FSR1 to                      | address data         | memory - val  | ue of FSR1 po | st-incremente | ed (not a phys  | sical register) | n/a                  | 50                  |  |  |

| POSTDEC1  | Uses conten   | ts of FSR1 to                      | address data         | memory - valu | ue of FSR1 po | st-decremente | ed (not a phys  | sical register) | n/a                  | 50                  |  |  |

| PREINC1   | Uses conten   | ts of FSR1 to                      | address data         | memory - val  | ue of FSR1 pr | e-incremente  | d (not a physi  | cal register)   | n/a                  | 50                  |  |  |

| PLUSW1    |               | nts of FSR1 to<br>lue in WREG.     |                      | a memory - v  | alue of FSR1  | (not a physic | cal register).  |                 | n/a                  | 50                  |  |  |

| FSR1H     | —             | _                                  |                      | _             | Indirect Data | Memory Add    | lress Pointer   | 1 High Byte     | 0000                 | 50                  |  |  |

| FSR1L     | Indirect Data | a Memory Ad                        | dress Pointer        | r 1 Low Byte  |               |               |                 |                 | xxxx xxxx            | 50                  |  |  |

| BSR       | —             | _                                  |                      | —             | Bank Select   | Register      |                 |                 | 0000                 | 49                  |  |  |

| INDF2     | Uses conter   | nts of FSR2 to                     | address dat          | a memory - v  | alue of FSR2  | not changed   | l (not a physi  | cal register)   | n/a                  | 50                  |  |  |

| POSTINC2  | Uses conten   | ts of FSR2 to                      | address data         | memory - val  | ue of FSR2 po | st-incremente | ed (not a phys  | sical register) | n/a                  | 50                  |  |  |

| POSTDEC2  | Uses conten   | ts of FSR2 to                      | address data         | memory - valı | ue of FSR2 po | st-decremente | ed (not a phys  | sical register) | n/a                  | 50                  |  |  |

| PREINC2   | Uses conten   | ts of FSR2 to                      | address data         | memory - val  | ue of FSR2 pr | e-incremente  | d (not a physi  | cal register)   | n/a                  | 50                  |  |  |

| PLUSW2    |               | nts of FSR2 to<br>lue in WREG.     |                      | a memory - v  | alue of FSR2  | (not a physic | cal register).  |                 | n/a                  | 50                  |  |  |

| FSR2H     |               | _                                  | _                    | —             | Indirect Data | Memory Add    | dress Pointer   | 2 High Byte     | 0000                 | 50                  |  |  |

| FSR2L     | Indirect Dat  | a Memory Ad                        | dress Pointer        | r 2 Low Byte  |               |               |                 |                 | xxxx xxxx            | 50                  |  |  |

| STATUS    | —             | —                                  | _                    | Ν             | OV            | Z             | DC              | С               | x xxxx               | 52                  |  |  |

| TMR0H     | Timer0 Reg    | ister High Byt                     | e                    |               |               |               |                 |                 | 0000 0000            | 105                 |  |  |

|           |               |                                    | · _                  |               |               |               |                 |                 |                      | 105                 |  |  |

| TMR0L     | Timer0 Reg    | Ister Low Byte                     |                      |               |               |               |                 |                 | XXXX XXXX            | 105                 |  |  |

Note 1: RA6 and associated bits are configured as port pins in RCIO and ECIO Oscillator mode only and read '0' in all other Oscillator modes.

Bit 21 of the TBLPTRU allows access to the device configuration bits.

3: These registers and bits are reserved on the PIC18F2X2 devices; always maintain these clear.

NOTES:

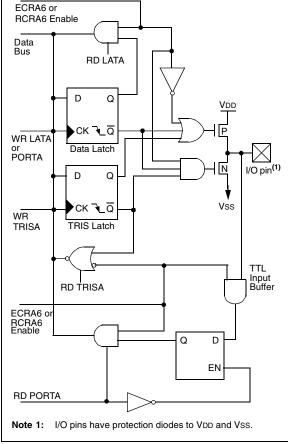

## FIGURE 9-3: BLOCK DIAGRAM OF RA6 PIN

TABLE 9-11: REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Name   | Bit 7        | Bit 6         | Bit 5         | Bit 4          | Bit 3 | Bit 2     | Bit 1         | Bit 0  | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |

|--------|--------------|---------------|---------------|----------------|-------|-----------|---------------|--------|----------------------|---------------------------------|

| PORTD  | Port Data    | Latch whe     | en written; F | Port pins wher | read  |           |               |        | xxxx xxxx            | uuuu uuuu                       |

| LATD   | LATD Data    | a Output b    | its           |                |       |           |               |        | xxxx xxxx            | uuuu uuuu                       |

| TRISD  | PORTD D      | ata Directi   | on bits       |                |       |           |               |        | 1111 1111            | 1111 1111                       |

| PORTE  | _            | _             | _             | —              | _     | RE2       | RE1           | RE0    | 000                  | 000                             |

| LATE   | _            | _             | _             | _              | _     | LATE Data | a Output bits | 5      | xxx                  | uuu                             |

| TRISE  | IBF          | OBF           | IBOV          | PSPMODE        | —     | PORTE D   | ata Direction | n bits | 0000 -111            | 0000 -111                       |

| INTCON | GIE/<br>GIEH | PEIE/<br>GIEL | TMR0IF        | INTOIE         | RBIE  | TMR0IF    | INTOIF        | RBIF   | 0000 000x            | 0000 000u                       |

| PIR1   | PSPIF        | ADIF          | RCIF          | TXIF           | SSPIF | CCP1IF    | TMR2IF        | TMR1IF | 0000 0000            | 0000 0000                       |

| PIE1   | PSPIE        | ADIE          | RCIE          | TXIE           | SSPIE | CCP1IE    | TMR2IE        | TMR1IE | 0000 0000            | 0000 0000                       |

| IPR1   | PSPIP        | ADIP          | RCIP          | TXIP           | SSPIP | CCP1IP    | TMR2IP        | TMR1IP | 0000 0000            | 0000 0000                       |

| ADCON1 | ADFM         | ADCS2         | _             | _              | PCFG3 | PCFG2     | PCFG1         | PCFG0  | 00 0000              | 00 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Parallel Slave Port.

### 13.2 Timer1 Oscillator

The Timer1 oscillator may be used as the clock source for Timer3. The Timer1 oscillator is enabled by setting the T1OSCEN (T1CON<3>) bit. The oscillator is a low power oscillator rated up to 200 KHz. See Section 11.0 for further details.

### 13.3 Timer3 Interrupt

The TMR3 Register pair (TMR3H:TMR3L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR3 Interrupt, if enabled, is generated on overflow, which is latched in interrupt flag bit, TMR3IF (PIR2<1>). This interrupt can be enabled/disabled by setting/clearing TMR3 interrupt enable bit, TMR3IE (PIE2<1>).

### 13.4 Resetting Timer3 Using a CCP Trigger Output

If the CCP module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer3.

| Note: | The special event triggers from the CCP |

|-------|-----------------------------------------|

|       | module will not set interrupt flag bit, |

|       | TMR3IF (PIR1<0>).                       |

Timer3 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer3 is running in Asynchronous Counter mode, this RESET operation may not work. In the event that a write to Timer3 coincides with a special event trigger from CCP1, the write will take precedence. In this mode of operation, the CCPR1H:CCPR1L registers pair effectively becomes the period register for Timer3.

| Name   | Bit 7                                                                      | Bit 6          | Bit 5        | Bit 4         | Bit 3         | Bit 2         | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |

|--------|----------------------------------------------------------------------------|----------------|--------------|---------------|---------------|---------------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE/<br>GIEH                                                               | PEIE/<br>GIEL  | TMR0IE       | INTOIE        | RBIE          | TMR0IF        | INTOIF | RBIF   | 0000 000x            | 0000 000u                       |

| PIR2   | —                                                                          | _              | _            | EEIF          | BCLIF         | LVDIF         | TMR3IF | CCP2IF | 0 0000               | 0 0000                          |

| PIE2   | —                                                                          | _              | _            | EEIE          | BCLIE         | LVDIE         | TMR3IE | CCP2IE | 0 0000               | 0 0000                          |

| IPR2   | _                                                                          | -              | -            | EEIP          | BCLIP         | LVDIP         | TMR3IP | CCP2IP | 1 1111               | 1 1111                          |

| TMR3L  | Holding F                                                                  | legister for t | he Least Sig | gnificant Byt | e of the 16-b | it TMR3 Re    | gister |        | xxxx xxxx            | uuuu uuuu                       |

| TMR3H  | Holding Register for the Most Significant Byte of the 16-bit TMR3 Register |                |              |               |               |               |        |        | xxxx xxxx            | uuuu uuuu                       |

| T1CON  | RD16                                                                       |                | T1CKPS1      | T1CKPS0       | T1OSCEN       | T1SYNC        | TMR1CS | TMR10N | 0-00 0000            | u-uu uuuu                       |

| T3CON  | RD16                                                                       | T3CCP2         | T3CKPS1      | T3CKPS0       | T3CCP1        | <b>T3SYNC</b> | TMR3CS | TMR3ON | 0000 0000            | uuuu uuuu                       |

### TABLE 13-1: REGISTERS ASSOCIATED WITH TIMER3 AS A TIMER/COUNTER

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

### 15.3.1 REGISTERS

The MSSP module has four registers for SPI mode operation. These are:

- MSSP Control Register1 (SSPCON1)

- MSSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

SSPCON1 and SSPSTAT are the control and status registers in SPI mode operation. The SSPCON1 register is readable and writable. The lower 6 bits of the SSPSTAT are read only. The upper two bits of the SSPSTAT are read/write. SSPSR is the shift register used for shifting data in or out. SSPBUF is the buffer register to which data bytes are written to or read from.

In receive operations, SSPSR and SSPBUF together create a double buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not double buffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

### REGISTER 15-1: SSPSTAT: MSSP STATUS REGISTER (SPI MODE)

|       | R/W-0                                                                        | R/W-0                      | R-0            | R-0          | R-0          | R-0         | R-0           | R-0        |  |  |  |  |

|-------|------------------------------------------------------------------------------|----------------------------|----------------|--------------|--------------|-------------|---------------|------------|--|--|--|--|

|       | SMP                                                                          | CKE                        | D/A            | Р            | S            | R/W         | UA            | BF         |  |  |  |  |

|       | bit 7                                                                        |                            |                |              |              |             |               | bit 0      |  |  |  |  |

|       |                                                                              |                            |                |              |              |             |               |            |  |  |  |  |

| bit 7 | SMP: Sample bit                                                              |                            |                |              |              |             |               |            |  |  |  |  |

|       | <u>SPI Master mode:</u><br>1 = Input data sampled at end of data output time |                            |                |              |              |             |               |            |  |  |  |  |

|       | •                                                                            | ata sampled<br>ata sampled |                | •            |              |             |               |            |  |  |  |  |

|       | SPI Slave r                                                                  | •                          | at midule 0    | ι ααία σάιρα |              |             |               |            |  |  |  |  |

|       |                                                                              | be cleared v               | when SPI is    | used in Slav | e mode       |             |               |            |  |  |  |  |

| bit 6 | CKE: SPI (                                                                   | Clock Edge S               | Select         |              |              |             |               |            |  |  |  |  |

|       | When CKP                                                                     |                            |                |              |              |             |               |            |  |  |  |  |

|       |                                                                              | ansmitted or               |                |              |              |             |               |            |  |  |  |  |

|       |                                                                              | ansmitted or               | i falling edge | e of SCK     |              |             |               |            |  |  |  |  |

|       | <u>When CKP</u><br>1 = Data tra                                              | <u> </u>                   | , falling edg  | e of SCK     |              |             |               |            |  |  |  |  |

|       |                                                                              | ansmitted or               |                |              |              |             |               |            |  |  |  |  |

| bit 5 | D/A: Data/                                                                   | Address bit                |                |              |              |             |               |            |  |  |  |  |

|       | Used in I <sup>2</sup> C                                                     | mode only                  |                |              |              |             |               |            |  |  |  |  |

| bit 4 | P: STOP b                                                                    |                            |                |              |              |             |               |            |  |  |  |  |

|       | Used in I <sup>2</sup> (<br>cleared.                                         | C mode only                | /. This bit is | cleared wh   | nen the MS   | SP module   | is disabled   | , SSPEN is |  |  |  |  |

| bit 3 | S: START I                                                                   | bit                        |                |              |              |             |               |            |  |  |  |  |

|       | Used in I <sup>2</sup> C                                                     | c mode only                |                |              |              |             |               |            |  |  |  |  |

| bit 2 |                                                                              | /Write bit inf             | ormation       |              |              |             |               |            |  |  |  |  |

|       |                                                                              | mode only                  |                |              |              |             |               |            |  |  |  |  |

| bit 1 | UA: Update                                                                   |                            |                |              |              |             |               |            |  |  |  |  |

|       |                                                                              | mode only                  |                |              |              |             |               |            |  |  |  |  |

| bit 0 |                                                                              | Full Status b              | •              | • /          |              |             |               |            |  |  |  |  |

|       |                                                                              | e complete,                |                |              |              |             |               |            |  |  |  |  |

|       |                                                                              | e not comple               | ele, 55PDU     | - is empty   |              |             |               |            |  |  |  |  |

|       | Legend:                                                                      |                            |                |              |              |             |               |            |  |  |  |  |

|       | R = Reada                                                                    | ble bit                    | W = Writab     | le bit       | U = Unimp    | lemented bi | t, read as '0 | ,          |  |  |  |  |

|       | - n = Value                                                                  | at POR                     | '1' = Bit is : | set          | '0' = Bit is |             | x = Bit is u  |            |  |  |  |  |

| FIGURE 15-10:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | I <sup>2</sup> C SLAVE MOD                                                                                                | DE TIMING V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | VITH SE                                                                            | N = 0 (RI                                                          | ECEPTION, 1                                                                                                                             | 0-BIT ADDRESS)                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                           | Cleared in software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                    | C SPOV is set<br>because SSPBUF is<br>still full. ACK is not sent. |                                                                                                                                         |                                              |

| Clock is held low until<br>byten tights                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                           | Cleared in software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                    |                                                                    | <ul> <li>Cleared by hardware when<br/>SSPADD is updated with high<br/>byte of address</li> </ul>                                        |                                              |

| Clock is held low until<br>update of SSPADD has before the product<br>taken to the taken to be the taken to the tak | d Byte of Address                                                                                                         | Cleared in software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Dummy read of SSPBUF<br>to clear BF flag                                           |                                                                    | Cleared by hardware<br>when SSPADD is updated<br>with low byte of address<br>UA is set indicating that<br>SSPADD needs to be<br>updated |                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $SDA = \frac{\text{Receive First Byte of Address}}{\sqrt{1}\sqrt{1}\sqrt{1}\sqrt{1}\sqrt{0}\sqrt{Ag}\sqrt{AB}\sqrt{AGK}}$ | SSPIF<br>(PIR1<3>) (PIR1<3>) | SSPBUF is written with contents of SSPSR<br>sontents of SSPSR<br>SSPOV (SSPCON<6>) | UA (SSPSTAT<1>)                                                    | UA is set indicating that the SSPADD needs to be updated                                                                                | CKP (CKP does not reset to '0' when SEN = 0) |

|                  | U-0                                                                                                                            | U-0                                                          | U-0                                | U-0           | R/C-1               | R/C-1               | R/C-1 | R/C-1 |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------|---------------|---------------------|---------------------|-------|-------|--|

|                  | _                                                                                                                              | _                                                            | _                                  | _             | WRT3 <sup>(1)</sup> | WRT2 <sup>(1)</sup> | WRT1  | WRT0  |  |

|                  | bit 7                                                                                                                          |                                                              |                                    |               |                     |                     |       | bit 0 |  |

| bit 7-4<br>bit 3 | <b>WRT3:</b> Wri<br>1 = Block 3                                                                                                | ented: Read<br>te Protection<br>6 (006000-00<br>6 (006000-00 | bit <sup>(1)</sup><br>7FFFh) not v | •             | ed                  |                     |       |       |  |

| bit 2            | <b>WRT2:</b> Wri<br>1 = Block 2                                                                                                | te Protection<br>2 (004000-00<br>2 (004000-00                | bit <sup>(1)</sup><br>5FFFh) not v | write protect | ed                  |                     |       |       |  |

| bit 1            | WRT1: Write Protection bit<br>1 = Block 1 (002000-003FFFh) not write protected<br>0 = Block 1 (002000-003FFFh) write protected |                                                              |                                    |               |                     |                     |       |       |  |

| bit 0            | 1 = Block 0                                                                                                                    | te Protection<br>(000200h-0<br>(000200h-0                    | 01FFFh) not                        | •             |                     |                     |       |       |  |

REGISTER 19-8: CONFIGURATION REGISTER 6 LOW (CONFIG6L: BYTE ADDRESS 30000Ah)

**Note 1:** Unimplemented in PIC18FX42 devices; maintain this bit set.

| Legend:              |                      |                                     |

|----------------------|----------------------|-------------------------------------|

| R = Readable bit     | C = Clearable bit    | U = Unimplemented bit, read as '0'  |

| - n = Value when dev | vice is unprogrammed | u = Unchanged from programmed state |

### REGISTER 19-9: CONFIGURATION REGISTER 6 HIGH (CONFIG6H: BYTE ADDRESS 30000Bh)

|         | R/C-1      | R/C-1          | C-1          | U-0           | U-0           | U-0        | U-0 | U-0   |

|---------|------------|----------------|--------------|---------------|---------------|------------|-----|-------|

|         | WRTD       | WRTB           | WRTC         | _             | —             | —          | _   | _     |

|         | bit 7      |                |              |               |               |            |     | bit 0 |

|         |            |                |              |               |               |            |     |       |

| bit 7   | WRTD: Da   | ta EEPRON      | 1 Write Prot | ection bit    |               |            |     |       |

|         | 1 = Data E | EPROM not      | write prote  | cted          |               |            |     |       |

|         | 0 = Data E | EPROM wri      | te protected | 1             |               |            |     |       |

| bit 6   | WRTB: Bo   | ot Block Wr    | te Protectio | n bit         |               |            |     |       |

|         | 1 = Boot B | lock (00000    | 0-0001FFh)   | not write pr  | otected       |            |     |       |

|         | 0 = Boot B | lock (00000    | 0-0001FFh)   | write protect | ted           |            |     |       |

| bit 5   | WRTC: Co   | nfiguration I  | Register Wr  | ite Protectio | n bit         |            |     |       |

|         | 1 = Config | uration regis  | ters (30000  | 0-3000FFh)    | not write pro | otected    |     |       |

|         | 0 = Config | uration regis  | ters (30000  | 0-3000FFh)    | write protect | ted        |     |       |

|         | Note:      | This bit is re | ead only, an | d cannot be   | changed in    | User mode. |     |       |

| bit 4-0 | Unimplem   | ented: Rea     | d as '0'     |               |               |            |     |       |

|         | -          |                |              |               |               |            |     |       |

|         | Legend:    |                |              |               |               |            |     |       |

|         |            |                |              |               |               |            |     |       |

| Legena:                 |                   |                                     |

|-------------------------|-------------------|-------------------------------------|

| R = Readable bit        | C =Clearable bit  | U = Unimplemented bit, read as '0'  |

| - n = Value when device | e is unprogrammed | u = Unchanged from programmed state |

#### 19.4.2 DATA EEPROM CODE PROTECTION

The entire Data EEPROM is protected from external reads and writes by two bits: CPD and WRTD. CPD inhibits external reads and writes of Data EEPROM. WRTD inhibits external writes to Data EEPROM. The CPU can continue to read and write Data EEPROM regardless of the protection bit settings.

### 19.4.3 CONFIGURATION REGISTER PROTECTION

The configuration registers can be write protected. The WRTC bit controls protection of the configuration registers. In User mode, the WRTC bit is readable only. WRTC can only be written via ICSP or an external programmer.

### 19.5 ID Locations

Eight memory locations (20000h - 200007h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are accessible during normal execution through the TBLRD and TBLWT instructions, or during program/verify. The ID locations can be read when the device is code protected.

The sequence for programming the ID locations is similar to programming the FLASH memory (see Section 5.5.1).

### 19.6 In-Circuit Serial Programming

PIC18FXXX microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

### 19.7 In-Circuit Debugger

When the DEBUG bit in configuration register CONFIG4L is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB<sup>®</sup> IDE. When the microcontroller has this feature enabled, some of the resources are not available for general use. Table 19-4 shows which features are consumed by the background debugger.

| I/O pins       | RB6, RB7  |

|----------------|-----------|

| Stack          | 2 levels  |

| Program Memory | 512 bytes |

| Data Memory    | 10 bytes  |

To use the In-Circuit Debugger function of the microcontroller, the design must implement In-Circuit Serial Programming connections to MCLR/VPP, VDD, GND, RB7 and RB6. This will interface to the In-Circuit Debugger module available from Microchip or one of the third party development tool companies.

### 19.8 Low Voltage ICSP Programming

The LVP bit configuration register CONFIG4L enables low voltage ICSP programming. This mode allows the microcontroller to be programmed via ICSP using a VDD source in the operating voltage range. This only means that VPP does not have to be brought to VIHH, but can instead be left at the normal operating voltage. In this mode, the RB5/PGM pin is dedicated to the programming function and ceases to be a general purpose I/O pin. During programming, VDD is applied to the MCLR/VPP pin. To enter Programming mode, VDD must be applied to the RB5/PGM, provided the LVP bit is set. The LVP bit defaults to a ('1') from the factory.

- Note 1: The High Voltage Programming mode is always available, regardless of the state of the LVP bit, by applying VIHH to the MCLR pin.

- 2: While in low voltage ICSP mode, the RB5 pin can no longer be used as a general purpose I/O pin, and should be held low during normal operation to protect against inadvertent ICSP mode entry.

- **3:** When using low voltage ICSP programming (LVP), the pull-up on RB5 becomes disabled. If TRISB bit 5 is cleared, thereby setting RB5 as an output, LATB bit 5 must also be cleared for proper operation.

If Low Voltage Programming mode is not used, the LVP bit can be programmed to a '0' and RB5/PGM becomes a digital I/O pin. However, the LVP bit may only be programmed when programming is entered with VIHH on MCLR/VPP.

It should be noted that once the LVP bit is programmed to 0, only the High Voltage Programming mode is available and only High Voltage Programming mode can be used to program the device.

When using low voltage ICSP, the part must be supplied 4.5V to 5.5V, if a bulk erase will be executed. This includes reprogramming of the code protect bits from an on-state to off-state. For all other cases of low voltage ICSP, the part may be programmed at the normal operating voltage. This means unique user IDs, or user code can be reprogrammed or added.

### TABLE 20-1: OPCODE FIELD DESCRIPTIONS

| Field           | Description                                                                                                                                                      |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| a               | RAM access bit<br>a = 0: RAM location in Access RAM (BSR register is ignored)<br>a = 1: RAM bank is specified by BSR register                                    |

|                 |                                                                                                                                                                  |

| bbb             | Bit address within an 8-bit file register (0 to 7)                                                                                                               |

| BSR<br>d        | Bank Select Register. Used to select the current RAM bank.<br>Destination select bit;                                                                            |

| α               | d = 0: store result in WREG,<br>d = 1: store result in file register f.                                                                                          |

| dest            | Destination either the WREG register or the specified register file location                                                                                     |

| f               | 8-bit Register file address (0x00 to 0xFF)                                                                                                                       |

| fs              | 12-bit Register file address (0x000 to 0xFFF). This is the source address.                                                                                       |

| fd              | 12-bit Register file address (0x000 to 0xFFF). This is the destination address.                                                                                  |

| k               | Literal field, constant data or label (may be either an 8-bit, 12-bit or a 20-bit value)                                                                         |

| label           | Label name                                                                                                                                                       |

| mm              | The mode of the TBLPTR register for the Table Read and Table Write instructions.<br>Only used with Table Read and Table Write instructions:                      |

| *               | No Change to register (such as TBLPTR with Table reads and writes)                                                                                               |

| *+              | Post-Increment register (such as TBLPTR with Table reads and writes)                                                                                             |

| * _             | Post-Decrement register (such as TBLPTR with Table reads and writes)                                                                                             |

| +*              | Pre-Increment register (such as TBLPTR with Table reads and writes)                                                                                              |

| n               | The relative address (2's complement number) for relative branch instructions, or the direct address for Call/Branch and Return instructions                     |

| PRODH           | Product of Multiply high byte                                                                                                                                    |

| PRODL           | Product of Multiply low byte                                                                                                                                     |

| s               | Fast Call/Return mode select bit.                                                                                                                                |

| 6               | s = 0: do not update into/from shadow registers<br>s = 1: certain registers loaded into/from shadow registers (Fast mode)                                        |

| u               | Unused or Unchanged                                                                                                                                              |