Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 40MHz                                                                   |

| Connectivity               | I²C, SPI, UART/USART                                                    |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                              |

| Number of I/O              | 34                                                                      |

| Program Memory Size        | 16KB (8K x 16)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 256 x 8                                                                 |

| RAM Size                   | 768 × 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                             |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                |

| Supplier Device Package    | 40-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f442-e-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 2-2:CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR

| Ranges Tested: |               |                 |          |  |  |  |  |  |

|----------------|---------------|-----------------|----------|--|--|--|--|--|

| Mode           | Freq          | C1              | C2       |  |  |  |  |  |

| LP             | 32.0 kHz      | 33 pF           | 33 pF    |  |  |  |  |  |

|                | 200 kHz       | 15 pF           | 15 pF    |  |  |  |  |  |

| XT             | 200 kHz       | 22-68 pF        | 22-68 pF |  |  |  |  |  |

|                | 1.0 MHz       | 15 pF           | 15 pF    |  |  |  |  |  |

|                | 4.0 MHz       | 15 pF           | 15 pF    |  |  |  |  |  |

| HS             | 4.0 MHz       | 15 pF           | 15 pF    |  |  |  |  |  |

|                | 8.0 MHz       | 15-33 pF        | 15-33 pF |  |  |  |  |  |

|                | 20.0 MHz      | 15-33 pF        | 15-33 pF |  |  |  |  |  |

|                | 25.0 MHz      | 15-33 pF        | 15-33 pF |  |  |  |  |  |

| These value    | es are for de | sign guidance c | only.    |  |  |  |  |  |

These values are for design guidance only See notes following this table.

| Crystals Used |                        |          |  |  |  |  |  |

|---------------|------------------------|----------|--|--|--|--|--|

| 32.0 kHz      | Epson C-001R32.768K-A  | ± 20 PPM |  |  |  |  |  |

| 200 kHz       | STD XTL 200.000KHz     | ± 20 PPM |  |  |  |  |  |

| 1.0 MHz       | ECS ECS-10-13-1        | ± 50 PPM |  |  |  |  |  |

| 4.0 MHz       | ECS ECS-40-20-1        | ± 50 PPM |  |  |  |  |  |

| 8.0 MHz       | Epson CA-301 8.000M-C  | ± 30 PPM |  |  |  |  |  |

| 20.0 MHz      | Epson CA-301 20.000M-C | ± 30 PPM |  |  |  |  |  |

|               |                        |          |  |  |  |  |  |

- Note 1: Higher capacitance increases the stability of the oscillator, but also increases the start-up time.

- 2: Rs may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

- 3: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components., or verify oscillator performance.

An external clock source may also be connected to the OSC1 pin in the HS, XT and LP modes, as shown in Figure 2-2.

# FIGURE 2-2: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

Open -

OSC2

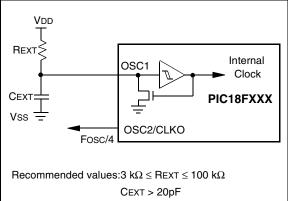

# 2.3 RC Oscillator

For timing-insensitive applications, the "RC" and "RCIO" device options offer additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 2-3 shows how the R/C combination is connected.

In the RC Oscillator mode, the oscillator frequency divided by 4 is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic.

| Note: | If the oscillator frequency divided by 4 sig- |

|-------|-----------------------------------------------|

|       | nal is not required in the application, it is |

|       | recommended to use RCIO mode to save          |

|       | current.                                      |

The RCIO Oscillator mode functions like the RC mode, except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6).

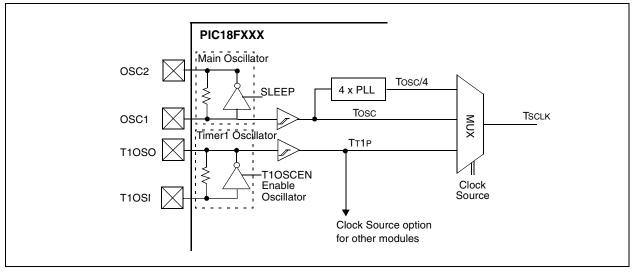

# 2.6 Oscillator Switching Feature

The PIC18FXX2 devices include a feature that allows the system clock source to be switched from the main oscillator to an alternate low frequency clock source. For the PIC18FXX2 devices, this alternate clock source is the Timer1 oscillator. If a low frequency crystal (32 kHz, for example) has been attached to the Timer1 oscillator pins and the Timer1 oscillator has been enabled, the device can switch to a Low Power Execution mode. Figure 2-7 shows a block diagram of the system clock sources. The clock switching feature is enabled <u>by programming the Oscillator Switching</u> Enable (OSCSEN) bit in Configuration Register1H to a '0'. Clock switching is disabled in an erased device. See Section 11.0 for further details of the Timer1 oscillator. See Section 19.0 for Configuration Register details.

## FIGURE 2-7: DEVICE CLOCK SOURCES

| TABLE 3-3:             | INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |     |     |     |                                    |                                                               |                                 |  |  |  |

|------------------------|---------------------------------------------------------|-----|-----|-----|------------------------------------|---------------------------------------------------------------|---------------------------------|--|--|--|

| Register               | Applicable Devices                                      |     |     |     | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset<br>RESET Instruction<br>Stack Resets | Wake-up via WDT<br>or Interrupt |  |  |  |

| IPR2                   | 242                                                     | 442 | 252 | 452 | 1 1111                             | 1 1111                                                        | u uuuu                          |  |  |  |

| PIR2                   | 242                                                     | 442 | 252 | 452 | 0 0000                             | 0 0000                                                        | u uuuu <b>(1)</b>               |  |  |  |

| PIE2                   | 242                                                     | 442 | 252 | 452 | 0 0000                             | 0 0000                                                        | u uuuu                          |  |  |  |

| IPR1                   | 242                                                     | 442 | 252 | 452 | 1111 1111                          | 1111 1111                                                     | uuuu uuuu                       |  |  |  |

| IFRI                   | 242                                                     | 442 | 252 | 452 | -111 1111                          | -111 1111                                                     | -uuu uuuu                       |  |  |  |

|                        | 242                                                     | 442 | 252 | 452 | 0000 0000                          | 0000 0000                                                     | uuuu uuuu <b>(1)</b>            |  |  |  |

| PIR1                   | 242                                                     | 442 | 252 | 452 | -000 0000                          | -000 0000                                                     | -uuu uuuu <b>(1)</b>            |  |  |  |

|                        | 242                                                     | 442 | 252 | 452 | 0000 0000                          | 0000 0000                                                     | uuuu uuuu                       |  |  |  |

| PIE1                   | 242                                                     | 442 | 252 | 452 | -000 0000                          | -000 0000                                                     | -uuu uuuu                       |  |  |  |

| TRISE                  | 242                                                     | 442 | 252 | 452 | 0000 -111                          | 0000 -111                                                     | uuuu -uuu                       |  |  |  |

| TRISD                  | 242                                                     | 442 | 252 | 452 | 1111 1111                          | 1111 1111                                                     | uuuu uuuu                       |  |  |  |

| TRISC                  | 242                                                     | 442 | 252 | 452 | 1111 1111                          | 1111 1111                                                     | սսսս սսսս                       |  |  |  |

| TRISB                  | 242                                                     | 442 | 252 | 452 | 1111 1111                          | 1111 1111                                                     | սսսս սսսս                       |  |  |  |

| TRISA <sup>(5,6)</sup> | 242                                                     | 442 | 252 | 452 | -111 1111 <b>(5)</b>               | -111 1111 <b>(5)</b>                                          | -uuu uuuu <b>(5)</b>            |  |  |  |

| LATE                   | 242                                                     | 442 | 252 | 452 | xxx                                | uuu                                                           | uuu                             |  |  |  |

| LATD                   | 242                                                     | 442 | 252 | 452 | XXXX XXXX                          | uuuu uuuu                                                     | սսսս սսսս                       |  |  |  |

| LATC                   | 242                                                     | 442 | 252 | 452 | xxxx xxxx                          | uuuu uuuu                                                     | uuuu uuuu                       |  |  |  |

| LATB                   | 242                                                     | 442 | 252 | 452 | xxxx xxxx                          | uuuu uuuu                                                     | uuuu uuuu                       |  |  |  |

| LATA <sup>(5,6)</sup>  | 242                                                     | 442 | 252 | 452 | -xxx xxxx(5)                       | -uuu uuuu <b>(5)</b>                                          | -uuu uuuu <b>(5)</b>            |  |  |  |

| PORTE                  | 242                                                     | 442 | 252 | 452 | 000                                | 000                                                           | uuu                             |  |  |  |

| PORTD                  | 242                                                     | 442 | 252 | 452 | xxxx xxxx                          | uuuu uuuu                                                     | սսսս սսսս                       |  |  |  |

| PORTC                  | 242                                                     | 442 | 252 | 452 | XXXX XXXX                          | uuuu uuuu                                                     | սսսս սսսս                       |  |  |  |

| PORTB                  | 242                                                     | 442 | 252 | 452 | xxxx xxxx                          | uuuu uuuu                                                     | սսսս սսսս                       |  |  |  |

| PORTA <sup>(5,6)</sup> | 242                                                     | 442 | 252 | 452 | -x0x 0000 <b>(5)</b>               | -u0u 0000 <b>(5)</b>                                          | -uuu uuuu <b>(5)</b>            |  |  |  |

TABLE 3-3:

INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

**Note 1:** One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- **3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 4: See Table 3-2 for RESET value for specific condition.

- 5: Bit 6 of PORTA, LATA, and TRISA are enabled in ECIO and RCIO Oscillator modes only. In all other Oscillator modes, they are disabled and read '0'.

- 6: Bit 6 of PORTA, LATA and TRISA are not available on all devices. When unimplemented, they are read '0'.

# PIC18FXX2

NOTES:

# PIC18FXX2

## EXAMPLE 7-3: 16 x 16 UNSIGNED MULTIPLY ROUTINE

|   | MOVF     | ARG1L,  | W      |   |                  |

|---|----------|---------|--------|---|------------------|

|   | MULWF    | -       |        | ; | ARG1L * ARG2L -> |

|   |          |         |        |   | PRODH: PRODL     |

|   | MOVFF    | PRODH,  | RES1   |   |                  |

|   | MOVFF    |         |        |   |                  |

|   | 110 1 1  | 110001, | ICED 0 | ' |                  |

| ' | MOVF     | ARG1H,  | W      |   |                  |

|   | MULWF    |         | ••     |   | ARG1H * ARG2H -> |

|   | пошл     | 1110211 |        |   | PRODH: PRODL     |

|   | MOVFF    | PRODH,  | PEGS   |   | TRODITIRODE      |

|   |          | PRODL,  |        |   |                  |

|   | 110 11 1 | IRODE,  | ICHO2  | ' |                  |

| ; | MOVF     | ARG1L,  | W      |   |                  |

|   | MULWF    |         |        |   | ARG1L * ARG2H -> |

|   | MOTIME   | ARGZII  |        | ' | PRODH: PRODL     |

|   | MOVF     | PRODL,  | 747    | ; | FRODITERRODE     |

|   | ADDWF    |         |        |   | Add cross        |

|   |          | PRODH,  |        |   | products         |

|   |          | RES2,   |        | ; | produces         |

|   | CLRF     | -       | -      | ; |                  |

|   |          | RES3,   | F      | ; |                  |

|   | ADDWFC   | REDJ,   | Ľ      | ' |                  |

| ' | MOVF     | ARG1H,  | W      | ; |                  |

|   | MULWF    |         |        |   | ARG1H * ARG2L -> |

|   | MOTIME   | ARGZI   |        |   | PRODH: PRODL     |

|   | MOVF     | PRODL,  | TAT    | ; |                  |

|   | ADDWF    |         |        |   | Add cross        |

|   | MOVF     | PRODH,  |        |   | products         |

|   |          | RES2,   |        |   | Produces         |

|   | CLRF     |         | τ.     | ; |                  |

|   |          | RES3,   | F      | ; |                  |

|   | ADD MI.C | 1, 2017 | τ.     | ; |                  |

|   |          |         |        |   |                  |

Example 7-4 shows the sequence to do a 16 x 16 signed multiply. Equation 7-2 shows the algorithm used. The 32-bit result is stored in four registers, RES3:RES0. To account for the sign bits of the arguments, each argument pairs Most Significant bit (MSb) is tested and the appropriate subtractions are done.

#### EQUATION 7-2: 16 x 16 SIGNED MULTIPLICATION ALGORITHM

| RES3:R | ESO                                                             |

|--------|-----------------------------------------------------------------|

| =      | ARG1H:ARG1L • ARG2H:ARG2L                                       |

| =      | $(ARG1H \bullet ARG2H \bullet 2^{16}) +$                        |

|        | $(ARG1H \bullet ARG2L \bullet 2^8) +$                           |

|        | $(ARG1L \bullet ARG2H \bullet 2^8) +$                           |

|        | $(ARG1L \bullet ARG2L) +$                                       |

|        | $(-1 \bullet ARG2H < 7 > \bullet ARG1H:ARG1L \bullet 2^{16}) +$ |

|        | $(-1 \bullet ARG1H < 7 > \bullet ARG2H: ARG2L \bullet 2^{16})$  |

## EXAMPLE 7-4: 16 x 16 SIGNED MULTIPLY ROUTINE

|     | MOVF           | ARG1L,  | W      |   |                  |

|-----|----------------|---------|--------|---|------------------|

|     | MULWF          | ARG2L   |        | ; | ARG1L * ARG2L -> |

|     |                |         |        | ; | PRODH: PRODL     |

|     | MOVFF          | PRODH,  | RES1   | ; |                  |

|     | MOVFF          | PRODL,  | RES0   | ; |                  |

| ;   |                |         |        |   |                  |

|     | MOVF           | ARG1H,  | W      |   |                  |

|     | MULWF          | ARG2H   |        | ; | ARG1H * ARG2H -> |

|     |                |         |        | ; | PRODH: PRODL     |

|     | MOVFF          | PRODH,  | RES3   | ; |                  |

|     | MOVFF          | PRODL,  | RES2   | ; |                  |

| ;   |                |         |        |   |                  |

|     | MOVF           | ARG1L,  | W      |   |                  |

|     | MULWF          | ARG2H   |        |   | ARG1L * ARG2H -> |

|     |                |         |        | ; | PRODH: PRODL     |

|     | MOVF           | PRODL,  |        | ; |                  |

|     | ADDWF          | RES1,   | F      |   | Add cross        |

|     | MOVF           |         | W      | ; | products         |

|     | ADDWFC         |         | F      | ; |                  |

|     |                | WREG    | _      | ; |                  |

|     | ADDWFC         | RES3,   | F      | ; |                  |

| ;   |                |         |        |   |                  |

|     | MOVF           | ARG1H,  | W      | ; |                  |

|     | MULWF          | ARG2L   |        |   | ARG1H * ARG2L -> |

|     | MOLTE          | DDODI   |        |   | PRODH: PRODL     |

|     | MOVF           | PRODL,  |        | ; | Add among        |

|     |                | RES1,   | F      |   | Add cross        |

|     | MOVF           |         | W<br>F |   | products         |

|     | ADDWFC<br>CLRF | WREG    | г      | ; |                  |

|     | ADDWFC         | RES3,   | F      | ; |                  |

|     | ADDWIC         | RE05,   | Ľ      | ; |                  |

| ;   | BTFSS          | ARG2H,  | 7      |   | ARG2H:ARG2L neg? |

|     | BRA            | SIGN AF |        |   | no, check ARG1   |

|     | MOVF           | ARG1L,  |        | ; | no, encer meer   |

|     | SUBWF          | RES2    |        | ; |                  |

|     | MOVF           | ARG1H,  | W      | ; |                  |

|     | SUBWFB         |         |        | ' |                  |

| ;   |                |         |        |   |                  |

|     | N_ARG1         |         |        |   |                  |

|     |                | ARG1H,  | 7      | ; | ARG1H:ARG1L neg? |

|     | BRA            | CONT_CC | DE     |   | no, done         |

|     | MOVF           | ARG2L,  |        | ; |                  |

|     | SUBWF          | RES2    |        | ; |                  |

|     | MOVF           | ARG2H,  | W      | ; |                  |

|     | SUBWFB         | RES3    |        |   |                  |

| ;   |                |         |        |   |                  |

| CON | T_CODE         |         |        |   |                  |

|     | :              |         |        |   |                  |

|     |                |         |        |   |                  |

# 8.0 INTERRUPTS

The PIC18FXX2 devices have multiple interrupt sources and an interrupt priority feature that allows each interrupt source to be assigned a high priority level or a low priority level. The high priority interrupt vector is at 000008h and the low priority interrupt vector is at 000018h. High priority interrupt events will override any low priority interrupts that may be in progress.

There are ten registers which are used to control interrupt operation. These registers are:

- RCON

- INTCON

- INTCON2

- INTCON3

- PIR1, PIR2

- PIE1, PIE2

- IPR1, IPR2

It is recommended that the Microchip header files supplied with MPLAB<sup>®</sup> IDE be used for the symbolic bit names in these registers. This allows the assembler/ compiler to automatically take care of the placement of these bits within the specified register.

Each interrupt source, except INTO, has three bits to control its operation. The functions of these bits are:

- Flag bit to indicate that an interrupt event occurred

- Enable bit that allows program execution to branch to the interrupt vector address when the flag bit is set

- Priority bit to select high priority or low priority

The interrupt priority feature is enabled by setting the IPEN bit (RCON<7>). When interrupt priority is enabled, there are two bits which enable interrupts globally. Setting the GIEH bit (INTCON<7>) enables all interrupts that have the priority bit set. Setting the GIEL bit (INTCON<6>) enables all interrupts that have the priority bit cleared. When the interrupt flag, enable bit and appropriate global interrupt enable bit are set, the interrupt will vector immediately to address 000008h or 000018h, depending on the priority level. Individual interrupts can be disabled through their corresponding enable bits.

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PICmicro<sup>®</sup> mid-range devices. In Compatibility mode, the interrupt priority bits for each source have no effect. INTCON<6> is the PEIE bit, which enables/disables all peripheral interrupt sources. INTCON<7> is the GIE bit, which enables/disables all interrupt sources. All interrupts branch to address 000008h in Compatibility mode.

When an interrupt is responded to, the Global Interrupt Enable bit is cleared to disable further interrupts. If the IPEN bit is cleared, this is the GIE bit. If interrupt priority levels are used, this will be either the GIEH or GIEL bit. High priority interrupt sources can interrupt a low priority interrupt.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (000008h or 000018h). Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bits must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit (GIEH or GIEL if priority levels are used), which re-enables interrupts.

For external interrupt events, such as the INT pins or the PORTB input change interrupt, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding enable bit or the GIE bit.

**Note:** Do not use the MOVFF instruction to modify any of the Interrupt control registers while **any** interrupt is enabled. Doing so may cause erratic microcontroller behavior.

|         | U-0                                                                         | U-0          | U-0          | R/W-0         | R/W-0       | R/W-0     | R/W-0        | R/W-0  |  |  |

|---------|-----------------------------------------------------------------------------|--------------|--------------|---------------|-------------|-----------|--------------|--------|--|--|

|         | —                                                                           | —            | —            | EEIE          | BCLIE       | LVDIE     | TMR3IE       | CCP2IE |  |  |

|         | bit 7                                                                       |              |              |               |             |           |              | bit 0  |  |  |

|         |                                                                             |              |              |               |             |           |              |        |  |  |

| bit 7-5 | Unimpleme                                                                   | nted: Read   | l as '0'     |               |             |           |              |        |  |  |

| bit 4   | EEIE: Data E                                                                | EPROM/F      | LASH Write   | e Operation I | nterrupt En | able bit  |              |        |  |  |

|         | 1 = Enabled                                                                 |              |              |               |             |           |              |        |  |  |

|         | 0 = Disabled                                                                |              |              |               |             |           |              |        |  |  |

| bit 3   | BCLIE: Bus                                                                  | Collision In | terrupt Ena  | ble bit       |             |           |              |        |  |  |

|         | 1 = Enabled                                                                 |              |              |               |             |           |              |        |  |  |

|         | 0 = Disabled                                                                |              |              |               |             |           |              |        |  |  |

| bit 2   | LVDIE: Low                                                                  | Voltage De   | tect Interru | ot Enable bit |             |           |              |        |  |  |

|         | 1 = Enabled                                                                 |              |              |               |             |           |              |        |  |  |

|         | 0 = Disabled                                                                |              |              |               |             |           |              |        |  |  |

| bit 1   | TMR3IE: TMR3 Overflow Interrupt Enable bit                                  |              |              |               |             |           |              |        |  |  |

|         | 1 = Enables                                                                 |              |              |               |             |           |              |        |  |  |

|         | 0 = Disables                                                                |              |              |               |             |           |              |        |  |  |

| bit 0   | <b>CCP2IE</b> : CCP2 Interrupt Enable bit<br>1 = Enables the CCP2 interrupt |              |              |               |             |           |              |        |  |  |

|         | 1 = Enables<br>0 = Disables                                                 |              |              |               |             |           |              |        |  |  |

|         |                                                                             |              | menupi       |               |             |           |              |        |  |  |

|         | Legend:                                                                     |              |              |               |             |           |              |        |  |  |

|         | -                                                                           | - hit        | 14/ 14       | witchle hit   |             | ا         | hit un na    | (O)    |  |  |

|         | R = Readabl                                                                 |              |              | ritable bit   |             |           | bit, read as |        |  |  |

|         | - n = Value a                                                               | t POR        | '1' = B      | it is set     | ′0′ = Bit i | s cleared | x = Bit is u | nknown |  |  |

## REGISTER 8-7: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

# 8.6 INT0 Interrupt

External interrupts on the RB0/INT0, RB1/INT1 and RB2/INT2 pins are edge triggered: either rising, if the corresponding INTEDGx bit is set in the INTCON2 register, or falling, if the INTEDGx bit is clear. When a valid edge appears on the RBx/INTx pin, the corresponding flag bit INTxF is set. This interrupt can be disabled by clearing the corresponding enable bit INTxE. Flag bit INTxF must be cleared in software in the Interrupt Service Routine before re-enabling the interrupt. All external interrupts (INT0, INT1 and INT2) can wake-up the processor from SLEEP, if bit INTxE was set prior to going into SLEEP. If the global interrupt enable bit GIE is set, the processor will branch to the interrupt vector following wake-up.

Interrupt priority for INT1 and INT2 is determined by the value contained in the interrupt priority bits, INT1IP (INTCON3<6>) and INT2IP (INTCON3<7>). There is no priority bit associated with INT0. It is always a high priority interrupt source.

## 8.7 TMR0 Interrupt

In 8-bit mode (which is the default), an overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit TMR0IF. In 16-bit mode, an overflow (FFFFh  $\rightarrow$  0000h) in the TMR0H:TMR0L registers will set flag bit TMR0IF. The interrupt can be enabled/disabled by setting/ clearing enable bit T0IE (INTCON<5>). Interrupt priority for Timer0 is determined by the value contained in the interrupt priority bit TMR0IP (INTCON2<2>). See Section 10.0 for further details on the Timer0 module.

## 8.8 PORTB Interrupt-on-Change

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit, RBIE (INTCON<3>). Interrupt priority for PORTB interrupt-on-change is determined by the value contained in the interrupt priority bit, RBIP (INTCON2<0>).

# 8.9 Context Saving During Interrupts

During an interrupt, the return PC value is saved on the stack. Additionally, the WREG, STATUS and BSR registers are saved on the fast return stack. If a fast return from interrupt is not used (See Section 4.3), the user may need to save the WREG, STATUS and BSR registers in software. Depending on the user's application, other registers may also need to be saved. Equation 8-1 saves and restores the WREG, STATUS and BSR registers during an Interrupt Service Routine.

EXAMPLE 8-1: SAVING STATUS, WREG AND BSR REGISTERS IN RAM

| MOVWF<br>MOVFF<br>MOVFF | W_TEMP<br>STATUS, STATUS_TEMP<br>BSR, BSR_TEMP | ; W_TEMP is in virtual bank<br>; STATUS_TEMP located anywhere<br>; BSR located anywhere |

|-------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------|

| ;                       |                                                |                                                                                         |

| ; USER                  | ISR CODE                                       |                                                                                         |

| ;                       |                                                |                                                                                         |

| MOVFF                   | BSR TEMP, BSR                                  | ; Restore BSR                                                                           |

| MOVF                    | W TEMP, W                                      | ; Restore WREG                                                                          |

| MOVFF                   |                                                | ; Restore STATUS                                                                        |

|                         |                                                |                                                                                         |

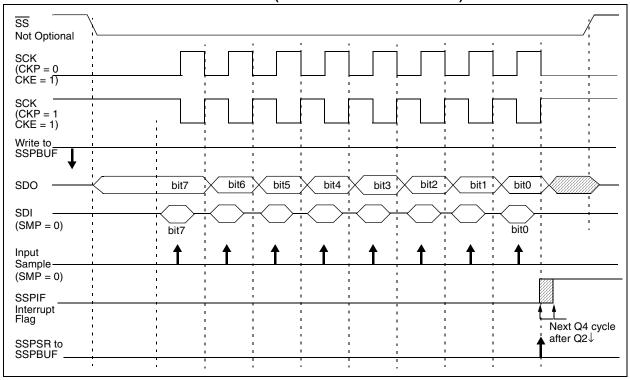

# FIGURE 15-6: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

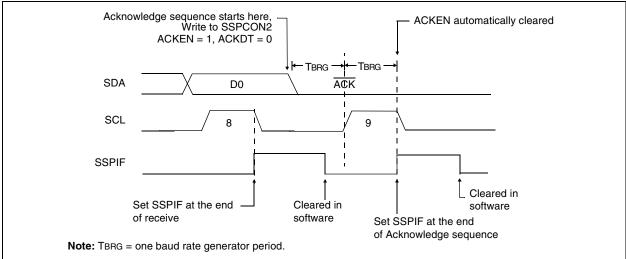

### 15.4.12 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge sequence enable bit, ACKEN (SSPCON2<4>). When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit are presented on the SDA pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The baud rate generator then counts for one rollover period (TBRG) and the SCL pin is de-asserted (pulled high). When the SCL pin is sampled high (clock arbitration), the baud rate generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the baud rate generator is turned off and the MSSP module then goes into IDLE mode (Figure 15-23).

## 15.4.12.1 WCOL Status Flag

If the user writes the SSPBUF when an Acknowledge sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

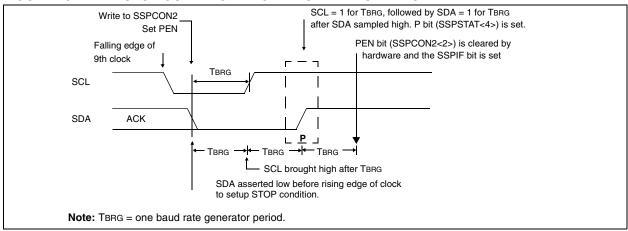

## 15.4.13 STOP CONDITION TIMING

A STOP bit is asserted on the SDA pin at the end of a receive/transmit by setting the STOP sequence enable bit, PEN (SSPCON2<2>). At the end of a receive/transmit the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the baud rate generator is reloaded and counts down to 0. When the baud rate generator times out, the SCL pin will be brought high, and one TBRG (baud rate generator rollover count) later, the SDA pin will be de-asserted. When the SDA pin is sampled high while SCL is high, the P bit (SSPSTAT<4>) is set. A TBRG later, the PEN bit is cleared and the SSPIF bit is set (Figure 15-24).

#### 15.4.13.1 WCOL Status Flag

If the user writes the SSPBUF when a STOP sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

## FIGURE 15-23: ACKNOWLEDGE SEQUENCE WAVEFORM

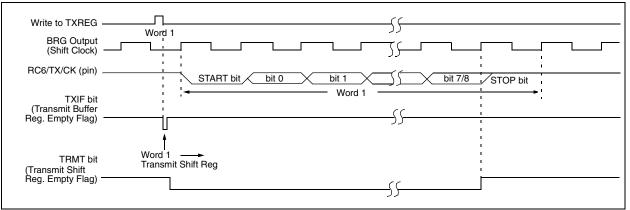

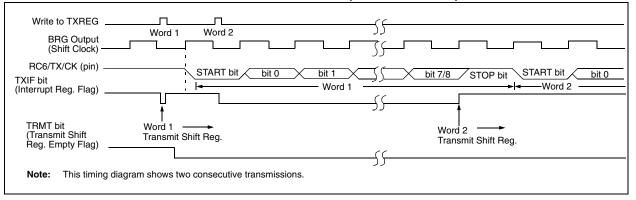

#### FIGURE 16-3: ASYNCHRONOUS TRANSMISSION (BACK TO BACK)

#### TABLE 16-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Name   | Bit 7                                     | Bit 6       | Bit 5  | Bit 4         | Bit 3 | Bit 2  | Bit 1         | Bit 0  | Value on<br>POR, BOR | Value o<br>All Oth<br>RESET | ner |

|--------|-------------------------------------------|-------------|--------|---------------|-------|--------|---------------|--------|----------------------|-----------------------------|-----|

| INTCON | GIE/GIEH                                  | PEIE/GIEL   | TMR0IE | <b>INTOIE</b> | RBIE  | TMR0IF | <b>INT0IF</b> | RBIF   | 0000 000x            | 0000 0                      | 00u |

| PIR1   | PSPIF <sup>(1)</sup>                      | ADIF        | RCIF   | TXIF          | SSPIF | CCP1IF | TMR2IF        | TMR1IF | 0000 0000            | 0000 0                      | 000 |

| PIE1   | PSPIE <sup>(1)</sup>                      | ADIE        | RCIE   | TXIE          | SSPIE | CCP1IE | TMR2IE        | TMR1IE | 0000 0000            | 0000 0                      | 000 |

| IPR1   | PSPIP <sup>(1)</sup>                      | ADIP        | RCIP   | TXIP          | SSPIP | CCP1IP | TMR2IP        | TMR1IP | 0000 0000            | 0000 0                      | 000 |

| RCSTA  | SPEN                                      | RX9         | SREN   | CREN          | ADDEN | FERR   | OERR          | RX9D   | 0000 -00x            | 0000 -                      | 00x |

| TXREG  | USART Tra                                 | nsmit Regis | ter    |               |       |        |               |        | 0000 0000            | 0000 0                      | 000 |

| TXSTA  | CSRC                                      | TX9         | TXEN   | SYNC          | _     | BRGH   | TRMT          | TX9D   | 0000 -010            | 0000 -                      | 010 |

| SPBRG  | SPBRG Baud Rate Generator Register        |             |        |               |       |        |               |        | 0000 0000            | 0000 0                      | 000 |

|        | example unimplemented leasting used as 10 |             |        |               |       |        |               |        |                      |                             |     |

Legend: x = unknown, - = unimplemented locations read as '0'.

Shaded cells are not used for Asynchronous Transmission.

Note 1: The PSPIF, PSPIE and PSPIP bits are reserved on the PIC18F2X2 devices; always maintain these bits clear.

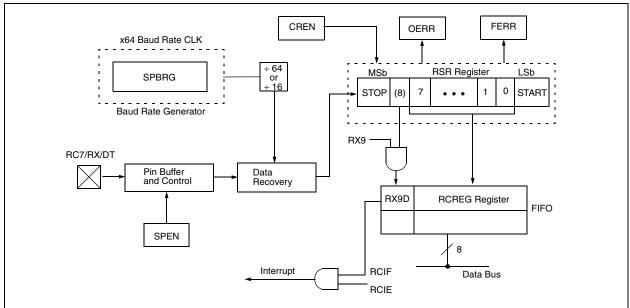

## 16.2.2 USART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 16-4. The data is received on the RC7/RX/DT pin and drives the data recovery block. The data recovery block is actually a high speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at Fosc. This mode would typically be used in RS-232 systems.

To set up an Asynchronous Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH (Section 16.1).

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, set enable bit RCIE.

- 4. If 9-bit reception is desired, set bit RX9.

- 5. Enable the reception by setting bit CREN.

- 6. Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 7. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

# 16.2.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is required, set the BRGH bit.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are required, set the RCEN bit and select the desired priority level with the RCIP bit.

- 4. Set the RX9 bit to enable 9-bit reception.

- 5. Set the ADDEN bit to enable address detect.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF bit will be set when reception is complete. The interrupt will be acknowledged if the RCIE and GIE bits are set.

- 8. Read the RCSTA register to determine if any error occurred during reception, as well as read bit 9 of data (if applicable).

- 9. Read RCREG to determine if the device is being addressed.

- 10. If any error occurred, clear the CREN bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and interrupt the CPU.

## FIGURE 16-4: USART RECEIVE BLOCK DIAGRAM

#### 18.2.1 REFERENCE VOLTAGE SET POINT

The Internal Reference Voltage of the LVD module may be used by other internal circuitry (the Programmable Brown-out Reset). If these circuits are disabled (lower current consumption), the reference voltage circuit requires a time to become stable before a low voltage condition can be reliably detected. This time is invariant of system clock speed. This start-up time is specified in electrical specification parameter 36. The low voltage interrupt flag will not be enabled until a stable reference voltage is reached. Refer to the waveform in Figure 18-4.

#### 18.2.2 CURRENT CONSUMPTION

When the module is enabled, the LVD comparator and voltage divider are enabled and will consume static current. The voltage divider can be tapped from multiple places in the resistor array. Total current consumption, when enabled, is specified in electrical specification parameter #D022B.

### 18.3 Operation During SLEEP

When enabled, the LVD circuitry continues to operate during SLEEP. If the device voltage crosses the trip point, the LVDIF bit will be set and the device will wakeup from SLEEP. Device execution will continue from the interrupt vector address if interrupts have been globally enabled.

## 18.4 Effects of a RESET

A device RESET forces all registers to their RESET state. This forces the LVD module to be turned off.

# PIC18FXX2

| GOT   | ю                                       | Uncondi                                                                       | Unconditional Branch                      |                             |                     |                                        |  |  |  |

|-------|-----------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------|-----------------------------|---------------------|----------------------------------------|--|--|--|

| Synt  | ax:                                     | [ label ]                                                                     | [ <i>label</i> ] GOTO k                   |                             |                     |                                        |  |  |  |

| Ope   | rands:                                  | $0 \le k \le 10$                                                              | 048575                                    |                             |                     |                                        |  |  |  |

| Ope   | ration:                                 | $k \rightarrow PC <$                                                          | 20:1>                                     |                             |                     |                                        |  |  |  |

| Statu | us Affected:                            | None                                                                          |                                           |                             |                     |                                        |  |  |  |

| 1st v | oding:<br>vord (k<7:0>)<br>word(k<19:8> | .) 1110                                                                       | 1111<br>k <sub>19</sub> kkk               | k <sub>7</sub> k}<br>kkk    |                     | kkkk <sub>0</sub><br>kkkk <sub>8</sub> |  |  |  |

| Deso  | cription:                               | GOTO allo<br>branch ar<br>2 Mbyte r<br>value 'k' i<br>GOTO is a<br>instructio | nywhere<br>nemory<br>s loadec<br>Ilways a | withir<br>range<br>I into I | n en<br>. Th<br>PC< | tire<br>ne 20-bit<br>:20:1>.           |  |  |  |

| Wor   | ds:                                     | 2                                                                             |                                           |                             |                     |                                        |  |  |  |

| Cycl  | es:                                     | 2                                                                             | 2                                         |                             |                     |                                        |  |  |  |

| QC    | ycle Activity:                          |                                                                               |                                           |                             |                     |                                        |  |  |  |

|       | Q1                                      | Q2                                                                            | Q                                         | 3                           |                     | Q4                                     |  |  |  |

|       | Decode                                  | Read literal<br>'k'<7:0>,                                                     | No<br>operat                              |                             |                     | ad literal<br><19:8>,                  |  |  |  |

| Decode    | Read literal<br>'k'<7:0>, | No<br>operation | Read literal<br>'k'<19:8>,<br>Write to PC |

|-----------|---------------------------|-----------------|-------------------------------------------|

| No        | No                        | No              | No                                        |

| operation | operation                 | operation       | operation                                 |

Example: GOTO THERE

After Instruction

PC = Address (THERE)

| INC                                    | F            | Incremen                                                                                                      | Increment f                                                  |                                                                |                                                        |  |  |  |

|----------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------|--|--|--|

| Synt                                   | ax:          | [ label ]                                                                                                     | INCF                                                         | f [,d [,a]                                                     |                                                        |  |  |  |

| Operands:                              |              | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                                                                         | 5                                                            |                                                                |                                                        |  |  |  |

| Ope                                    | ration:      | (f) + 1 $\rightarrow$                                                                                         | dest                                                         |                                                                |                                                        |  |  |  |

| Statu                                  | us Affected: | C, DC, N                                                                                                      | C, DC, N, OV, Z                                              |                                                                |                                                        |  |  |  |

| Enco                                   | oding:       | 0010                                                                                                          | 10da                                                         | ffff                                                           | ffff                                                   |  |  |  |

|                                        |              | increment<br>placed in<br>placed ba<br>If 'a' is 0,<br>selected,<br>If 'a' = 1, 1<br>selected a<br>(default). | W. If 'd'<br>.ck in reg<br>the Acce<br>overridin<br>then the | is 1, the<br>gister 'f' (<br>ess Bank<br>ng the BS<br>bank wil | result is<br>default).<br>will be<br>SR value.<br>I be |  |  |  |

| Words:<br>Cycles:<br>Q Cycle Activity: |              | 1                                                                                                             |                                                              |                                                                |                                                        |  |  |  |

|                                        |              | 1                                                                                                             |                                                              |                                                                |                                                        |  |  |  |

|                                        |              | :                                                                                                             |                                                              |                                                                |                                                        |  |  |  |

| ~ ~                                    |              |                                                                                                               |                                                              |                                                                |                                                        |  |  |  |

|                                        | Q1           | Q2                                                                                                            | Q3                                                           |                                                                | Q4                                                     |  |  |  |

|                                        | Q1<br>Decode | Q2<br>Read<br>register 'f'                                                                                    | Q3<br>Proce<br>Data                                          | ss V                                                           | Q4<br>Vrite to<br>stination                            |  |  |  |

|                                        |              | Read                                                                                                          | Proce<br>Data                                                | ss V                                                           | Vrite to                                               |  |  |  |

# 21.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK object linker combines relocatable objects created by the MPASM assembler and the MPLAB C17 and MPLAB C18 C compilers. It can also link relocatable objects from pre-compiled libraries, using directives from a linker script.

The MPLIB object librarian is a librarian for precompiled code to be used with the MPLINK object linker. When a routine from a library is called from another source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications. The MPLIB object librarian manages the creation and modification of library files.

The MPLINK object linker features include:

- Integration with MPASM assembler and MPLAB C17 and MPLAB C18 C compilers.

- Allows all memory areas to be defined as sections to provide link-time flexibility.

The MPLIB object librarian features include:

- Easier linking because single libraries can be included instead of many smaller files.

- Helps keep code maintainable by grouping related modules together.

- Allows libraries to be created and modules to be added, listed, replaced, deleted or extracted.

# 21.5 MPLAB SIM Software Simulator

The MPLAB SIM software simulator allows code development in a PC-hosted environment by simulating the PICmicro series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user-defined key press, to any of the pins. The execution can be performed in single step, execute until break, or trace mode.

The MPLAB SIM simulator fully supports symbolic debugging using the MPLAB C17 and the MPLAB C18 C compilers and the MPASM assembler. The software simulator offers the flexibility to develop and debug code outside of the laboratory environment, making it an excellent multiproject software development tool.

# 21.6 MPLAB ICE High Performance Universal In-Circuit Emulator with MPLAB IDE

The MPLAB ICE universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PICmicro microcontrollers (MCUs). Software control of the MPLAB ICE in-circuit emulator is provided by the MPLAB Integrated Development Environment (IDE), which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB ICE in-circuit emulator allows expansion to support new PICmicro microcontrollers.

The MPLAB ICE in-circuit emulator system has been designed as a real-time emulation system, with advanced features that are generally found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows environment were chosen to best make these features available to you, the end user.

# 21.7 ICEPIC In-Circuit Emulator

The ICEPIC low cost, in-circuit emulator is a solution for the Microchip Technology PIC16C5X, PIC16C6X, PIC16C7X and PIC16CXXX families of 8-bit One-Time-Programmable (OTP) microcontrollers. The modular system can support different subsets of PIC16C5X or PIC16CXXX products through the use of interchangeable personality modules, or daughter boards. The emulator is capable of emulating without target application circuitry being present.

# 21.8 MPLAB ICD In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD, is a powerful, low cost, run-time development tool. This tool is based on the FLASH PICmicro MCUs and can be used to develop for this and other PICmicro microcontrollers. The MPLAB ICD utilizes the in-circuit debugging capability built into the FLASH devices. This feature, along with Microchip's In-Circuit Serial Programming<sup>™</sup> protocol, offers cost-effective in-circuit FLASH debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by watching variables, single-stepping and setting break points. Running at full speed enables testing hardware in realtime.

# 21.9 PRO MATE II Universal Device Programmer

The PRO MATE II universal device programmer is a full-featured programmer, capable of operating in stand-alone mode, as well as PC-hosted mode. The PRO MATE II device programmer is CE compliant.

The PRO MATE II device programmer has programmable VDD and VPP supplies, which allow it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for instructions and error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In stand-alone mode, the PRO MATE II device programmer can read, verify, or program PICmicro devices. It can also set code protection in this mode.

## 21.10 PICSTART Plus Entry Level Development Programmer

The PICSTART Plus development programmer is an easy-to-use, low cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient.

The PICSTART Plus development programmer supports all PICmicro devices with up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant.

## 21.11 PICDEM 1 Low Cost PICmicro Demonstration Board

The PICDEM 1 demonstration board is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44, All necessary hardware and software is included to run basic demo programs. The user can program the sample microcontrollers provided with the PICDEM 1 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The user can also connect the PICDEM 1 demonstration board to the MPLAB ICE incircuit emulator and download the firmware to the emulator for testing. A prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push button switches and eight LEDs connected to PORTB.

## 21.12 PICDEM 2 Low Cost PIC16CXX Demonstration Board

The PICDEM 2 demonstration board is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 2 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a serial EEPROM to demonstrate usage of the I<sup>2</sup>C<sup>™</sup> bus and separate headers for connection to an LCD module and a keypad.

| Param<br>No. | Sym             | Characteristic                | Min | Тур† | Мах | Units | Conditions   |

|--------------|-----------------|-------------------------------|-----|------|-----|-------|--------------|

| _            | Fosc            | Oscillator Frequency Range    | 4   | —    | 10  | MHz   | HS mode only |

| —            | Fsys            | On-chip VCO System Frequency  | 16  | —    | 40  | MHz   | HS mode only |

| —            | t <sub>rc</sub> | PLL Start-up Time (Lock Time) | —   | —    | 2   | ms    |              |

| _            | $\Delta CLK$    | CLKO Stability (Jitter)       | -2  | —    | +2  | %     |              |

# TABLE 22-5:PLL CLOCK TIMING SPECIFICATIONS (VDD = 4.2 TO 5.5V)

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

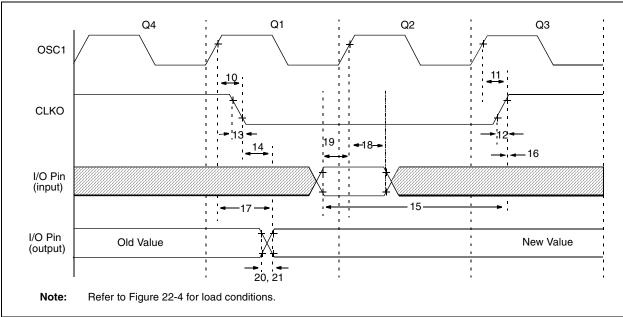

# FIGURE 22-6: CLKO AND I/O TIMING

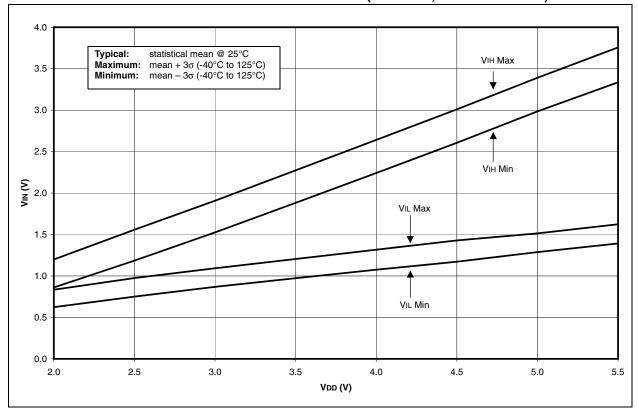

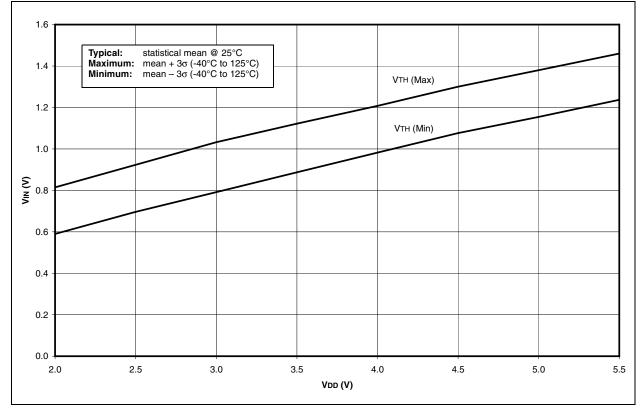

FIGURE 23-25: MINIMUM AND MAXIMUM VIN vs. VDD (ST INPUT, -40°C TO +125°C)

© 2006 Microchip Technology Inc.

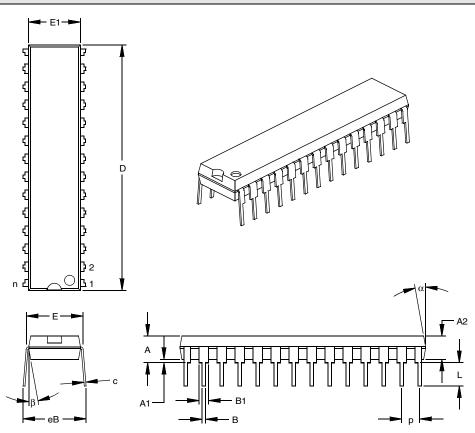

# 24.2 Package Details

The following sections give the technical details of the packages.

# 28-Lead Skinny Plastic Dual In-line (SP) – 300 mil Body (PDIP)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units        | INCHES* |       |       | MILLIMETERS |       |       |

|----------------------------|--------------|---------|-------|-------|-------------|-------|-------|

| Dimer                      | ision Limits | MIN     | NOM   | MAX   | MIN         | NOM   | MAX   |

| Number of Pins             | 28           |         |       | 28    |             |       |       |

| Pitch                      | р            |         | .100  |       |             | 2.54  |       |

| Top to Seating Plane       | А            | .140    | .150  | .160  | 3.56        | 3.81  | 4.06  |

| Molded Package Thickness   | A2           | .125    | .130  | .135  | 3.18        | 3.30  | 3.43  |

| Base to Seating Plane      | A1           | .015    |       |       | 0.38        |       |       |

| Shoulder to Shoulder Width | E            | .300    | .310  | .325  | 7.62        | 7.87  | 8.26  |

| Molded Package Width       | E1           | .275    | .285  | .295  | 6.99        | 7.24  | 7.49  |

| Overall Length             | D            | 1.345   | 1.365 | 1.385 | 34.16       | 34.67 | 35.18 |

| Tip to Seating Plane       | L            | .125    | .130  | .135  | 3.18        | 3.30  | 3.43  |

| Lead Thickness             | С            | .008    | .012  | .015  | 0.20        | 0.29  | 0.38  |

| Upper Lead Width           | B1           | .040    | .053  | .065  | 1.02        | 1.33  | 1.65  |

| Lower Lead Width           | В            | .016    | .019  | .022  | 0.41        | 0.48  | 0.56  |

| Overall Row Spacing        | § eB         | .320    | .350  | .430  | 8.13        | 8.89  | 10.92 |

| Mold Draft Angle Top       | α            | 5       | 10    | 15    | 5           | 10    | 15    |

| Mold Draft Angle Bottom    | β            | 5       | 10    | 15    | 5           | 10    | 15    |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimension D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MO-095

Drawing No. C04-070

# W

| Wake up from CLEED         | 105 005      |

|----------------------------|--------------|

| Wake-up from SLEEP         | 195, 205     |

| Using Interrupts           |              |

| Watchdog Timer (WDT)       | 195, 203     |

| Associated Registers       | 204          |

| Control Register           | 203          |

| Postscaler                 | 203, 204     |

| Programming Considerations |              |

| RC Oscillator              | 203          |

| Time-out Period            | 203          |

| WCOL                       | 153          |

| WCOL Status Flag1          | 53, 155, 158 |

| WWW, On-Line Support       | 5            |

# Х

| XORLW | 251 |

|-------|-----|

|       | 201 |

| XOBWE | 252 |

| XORWF | 202 |