Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                  |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 34                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 768 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f442t-e-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.10 Access Bank

The Access Bank is an architectural enhancement which is very useful for C compiler code optimization. The techniques used by the C compiler may also be useful for programs written in assembly.

This data memory region can be used for:

- · Intermediate computational values

- · Local variables of subroutines

- Faster context saving/switching of variables

- · Common variables

- Faster evaluation/control of SFRs (no banking)

The Access Bank is comprised of the upper 128 bytes in Bank 15 (SFRs) and the lower 128 bytes in Bank 0. These two sections will be referred to as Access RAM High and Access RAM Low, respectively. Figure 4-6 and Figure 4-7 indicate the Access RAM areas.

A bit in the instruction word specifies if the operation is to occur in the bank specified by the BSR register or in the Access Bank. This bit is denoted by the 'a' bit (for access bit).

When forced in the Access Bank (a = 0), the last address in Access RAM Low is followed by the first address in Access RAM High. Access RAM High maps the Special Function registers, so that these registers can be accessed without any software overhead. This is useful for testing status flags and modifying control bits.

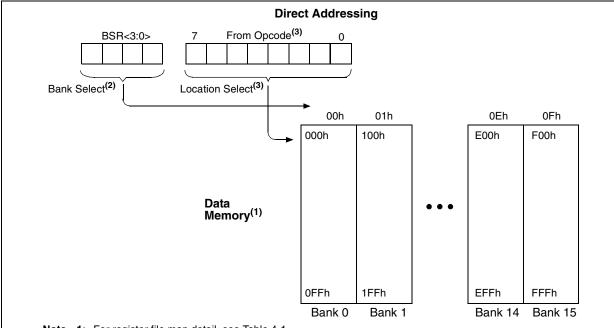

#### 4.11 Bank Select Register (BSR)

The need for a large general purpose memory space dictates a RAM banking scheme. The data memory is partitioned into sixteen banks. When using direct addressing, the BSR should be configured for the desired bank.

BSR<3:0> holds the upper 4 bits of the 12-bit RAM address. The BSR<7:4> bits will always read '0's, and writes will have no effect.

A MOVLB instruction has been provided in the instruction set to assist in selecting banks.

If the currently selected bank is not implemented, any read will return all '0's and all writes are ignored. The STATUS register bits will be set/cleared as appropriate for the instruction performed.

Each Bank extends up to FFh (256 bytes). All data memory is implemented as static RAM.

A MOVFF instruction ignores the BSR, since the 12-bit addresses are embedded into the instruction word.

Section 4.12 provides a description of indirect addressing, which allows linear addressing of the entire RAM space.

#### FIGURE 4-8: DIRECT ADDRESSING

- Note 1: For register file map detail, see Table 4-1.

- 2: The access bit of the instruction can be used to force an override of the selected bank (BSR<3:0>) to the registers of the Access Bank.

- 3: The MOVFF instruction embeds the entire 12-bit address in the instruction.

#### 4.13 STATUS Register

The STATUS register, shown in Register 4-2, contains the arithmetic status of the ALU. The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC, C, OV, or N bits, then the write to these five bits is disabled. These bits are set or cleared according to the device logic. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF, MOVFF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C, DC, OV, or N bits from the STATUS register. For other instructions not affecting any status bits, see Table 20-2.

Note: The C and DC bits operate as a borrow and digit borrow bit respectively, in subtraction.

#### REGISTER 4-2: STATUS REGISTER

| U-0   | U-0 | U-0 | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|-------|-----|-----|-------|-------|-------|-------|-------|

| _     | _   | _   | N     | OV    | Z     | DC    | С     |

| bit 7 |     |     |       |       |       |       | bit 0 |

bit 7-5 **Unimplemented:** Read as '0'

bit 4 N: Negative bit

This bit is used for signed arithmetic (2's complement). It indicates whether the result was negative (ALU MSB = 1).

- 1 = Result was negative

- 0 = Result was positive

- bit 3 **OV:** Overflow bit

This bit is used for signed arithmetic (2's complement). It indicates an overflow of the 7-bit magnitude, which causes the sign bit (bit7) to change state.

- 1 = Overflow occurred for signed arithmetic (in this arithmetic operation)

- 0 = No overflow occurred

- bit 2 Z: Zero bit

- 1 = The result of an arithmetic or logic operation is zero

- 0 = The result of an arithmetic or logic operation is not zero

- bit 1 **DC:** Digit carry/borrow bit

For ADDWF, ADDLW, SUBLW, and SUBWF instructions

- 1 = A carry-out from the 4th low order bit of the result occurred

- 0 = No carry-out from the 4th low order bit of the result

Note: For borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the bit 4 or bit 3 of the source register.

bit 0 C: Carry/borrow bit

For ADDWF, ADDLW, SUBLW, and SUBWF instructions

- 1 = A carry-out from the Most Significant bit of the result occurred

- 0 = No carry-out from the Most Significant bit of the result occurred

Note: For borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high or low order bit of the source register.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

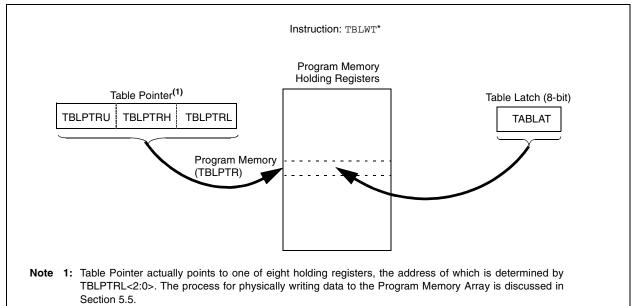

#### FIGURE 5-2: TABLE WRITE OPERATION

#### 5.2 Control Registers

Several control registers are used in conjunction with the TBLRD and TBLWT instructions. These include the:

- · EECON1 register

- EECON2 register

- TABLAT register

- · TBLPTR registers

#### 5.2.1 EECON1 AND EECON2 REGISTERS

EECON1 is the control register for memory accesses.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the memory write and erase sequences.

Control bit EEPGD determines if the access will be a program or data EEPROM memory access. When clear, any subsequent operations will operate on the data EEPROM memory. When set, any subsequent operations will operate on the program memory.

Control bit CFGS determines if the access will be to the configuration registers or to program memory/data EEPROM memory. When set, subsequent operations will operate on configuration registers, regardless of EEPGD (see "Special Features of the CPU", Section 19.0). When clear, memory selection access is determined by EEPGD.

The FREE bit, when set, will allow a program memory erase operation. When the FREE bit is set, the erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a MCLR Reset or a WDT Time-out Reset during normal operation. In these situations, the user can check the WRERR bit and rewrite the location. It is necessary to reload the data and address registers (EEDATA and EEADR), due to RESET values of zero.

Control bit WR initiates write operations. This bit cannot be cleared, only set, in software. It is cleared in hardware at the completion of the write operation. The inability to clear the WR bit in software prevents the accidental or premature termination of a write operation.

Note:

Interrupt flag bit EEIF, in the PIR2 register, is set when the write is complete. It must be cleared in software.

#### REGISTER 5-1: **EECON1 REGISTER (ADDRESS FA6h)**

| R/W-x | R/W-x | U-0 | R/W-0 | R/W-x | R/W-0 | R/S-0 | R/S-0 |

|-------|-------|-----|-------|-------|-------|-------|-------|

| EEPGD | CFGS  | _   | FREE  | WRERR | WREN  | WR    | RD    |

| bit 7 |       |     |       |       |       |       | bit 0 |

bit 0

bit 7 **EEPGD:** FLASH Program or Data EEPROM Memory Select bit

> 1 = Access FLASH Program memory 0 = Access Data EEPROM memory

bit 6 CFGS: FLASH Program/Data EE or Configuration Select bit

1 = Access Configuration registers

0 = Access FLASH Program or Data EEPROM memory

Unimplemented: Read as '0' bit 5

bit 4 FREE: FLASH Row Erase Enable bit

> 1 = Erase the program memory row addressed by TBLPTR on the next WR command (cleared by completion of erase operation)

0 = Perform write only

bit 3 WRERR: FLASH Program/Data EE Error Flag bit

> 1 = A write operation is prematurely terminated (any RESET during self-timed programming in normal operation)

0 = The write operation completed

Note: When a WRERR occurs, the EEPGD and CFGS bits are not cleared. This allows tracing of the error condition.

bit 2 WREN: FLASH Program/Data EE Write Enable bit

1 = Allows write cycles

0 = Inhibits write to the EEPROM

bit 1 WR: Write Control bit

> 1 = Initiates a data EEPROM erase/write cycle or a program memory erase cycle or write cycle. (The operation is self timed and the bit is cleared by hardware once write is complete. The WR bit can only be set (not cleared) in software.)

0 = Write cycle to the EEPROM is complete

bit 0 RD: Read Control bit

1 = Initiates an EEPROM read

(Read takes one cycle. RD is cleared in hardware. The RD bit can only be set (not cleared) in software. RD bit cannot be set when EEPGD = 1.)

0 = Does not initiate an EEPROM read

Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### 8.1 INTCON Registers

The INTCON Registers are readable and writable registers, which contain various enable, priority and flag bits.

Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

#### REGISTER 8-1: INTCON REGISTER

| R/W-0    | R/W-0     | R/W-0  | R/W-0  | R/W-0 | R/W-0  | R/W-0  | R/W-x |

|----------|-----------|--------|--------|-------|--------|--------|-------|

| GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF  |

| hit 7    |           |        |        |       |        |        | hit 0 |

Note:

bit 7 GIE/GIEH: Global Interrupt Enable bit

When IPEN = 0:

- 1 = Enables all unmasked interrupts

- 0 = Disables all interrupts

When IPEN = 1:

- 1 = Enables all high priority interrupts

- 0 = Disables all interrupts

- bit 6 PEIE/GIEL: Peripheral Interrupt Enable bit

When IPEN = 0:

- 1 = Enables all unmasked peripheral interrupts

- 0 = Disables all peripheral interrupts

When IPEN = 1:

- 1 = Enables all low priority peripheral interrupts

- 0 = Disables all low priority peripheral interrupts

- bit 5 TMR0IE: TMR0 Overflow Interrupt Enable bit

- 1 = Enables the TMR0 overflow interrupt

- 0 = Disables the TMR0 overflow interrupt

- bit 4 INTOIE: INTO External Interrupt Enable bit

- 1 = Enables the INT0 external interrupt

- 0 = Disables the INT0 external interrupt

- bit 3 RBIE: RB Port Change Interrupt Enable bit

- 1 = Enables the RB port change interrupt

- 0 = Disables the RB port change interrupt

- bit 2 TMR0IF: TMR0 Overflow Interrupt Flag bit

- 1 = TMR0 register has overflowed (must be cleared in software)

- 0 = TMR0 register did not overflow

- bit 1 INT0IF: INT0 External Interrupt Flag bit

- 1 = The INT0 external interrupt occurred (must be cleared in software)

- 0 = The INT0 external interrupt did not occur

- bit 0 RBIF: RB Port Change Interrupt Flag bit

- 1 = At least one of the RB7:RB4 pins changed state (must be cleared in software)

- 0 = None of the RB7:RB4 pins have changed state

**Note:** A mismatch condition will continue to set this bit. Reading PORTB will end the mismatch condition and allow the bit to be cleared.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 8.2 PIR Registers

The PIR registers contain the individual flag bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Flag Registers (PIR1, PIR2).

- Note 1: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

- 2: User software should ensure the appropriate interrupt flag bits are cleared prior to enabling an interrupt, and after servicing that interrupt.

#### REGISTER 8-4: PIR1: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 1

| R/W-0                | R/W-0 | R-0  | R-0  | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|----------------------|-------|------|------|-------|--------|--------|--------|

| PSPIF <sup>(1)</sup> | ADIF  | RCIF | TXIF | SSPIF | CCP1IF | TMR2IF | TMR1IF |

| bit 7                |       |      |      |       |        |        | bit 0  |

bit 7 **PSPIF**<sup>(1)</sup>: Parallel Slave Port Read/Write Interrupt Flag bit

1 = A read or a write operation has taken place (must be cleared in software)

0 = No read or write has occurred

bit 6 ADIF: A/D Converter Interrupt Flag bit

1 = An A/D conversion completed (must be cleared in software)

0 = The A/D conversion is not complete

bit 5 RCIF: USART Receive Interrupt Flag bit

1 = The USART receive buffer, RCREG, is full (cleared when RCREG is read)

0 = The USART receive buffer is empty

bit 4 TXIF: USART Transmit Interrupt Flag bit (see Section 16.0 for details on TXIF functionality)

1 = The USART transmit buffer, TXREG, is empty (cleared when TXREG is written)

0 = The USART transmit buffer is full

bit 3 SSPIF: Master Synchronous Serial Port Interrupt Flag bit

1 = The transmission/reception is complete (must be cleared in software)

0 = Waiting to transmit/receive

bit 2 CCP1IF: CCP1 Interrupt Flag bit

Capture mode:

1 = A TMR1 register capture occurred (must be cleared in software)

0 = No TMR1 register capture occurred

Compare mode:

1 = A TMR1 register compare match occurred (must be cleared in software)

0 = No TMR1 register compare match occurred

PWM mode:

Unused in this mode

bit 1 TMR2IF: TMR2 to PR2 Match Interrupt Flag bit

1 = TMR2 to PR2 match occurred (must be cleared in software)

0 = No TMR2 to PR2 match occurred

bit 0 TMR1IF: TMR1 Overflow Interrupt Flag bit

1 = TMR1 register overflowed (must be cleared in software)

0 = MR1 register did not overflow

Note 1: This bit is reserved on PIC18F2X2 devices; always maintain this bit clear.

| Legend:            |                  |                        |                    |

|--------------------|------------------|------------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

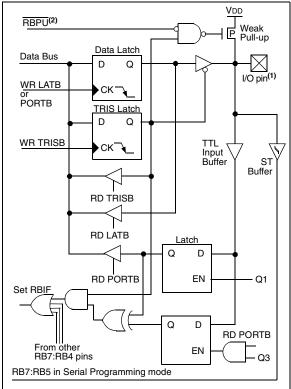

# 9.2 PORTB, TRISB and LATB Registers

PORTB is an 8-bit wide, bi-directional port. The corresponding Data Direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATB) is also memory mapped. Read-modify-write operations on the LATB register reads and writes the latched output value for PORTB.

#### **EXAMPLE 9-2: INITIALIZING PORTB**

```

CLRF

PORTB

; Initialize PORTB by

; clearing output

; data latches

CLRF

LATE

; Alternate method

; to clear output

; data latches

MOVIW OXCE

; Value used to

; initialize data

; direction

MOVWF TRISB

; Set RB<3:0> as inputs

; RB<5:4> as outputs

; RB<7:6> as inputs

```

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit  $\overline{\text{RBPU}}$  (INTCON2<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

**Note:** On a Power-on Reset, these pins are configured as digital inputs.

Four of the PORTB pins, RB7:RB4, have an interrupt-on-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupt-on-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with flag bit, RBIF (INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- Any read or write of PORTB (except with the MOVFF instruction). This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

RB3 can be configured by the configuration bit CCP2MX as the alternate peripheral pin for the CCP2 module (CCP2MX='0').

FIGURE 9-4: BLOCK DIAGRAM OF RB7:RB4 PINS

Note 1: I/O pins have diode protection to VDD and Vss.

To enable weak <u>pull-ups</u>, set the appropriate TRIS bit(s) and clear the <u>RBPU</u> bit (INTCON2<7>).

- Note 1: While in Low Voltage ICSP mode, the RB5 pin can no longer be used as a general purpose I/O pin, and should be held low during normal operation to protect against inadvertent ICSP mode entry.

- 2: When using Low Voltage ICSP programming (LVP), the pull-up on RB5 becomes disabled. If TRISB bit 5 is cleared, thereby setting RB5 as an output, LATB bit 5 must also be cleared for proper operation.

## PIC18FXX2

TABLE 9-5: PORTC FUNCTIONS

| Name            | Bit# | Buffer Type | Function                                                                                                                                  |

|-----------------|------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| RC0/T1OSO/T1CKI | bit0 | ST          | Input/output port pin or Timer1 oscillator output/Timer1 clock input.                                                                     |

| RC1/T1OSI/CCP2  | bit1 | ST          | Input/output port pin, Timer1 oscillator input, or Capture2 input/<br>Compare2 output/PWM output when CCP2MX configuration bit is<br>set. |

| RC2/CCP1        | bit2 | ST          | Input/output port pin or Capture1 input/Compare1 output/PWM1 output.                                                                      |

| RC3/SCK/SCL     | bit3 | ST          | RC3 can also be the synchronous serial clock for both SPI and I <sup>2</sup> C modes.                                                     |

| RC4/SDI/SDA     | bit4 | ST          | RC4 can also be the SPI Data In (SPI mode) or Data I/O (I <sup>2</sup> C mode).                                                           |

| RC5/SDO         | bit5 | ST          | Input/output port pin or Synchronous Serial Port data output.                                                                             |

| RC6/TX/CK       | bit6 | ST          | Input/output port pin, Addressable USART Asynchronous Transmit, or Addressable USART Synchronous Clock.                                   |

| RC7/RX/DT       | bit7 | ST          | Input/output port pin, Addressable USART Asynchronous Receive, or Addressable USART Synchronous Data.                                     |

Legend: ST = Schmitt Trigger input

TABLE 9-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Name  | Bit 7   | Bit 6                                        | Bit 5       | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |

|-------|---------|----------------------------------------------|-------------|-------|-------|-------|-------|-------|----------------------|---------------------------------|

| PORTC | RC7     | RC6                                          | RC5         | RC4   | RC3   | RC2   | RC1   | RC0   | xxxx xxxx            | uuuu uuuu                       |

| LATC  | LATC Da | ATC Data Output Register xxxx xxxx uuuu uuuu |             |       |       |       |       |       |                      |                                 |

| TRISC | PORTC I | Data Direct                                  | ion Registe | r     |       |       |       |       | 1111 1111            | 1111 1111                       |

Legend: x = unknown, u = unchanged

## PIC18FXX2

NOTES:

#### 15.4.4 CLOCK STRETCHING

Both 7- and 10-bit Slave modes implement automatic clock stretching during a transmit sequence.

The SEN bit (SSPCON2<0>) allows clock stretching to be enabled during receives. Setting SEN will cause the SCL pin to be held low at the end of each data receive sequence.

### 15.4.4.1 Clock Stretching for 7-bit Slave Receive Mode (SEN = 1)

In 7-bit Slave Receive mode, on the falling edge of the ninth clock at the end of the  $\overline{ACK}$  sequence, if the BF bit is set, the CKP bit in the SSPCON1 register is automatically cleared, forcing the SCL output to be held low. The CKP being cleared to '0' will assert the SCL line low. The CKP bit must be set in the user's ISR before reception is allowed to continue. By holding the SCL line low, the user has time to service the ISR and read the contents of the SSPBUF before the master device can initiate another receive sequence. This will prevent buffer overruns from occurring (see Figure 15-13).

- Note 1: If the user reads the contents of the SSPBUF before the falling edge of the ninth clock, thus clearing the BF bit, the CKP bit will not be cleared and clock stretching will not occur.

- 2: The CKP bit can be set in software, regardless of the state of the BF bit. The user should be careful to clear the BF bit in the ISR before the next receive sequence, in order to prevent an overflow condition.

#### 15.4.4.2 Clock Stretching for 10-bit Slave Receive Mode (SEN = 1)

In 10-bit Slave Receive mode, during the address sequence, clock stretching automatically takes place but CKP is not cleared. During this time, if the UA bit is set after the ninth clock, clock stretching is initiated. The UA bit is set after receiving the upper byte of the 10-bit address, and following the receive of the second byte of the 10-bit address with the R/W bit cleared to '0'. The release of the clock line occurs upon updating SSPADD. Clock stretching will occur on each data receive sequence as described in 7-bit mode.

Note: If the user polls the UA bit and clears it by updating the SSPADD register before the falling edge of the ninth clock occurs, and if the user hasn't cleared the BF bit by reading the SSPBUF register before that time, then the CKP bit will still NOT be asserted low. Clock stretching on the basis of the state of the BF bit only occurs during a data sequence, not an address sequence.

#### 15.4.4.3 Clock Stretching for 7-bit Slave Transmit Mode

7-bit Slave Transmit mode implements clock stretching by clearing the CKP bit after the falling edge of the ninth clock, if the BF bit is clear. This occurs, regardless of the state of the SEN bit.

The user's ISR must set the CKP bit before transmission is allowed to continue. By holding the SCL line low, the user has time to service the ISR and load the contents of the SSPBUF before the master device can initiate another transmit sequence (see Figure 15-9).

- Note 1: If the user loads the contents of SSPBUF, setting the BF bit before the falling edge of the ninth clock, the CKP bit will not be cleared and clock stretching will not occur.

- **2:** The CKP bit can be set in software, regardless of the state of the BF bit.

#### 15.4.4.4 Clock Stretching for 10-bit Slave Transmit Mode

In 10-bit Slave Transmit mode, clock stretching is controlled during the first two address sequences by the state of the UA bit, just as it is in 10-bit Slave Receive mode. The first two addresses are followed by a third address sequence, which contains the high order bits of the 10-bit address and the R/W bit set to '1'. After the third address sequence is performed, the UA bit is not set, the module is now configured in Transmit mode, and clock stretching is controlled by the BF flag, as in 7-bit Slave Transmit mode (see Figure 15-11).

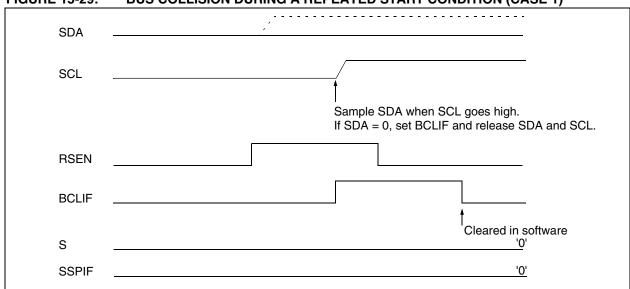

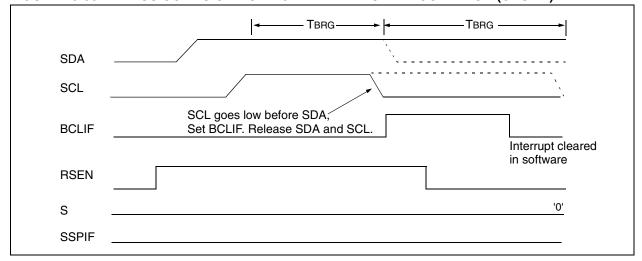

### 15.4.17.2 Bus Collision During a Repeated START Condition

During a Repeated START condition, a bus collision occurs if:

- A low level is sampled on SDA when SCL goes from low level to high level.

- SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user de-asserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0> and counts down to 0. The SCL pin is then de-asserted, and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 15-29). If SDA is sampled high, the BRG is

reloaded and begins counting. If SDA goes from high to low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high to low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated START condition, Figure 15-30.

If, at the end of the BRG time-out both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated START condition is complete.

FIGURE 15-29: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

FIGURE 15-30: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

#### **REGISTER 17-2: ADCON1 REGISTER**

| R/W-0 | R/W-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-----|-----|-------|-------|-------|-------|

| ADFM  | ADCS2 | _   | _   | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| bit 7 |       |     |     |       |       |       | bit 0 |

bit 7 ADFM: A/D Result Format Select bit

1 = Right justified. Six (6) Most Significant bits of ADRESH are read as '0'.

0 = Left justified. Six (6) Least Significant bits of ADRESL are read as '0'.

bit 6 ADCS2: A/D Conversion Clock Select bit (ADCON1 bits in bold)

| ADCON1<br><adcs2></adcs2> | ADCON0<br><adcs1:adcs0></adcs1:adcs0> | Clock Conversion                                        |

|---------------------------|---------------------------------------|---------------------------------------------------------|

| 0                         | 00                                    | Fosc/2                                                  |

| 0                         | 01                                    | Fosc/8                                                  |

| 0                         | 10                                    | Fosc/32                                                 |

| 0                         | 11                                    | FRC (clock derived from the internal A/D RC oscillator) |

| 1                         | 00                                    | Fosc/4                                                  |

| 1                         | 01                                    | Fosc/16                                                 |

| 1                         | 10                                    | Fosc/64                                                 |

| 1                         | 11                                    | FRC (clock derived from the internal A/D RC oscillator) |

bit 5-4 Unimplemented: Read as '0'

bit 3-0 PCFG3:PCFG0: A/D Port Configuration Control bits

| PCFG<br><3:0> | AN7 | AN6 | AN5 | AN4 | AN3   | AN2   | AN1 | AN0 | VREF+ | VREF- | C/R   |

|---------------|-----|-----|-----|-----|-------|-------|-----|-----|-------|-------|-------|

| 0000          | Α   | Α   | Α   | Α   | Α     | Α     | Α   | Α   | VDD   | Vss   | 8/0   |

| 0001          | Α   | Α   | Α   | Α   | VREF+ | Α     | Α   | Α   | AN3   | Vss   | 7/1   |

| 0010          | D   | D   | D   | Α   | Α     | Α     | Α   | Α   | VDD   | Vss   | 5/0   |

| 0011          | D   | D   | D   | Α   | VREF+ | Α     | Α   | Α   | AN3   | Vss   | 4 / 1 |

| 0100          | D   | D   | D   | D   | Α     | D     | Α   | Α   | VDD   | Vss   | 3/0   |

| 0101          | D   | D   | D   | D   | VREF+ | D     | Α   | Α   | AN3   | Vss   | 2/1   |

| 011x          | D   | D   | D   | D   | D     | D     | D   | D   | _     | _     | 0/0   |

| 1000          | Α   | Α   | Α   | Α   | VREF+ | VREF- | Α   | Α   | AN3   | AN2   | 6/2   |

| 1001          | D   | D   | Α   | Α   | Α     | Α     | Α   | Α   | VDD   | Vss   | 6/0   |

| 1010          | D   | D   | Α   | Α   | VREF+ | Α     | Α   | Α   | AN3   | Vss   | 5/1   |

| 1011          | D   | D   | Α   | Α   | VREF+ | VREF- | Α   | Α   | AN3   | AN2   | 4/2   |

| 1100          | D   | D   | D   | Α   | VREF+ | VREF- | Α   | Α   | AN3   | AN2   | 3/2   |

| 1101          | D   | D   | D   | D   | VREF+ | VREF- | Α   | Α   | AN3   | AN2   | 2/2   |

| 1110          | D   | D   | D   | D   | D     | D     | D   | Α   | VDD   | Vss   | 1/0   |

| 1111          | D   | D   | D   | D   | VREF+ | VREF- | D   | Α   | AN3   | AN2   | 1/2   |

A = Analog input D = Digital I/O

C/R = # of analog input channels / # of A/D voltage references

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

**Note:** On any device RESET, the port pins that are multiplexed with analog functions (ANx) are forced to be an analog input.

### 19.4.2 DATA EEPROM CODE PROTECTION

The entire Data EEPROM is protected from external reads and writes by two bits: CPD and WRTD. CPD inhibits external reads and writes of Data EEPROM. WRTD inhibits external writes to Data EEPROM. The CPU can continue to read and write Data EEPROM regardless of the protection bit settings.

### 19.4.3 CONFIGURATION REGISTER PROTECTION

The configuration registers can be write protected. The WRTC bit controls protection of the configuration registers. In User mode, the WRTC bit is readable only. WRTC can only be written via ICSP or an external programmer.

#### 19.5 ID Locations

Eight memory locations (200000h - 200007h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are accessible during normal execution through the TBLRD and TBLWT instructions, or during program/verify. The ID locations can be read when the device is code protected.

The sequence for programming the ID locations is similar to programming the FLASH memory (see Section 5.5.1).

#### 19.6 In-Circuit Serial Programming

PIC18FXXX microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

#### 19.7 In-Circuit Debugger

When the DEBUG bit in configuration register CONFIG4L is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB® IDE. When the microcontroller has this feature enabled, some of the resources are not available for general use. Table 19-4 shows which features are consumed by the background debugger.

TABLE 19-4: DEBUGGER RESOURCES

| I/O pins       | RB6, RB7  |

|----------------|-----------|

| Stack          | 2 levels  |

| Program Memory | 512 bytes |

| Data Memory    | 10 bytes  |

To use the In-Circuit Debugger function of the microcontroller, the design must implement In-Circuit Serial Programming connections to MCLR/VPP, VDD, GND, RB7 and RB6. This will interface to the In-Circuit Debugger module available from Microchip or one of the third party development tool companies.

#### 19.8 Low Voltage ICSP Programming

The LVP bit configuration register CONFIG4L enables low voltage ICSP programming. This mode allows the microcontroller to be programmed via ICSP using a VDD source in the operating voltage range. This only means that VPP does not have to be brought to VIHH, but can instead be left at the normal operating voltage. In this mode, the RB5/PGM pin is dedicated to the programming function and ceases to be a general purpose I/O pin. During programming, VDD is applied to the MCLR/VPP pin. To enter Programming mode, VDD must be applied to the RB5/PGM, provided the LVP bit is set. The LVP bit defaults to a ('1') from the factory.

- Note 1: The High Voltage Programming mode is always available, regardless of the state of the LVP bit, by applying VIHH to the MCLR pin.

- 2: While in low voltage ICSP mode, the RB5 pin can no longer be used as a general purpose I/O pin, and should be held low during normal operation to protect against inadvertent ICSP mode entry.

- **3:** When using low voltage ICSP programming (LVP), the pull-up on RB5 becomes disabled. If TRISB bit 5 is cleared, thereby setting RB5 as an output, LATB bit 5 must also be cleared for proper operation.

If Low Voltage Programming mode is not used, the LVP bit can be programmed to a '0' and RB5/PGM becomes a digital I/O pin. However, the LVP bit may only be programmed when programming is entered with VIHH on MCLR/VPP.

It should be noted that once the LVP bit is programmed to 0, only the High Voltage Programming mode is available and only High Voltage Programming mode can be used to program the device.

When using low voltage ICSP, the part must be supplied 4.5V to 5.5V, if a bulk erase will be executed. This includes reprogramming of the code protect bits from an on-state to off-state. For all other cases of low voltage ICSP, the part may be programmed at the normal operating voltage. This means unique user IDs, or user code can be reprogrammed or added.

RETURN **Return from Subroutine** Syntax: [label] RETURN [s] Operands:  $s\in \left[ 0,1\right]$ Operation:  $(TOS) \rightarrow PC$ , if s = 1 $(WS) \rightarrow W$ ,  $(STATUSS) \rightarrow STATUS,$  $(BSRS) \rightarrow BSR$ , PCLATU, PCLATH are unchanged Status Affected: None Encoding: 0000 0000 0001 001s Description: Return from subroutine. The stack is popped and the top of the stack

is popped and the top of the stack (TOS) is loaded into the program counter. If 's'= 1, the contents of the shadow registers WS, STATUSS and BSRS are loaded into their corresponding registers, W, STATUS and BSR. If 's' = 0, no update of these registers occurs (default).

Words: 1 Cycles: 2

Q Cycle Activity:

| Q1           | Q2              | Q3              | Q4                   |

|--------------|-----------------|-----------------|----------------------|

| Decode       | No<br>operation | Process<br>Data | pop PC from<br>stack |

| No operation | No<br>operation | No<br>operation | No operation         |

Example: RETURN

After Interrupt PC = TOS

| RLC               | F            | Rotate L                                                                                                         | Rotate Left f through Carry                                                                      |                                                                                               |                                                      |  |  |

|-------------------|--------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------|--|--|

| Synt              | ax:          | [ label ]                                                                                                        | RLCF                                                                                             | f [,d [,a                                                                                     | ]                                                    |  |  |

| Ope               | rands:       | $0 \le f \le 25$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                               | 55                                                                                               |                                                                                               |                                                      |  |  |

| Operation:        |              | (f<7>) →                                                                                                         | $(f) \rightarrow dest,  (f<7>) \rightarrow C,  (C) \rightarrow dest<0>$                          |                                                                                               |                                                      |  |  |

| Statu             | us Affected: | C, N, Z                                                                                                          |                                                                                                  |                                                                                               |                                                      |  |  |

| Enco              | oding:       | 0011                                                                                                             | 01da                                                                                             | ffff                                                                                          | ffff                                                 |  |  |

| Description:      |              | rotated of<br>the Carry<br>is placed<br>is stored<br>(default).<br>Bank will<br>the BSR<br>bank will<br>BSR valu | Flag. If 'in W. If 'back in r<br>If 'a' is 0<br>be select<br>value. If<br>be select<br>ie (defau | d' is 0, tl<br>d' is 1, th<br>egister 'f<br>, the Acc<br>ted, ove<br>'a' = 1, tl<br>ted as po | ne result<br>ne result<br>cess<br>rriding<br>nen the |  |  |

| Wor               | ds:          | 1                                                                                                                |                                                                                                  |                                                                                               |                                                      |  |  |

| Cycles:           |              | 1                                                                                                                |                                                                                                  |                                                                                               |                                                      |  |  |

| Q Cycle Activity: |              |                                                                                                                  |                                                                                                  |                                                                                               |                                                      |  |  |

|                   | Q1           | Q2                                                                                                               | Q3                                                                                               |                                                                                               | Q4                                                   |  |  |

|                   | Decode       | Read<br>register 'f'                                                                                             | Proces<br>Data                                                                                   | -                                                                                             | rite to<br>tination                                  |  |  |

Example: RLCF REG, 0, 0

Before Instruction

REG = 1110 0110 C = 0

After Instruction

REG = 1110 0110 W = 1100 1100 C - 1

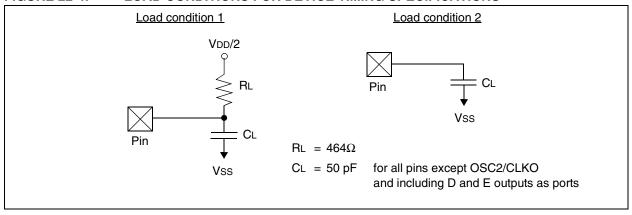

#### 22.3.2 TIMING CONDITIONS

The temperature and voltages specified in Table 22-3 apply to all timing specifications unless otherwise noted. Figure 22-4 specifies the load conditions for the timing specifications.

#### TABLE 22-3: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

Standard Operating Conditions (unless otherwise stated)

Operating temperature -40°C ≤ TA ≤ +85°C for industrial

-40°C ≤ TA ≤ +125°C for extended

Operating voltage VDD range as described in DC spec Section 22.1 and Section 22.2.

LC parts operate for industrial temperatures only.

#### FIGURE 22-4: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

### TABLE 22-16: I<sup>2</sup>C BUS DATA REQUIREMENTS (SLAVE MODE)

| Param.<br>No. | Symbol  | Characteristic             |              | Min         | Max  | Units | Conditions                                     |

|---------------|---------|----------------------------|--------------|-------------|------|-------|------------------------------------------------|

| 100           | THIGH   | Clock high time            | 100 kHz mode | 4.0         | _    | μs    | PIC18FXXX must operate at a minimum of 1.5 MHz |

|               |         |                            | 400 kHz mode | 0.6         | _    | μs    | PIC18FXXX must operate at a minimum of 10 MHz  |

|               |         |                            | SSP Module   | 1.5 TcY     | _    |       |                                                |

| 101           | TLOW    | Clock low time             | 100 kHz mode | 4.7         | _    | μs    | PIC18FXXX must operate at a minimum of 1.5 MHz |

|               |         |                            | 400 kHz mode | 1.3         | _    | μs    | PIC18FXXX must operate at a minimum of 10 MHz  |

|               |         |                            | SSP Module   | 1.5 Tcy     |      |       |                                                |

| 102           | TR      | SDA and SCL rise           | 100 kHz mode | _           | 1000 | ns    |                                                |

|               |         | time                       | 400 kHz mode | 20 + 0.1 CB | 300  | ns    | CB is specified to be from 10 to 400 pF        |

| 103 TF        | TF      | SDA and SCL fall time      | 100 kHz mode | _           | 1000 | ns    | VDD ≥ 4.2V                                     |

|               |         |                            | 400 kHz mode | 20 + 0.1 CB | 300  | ns    | VDD ≥ 4.2V                                     |

| 90 Tsu:sta    | Tsu:sta | START condition setup time | 100 kHz mode | 4.7         | _    | μs    | Only relevant for Repeated                     |

|               |         |                            | 400 kHz mode | 0.6         | _    | μs    | START condition                                |

| 91            | THD:STA | START condition hold       | 100 kHz mode | 4.0         | _    | μs    | After this period, the first clock             |

|               |         | time                       | 400 kHz mode | 0.6         | _    | μs    | pulse is generated                             |

| 106           | THD:DAT | Data input hold time       | 100 kHz mode | 0           | _    | ns    |                                                |

|               |         |                            | 400 kHz mode | 0           | 0.9  | μs    |                                                |

| 107           | TSU:DAT | Data input setup time      | 100 kHz mode | 250         | _    | ns    | (Note 2)                                       |

|               |         |                            | 400 kHz mode | 100         | _    | ns    |                                                |

| 92            | Tsu:sto | STOP condition             | 100 kHz mode | 4.7         | _    | μs    |                                                |

|               |         | setup time                 | 400 kHz mode | 0.6         | _    | μs    |                                                |

| 109           | TAA     | Output valid from          | 100 kHz mode | _           | 3500 | ns    | (Note 1)                                       |

|               |         | clock                      | 400 kHz mode | _           | _    | ns    |                                                |

| 110           | TBUF    | Bus free time              | 100 kHz mode | 4.7         | _    | μs    | Time the bus must be free                      |

|               |         |                            | 400 kHz mode | 1.3         | _    | μs    | before a new transmission can start            |

| D102          | Св      | Bus capacitive loading     |              | _           | 400  | pF    |                                                |

Note 1: As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

<sup>2:</sup> A Fast mode I<sup>2</sup>C bus device can be used in a Standard mode I<sup>2</sup>C bus system, but the requirement Tsu:DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line.

TR max. + Tsu:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification) before the SCL line is released.

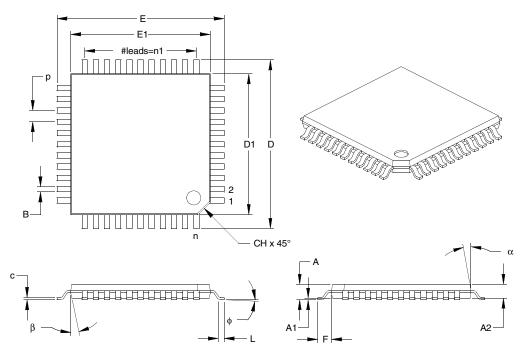

#### 44-Lead Plastic Thin Quad Flatpack (PT) 10x10x1 mm Body, 1.0/0.10 mm Lead Form (TQFP)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          |     | INCHES |           | MILLIMETERS* |           |       |       |

|--------------------------|-----|--------|-----------|--------------|-----------|-------|-------|

| Dimension Lim            | MIN | NOM    | MAX       | MIN          | NOM       | MAX   |       |

| Number of Pins           | n   |        | 44        |              |           | 44    |       |

| Pitch                    | р   |        | .031      |              |           | 0.80  |       |

| Pins per Side            | n1  |        | 11        |              |           | 1     | 1     |

| Overall Height           | Α   | .039   | .043      | .047         | 1.00      | 1.10  | 1.20  |

| Molded Package Thickness | A2  | .037   | .039      | .041         | 0.95      | 1.00  | 1.05  |

| Standoff                 | A1  | .002   | .004      | .006         | 0.05      | 0.10  | 0.15  |

| Foot Length              | L   | .018   | .024      | .030         | 0.45      | 0.60  | 0.75  |

| Footprint (Reference)    | F   |        | .039 REF. |              | 1.00 REF. |       |       |

| Foot Angle               | ф   | 0      | 3.5       | 7            | 0         | 3.5   | 7     |

| Overall Width            | Е   | .463   | .472      | .482         | 11.75     | 12.00 | 12.25 |

| Overall Length           | D   | .463   | .472      | .482         | 11.75     | 12.00 | 12.25 |

| Molded Package Width     | E1  | .390   | .394      | .398         | 9.90      | 10.00 | 10.10 |

| Molded Package Length    | D1  | .390   | .394      | .398         | 9.90      | 10.00 | 10.10 |

| Lead Thickness           | С   | .004   | .006      | .008         | 0.09      | 0.15  | 0.20  |

| Lead Width               | В   | .012   | .015      | .017         | 0.30      | 0.38  | 0.44  |

| Pin 1 Corner Chamfer     | CH  | .025   | .035      | .045         | 0.64      | 0.89  | 1.14  |

| Mold Draft Angle Top     | α   | 5      | 10        | 15           | 5         | 10    | 15    |

| Mold Draft Angle Bottom  | β   | 5      | 10        | 15           | 5         | 10    | 15    |

<sup>\*</sup> Controlling Parameter

#### Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. REF: Reference Dimension, usually without tolerance, for information purposes only.

See ASME Y14.5M JEDEC Equivalent: MS-026 Drawing No. C04-076

Revised 07-22-05

## PIC18FXX2

NOTES:

#### **INDEX**

| A                                             |     | Block Diagrams                        |     |

|-----------------------------------------------|-----|---------------------------------------|-----|

| A/D                                           | 181 | A/D Converter                         |     |

| A/D Converter Flag (ADIF Bit)                 |     | Analog Input Model                    |     |

| A/D Converter Interrupt, Configuring          |     | Baud Rate Generator                   | 151 |

| Acquisition Requirements                      |     | Capture Mode Operation                |     |

| ADCON0 Register                               |     | Compare Mode Operation                | 120 |

| ADCON1 Register                               |     | Low Voltage Detect                    |     |

| ADRESH Register                               |     | External Reference Source             | 190 |

| ADRESH/ADRESL Registers                       |     | Internal Reference Source             | 190 |

|                                               |     | MSSP                                  |     |

| Applea Bort Bins                              |     | I <sup>2</sup> C Mode                 | 134 |

| Analog Port Pins                              |     | MSSP (SPI Mode)                       |     |

| Analog Port Pins, Configuring                 |     | On-Chip Reset Circuit                 | 25  |

| Associated Registers                          |     | Parallel Slave Port (PORTD and PORTE) |     |

| Configuring the Module                        |     | PIC18F2X2                             |     |

| Conversion Clock (TAD)                        |     | PIC18F4X2                             |     |

| Conversion Status (GO/DONE Bit)               |     | PLL                                   |     |

| Conversions                                   |     | PORTC (Peripheral Output Override)    |     |

| Converter Characteristics                     | 287 | PORTD (I/O Mode)                      |     |

| Equations                                     |     | PORTE (I/O Mode)                      |     |

| Acquisition Time                              | 185 |                                       |     |

| Minimum Charging Time                         | 185 | PWM Operation (Simplified)            |     |

| Examples                                      |     | RA3:RA0 and RA5 Port Pins             | _   |

| Calculating the Minimum Required              |     | RA4/T0CKI Pin                         |     |

| Acquisition Time                              | 185 | RA6 Pin                               |     |

| Result Registers                              |     | RB2:RB0 Port Pins                     |     |

| Special Event Trigger (CCP)                   |     | RB3 Pin                               |     |

| TAD vs. Device Operating Frequencies          |     | RB7:RB4 Port Pins                     |     |

| Use of the CCP2 Trigger                       |     | Table Read Operation                  | 55  |

| Absolute Maximum Ratings                      |     | Table Write Operation                 | 56  |

| AC (Timing) Characteristics                   |     | Table Writes to FLASH Program Memory  | 61  |

| Load Conditions for Device Timing             | 200 | Timer0 in 16-bit Mode                 | 104 |

| Specifications                                | 270 | Timer0 in 8-bit Mode                  | 104 |

| Parameter Symbology                           |     | Timer1                                | 108 |

| • ••                                          |     | Timer1 (16-bit R/W Mode)              | 108 |

| Temperature and Voltage Specifications - AC . |     | Timer2                                | 112 |

| Timing Conditions                             |     | Timer3                                | 114 |

| ACKSTAT Status Flag                           |     | Timer3 (16-bit R/W Mode)              |     |

| ADCON0 Register                               |     | USART                                 |     |

| GO/DONE Bit                                   |     | Asynchronous Receive                  | 174 |

| ADCON1 Register                               |     | Asynchronous Transmit                 |     |

| ADDLW                                         |     | Watchdog Timer                        |     |

| ADDWF                                         |     | BN                                    |     |

| ADDWFC                                        |     | BNC                                   |     |

| ADRESH Register                               |     | BNN                                   |     |

| ADRESH/ADRESL Registers                       |     |                                       |     |

| ADRESL Register                               | 181 | BNOV                                  |     |

| Analog-to-Digital Converter. See A/D          |     | BNZ                                   | 222 |

| ANDLW                                         | 218 | BOR. See Brown-out Reset              |     |

| ANDWF                                         | 219 | BOV                                   | _   |

| Assembler                                     |     | BRA                                   | 223 |

| MPASM Assembler                               | 253 | BRG. See Baud Rate Generator          |     |

| _                                             |     | Brown-out Reset (BOR)                 |     |

| В                                             |     | BSF                                   | 223 |

| Baud Rate Generator                           | 151 | BTFSC                                 | 224 |

| BC                                            |     | BTFSS                                 | 224 |

| BCF                                           | -   | BTG                                   | 225 |

| BF Status Flag                                |     | Bus Collision During a STOP Condition | 163 |

|                                               |     | BZ                                    | 226 |

|                                               |     |                                       |     |

## PIC18FXX2

| Example SPI Master Mode (CKE = 0)278                        | USART Synchronous Transmission                  |                 |

|-------------------------------------------------------------|-------------------------------------------------|-----------------|

| Example SPI Master Mode (CKE = 1)279                        | (Through TXEN)                                  | 177             |

| Example SPI Slave Mode (CKE = 0)280                         | Wake-up from SLEEP via Interrupt                | 206             |

| Example SPI Slave Mode (CKE = 1)281                         | Timing Diagrams Requirements                    |                 |

| External Clock (All Modes except PLL)271                    | Master SSP I <sup>2</sup> C Bus START/STOP Bits | 284             |

| First START Bit Timing153                                   | Timing Requirements                             |                 |

| I <sup>2</sup> C Bus Data282                                | A/D Conversion                                  | 288             |

| I <sup>2</sup> C Bus START/STOP Bits282                     | Capture/Compare/PWM (CCP1 and CCP2)             | 270             |

| I <sup>2</sup> C Master Mode (Reception, 7-bit Address) 157 | CLKO and I/O                                    |                 |

| I <sup>2</sup> C Master Mode (Transmission,                 | Example SPI Mode (Master Mode, CKE = 0)         | 278             |

| 7 or 10-bit Address)156                                     | Example SPI Mode (Master Mode, CKE = 1)         | 279             |

| I <sup>2</sup> C Slave Mode Timing (10-bit Reception,       | Example SPI Mode (Slave Mode, CKE = 0)          | 280             |

| SEN = 0)142                                                 | Example SPI Slave Mode (CKE = 1)                | 28 <sup>-</sup> |

| I <sup>2</sup> C Slave Mode Timing (10-bit Transmission)143 | External Clock                                  | 27              |

| I <sup>2</sup> C Slave Mode Timing (7-bit Reception,        | I <sup>2</sup> C Bus Data (Slave Mode)          |                 |

| SEN = 0)140                                                 | Master SSP I <sup>2</sup> C Bus Data            |                 |

| I <sup>2</sup> C Slave Mode Timing (7-bit Reception,        | Parallel Slave Port (PIC18F4X2)                 | 27              |

| SEN = 1)146, 147                                            | RESET, Watchdog Timer, Oscillator Start-up      |                 |

| I <sup>2</sup> C Slave Mode Timing (7-bit Transmission)141  | Timer, Power-up Timer and                       |                 |

| Low Voltage Detect192                                       | Brown-out Reset Requirements                    | 274             |

| Master SSP I <sup>2</sup> C Bus Data284                     | Timer0 and Timer1 External Clock                | 27              |

| Master SSP I <sup>2</sup> C Bus START/STOP Bits284          | USART Synchronous Receive                       | 286             |

| Parallel Slave Port (PIC18F4X2)277                          | USART Synchronous Transmission                  | 286             |

| Parallel Slave Port (Read)101                               | Timing Specifications                           |                 |

| Parallel Slave Port (Write)100                              | PLL Clock                                       | 272             |

| PWM Output122                                               | TRISE Register                                  |                 |

| Repeat START Condition154                                   | PSPMODE Bit                                     | 95, 100         |

| RESET, Watchdog Timer (WDT),                                | TSTFSZ                                          | 25              |

| Oscillator Start-up Timer (OST) and                         | Two-Word Instructions                           |                 |

| Power-up Timer (PWRT)273                                    | Example Cases                                   | 4 <sup>-</sup>  |

| Slave Synchronization131                                    | TXSTA Register                                  |                 |

| Slaver Mode General Call Address Sequence                   | BRGH Bit                                        | 168             |

| (7 or 10-bit <u>Addres</u> s Mode)148                       | U                                               |                 |

| Slow Rise Time (MCLR Tied to VDD)                           |                                                 |                 |

| SPI Mode (Master Mode)                                      | Universal Synchronous Asynchronous              |                 |

| SPI Mode (Slave Mode with CKE = 0)                          | Receiver Transmitter. See USART                 | 101             |

| SPI Mode (Slave Mode with CKE = 1)                          | USART                                           |                 |

| Stop Condition Receive or Transmit Mode                     | Asynchronous Mode                               |                 |

| Time-out Sequence on POR w/PLL Enabled                      | Associated Registers, Receive                   |                 |

| (MCLR Tied to VDD)                                          | Receiver                                        |                 |

| Time-out Sequence on Power-up (MCLR Not Tied to VDD)        | Transmitter                                     |                 |

| Case 1                                                      | Baud Rate Generator (BRG)                       |                 |

| Case 2                                                      | Associated Registers                            |                 |

| Time-out Sequence on Power-up                               | Baud Rate Error, Calculating                    |                 |

| (MCLR Tied to VDD)32                                        | Baud Rate Formula                               |                 |

| Timer0 and Timer1 External Clock                            | Baud Rates for Asynchronous Mode                |                 |

| Timing for Transition Between Timer1 and                    | (BRGH = 0)                                      | 170             |

| OSC1 (HS with PLL)23                                        | Baud Rates for Asynchronous Mode                |                 |

| Transition Between Timer1 and OSC1                          | (BRGH = 1)                                      | 17              |

| (HS, XT, LP)22                                              | Baud Rates for Synchronous Mode                 |                 |

| Transition Between Timer1 and OSC1                          | High Baud Rate Select (BRGH Bit)                |                 |

| (RC, EC)23                                                  | Sampling                                        |                 |

| Transition from OSC1 to Timer1 Oscillator                   | Serial Port Enable (SPEN Bit)                   |                 |

| USART Asynchronous Master Transmission                      | Synchronous Master Mode                         |                 |

| USART Asynchronous Master Transmission                      | Associated Registers, Reception                 |                 |

| (Back to Back)173                                           | Associated Registers, Transmit                  |                 |

| USART Asynchronous Reception175                             | Reception                                       |                 |

| USART Synchronous Receive (Master/Slave)286                 | Transmission                                    |                 |

| USART Synchronous Reception                                 | Synchronous Slave Mode                          |                 |

| (Master Mode, SREN)178                                      | Associated Registers, Receive                   |                 |

| USART Synchronous Transmission 177                          | Associated Registers, Transmit                  |                 |

| USART Synchronous Transmission                              | Reception                                       |                 |

| (Master/Slave)286                                           | Transmission                                    |                 |

|                                                             |                                                 |                 |