Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 40MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                              |

| Number of I/O              | 34                                                                      |

| Program Memory Size        | 32KB (16K x 16)                                                         |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 256 x 8                                                                 |

| RAM Size                   | 1.5K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                             |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-LCC (J-Lead)                                                         |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f452-e-l |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

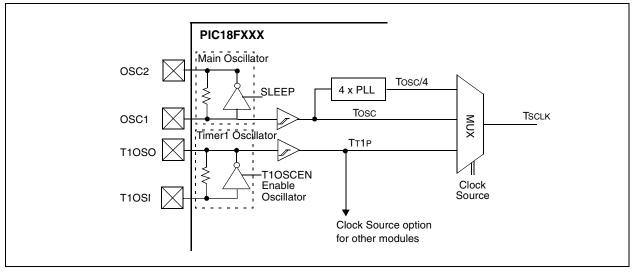

# 2.6 Oscillator Switching Feature

The PIC18FXX2 devices include a feature that allows the system clock source to be switched from the main oscillator to an alternate low frequency clock source. For the PIC18FXX2 devices, this alternate clock source is the Timer1 oscillator. If a low frequency crystal (32 kHz, for example) has been attached to the Timer1 oscillator pins and the Timer1 oscillator has been enabled, the device can switch to a Low Power Execution mode. Figure 2-7 shows a block diagram of the system clock sources. The clock switching feature is enabled <u>by programming the Oscillator Switching</u> Enable (OSCSEN) bit in Configuration Register1H to a '0'. Clock switching is disabled in an erased device. See Section 11.0 for further details of the Timer1 oscillator. See Section 19.0 for Configuration Register details.

## FIGURE 2-7: DEVICE CLOCK SOURCES

| File Name | Bit 7       | Bit 6                         | Bit 5                     | Bit 4           | Bit 3         | Bit 2          | Bit 1                   | Bit 0   | Value on POR, BOR | Details<br>on page: |

|-----------|-------------|-------------------------------|---------------------------|-----------------|---------------|----------------|-------------------------|---------|-------------------|---------------------|

| OSCCON    | —           | —                             | —                         | —               | —             | —              | —                       | SCS     | 0                 | 21                  |

| LVDCON    | _           | —                             | IRVST                     | LVDEN           | LVDL3         | LVDL2          | LVDL1                   | LVDL0   | 00 0101           | 191                 |

| WDTCON    | _           | —                             | —                         | —               | _             | —              | —                       | SWDTE   | 0                 | 203                 |

| RCON      | IPEN        | _                             | _                         | RI              | TO            | PD             | POR                     | BOR     | 01 11qq           | 53, 28, 84          |

| TMR1H     | Timer1 Reg  | ister High Byt                | e                         | •               |               | •              | •                       |         | xxxx xxxx         | 107                 |

| TMR1L     | Timer1 Reg  | ister Low Byte                | Э                         |                 |               |                |                         |         | xxxx xxxx         | 107                 |

| T1CON     | RD16        |                               | T1CKPS1                   | T1CKPS0         | T1OSCEN       | T1SYNC         | TMR1CS                  | TMR10N  | 0-00 0000         | 107                 |

| TMR2      | Timer2 Reg  | ister                         |                           |                 |               |                |                         |         | 0000 0000         | 111                 |

| PR2       | Timer2 Peri | od Register                   |                           |                 |               |                |                         |         | 1111 1111         | 112                 |

| T2CON     | _           | TOUTPS3                       | TOUTPS2                   | TOUTPS1         | TOUTPS0       | TMR2ON         | T2CKPS1                 | T2CKPS0 | -000 0000         | 111                 |

| SSPBUF    | SSP Receiv  | e Buffer/Tran                 | smit Register             | ſ               |               | •              | •                       |         | xxxx xxxx         | 125                 |

| SSPADD    | SSP Addres  | ss Register in                | I <sup>2</sup> C Slave me | ode. SSP Bau    | ud Rate Reloa | ad Register ir | I <sup>2</sup> C Master | mode.   | 0000 0000         | 134                 |

| SSPSTAT   | SMP         | CKE                           | D/A                       | Р               | S             | R/W            | UA                      | BF      | 0000 0000         | 126                 |

| SSPCON1   | WCOL        | SSPOV                         | SSPEN                     | CKP             | SSPM3         | SSPM2          | SSPM1                   | SSPM0   | 0000 0000         | 127                 |

| SSPCON2   | GCEN        | ACKSTAT                       | ACKDT                     | ACKEN           | RCEN          | PEN            | RSEN                    | SEN     | 0000 0000         | 137                 |

| ADRESH    | A/D Result  | A/D Result Register High Byte |                           |                 |               |                |                         |         |                   | 187,188             |

| ADRESL    | A/D Result  | Register Low                  | Byte                      |                 |               |                |                         |         | xxxx xxxx         | 187,188             |

| ADCON0    | ADCS1       | ADCS0                         | CHS2                      | CHS1            | CHS0          | GO/DONE        |                         | ADON    | 0000 00-0         | 181                 |

| ADCON1    | ADFM        | ADCS2                         | —                         | —               | PCFG3         | PCFG2          | PCFG1                   | PCFG0   | 00 0000           | 182                 |

| CCPR1H    | Capture/Co  | mpare/PWM                     | Register1 Hig             | h Byte          |               | •              | •                       |         | xxxx xxxx         | 121, 123            |

| CCPR1L    | Capture/Co  | mpare/PWM                     | Register1 Lov             | w Byte          |               |                |                         |         | xxxx xxxx         | 121, 123            |

| CCP1CON   |             |                               | DC1B1                     | DC1B0           | CCP1M3        | CCP1M2         | CCP1M1                  | CCP1M0  | 00 0000           | 117                 |

| CCPR2H    | Capture/Co  | mpare/PWM                     | Register2 Hig             | gh Byte         |               | •              | •                       |         | xxxx xxxx         | 121, 123            |

| CCPR2L    | Capture/Co  | mpare/PWM                     | Register2 Lov             | w Byte          |               |                |                         |         | xxxx xxxx         | 121, 123            |

| CCP2CON   | —           | _                             | DC2B1                     | DC2B0           | CCP2M3        | CCP2M2         | CCP2M1                  | CCP2M0  | 00 0000           | 117                 |

| TMR3H     | Timer3 Reg  | ister High Byt                | e                         |                 |               |                |                         |         | xxxx xxxx         | 113                 |

| TMR3L     | Timer3 Reg  | ister Low Byte                | e                         |                 |               |                |                         |         | xxxx xxxx         | 113                 |

| T3CON     | RD16        | T3CCP2                        | T3CKPS1                   | T3CKPS0         | T3CCP1        | T3SYNC         | TMR3CS                  | TMR3ON  | 0000 0000         | 113                 |

| SPBRG     | USART1 Ba   | aud Rate Gen                  | erator                    | •               |               | •              | •                       |         | 0000 0000         | 168                 |

| RCREG     | USART1 Re   | eceive Regist                 | ər                        |                 |               |                |                         |         | 0000 0000         | 175, 178,<br>180    |

| TXREG     | USART1 Tra  | ansmit Regist                 | er                        |                 |               |                |                         |         | 0000 0000         | 173, 176,<br>179    |

| TXSTA     | CSRC        | TX9                           | TXEN                      | SYNC            | —             | BRGH           | TRMT                    | TX9D    | 0000 -010         | 166                 |

| RCSTA     | SPEN        | RX9                           | SREN                      | CREN            | ADDEN         | FERR           | OERR                    | RX9D    | 0000 000x         | 167                 |

| EEADR     | Data EEPR   | OM Address                    | Register                  |                 | •             |                |                         | •       | 0000 0000         | 65, 69              |

| EEDATA    | Data EEPR   | OM Data Reg                   | ister                     |                 |               |                |                         |         | 0000 0000         | 69                  |

| EECON2    | Data EEPR   | OM Control R                  | legister 2 (no            | t a physical re | egister)      |                |                         |         |                   | 65, 69              |

| EECON1    | EEPGD       | CFGS                          | _                         | FREE            | WRERR         | WREN           | WR                      | RD      | xx-0 x000         | 66                  |

Legend: x = unknown, u = unchanged, - = unimplemented, q = value depends on condition Note 1: RA6 and associated bits are configured as port pins in RCIO and ECIO Oscillator mode only and read '0' in all other Oscillator modes. 2: Bit 21 of the TBLPTRU allows access to the device configuration bits.

3: These registers and bits are reserved on the PIC18F2X2 devices; always maintain these clear.

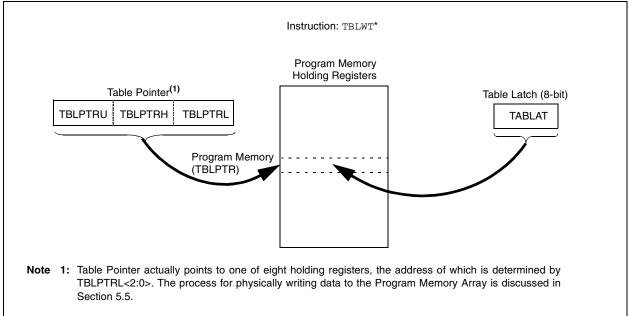

# 5.2 Control Registers

Several control registers are used in conjunction with the TBLRD and TBLWT instructions. These include the:

- EECON1 register

- EECON2 register

- TABLAT register

- TBLPTR registers

## 5.2.1 EECON1 AND EECON2 REGISTERS

EECON1 is the control register for memory accesses.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the memory write and erase sequences.

Control bit EEPGD determines if the access will be a program or data EEPROM memory access. When clear, any subsequent operations will operate on the data EEPROM memory. When set, any subsequent operations will operate on the program memory.

Control bit CFGS determines if the access will be to the configuration registers or to program memory/data EEPROM memory. When set, subsequent operations will operate on configuration registers, regardless of EEPGD (see "Special Features of the CPU", Section 19.0). When clear, memory selection access is determined by EEPGD.

The FREE bit, when set, will allow a program memory erase operation. When the FREE bit is set, the erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a MCLR Reset or a WDT Time-out Reset during normal operation. In these situations, the user can check the WRERR bit and rewrite the location. It is necessary to reload the data and address registers (EEDATA and EEADR), due to RESET values of zero.

Control bit WR initiates write operations. This bit cannot be cleared, only set, in software. It is cleared in hardware at the completion of the write operation. The inability to clear the WR bit in software prevents the accidental or premature termination of a write operation.

Note: Interrupt flag bit EEIF, in the PIR2 register, is set when the write is complete. It must be cleared in software.

# REGISTER 5-1: EECON1 REGISTER (ADDRESS FA6h)

|       | R/W-x                                                                                      | R/W-x                       | U-0         | R/W-0         | R/W-x                            | R/W-0       | R/S-0       | R/S-0       |  |  |

|-------|--------------------------------------------------------------------------------------------|-----------------------------|-------------|---------------|----------------------------------|-------------|-------------|-------------|--|--|

|       | EEPGD                                                                                      | CFGS                        | —           | FREE          | WRERR                            | WREN        | WR          | RD          |  |  |

|       | bit 7                                                                                      |                             |             |               |                                  |             |             | bit 0       |  |  |

| L:1 7 |                                                                                            |                             |             |               | Assess Only at                   | L 14        |             |             |  |  |

| bit 7 |                                                                                            |                             |             |               |                                  |             |             |             |  |  |

|       | 1 = Access FLASH Program memory<br>0 = Access Data EEPROM memory                           |                             |             |               |                                  |             |             |             |  |  |

| bit 6 | CFGS: FLASH Program/Data EE or Configuration Select bit                                    |                             |             |               |                                  |             |             |             |  |  |

|       |                                                                                            | Configurati                 |             |               |                                  |             |             |             |  |  |

|       | 0 = Access                                                                                 | FLASH Pro                   | ogram or Da | ata EEPRON    | /I memory                        |             |             |             |  |  |

| bit 5 | Unimplem                                                                                   | ented: Rea                  | d as '0'    |               |                                  |             |             |             |  |  |

| bit 4 |                                                                                            | ASH Row Er                  |             |               |                                  |             |             |             |  |  |

|       |                                                                                            |                             |             |               | d by TBLPTR c                    | on the next | WR comma    | and         |  |  |

|       | (cleared by completion of erase operation)<br>0 = Perform write only                       |                             |             |               |                                  |             |             |             |  |  |

| bit 3 | WRERR: F                                                                                   | LASH Prog                   | ram/Data E  | E Error Flag  | ı bit                            |             |             |             |  |  |

|       |                                                                                            | -                           |             | ly terminate  |                                  |             |             |             |  |  |

|       |                                                                                            |                             |             |               | ng in normal op                  | eration)    |             |             |  |  |

|       |                                                                                            | ite operatior               | -           |               |                                  |             |             |             |  |  |

|       |                                                                                            | nen a WRE⊦<br>cing of the € |             |               | and CFGS bits                    | are not cle | eared. This | allows      |  |  |

|       | i u                                                                                        |                             |             | 011.          |                                  |             |             |             |  |  |

| bit 2 | WREN: FL                                                                                   | ASH Progra                  | ım/Data EE  | Write Enab    | le bit                           |             |             |             |  |  |

|       |                                                                                            | write cycles                |             |               |                                  |             |             |             |  |  |

|       |                                                                                            | write to the                | EEPROM      |               |                                  |             |             |             |  |  |

| bit 1 | WR: Write                                                                                  |                             |             | ,             |                                  |             |             |             |  |  |

|       |                                                                                            |                             |             |               | or a program m<br>leared by hard |             |             |             |  |  |

|       | · · ·                                                                                      |                             |             | eared) in sof | •                                | ware once   |             | ipiele. The |  |  |

|       |                                                                                            | ycle to the E               |             |               | ,                                |             |             |             |  |  |

| bit 0 | RD: Read                                                                                   | Control bit                 |             |               |                                  |             |             |             |  |  |

|       |                                                                                            | s an EEPRC                  |             |               |                                  |             |             |             |  |  |

|       | (Read takes one cycle. RD is cleared in hardware. The RD bit can only be set (not cleared) |                             |             |               |                                  |             |             |             |  |  |

|       | in software. RD bit cannot be set when EEPGD = 1.)<br>0 = Does not initiate an EEPROM read |                             |             |               |                                  |             |             |             |  |  |

|       | 0 – <b>2000</b> H                                                                          | et annato u                 |             |               |                                  |             |             |             |  |  |

|       | Legend:                                                                                    |                             |             |               |                                  |             |             |             |  |  |

|       | Logona                                                                                     |                             |             |               |                                  |             |             |             |  |  |

W = Writable bit

'1' = Bit is set

R = Readable bit

- n = Value at POR

x = Bit is unknown

U = Unimplemented bit, read as '0'

'0' = Bit is cleared

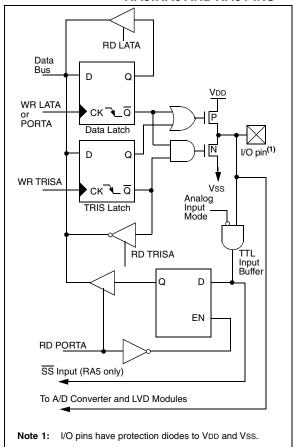

# 9.0 I/O PORTS

Depending on the device selected, there are either five ports or three ports available. Some pins of the I/O ports are multiplexed with an alternate function from the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Each port has three registers for its operation. These registers are:

- TRIS register (data direction register)

- PORT register (reads the levels on the pins of the device)

- LAT register (output latch)

The data latch (LAT register) is useful for read-modify-write operations on the value that the I/O pins are driving.

## 9.1 PORTA, TRISA and LATA Registers

PORTA is a 7-bit wide, bi-directional port. The corresponding Data Direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch.

The Data Latch register (LATA) is also memory mapped. Read-modify-write operations on the LATA register reads and writes the latched output value for PORTA.

The RA4 pin is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers.

The other PORTA pins are multiplexed with analog inputs and the analog VREF+ and VREF- inputs. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

Note: On a Power-on Reset, RA5 and RA3:RA0 are configured as analog inputs and read as '0'. RA6 and RA4 are configured as digital inputs.

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

#### EXAMPLE 9-1: INITIALIZING PORTA

| CLRF PORTA   | ; Initialize PORTA by<br>; clearing output |

|--------------|--------------------------------------------|

|              | ; data latches                             |

| CLRF LATA    | ; Alternate method                         |

|              | ; to clear output                          |

|              | ; data latches                             |

| MOVLW 0x07   | ; Configure A/D                            |

| MOVWF ADCON1 | ; for digital inputs                       |

| MOVLW 0xCF   | ; Value used to                            |

|              | ; initialize data                          |

|              | ; direction                                |

| MOVWF TRISA  | ; Set RA<3:0> as inputs                    |

|              | ; RA<5:4> as outputs                       |

|              |                                            |

BLOCK DIAGRAM OF RA3:RA0 AND RA5 PINS

# PIC18FXX2

## REGISTER 9-1: TRISE REGISTER

|       | R-0                    | R-0                           | R/W-0        | R/W-0            | U-0          | R/W-1       | R/W-1          | R/W-1  |

|-------|------------------------|-------------------------------|--------------|------------------|--------------|-------------|----------------|--------|

|       | IBF                    | OBF                           | IBOV         | PSPMODE          | —            | TRISE2      | TRISE1         | TRISE0 |

|       | bit 7                  |                               |              |                  |              |             |                | bit 0  |

|       |                        |                               |              |                  |              |             |                |        |

| bit 7 | •                      | Buffer Full S                 |              |                  |              | 0011        |                |        |

|       |                        | d nas been r<br>Ind has been  |              | d waiting to be  | read by the  | e CPU       |                |        |

| bit 6 |                        | out Buffer Fu                 |              | ŀ                |              |             |                |        |

| bit 0 |                        |                               |              | previously writ  | ten word     |             |                |        |

|       | 0 = The ou             | utput buffer h                | nas been re  | ad               |              |             |                |        |

| bit 5 |                        |                               |              | ct bit (in Micro |              |             |                |        |

|       |                        | e occurred w<br>be cleared ir |              | iously input wo  | ord has not  | been read   |                |        |

|       | · ·                    | erflow occuri                 | ,            |                  |              |             |                |        |

| bit 4 | PSPMOD                 | E: Parallel S                 | lave Port N  | lode Select bit  |              |             |                |        |

|       |                        | el Slave Port                 |              |                  |              |             |                |        |

|       |                        | al purpose I/                 |              |                  |              |             |                |        |

| bit 3 | -                      | nented: Rea                   |              |                  |              |             |                |        |

| bit 2 |                        | RE2 Directior                 | n Control bi | t                |              |             |                |        |

|       | 1 = Input<br>0 = Outpu | t                             |              |                  |              |             |                |        |

| bit 1 | •                      | RE1 Direction                 | n Control bi | t                |              |             |                |        |

|       | 1 = Input              |                               |              |                  |              |             |                |        |

|       | 0 = Outpu              | t                             |              |                  |              |             |                |        |

| bit 0 |                        | RE0 Directior                 | n Control bi | t                |              |             |                |        |

|       | 1 = Input<br>0 = Outpu | t                             |              |                  |              |             |                |        |

|       | o – Outpu              |                               |              |                  |              |             |                |        |

|       | Legend:                |                               |              |                  |              |             |                |        |

|       | R = Reada              | able bit                      | W = 1        | Writable bit     | U = Unim     | plemented l | bit, read as ' | 0'     |

|       | - n = Value            | e at POR                      | '1' =        | Bit is set       | '0' = Bit is | •           | x = Bit is u   |        |

| Name      | Bit 7                | Bit 6                                                                       | Bit 5        | Bit 4         | Bit 3         | Bit 2       | Bit 1         | Bit 0       | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |  |  |  |  |  |  |

|-----------|----------------------|-----------------------------------------------------------------------------|--------------|---------------|---------------|-------------|---------------|-------------|----------------------|---------------------------------|--|--|--|--|--|--|

| INTCON    | GIE/GIEH             | PEIE/GIEL                                                                   | TMR0IE       | INT0IE        | RBIE          | TMR0IF      | INTOIF        | RBIF        | 0000 000x            | 0000 000u                       |  |  |  |  |  |  |

| PIR1      | PSPIF <sup>(1)</sup> | ADIF                                                                        | RCIF         | TXIF          | SSPIF         | CCP1IF      | TMR2IF        | TMR1IF      | 0000 0000            | 0000 0000                       |  |  |  |  |  |  |

| PIE1      | PSPIE <sup>(1)</sup> | ADIE                                                                        | RCIE         | TXIE          | SSPIE         | CCP1IE      | TMR2IE        | TMR1IE      | 0000 0000            | 0000 0000                       |  |  |  |  |  |  |

| IPR1      | PSPIP <sup>(1)</sup> | ADIP                                                                        | RCIP         | TXIP          | SSPIP         | CCP1IP      | TMR2IP        | TMR1IP      | 0000 0000            | 0000 0000                       |  |  |  |  |  |  |

| TRISC     | PORTC D              | ata Direction                                                               | Register     |               |               |             |               |             | 1111 1111            | 1111 1111                       |  |  |  |  |  |  |

| TMR1L     | Holding Re           | egister for th                                                              | e Least Sigr | nificant Byte | of the 16-bit | TMR1 Reg    | gister        |             | xxxx xxxx            | uuuu uuuu                       |  |  |  |  |  |  |

| TMR1H     | Holding Re           | egister for th                                                              | e Most Sign  | ificant Byte  | of the 16-bit | TMR1 Reg    | ister         |             | xxxx xxxx            | uuuu uuuu                       |  |  |  |  |  |  |

| T1CON     | RD16                 | —                                                                           | T1CKPS1      | T1CKPS0       | T1OSCEN       | T1SYNC      | TMR1CS        | TMR1ON      | 0-00 0000            | u-uu uuuu                       |  |  |  |  |  |  |

| CCPR1L    | Capture/C            | ompare/PWI                                                                  | M Register1  | (LSB)         |               |             |               |             | xxxx xxxx            | uuuu uuuu                       |  |  |  |  |  |  |

| CCPR1H    | Capture/C            | ompare/PWI                                                                  | M Register1  | (MSB)         |               |             |               |             | xxxx xxxx            | uuuu uuuu                       |  |  |  |  |  |  |

| CCP1CON   |                      | —                                                                           | DC1B1        | DC1B0         | CCP1M3        | CCP1M2      | CCP1M1        | CCP1M0      | 00 0000              | 00 0000                         |  |  |  |  |  |  |

| CCPR2L    | Capture/C            | ompare/PWI                                                                  | M Register2  | (LSB)         |               |             |               |             | xxxx xxxx            | uuuu uuuu                       |  |  |  |  |  |  |

| CCPR2H    | Capture/C            | ompare/PWI                                                                  | M Register2  | (MSB)         |               |             |               |             | xxxx xxxx            | uuuu uuuu                       |  |  |  |  |  |  |

| CCP2CON   |                      | —                                                                           | DC2B1        | DC2B0         | CCP2M3        | CCP2M2      | CCP2M1        | CCP2M0      | 00 0000              | 00 0000                         |  |  |  |  |  |  |

| PIR2      |                      | —                                                                           | _            | EEIE          | BCLIF         | LVDIF       | TMR3IF        | CCP2IF      | 0 0000               | 0 0000                          |  |  |  |  |  |  |

| PIE2      |                      | —                                                                           | _            | EEIF          | BCLIE         | LVDIE       | TMR3IE        | CCP2IE      | 0 0000               | 0 0000                          |  |  |  |  |  |  |

| IPR2      |                      | —                                                                           | _            | EEIP          | BCLIP         | LVDIP       | TMR3IP        | CCP2IP      | 1 1111               | 1 1111                          |  |  |  |  |  |  |

| TMR3L     | Holding Re           | egister for th                                                              | e Least Sigr | nificant Byte | of the 16-bit | TMR3 Reg    | gister        |             | xxxx xxxx            | uuuu uuuu                       |  |  |  |  |  |  |

| TMR3H     | Holding Re           | egister for th                                                              | e Most Sign  | ificant Byte  | of the 16-bit | TMR3 Reg    | ister         |             | xxxx xxxx            | uuuu uuuu                       |  |  |  |  |  |  |

| T3CON     | RD16                 | RD16 T3CCP2 T3CKPS1 T3CKPS0 T3CCP1 T3SYNC TMR3CS TMR3ON 0000 0000 uuuu uuuu |              |               |               |             |               |             | uuuu uuuu            |                                 |  |  |  |  |  |  |

| Legend: x | = unknow             | n, u = uncha                                                                | nged, - = ur | nimplemente   | d, read as 'C | '. Shaded o | cells are not | t used by C | apture and Tin       |                                 |  |  |  |  |  |  |

# TABLE 14-3: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, TIMER1 AND TIMER3

Note 1: The PSPIF, PSPIE and PSPIP bits are reserved on the PIC18F2x2 devices; always maintain these bits clear.

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| WCOL  | SSPOV | SSPEN | СКР   | SSPM3 | SSPM2 | SSPM1 | SSPM0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

|       |       |       |       |       |       |       |       |

# REGISTER 15-2: SSPCON1: MSSP CONTROL REGISTER1 (SPI MODE)

bit 7 WCOL: Write Collision Detect bit (Transmit mode only)

- 1 = The SSPBUF register is written while it is still transmitting the previous word (must be cleared in software)

- $0 = No \ collision$

- bit 6 SSPOV: Receive Overflow Indicator bit

## SPI Slave mode:

- 1 = A new byte is received while the SSPBUF register is still holding the previous data. In case of overflow, the data in SSPSR is lost. Overflow can only occur in Slave mode. The user must read the SSPBUF, even if only transmitting data, to avoid setting overflow (must be cleared in software).

- 0 = No overflow

- **Note:** In Master mode, the overflow bit is not set since each new reception (and transmission) is initiated by writing to the SSPBUF register.

#### bit 5 SSPEN: Synchronous Serial Port Enable bit

- 1 = Enables serial port and configures SCK, SDO, SDI, and  $\overline{SS}$  as serial port pins

- 0 = Disables serial port and configures these pins as I/O port pins

- **Note:** When enabled, these pins must be properly configured as input or output.

#### bit 4 CKP: Clock Polarity Select bit

- 1 = IDLE state for clock is a high level

- 0 = IDLE state for clock is a low level

- bit 3-0 SSPM3:SSPM0: Synchronous Serial Port Mode Select bits

- 0101 = SPI Slave mode, clock = SCK pin,  $\overline{SS}$  pin control disabled,  $\overline{SS}$  can be used as I/O pin

- $0100 = SPI Slave mode, clock = SCK pin, \overline{SS} pin control enabled$

- 0011 = SPI Master mode, clock = TMR2 output/2

- 0010 = SPI Master mode, clock = FOSC/64

- 0001 = SPI Master mode, clock = Fosc/16

- 0000 = SPI Master mode, clock = Fosc/4

- Note: Bit combinations not specifically listed here are either reserved, or implemented in  $I^2C$  mode only.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented I  | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

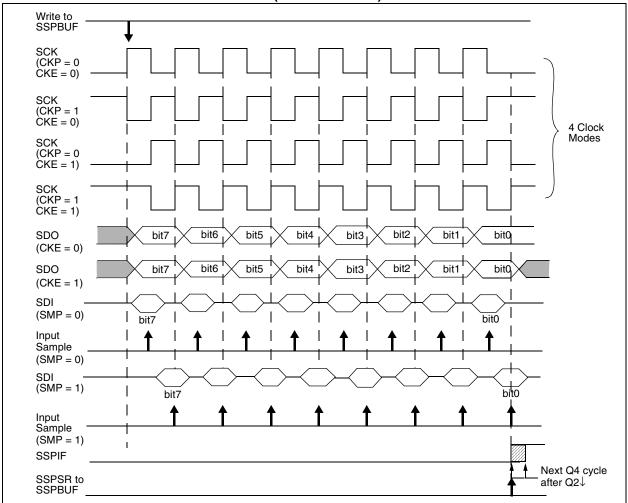

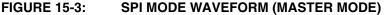

#### 15.3.5 MASTER MODE

The master can initiate the data transfer at any time because it controls the SCK. The master determines when the slave (Processor 2, Figure 15-2) is to broadcast data by the software protocol.

In Master mode, the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SDO output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and status bits appropriately set). This could be useful in receiver applications as a "Line Activity Monitor" mode.

The clock polarity is selected by appropriately programming the CKP bit (SSPCON1<4>). This then, would give waveforms for SPI communication as shown in Figure 15-3, Figure 15-5, and Figure 15-6, where the MSB is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 Tcy)

- Fosc/64 (or 16 Tcy)

- Timer2 output/2

This allows a maximum data rate (at 40 MHz) of 10.00 Mbps.

Figure 15-3 shows the waveforms for Master mode. When the CKE bit is set, the SDO data is valid before there is a clock edge on SCK. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPBUF is loaded with the received data is shown.

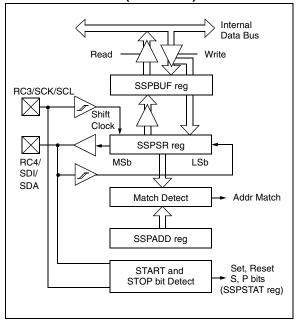

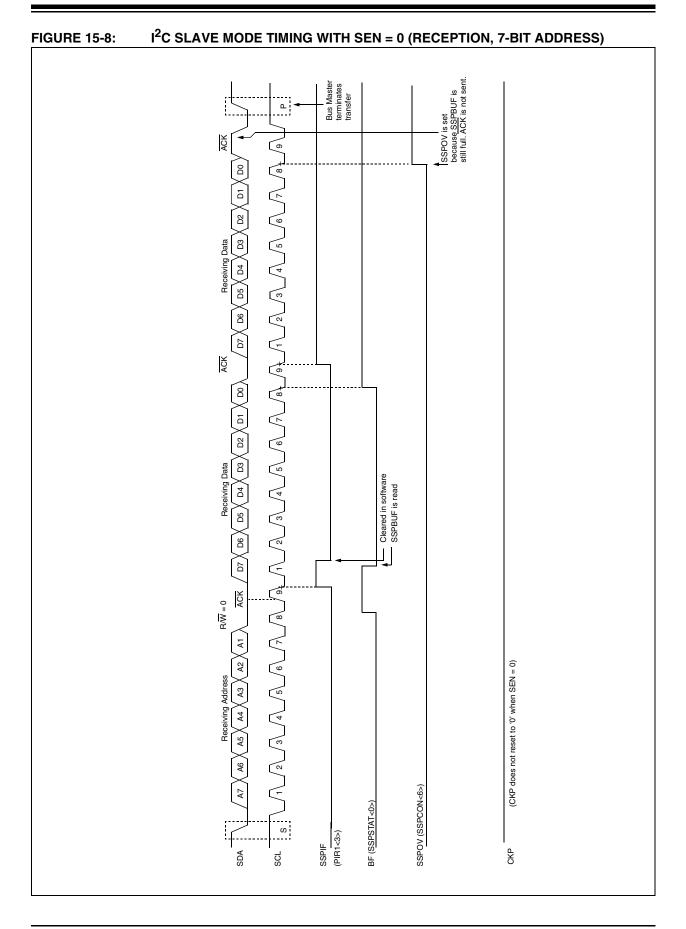

# 15.4 I<sup>2</sup>C Mode

The MSSP module in  $I^2C$  mode fully implements all master and slave functions (including general call support) and provides interrupts on START and STOP bits in hardware to determine a free bus (multi-master function). The MSSP module implements the Standard mode specifications, as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer:

- Serial clock (SCL) RC3/SCK/SCL

- Serial data (SDA) RC4/SDI/SDA

The user must configure these pins as inputs or outputs through the TRISC<4:3> bits.

#### FIGURE 15-7: MSSP BLOCK DIAGRAM (I<sup>2</sup>C MODE)

## 15.4.1 REGISTERS

The MSSP module has six registers for  $\mathsf{I}^2\mathsf{C}$  operation. These are:

- MSSP Control Register1 (SSPCON1)

- MSSP Control Register2 (SSPCON2)

- MSSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

- MSSP Address Register (SSPADD)

SSPCON, SSPCON2 and SSPSTAT are the control and status registers in  $I^2C$  mode operation. The SSPCON and SSPCON2 registers are readable and writable. The lower 6 bits of the SSPSTAT are read only. The upper two bits of the SSPSTAT are read/ write.

SSPSR is the shift register used for shifting data in or out. SSPBUF is the buffer register to which data bytes are written to or read from.

SSPADD register holds the slave device address when the SSP is configured in  $I^2C$  Slave mode. When the SSP is configured in Master mode, the lower seven bits of SSPADD act as the baud rate generator reload value.

In receive operations, SSPSR and SSPBUF together, create a double buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not double buffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

# PIC18FXX2

## 15.4.10 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address, or the other half of a 10-bit address is accomplished by simply writing a value to the SSPBUF register. This action will set the buffer full flag bit, BF, and allow the baud rate generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted (see data hold time specification parameter 106). SCL is held low for one baud rate generator rollover count (TBRG). Data should be valid before SCL is released high (see data setup time specification parameter 107). When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time if an address match occurred or if data was received properly. The status of ACK is written into the ACKDT bit on the falling edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPIF bit is set and the master clock (baud rate generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 15-21).

After the write to the SSPBUF, each bit of address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will de-assert the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT status bit (SSPCON2<6>). Following the falling edge of the ninth clock transmission of the address, the SSPIF is set, the BF flag is cleared and the baud rate generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

## 15.4.10.1 BF Status Flag

In Transmit mode, the BF bit (SSPSTAT<0>) is set when the CPU writes to SSPBUF and is cleared when all 8 bits are shifted out.

## 15.4.10.2 WCOL Status Flag

If the user writes the SSPBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

WCOL must be cleared in software.

## 15.4.10.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit (SSPCON2<6>) is cleared when the slave has sent an Acknowledge (ACK = 0), and is set when the slave does not Acknowledge (ACK = 1). A slave sends an Acknowledge when it has recognized its address (including a general call) or when the slave has properly received its data.

# 15.4.11 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the receive enable bit, RCEN (SSPCON2<3>).

Note: In the MSSP module, the RCEN bit must be set after the ACK sequence or the RCEN bit will be disregarded.

The baud rate generator begins counting, and on each rollover, the state of the SCL pin changes (high to low/ low to high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag bit is set, the SSPIF flag bit is set and the baud rate generator is suspended from counting, holding SCL low. The MSSP is now in IDLE state, awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception, by setting the Acknowledge sequence enable bit, ACKEN (SSPCON2<4>).

## 15.4.11.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when the SSPBUF register is read.

## 15.4.11.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when 8 bits are received into the SSPSR and the BF flag bit is already set from a previous reception.

## 15.4.11.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

# TABLE 16-4: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0)

| BAUD           | Fosc = | 40 MHz  | SPBRG              | 33     | MHz    | SPBRG              | 25     | MHz         | SPBRG              | 20 1       | ИНz    | SPBRG              |

|----------------|--------|---------|--------------------|--------|--------|--------------------|--------|-------------|--------------------|------------|--------|--------------------|

| RATE           |        | %       | value              |        | %      | value              |        | %           | value              |            | %      | value              |

| (Kbps)         | KBAUD  | ERROR   | (decimal)          | KBAUD  | ERROR  | (decimal)          | KBAUD  | ERROR       | (decimal)          | KBAUD      | ERROR  | (decimal)          |

| 0.3            | NA     | -       | -                  | NA     | -      | -                  | NA     | -           | -                  | NA         | -      | -                  |

| 1.2            | NA     | -       | -                  | NA     | -      | -                  | NA     | -           | -                  | NA         | -      | -                  |

| 2.4            | NA     | -       | -                  | 2.40   | -0.07  | 214                | 2.40   | -0.15       | 162                | 2.40       | +0.16  | 129                |

| 9.6            | 9.62   | +0.16   | 64                 | 9.55   | -0.54  | 53                 | 9.53   | -0.76       | 40                 | 9.47       | -1.36  | 32                 |

| 19.2           | 18.94  | -1.36   | 32                 | 19.10  | -0.54  | 26                 | 19.53  | +1.73       | 19                 | 19.53      | +1.73  | 15                 |

| 76.8           | 78.13  | +1.73   | 7                  | 73.66  | -4.09  | 6                  | 78.13  | +1.73       | 4                  | 78.13      | +1.73  | 3                  |

| 96             | 89.29  | -6.99   | 6                  | 103.13 | +7.42  | 4                  | 97.66  | +1.73       | 3                  | 104.17     | +8.51  | 2                  |

| 300            | 312.50 | +4.17   | 1                  | 257.81 | -14.06 | 1                  | NA     | -           | -                  | 312.50     | +4.17  | 0                  |

| 500            | 625    | +25.00  | 0                  | NA     | -      | -                  | NA     | -           | -                  | NA         | -      | -                  |

| HIGH           | 625    | -       | 0                  | 515.63 | -      | 0                  | 390.63 | -           | 0                  | 312.50     | -      | 0                  |

| LOW            | 2.44   | -       | 255                | 2.01   | -      | 255                | 1.53   | -           | 255                | 1.22       | -      | 255                |

|                | _      |         |                    |        |        |                    |        |             |                    |            |        |                    |

| BAUD           | FOSC = | 16 MHz  | SPBRG              | 101    | MHz    | SPBRG              | 7.1590 | 9 MHz       | SPBRG              | 5.068      | 5 MHZ  | SPBRG              |

| RATE<br>(Kbps) |        | %       | value<br>(decimal) |        | %      | value<br>(decimal) |        | %           | value<br>(decimal) |            | %      | value<br>(decimal) |

| (1000)         | KBAUD  | ERROR   | (uconnai)          | KBAUD  | ERROR  | (uconnul)          | KBAUD  | ERROR       | (uconnul)          | KBAUD      | ERROR  | (uconnui)          |

| 0.3            | NA     | -       | -                  | NA     | -      | -                  | NA     | -           | -                  | NA         | -      | -                  |

| 1.2            | 1.20   | +0.16   | 207                | 1.20   | +0.16  | 129                | 1.20   | +0.23       | 92                 | 1.20       | 0      | 65                 |

| 2.4            | 2.40   | +0.16   | 103                | 2.40   | +0.16  | 64                 | 2.38   | -0.83       | 46                 | 2.40       | 0      | 32                 |

| 9.6            | 9.62   | +0.16   | 25                 | 9.77   | +1.73  | 15                 | 9.32   | -2.90       | 11                 | 9.90       | +3.13  | 7                  |

| 19.2           | 19.23  | +0.16   | 12                 | 19.53  | +1.73  | 7                  | 18.64  | -2.90       | 5                  | 19.80      | +3.13  | 3                  |

| 76.8           | 83.33  | +8.51   | 2                  | 78.13  | +1.73  | 1                  | 111.86 | +45.65      | 0                  | 79.20      | +3.13  | 0                  |

| 96             | 83.33  | -13.19  | 2                  | 78.13  | -18.62 | 1                  | NA     | -           | -                  | NA         | -      | -                  |

| 300            | 250    | -16.67  | 0                  | 156.25 | -47.92 | 0                  | NA     | -           | -                  | NA         | -      | -                  |

| 500            | NA     | -       | -                  | NA     | -      | -                  | NA     | -           | -                  | NA         | -      | -                  |

| HIGH           | 250    | -       | 0                  | 156.25 | -      | 0                  | 111.86 | -           | 0                  | 79.20      | -      | 0                  |

| LOW            | 0.98   | -       | 255                | 0.61   | -      | 255                | 0.44   | -           | 255                | 0.31       | -      | 255                |

| BAUD           | Fosc : | = 4 MHz | SPBRG              | 3.5795 | 45 MHz | SPBRG              | 11     | 1 MHz SPBRG |                    | 32.768 kHz |        | SPBRG              |

| RATE           |        | %       | value              |        | %      | value              |        | %           | value              |            | %      | value              |

| (Kbps)         | KBAUD  | ERROR   | (decimal)          | KBAUD  | ERROR  | (decimal)          | KBAUD  | ERROR       | (decimal)          | KBAUD      | ERROR  | (decimal)          |

| 0.3            | 0.30   | -0.16   | 207                | 0.30   | +0.23  | 185                | 0.30   | +0.16       | 51                 | 0.26       | -14.67 | 1                  |

| 1.2            | 1.20   | +1.67   | 51                 | 1.19   | -0.83  | 46                 | 1.20   | +0.16       | 12                 | NA         | -      | -                  |

| 2.4            | 2.40   | +1.67   | 25                 | 2.43   | +1.32  | 22                 | 2.23   | -6.99       | 6                  | NA         | -      | -                  |

| 9.6            | 8.93   | -6.99   | 6                  | 9.32   | -2.90  | 5                  | 7.81   | -18.62      | 1                  | NA         | -      | -                  |

| 19.2           | 20.83  | +8.51   | 2                  | 18.64  | -2.90  | 2                  | 15.63  | -18.62      | 0                  | NA         | -      | -                  |

| 76.8           | 62.50  | -18.62  | 0                  | 55.93  | -27.17 | 0                  | NA     | -           | -                  | NA         | -      | -                  |

| 96             | NA     | -       | -                  | NA     | -      | -                  | NA     | -           | -                  | NA         | -      | -                  |

| 300            | NA     | -       | -                  | NA     | -      | -                  | NA     | -           | -                  | NA         | -      | -                  |

| 500            | NA     | -       | -                  | NA     | -      | -                  | NA     | -           | -                  | NA         | -      | -                  |

| HIGH           | 62.50  | -       | 0                  | 55.93  | -      | 0                  | 15.63  | -           | 0                  | 0.51       | -      | 0                  |

| LOW            | 0.24   | -       | 255                | 0.22   | -      | 255                | 0.06   | -           | 255                | 0.002      | -      | 255                |

# 17.0 COMPATIBLE 10-BIT ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The Analog-to-Digital (A/D) converter module has five inputs for the PIC18F2X2 devices and eight for the PIC18F4X2 devices. This module has the ADCON0 and ADCON1 register definitions that are compatible with the mid-range A/D module.

The A/D allows conversion of an analog input signal to a corresponding 10-bit digital number.

## REGISTER 17-1: ADCON0 REGISTER

The A/D module has four registers. These registers are:

- A/D Result High Register (ADRESH)

- A/D Result Low Register (ADRESL)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

The ADCON0 register, shown in Register 17-1, controls the operation of the A/D module. The ADCON1 register, shown in Register 17-2, configures the functions of the port pins.

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | U-0 | R/W-0 |

|-------|-------|-------|-------|-------|---------|-----|-------|

| ADCS1 | ADCS0 | CHS2  | CHS1  | CHS0  | GO/DONE | —   | ADON  |

| bit 7 |       |       |       |       |         |     | bit 0 |

#### bit 7-6 ADCS1:ADCS0: A/D Conversion Clock Select bits (ADCON0 bits in **bold**)

| ADCON1<br><adcs2></adcs2> | ADCON0<br><adcs1:adcs0></adcs1:adcs0> | Clock Conversion                                        |

|---------------------------|---------------------------------------|---------------------------------------------------------|

| 0                         | 00                                    | Fosc/2                                                  |

| 0                         | 01                                    | Fosc/8                                                  |

| 0                         | 10                                    | Fosc/32                                                 |

| 0                         | 11                                    | FRC (clock derived from the internal A/D RC oscillator) |

| 1                         | 00                                    | Fosc/4                                                  |

| 1                         | 01                                    | Fosc/16                                                 |

| 1                         | 10                                    | Fosc/64                                                 |

| 1                         | 11                                    | FRC (clock derived from the internal A/D RC oscillator) |

#### bit 5-3 CHS2:CHS0: Analog Channel Select bits

- 000 = channel 0, (AN0)

- 001 = channel 1, (AN1)

- 010 =channel 2, (AN2)

- 011 =channel 3, (AN3)

- 100 =channel 4, (AN4)

- 101 = channel 5, (AN5)

- 110 = channel 6, (AN6)

- 110 = Channel 0, (ANO)

- 111 = channel 7, (AN7)

- **Note:** The PIC18F2X2 devices do not implement the full 8 A/D channels; the unimplemented selections are reserved. Do not select any unimplemented channel.

bit 2 GO/DONE: A/D Conversion Status bit

When ADON = 1:

- 1 = A/D conversion in progress (setting this bit starts the A/D conversion which is automatically cleared by hardware when the A/D conversion is complete)

0 = A/D conversion not in progress

- bit 1 Unimplemented: Read as '0'

#### bit 0 ADON: A/D On bit

1 = A/D converter module is powered up

0 = A/D converter module is shut-off and consumes no operating current

| Γ | Legend:            |                  |                      |                    |

|---|--------------------|------------------|----------------------|--------------------|

|   | R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

|   | - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| NEGF                  | Negate f                                                                                                                                                                                                                                                                |  |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:               | [ <i>label</i> ] NEGF f[,a]                                                                                                                                                                                                                                             |  |  |  |

| Operands:             | $0 \le f \le 255$<br>$a \in [0,1]$                                                                                                                                                                                                                                      |  |  |  |

| Operation:            | $(\overline{f}) + 1 \rightarrow f$                                                                                                                                                                                                                                      |  |  |  |

| Status Affected:      | N, OV, C, DC, Z                                                                                                                                                                                                                                                         |  |  |  |

| Encoding:             | 0110 110a ffff ffff                                                                                                                                                                                                                                                     |  |  |  |

| Description:          | Description: Location 'f' is negated using two's<br>complement. The result is placed<br>the data memory location 'f'. If 'a'<br>0, the Access Bank will be<br>selected, overriding the BSR value<br>If 'a' = 1, then the bank will be<br>selected as per the BSR value. |  |  |  |

| Words:                | 1                                                                                                                                                                                                                                                                       |  |  |  |

| Cycles:               | 1                                                                                                                                                                                                                                                                       |  |  |  |

| Q Cycle Activity:     |                                                                                                                                                                                                                                                                         |  |  |  |

| Q1                    | Q2 Q3 Q4                                                                                                                                                                                                                                                                |  |  |  |

| Decode                | ReadProcessWriteregister 'f'Dataregister 'f'                                                                                                                                                                                                                            |  |  |  |

| Example:              | NEGF REG, 1                                                                                                                                                                                                                                                             |  |  |  |

| Before Instru<br>REG  | ction<br>= 0011 1010 [0x3A]                                                                                                                                                                                                                                             |  |  |  |

| After Instruct<br>REG | ion<br>= 1100 0110 [0xC6]                                                                                                                                                                                                                                               |  |  |  |

| NOF               | )            | No Opera  | No Operation        |     |   |         |  |  |

|-------------------|--------------|-----------|---------------------|-----|---|---------|--|--|

| Synt              | ax:          | [ label ] | NOP                 |     |   |         |  |  |

| Ope               | rands:       | None      | None                |     |   |         |  |  |

| Operation:        |              | No opera  | tion                |     |   |         |  |  |

| Statu             | us Affected: | None      |                     |     |   |         |  |  |

| Encoding:         |              | 0000      | 0000                | 000 | 0 | 0000    |  |  |

|                   |              | 1111      | xxxx                | XXX | x | xxxx    |  |  |

| Description:      |              | No opera  | tion.               |     |   |         |  |  |

| Wor               | ds:          | 1         |                     |     |   |         |  |  |

| Cycles:           |              | 1         |                     |     |   |         |  |  |

| Q Cycle Activity: |              |           |                     |     |   |         |  |  |

|                   | Q1           | Q2        | Q3                  |     |   | Q4      |  |  |

|                   | Decode       | No        | No                  |     |   | No      |  |  |

|                   |              | operation | operation operation |     |   | eration |  |  |

#### Example:

None.

# PIC18FXX2

| URN             | Return fr                                                                                                                                                                                                                                           | Return from Subroutine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ax:             | [ label ]                                                                                                                                                                                                                                           | RETURI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | N [s]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |