Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                               |

| Number of I/O              | 34                                                                       |

| Program Memory Size        | 32KB (16K x 16)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 1.5K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-TQFP                                                                  |

| Supplier Device Package    | 44-TQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f452-e-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 1-3: PIC18F4X2 PINOUT I/O DESCRIPTIONS (CONTINUED)

| Dia Nama                                 | Pi  | n Numb | er   | Pin                       | Buffer           | D                                                                                            |

|------------------------------------------|-----|--------|------|---------------------------|------------------|----------------------------------------------------------------------------------------------|

| Pin Name                                 | DIP | PLCC   | TQFP | Туре                      | Type             | Description                                                                                  |

|                                          |     |        |      |                           |                  | PORTC is a bi-directional I/O port.                                                          |

| RC0/T1OSO/T1CKI<br>RC0<br>T1OSO<br>T1CKI | 15  | 16     | 32   | I/O<br>O<br>I             | ST<br>—<br>ST    | Digital I/O.<br>Timer1 oscillator output.<br>Timer1/Timer3 external clock input.             |

| RC1/T1OSI/CCP2<br>RC1<br>T1OSI<br>CCP2   | 16  | 18     | 35   | I/O<br> <br> <br> <br> /O | ST<br>CMOS<br>ST | Digital I/O.<br>Timer1 oscillator input.<br>Capture2 input, Compare2 output, PWM2 output.    |

| RC2/CCP1<br>RC2<br>CCP1                  | 17  | 19     | 36   | I/O<br>I/O                | ST<br>ST         | Digital I/O.<br>Capture1 input/Compare1 output/PWM1 output.                                  |

| RC3/SCK/SCL<br>RC3<br>SCK                | 18  | 20     | 37   | I/O<br>I/O                | ST<br>ST         | Digital I/O.<br>Synchronous serial clock input/output for<br>SPI mode.                       |

| SCL                                      |     |        |      | I/O                       | ST               | Synchronous serial clock input/output for I <sup>2</sup> C mode.                             |

| RC4/SDI/SDA<br>RC4<br>SDI<br>SDA         | 23  | 25     | 42   | I/O<br>I<br>I/O           | ST<br>ST<br>ST   | Digital I/O.<br>SPI Data In.<br>I <sup>2</sup> C Data I/O.                                   |

| RC5/SDO<br>RC5<br>SDO                    | 24  | 26     | 43   | I/O<br>O                  | ST<br>—          | Digital I/O.<br>SPI Data Out.                                                                |

| RC6/TX/CK<br>RC6<br>TX<br>CK             | 25  | 27     | 44   | I/O<br>O<br>I/O           | ST<br>—<br>ST    | Digital I/O.<br>USART Asynchronous Transmit.<br>USART Synchronous Clock (see related RX/DT). |

| RC7/RX/DT<br>RC7<br>RX<br>DT             | 26  | 29     | 1    | I/O<br>I<br>I/O           | ST<br>ST<br>ST   | Digital I/O.<br>USART Asynchronous Receive.<br>USART Synchronous Data (see related TX/CK).   |

Legend: TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

O = Output

OD = Open Drain (no P diode to VDD)

CMOS = CMOS compatible input or output

I = Input

P = Power

### 4.6 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle, while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO) then two cycles are required to complete the instruction (Example 4-2).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register" (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### **EXAMPLE 4-2: INSTRUCTION PIPELINE FLOW**

| 1                           | Tcy0    | Tcy1      | TCY2      | TCY3      | Tcy4        | Tcy5          |

|-----------------------------|---------|-----------|-----------|-----------|-------------|---------------|

| 1. MOVLW 55h                | etch 1  | Execute 1 | •         |           | •           |               |

| 2. MOVWF PORTB              |         | Fetch 2   | Execute 2 |           | _           |               |

| 3. BRA SUB_1                |         |           | Fetch 3   | Execute 3 |             |               |

| 4. BSF PORTA, BIT3 (Force   | ed NOP) | -         |           | Fetch 4   | Flush (NOP) |               |

| 5. Instruction @ address ST | UB_1    |           |           |           | Fetch SUB_1 | Execute SUB_1 |

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

## 4.7 Instructions in Program Memory

The program memory is addressed in bytes. Instructions are stored as two bytes or four bytes in program memory. The Least Significant Byte of an instruction word is always stored in a program memory location with an even address (LSB ='0'). Figure 4-5 shows an example of how instruction words are stored in the program memory. To maintain alignment with instruction boundaries, the PC increments in steps of 2 and the LSB will always read '0' (see Section 4.4).

The CALL and GOTO instructions have an absolute program memory address embedded into the instruction. Since instructions are always stored on word boundaries, the data contained in the instruction is a word address. The word address is written to PC<20:1>, which accesses the desired byte address in program memory. Instruction #2 in Figure 4-5 shows how the instruction "GOTO 000006h" is encoded in the program memory. Program branch instructions which encode a relative address offset operate in the same manner. The offset value stored in a branch instruction represents the number of single word instructions that the PC will be offset by. Section 20.0 provides further details of the instruction set.

FIGURE 4-5: INSTRUCTIONS IN PROGRAM MEMORY

|                |            |            | LOD 4   | 100 0   | Word Address        |

|----------------|------------|------------|---------|---------|---------------------|

|                | Program M  | lemory [   | LSB = 1 | LSB = 0 | 000000h             |

|                | Byte Locat |            |         |         | 00000011<br>000002h |

|                | Dyto Looat | -          |         |         | 000002H             |

|                |            | -          |         |         | 000004H             |

| Instruction 1: | MOVLW      | 055h       | 0Fh     | 55h     | 000008h             |

| Instruction 2: | GOTO       | 000006h    | EFh     | 03h     | 00000Ah             |

|                |            | Ī          | F0h     | 00h     | 00000Ch             |

| Instruction 3: | MOVFF      | 123h, 456h | C1h     | 23h     | 00000Eh             |

|                |            |            | F4h     | 56h     | 000010h             |

|                |            |            |         |         | 000012h             |

|                |            | Ī          |         |         | 000014h             |

NOTES:

### 8.0 INTERRUPTS

The PIC18FXX2 devices have multiple interrupt sources and an interrupt priority feature that allows each interrupt source to be assigned a high priority level or a low priority level. The high priority interrupt vector is at 000008h and the low priority interrupt vector is at 000018h. High priority interrupt events will override any low priority interrupts that may be in progress.

There are ten registers which are used to control interrupt operation. These registers are:

- RCON

- INTCON

- INTCON2

- INTCON3

- PIR1, PIR2

- PIE1, PIE2

- IPR1, IPR2

It is recommended that the Microchip header files supplied with MPLAB® IDE be used for the symbolic bit names in these registers. This allows the assembler/compiler to automatically take care of the placement of these bits within the specified register.

Each interrupt source, except INTO, has three bits to control its operation. The functions of these bits are:

- Flag bit to indicate that an interrupt event occurred

- Enable bit that allows program execution to branch to the interrupt vector address when the flag bit is set

- · Priority bit to select high priority or low priority

The interrupt priority feature is enabled by setting the IPEN bit (RCON<7>). When interrupt priority is enabled, there are two bits which enable interrupts globally. Setting the GIEH bit (INTCON<7>) enables all interrupts that have the priority bit set. Setting the GIEL bit (INTCON<6>) enables all interrupts that have the priority bit cleared. When the interrupt flag, enable bit and appropriate global interrupt enable bit are set, the interrupt will vector immediately to address 000008h or 000018h, depending on the priority level. Individual interrupts can be disabled through their corresponding enable bits.

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PICmicro® mid-range devices. In Compatibility mode, the interrupt priority bits for each source have no effect. INTCON<6> is the PEIE bit, which enables/disables all peripheral interrupt sources. INTCON<7> is the GIE bit, which enables/disables all interrupt sources. All interrupts branch to address 000008h in Compatibility mode.

When an interrupt is responded to, the Global Interrupt Enable bit is cleared to disable further interrupts. If the IPEN bit is cleared, this is the GIE bit. If interrupt priority levels are used, this will be either the GIEH or GIEL bit. High priority interrupt sources can interrupt a low priority interrupt.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (000008h or 000018h). Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bits must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit (GIEH or GIEL if priority levels are used), which re-enables interrupts.

For external interrupt events, such as the INT pins or the PORTB input change interrupt, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding enable bit or the GIE bit.

Note:

Do not use the MOVFF instruction to modify any of the Interrupt control registers while **any** interrupt is enabled. Doing so may cause erratic microcontroller behavior.

TABLE 9-5: PORTC FUNCTIONS

| Name            | Bit# | Buffer Type | Function                                                                                                                                  |

|-----------------|------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| RC0/T1OSO/T1CKI | bit0 | ST          | Input/output port pin or Timer1 oscillator output/Timer1 clock input.                                                                     |

| RC1/T1OSI/CCP2  | bit1 | ST          | Input/output port pin, Timer1 oscillator input, or Capture2 input/<br>Compare2 output/PWM output when CCP2MX configuration bit is<br>set. |

| RC2/CCP1        | bit2 | ST          | Input/output port pin or Capture1 input/Compare1 output/PWM1 output.                                                                      |

| RC3/SCK/SCL     | bit3 | ST          | RC3 can also be the synchronous serial clock for both SPI and I <sup>2</sup> C modes.                                                     |

| RC4/SDI/SDA     | bit4 | ST          | RC4 can also be the SPI Data In (SPI mode) or Data I/O (I <sup>2</sup> C mode).                                                           |

| RC5/SDO         | bit5 | ST          | Input/output port pin or Synchronous Serial Port data output.                                                                             |

| RC6/TX/CK       | bit6 | ST          | Input/output port pin, Addressable USART Asynchronous Transmit, or Addressable USART Synchronous Clock.                                   |

| RC7/RX/DT       | bit7 | ST          | Input/output port pin, Addressable USART Asynchronous Receive, or Addressable USART Synchronous Data.                                     |

Legend: ST = Schmitt Trigger input

TABLE 9-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Name  | Bit 7                     | Bit 6       | Bit 5       | Bit 4 | Bit 3     | Bit 2     | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |

|-------|---------------------------|-------------|-------------|-------|-----------|-----------|-------|-------|----------------------|---------------------------------|

| PORTC | RC7                       | RC6         | RC5         | RC4   | RC3       | RC2       | RC1   | RC0   | xxxx xxxx            | uuuu uuuu                       |

| LATC  | LATC Data Output Register |             |             |       |           |           |       |       | xxxx xxxx            | uuuu uuuu                       |

| TRISC | PORTC I                   | Data Direct | ion Registe |       | 1111 1111 | 1111 1111 |       |       |                      |                                 |

Legend: x = unknown, u = unchanged

#### 10.0 TIMERO MODULE

The Timer0 module has the following features:

- Software selectable as an 8-bit or 16-bit timer/ counter

- · Readable and writable

- Dedicated 8-bit software programmable prescaler

- · Clock source selectable to be external or internal

- Interrupt-on-overflow from FFh to 00h in 8-bit mode and FFFFh to 0000h in 16-bit mode

- Edge select for external clock

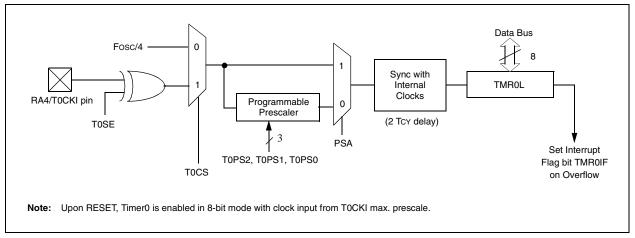

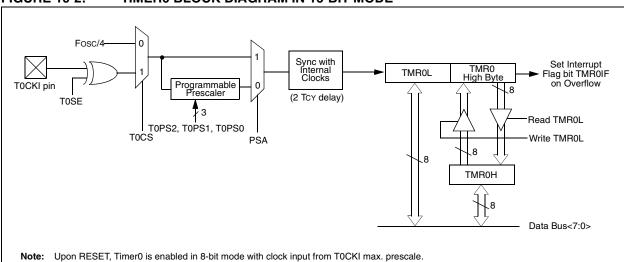

Figure 10-1 shows a simplified block diagram of the Timer0 module in 8-bit mode and Figure 10-2 shows a simplified block diagram of the Timer0 module in 16-bit mode.

The TOCON register (Register 10-1) is a readable and writable register that controls all the aspects of Timer0, including the prescale selection.

#### REGISTER 10-1: TOCON: TIMERO CONTROL REGISTER

| R/W-1  | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|--------|--------|-------|-------|-------|-------|-------|-------|

| TMR00N | T08BIT | T0CS  | T0SE  | PSA   | T0PS2 | T0PS1 | T0PS0 |

| bit 7  |        |       |       |       |       |       | bit 0 |

bit 7 TMR0ON: Timer0 On/Off Control bit

1 = Enables Timer0

0 = Stops Timer0

bit 6 T08BIT: Timer0 8-bit/16-bit Control bit

1 = Timer0 is configured as an 8-bit timer/counter

0 = Timer0 is configured as a 16-bit timer/counter

bit 5 TOCS: Timer0 Clock Source Select bit

1 = Transition on TOCKI pin

0 = Internal instruction cycle clock (CLKO)

bit 4 T0SE: Timer0 Source Edge Select bit

1 = Increment on high-to-low transition on TOCKI pin

0 = Increment on low-to-high transition on T0CKI pin

bit 3 PSA: Timer0 Prescaler Assignment bit

1 = TImer0 prescaler is NOT assigned. Timer0 clock input bypasses prescaler.

0 = Timer0 prescaler is assigned. Timer0 clock input comes from prescaler output.

bit 2-0 T0PS2:T0PS0: Timer0 Prescaler Select bits

111 = 1:256 prescale value

110 = 1:128 prescale value

101 = 1:64 prescale value

100 = 1:32 prescale value

011 = 1:16 prescale value

010 = 1:8 prescale value

001 = 1:4 prescale value

000 = 1:2 prescale value

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### FIGURE 10-1: TIMERO BLOCK DIAGRAM IN 8-BIT MODE

### FIGURE 10-2: TIMERO BLOCK DIAGRAM IN 16-BIT MODE

NOTES:

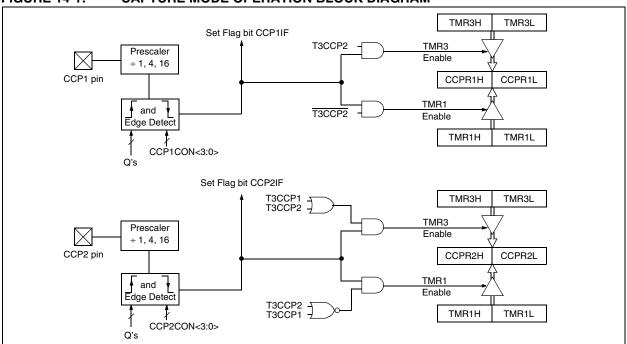

#### 14.3 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 or TMR3 registers when an event occurs on pin RC2/CCP1. An event is defined as one of the following:

- · every falling edge

- · every rising edge

- · every 4th rising edge

- · every 16th rising edge

The event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set; it must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value is overwritten by the new captured value.

## 14.3.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

**Note:** If the RC2/CCP1 is configured as an output, a write to the port can cause a capture condition.

#### 14.3.2 TIMER1/TIMER3 MODE SELECTION

The timers that are to be used with the capture feature (either Timer1 and/or Timer3) must be running in Timer mode or Synchronized Counter mode. In Asynchronous Counter mode, the capture operation may not work. The timer to be used with each CCP module is selected in the T3CON register.

#### 14.3.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit, CCP1IF, following any such change in Operating mode.

#### 14.3.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any RESET will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore, the first capture may be from a non-zero prescaler. Example 14-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

# EXAMPLE 14-1: CHANGING BETWEEN CAPTURE PRESCALERS

```

CLRF CCP1CON, F; Turn CCP module off

MOVLW NEW_CAPT_PS; Load WREG with the

; new prescaler mode

; value and CCP ON

MOVWF CCP1CON ; Load CCP1CON with

; this value

```

FIGURE 14-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 15.4.4 CLOCK STRETCHING

Both 7- and 10-bit Slave modes implement automatic clock stretching during a transmit sequence.

The SEN bit (SSPCON2<0>) allows clock stretching to be enabled during receives. Setting SEN will cause the SCL pin to be held low at the end of each data receive sequence.

# 15.4.4.1 Clock Stretching for 7-bit Slave Receive Mode (SEN = 1)

In 7-bit Slave Receive mode, on the falling edge of the ninth clock at the end of the  $\overline{ACK}$  sequence, if the BF bit is set, the CKP bit in the SSPCON1 register is automatically cleared, forcing the SCL output to be held low. The CKP being cleared to '0' will assert the SCL line low. The CKP bit must be set in the user's ISR before reception is allowed to continue. By holding the SCL line low, the user has time to service the ISR and read the contents of the SSPBUF before the master device can initiate another receive sequence. This will prevent buffer overruns from occurring (see Figure 15-13).

- Note 1: If the user reads the contents of the SSPBUF before the falling edge of the ninth clock, thus clearing the BF bit, the CKP bit will not be cleared and clock stretching will not occur.

- 2: The CKP bit can be set in software, regardless of the state of the BF bit. The user should be careful to clear the BF bit in the ISR before the next receive sequence, in order to prevent an overflow condition.

## 15.4.4.2 Clock Stretching for 10-bit Slave Receive Mode (SEN = 1)

In 10-bit Slave Receive mode, during the address sequence, clock stretching automatically takes place but CKP is not cleared. During this time, if the UA bit is set after the ninth clock, clock stretching is initiated. The UA bit is set after receiving the upper byte of the 10-bit address, and following the receive of the second byte of the 10-bit address with the R/W bit cleared to '0'. The release of the clock line occurs upon updating SSPADD. Clock stretching will occur on each data receive sequence as described in 7-bit mode.

Note: If the user polls the UA bit and clears it by updating the SSPADD register before the falling edge of the ninth clock occurs, and if the user hasn't cleared the BF bit by reading the SSPBUF register before that time, then the CKP bit will still NOT be asserted low. Clock stretching on the basis of the state of the BF bit only occurs during a data sequence, not an address sequence.

### 15.4.4.3 Clock Stretching for 7-bit Slave Transmit Mode

7-bit Slave Transmit mode implements clock stretching by clearing the CKP bit after the falling edge of the ninth clock, if the BF bit is clear. This occurs, regardless of the state of the SEN bit.

The user's ISR must set the CKP bit before transmission is allowed to continue. By holding the SCL line low, the user has time to service the ISR and load the contents of the SSPBUF before the master device can initiate another transmit sequence (see Figure 15-9).

- Note 1: If the user loads the contents of SSPBUF, setting the BF bit before the falling edge of the ninth clock, the CKP bit will not be cleared and clock stretching will not occur.

- **2:** The CKP bit can be set in software, regardless of the state of the BF bit.

### 15.4.4.4 Clock Stretching for 10-bit Slave Transmit Mode

In 10-bit Slave Transmit mode, clock stretching is controlled during the first two address sequences by the state of the UA bit, just as it is in 10-bit Slave Receive mode. The first two addresses are followed by a third address sequence, which contains the high order bits of the 10-bit address and the R/W bit set to '1'. After the third address sequence is performed, the UA bit is not set, the module is now configured in Transmit mode, and clock stretching is controlled by the BF flag, as in 7-bit Slave Transmit mode (see Figure 15-11).

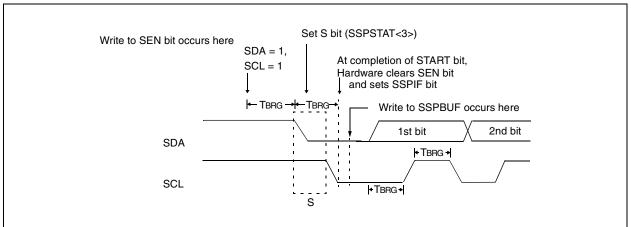

# 15.4.8 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a START condition, the user sets the START condition enable bit, SEN (SSPCON2<0>). If the SDA and SCL pins are sampled high, the baud rate generator is reloaded with the contents of SSPADD<6:0> and starts its count. If SCL and SDA are both sampled high when the baud rate generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low, while SCL is high, is the START condition and causes the S bit (SSPSTAT<3>) to be set. Following this, the baud rate generator is reloaded with the contents of SSPADD<6:0> and resumes its count. When the baud rate generator times out (TBRG), the SEN bit (SSPCON2<0>) will be automatically cleared by hardware, the baud rate generator is suspended. leaving the SDA line held low and the START condition is complete.

Note: If at the beginning of the START condition, the SDA and SCL pins are already sampled low or if during the START condition

IDLE state.

pled low, or if during the START condition the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLIF is set, the START condition is aborted, and the I<sup>2</sup>C module is reset into its 15.4.8.1 WCOL Status Flag

If the user writes the SSPBUF when a START sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

**Note:** Because queueing of events is not allowed, writing to the lower 5 bits of SSPCON2 is disabled until the START condition is complete.

#### FIGURE 15-19: FIRST START BIT TIMING

TABLE 16-3: BAUD RATES FOR SYNCHRONOUS MODE

| BAUD           | Fosc = | 40 MHz     | SPBRG              | 33 1   | VIHz       | SPBRG              | 25 [   | ИНz        | SPBRG              | 20     | MHz        | SPBRG              |

|----------------|--------|------------|--------------------|--------|------------|--------------------|--------|------------|--------------------|--------|------------|--------------------|

| RATE<br>(Kbps) | KBAUD  | %<br>ERROR | value<br>(decimal) |

| 0.3            | NA     | -          | -                  |

| 1.2            | NA     | -          | -                  |

| 2.4            | NA     | -          | -                  |

| 9.6            | NA     | -          | -                  |

| 19.2           | NA     | -          | -                  |

| 76.8           | 76.92  | +0.16      | 129                | 77.10  | +0.39      | 106                | 77.16  | +0.47      | 80                 | 76.92  | +0.16      | 64                 |

| 96             | 96.15  | +0.16      | 103                | 95.93  | -0.07      | 85                 | 96.15  | +0.16      | 64                 | 96.15  | +0.16      | 51                 |

| 300            | 303.03 | +1.01      | 32                 | 294.64 | -1.79      | 27                 | 297.62 | -0.79      | 20                 | 294.12 | -1.96      | 16                 |

| 500            | 500    | 0          | 19                 | 485.30 | -2.94      | 16                 | 480.77 | -3.85      | 12                 | 500    | 0          | 9                  |

| HIGH           | 10000  | -          | 0                  | 8250   | -          | 0                  | 6250   | -          | 0                  | 5000   | -          | 0                  |

| LOW            | 39.06  | -          | 255                | 32.23  | -          | 255                | 24.41  | -          | 255                | 19.53  | -          | 255                |

| BAUD           | Fosc = | 16 MHz     | SPBRG              | 10 [   | ИНz        | SPBRG              | 7.1590  | 9 MHz      | SPBRG              | 5.068   | 8 MHz      | SPBRG              |

|----------------|--------|------------|--------------------|--------|------------|--------------------|---------|------------|--------------------|---------|------------|--------------------|

| RATE<br>(Kbps) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD   | %<br>ERROR | value<br>(decimal) | KBAUD   | %<br>ERROR | value<br>(decimal) |

| 0.3            | NA     | -          | -                  | NA     | -          | -                  | NA      | -          | -                  | NA      | -          | -                  |

| 1.2            | NA     | -          | -                  | NA     | -          | -                  | NA      | -          | -                  | NA      | -          | -                  |

| 2.4            | NA     | -          | -                  | NA     | -          | -                  | NA      | -          | -                  | NA      | -          | -                  |

| 9.6            | NA     | -          | -                  | NA     | -          | -                  | 9.62    | +0.23      | 185                | 9.60    | 0          | 131                |

| 19.2           | 19.23  | +0.16      | 207                | 19.23  | +0.16      | 129                | 19.24   | +0.23      | 92                 | 19.20   | 0          | 65                 |

| 76.8           | 76.92  | +0.16      | 51                 | 75.76  | -1.36      | 32                 | 77.82   | +1.32      | 22                 | 74.54   | -2.94      | 16                 |

| 96             | 95.24  | -0.79      | 41                 | 96.15  | +0.16      | 25                 | 94.20   | -1.88      | 18                 | 97.48   | +1.54      | 12                 |

| 300            | 307.70 | +2.56      | 12                 | 312.50 | +4.17      | 7                  | 298.35  | -0.57      | 5                  | 316.80  | +5.60      | 3                  |

| 500            | 500    | 0          | 7                  | 500    | 0          | 4                  | 447.44  | -10.51     | 3                  | 422.40  | -15.52     | 2                  |

| HIGH           | 4000   | -          | 0                  | 2500   | -          | 0                  | 1789.80 | -          | 0                  | 1267.20 | -          | 0                  |

| LOW            | 15.63  | -          | 255                | 9.77   | -          | 255                | 6.99    | -          | 255                | 4.95    | -          | 255                |

| BAUD           | Fosc = | 4 MHz      | SPBRG              | 3.5795 | 45 MHz     | SPBRG              | 1 N   | 1Hz        | SPBRG              | 32.76 | 8 kHz      | SPBRG              |

|----------------|--------|------------|--------------------|--------|------------|--------------------|-------|------------|--------------------|-------|------------|--------------------|

| RATE<br>(Kbps) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD | %<br>ERROR | value<br>(decimal) | KBAUD | %<br>ERROR | value<br>(decimal) |

| 0.3            | NA     | -          | -                  | NA     | -          | -                  | NA    | -          | -                  | 0.30  | +1.14      | 26                 |

| 1.2            | NA     | -          | -                  | NA     | -          | -                  | 1.20  | +0.16      | 207                | 1.17  | -2.48      | 6                  |

| 2.4            | NA     | -          | -                  | NA     | -          | -                  | 2.40  | +0.16      | 103                | 2.73  | +13.78     | 2                  |

| 9.6            | 9.62   | +0.16      | 103                | 9.62   | +0.23      | 92                 | 9.62  | +0.16      | 25                 | 8.20  | -14.67     | 0                  |

| 19.2           | 19.23  | +0.16      | 51                 | 19.04  | -0.83      | 46                 | 19.23 | +0.16      | 12                 | NA    | -          | -                  |

| 76.8           | 76.92  | +0.16      | 12                 | 74.57  | -2.90      | 11                 | 83.33 | +8.51      | 2                  | NA    | -          | -                  |

| 96             | 1000   | +4.17      | 9                  | 99.43  | +3.57      | 8                  | 83.33 | -13.19     | 2                  | NA    | -          | -                  |

| 300            | 333.33 | +11.11     | 2                  | 298.30 | -0.57      | 2                  | 250   | -16.67     | 0                  | NA    | -          | -                  |

| 500            | 500    | 0          | 1                  | 447.44 | -10.51     | 1                  | NA    | -          | -                  | NA    | -          | -                  |

| HIGH           | 1000   | -          | 0                  | 894.89 | -          | 0                  | 250   | -          | 0                  | 8.20  | -          | 0                  |

| LOW            | 3.91   | -          | 255                | 3.50   | -          | 255                | 0.98  | -          | 255                | 0.03  | -          | 255                |

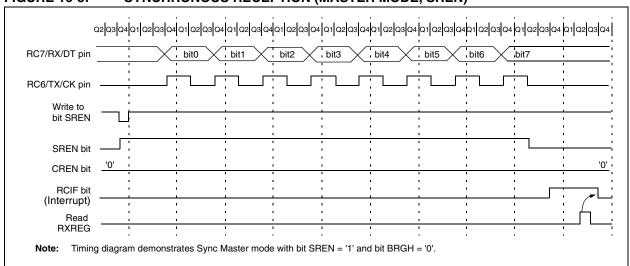

# 16.3.2 USART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either enable bit SREN (RCSTA<5>), or enable bit CREN (RCSTA<4>). Data is sampled on the RC7/RX/DT pin on the falling edge of the clock. If enable bit SREN is set, only a single word is received. If enable bit CREN is set, the reception is continuous until CREN is cleared. If both bits are set, then CREN takes precedence.

To set up a Synchronous Master Reception:

- Initialize the SPBRG register for the appropriate baud rate (Section 16.1).

- Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, set enable bit RCIE.

- 5. If 9-bit reception is desired, set bit RX9.

- 6. If a single reception is required, set bit SREN. For continuous reception, set bit CREN.

- Interrupt flag bit RCIF will be set when reception is complete and an interrupt will be generated if the enable bit RCIE was set.

- 8. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREG register.

- If any error occurred, clear the error by clearing bit CREN.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set

TABLE 16-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

| Name   | Bit 7                  | Bit 6         | Bit 5       | Bit 4  | Bit 3     | Bit 2     | Bit 1  | Bit 0  | Value on POR, BOR | Value on<br>All Other<br>RESETS |

|--------|------------------------|---------------|-------------|--------|-----------|-----------|--------|--------|-------------------|---------------------------------|

| INTCON | GIE/<br>GIEH           | PEIE/<br>GIEL | TMR0IE      | INT0IE | RBIE      | TMR0IF    | INTOIF | RBIF   | 0000 000x         | 0000 000u                       |

| PIR1   | PSPIF <sup>(1)</sup>   | ADIF          | RCIF        | TXIF   | SSPIF     | CCP1IF    | TMR2IF | TMR1IF | 0000 0000         | 0000 0000                       |

| PIE1   | PSPIE <sup>(1)</sup>   | ADIE          | RCIE        | TXIE   | SSPIE     | CCP1IE    | TMR2IE | TMR1IE | 0000 0000         | 0000 0000                       |

| IPR1   | PSPIP <sup>(1)</sup>   | ADIP          | RCIP        | TXIP   | SSPIP     | CCP1IP    | TMR2IP | TMR1IP | 0000 0000         | 0000 0000                       |

| RCSTA  | SPEN                   | RX9           | SREN        | CREN   | ADDEN     | FERR      | OERR   | RX9D   | 0000 -00x         | 0000 -00x                       |

| RCREG  | USART Receive Register |               |             |        |           |           |        |        | 0000 0000         | 0000 0000                       |

| TXSTA  | CSRC                   | TX9           | TXEN        | SYNC   | _         | BRGH      | TRMT   | TX9D   | 0000 -010         | 0000 -010                       |

| SPBRG  | Baud Rate              | e Genera      | tor Registe |        | 0000 0000 | 0000 0000 |        |        |                   |                                 |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for Synchronous Master Reception.

Note 1: The PSPIF, PSPIE and PSPIP bits are reserved on the PIC18F2X2 devices; always maintain these bits clear.

FIGURE 16-8: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

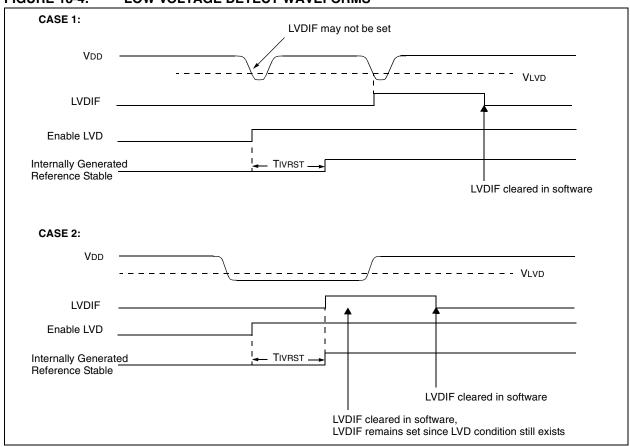

### 18.2 Operation

Depending on the power source for the device voltage, the voltage normally decreases relatively slowly. This means that the LVD module does not need to be constantly operating. To decrease the current requirements, the LVD circuitry only needs to be enabled for short periods, where the voltage is checked. After doing the check, the LVD module may be disabled.

Each time that the LVD module is enabled, the circuitry requires some time to stabilize. After the circuitry has stabilized, all status flags may be cleared. The module will then indicate the proper state of the system.

The following steps are needed to set up the LVD module:

- Write the value to the LVDL3:LVDL0 bits (LVDCON register), which selects the desired LVD Trip Point.

- Ensure that LVD interrupts are disabled (the LVDIE bit is cleared or the GIE bit is cleared).

- 3. Enable the LVD module (set the LVDEN bit in the LVDCON register).

- Wait for the LVD module to stabilize (the IRVST bit to become set).

- Clear the LVD interrupt flag, which may have falsely become set until the LVD module has stabilized (clear the LVDIF bit).

- 6. Enable the LVD interrupt (set the LVDIE and the GIE bits).

Figure 18-4 shows typical waveforms that the LVD module may be used to detect.

FIGURE 18-4: LOW VOLTAGE DETECT WAVEFORMS

# 19.0 SPECIAL FEATURES OF THE CPU

There are several features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving Operating modes and offer code protection. These are:

- · OSC Selection

- RESET

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code Protection

- ID Locations

- · In-Circuit Serial Programming

All PIC18FXX2 devices have a Watchdog Timer, which is permanently enabled via the configuration bits or software controlled. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay on power-up only, designed to keep the part in RESET while the power supply stabilizes. With these two timers on-chip, most applications need no external RESET circuitry.

SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer Wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost, while the LP crystal option saves power. A set of configuration bits are used to select various options.

## 19.1 Configuration Bits

The configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped starting at program memory location 300000h.

The user will note that address 300000h is beyond the user program memory space. In fact, it belongs to the configuration memory space (300000h - 3FFFFFh), which can only be accessed using Table Reads and Table Writes.

Programming the configuration registers is done in a manner similar to programming the FLASH memory (see Section 5.5.1). The only difference is the configuration registers are written a byte at a time. The sequence of events for programming configuration registers is:

- Load table pointer with address of configuration register being written.

- 2. Write a single byte using the TBLWT instruction.

- 3. Set EEPGD to point to program memory, set the CFGS bit to access configuration registers, and set WREN to enable byte writes.

- 4. Disable interrupts.

- 5. Write 55h to EECON2.

- 6. Write AAh to EECON2.

- 7. Set the WR bit. This will begin the write cycle.

- 8. CPU will stall for duration of write (approximately 2 ms using internal timer).

- 9. Execute a NOP.

- 10. Re-enable interrupts.

**NEGF** Negate f [label] NEGF f[,a] Syntax: Operands:  $0 \le f \le 255$  $a \in [0,1]$  $(\overline{f}) + 1 \rightarrow f$ Operation: Status Affected: N, OV, C, DC, Z Encoding: 0110 110a ffff ffff Description: Location 'f' is negated using two's complement. The result is placed in the data memory location 'f'. If 'a' is 0, the Access Bank will be selected, overriding the BSR value. If 'a' = 1, then the bank will be selected as per the BSR value. Words: 1 Cycles: 1

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4           |

|--------|--------------|---------|--------------|

| Decode | Read         | Process | Write        |

|        | register 'f' | Data    | register 'f' |

Example: NEGF REG, 1

Before Instruction

REG = 0011 1010 [0x3A]

After Instruction

REG = 1100 0110 [0xC6]

| NOF                   | •       | No Operation  |      |     |     |      |  |

|-----------------------|---------|---------------|------|-----|-----|------|--|

| Synt                  | ax:     | [ label ]     | NOP  |     |     |      |  |

| Ope                   | rands:  | None          |      |     |     |      |  |

| Ope                   | ration: | No operation  |      |     |     |      |  |

| Status Affected: None |         |               |      |     |     |      |  |

| Enco                  | oding:  | 0000          | 0000 | 000 | 0.0 | 0000 |  |

|                       |         | 1111          | XXXX | XXX | ΚX  | XXXX |  |

| Description:          |         | No operation. |      |     |     |      |  |

| Words:                |         | 1             | 1    |     |     |      |  |

| Cycles:               |         | 1             | 1    |     |     |      |  |

| Q Cycle Activity:     |         |               |      |     |     |      |  |

|                       | Q1      | Q2            | Q    | 3   |     | Q4   |  |

|                       | Decode  | No            | No   |     |     | No   |  |

operation

operation

operation

Example:

None.

# 22.2 DC Characteristics: PIC18FXX2 (Industrial, Extended) PIC18LFXX2 (Industrial)

| DC CHARACTERISTICS |        | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |                 |          |       |                                          |

|--------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------|-------|------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                                                                                                                                                           | Min             | Max      | Units | Conditions                               |

|                    | VIL    | Input Low Voltage                                                                                                                                                                        |                 |          |       |                                          |

|                    |        | I/O ports:                                                                                                                                                                               |                 |          |       |                                          |

| D030               |        | with TTL buffer                                                                                                                                                                          | Vss             | 0.15 VDD | V     | VDD < 4.5V                               |

| D030A              |        |                                                                                                                                                                                          | _               | 0.8      | V     | $4.5V \le VDD \le 5.5V$                  |

| D031               |        | with Schmitt Trigger buffer                                                                                                                                                              | Vss             | 0.2 VDD  | V     |                                          |

|                    |        | RC3 and RC4                                                                                                                                                                              | Vss             | 0.3 VDD  | V     |                                          |

| D032               |        | MCLR                                                                                                                                                                                     | Vss             | 0.2 VDD  | V     |                                          |

| D032A              |        | OSC1 (in XT, HS and LP modes) and T1OSI                                                                                                                                                  | Vss             | 0.3 VDD  | V     |                                          |

| D033               |        | OSC1 (in RC and EC mode) <sup>(1)</sup>                                                                                                                                                  | Vss             | 0.2 VDD  | V     |                                          |

|                    | VIH    | Input High Voltage                                                                                                                                                                       |                 |          |       |                                          |

|                    |        | I/O ports:                                                                                                                                                                               |                 |          |       |                                          |

| D040               |        | with TTL buffer                                                                                                                                                                          | 0.25 VDD + 0.8V | VDD      | V     | VDD < 4.5V                               |

| D040A              |        |                                                                                                                                                                                          | 2.0             | VDD      | V     | $4.5V \le VDD \le 5.5V$                  |

| D041               |        | with Schmitt Trigger buffer                                                                                                                                                              | 0.8 VDD         | VDD      | V     |                                          |

|                    |        | RC3 and RC4                                                                                                                                                                              | 0.7 VDD         | VDD      | V     |                                          |

| D042               |        | MCLR, OSC1 (EC mode)                                                                                                                                                                     | 0.8 VDD         | VDD      | V     |                                          |

| D042A              |        | OSC1 (in XT, HS and LP modes) and T1OSI                                                                                                                                                  | 0.7 VDD         | VDD      | V     |                                          |

| D043               |        | OSC1 (RC mode) <sup>(1)</sup>                                                                                                                                                            | 0.9 VDD         | VDD      | V     |                                          |

|                    | lı∟    | Input Leakage Current <sup>(2,3)</sup>                                                                                                                                                   |                 |          |       |                                          |

| D060               |        | I/O ports                                                                                                                                                                                | .02             | ±1       | μΑ    | Vss ≤ Vpin ≤ Vdd,<br>Pin at hi-impedance |

| D061               |        | MCLR                                                                                                                                                                                     | _               | ±1       | μΑ    | $Vss \le VPIN \le VDD$                   |

| D063               |        | OSC1                                                                                                                                                                                     | _               | ±1       | μΑ    | $Vss \le VPIN \le VDD$                   |

|                    | IPU    | Weak Pull-up Current                                                                                                                                                                     |                 |          |       |                                          |

| D070               | IPURB  | PORTB weak pull-up current                                                                                                                                                               | 50              | 450      | μΑ    | VDD = 5V, VPIN = VSS                     |

**Note 1:** In RC oscillator configuration, the OSC1/CLKI pin is a Schmitt Trigger input. It is not recommended that the PICmicro device be driven with an external clock while in RC mode.

<sup>2:</sup> The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

<sup>3:</sup> Negative current is defined as current sourced by the pin.

<sup>4:</sup> Parameter is characterized but not tested.

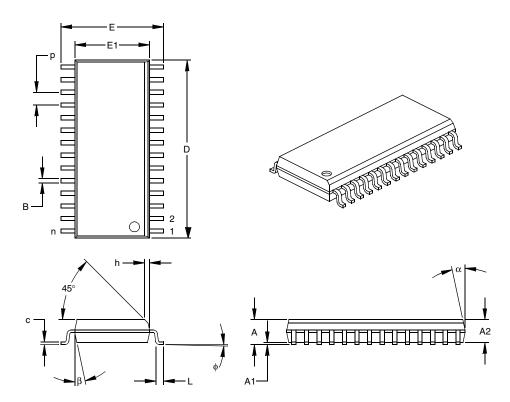

# 28-Lead Plastic Small Outline (SO) - Wide, 300 mil Body (SOIC)

**e:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units    | INCHES*  |                                                                                                    |      | MILLIMETERS |       |       |  |

|----------|----------|----------------------------------------------------------------------------------------------------|------|-------------|-------|-------|--|

| n Limits | MIN      | NOM                                                                                                | MAX  | MIN         | NOM   | MAX   |  |

| n        |          | 28                                                                                                 |      |             | 28    |       |  |

| р        |          | .050                                                                                               |      |             | 1.27  |       |  |

| Α        | .093     | .099                                                                                               | .104 | 2.36        | 2.50  | 2.64  |  |

| A2       | .088     | .091                                                                                               | .094 | 2.24        | 2.31  | 2.39  |  |

| A1       | .004     | .008                                                                                               | .012 | 0.10        | 0.20  | 0.30  |  |

| Е        | .394     | .407                                                                                               | .420 | 10.01       | 10.34 | 10.67 |  |

| E1       | .288     | .295                                                                                               | .299 | 7.32        | 7.49  | 7.59  |  |

| D        | .695     | .704                                                                                               | .712 | 17.65       | 17.87 | 18.08 |  |

| h        | .010     | .020                                                                                               | .029 | 0.25        | 0.50  | 0.74  |  |

| L        | .016     | .033                                                                                               | .050 | 0.41        | 0.84  | 1.27  |  |

| ф        | 0        | 4                                                                                                  | 8    | 0           | 4     | 8     |  |

| С        | .009     | .011                                                                                               | .013 | 0.23        | 0.28  | 0.33  |  |

| В        | .014     | .017                                                                                               | .020 | 0.36        | 0.42  | 0.51  |  |

| α        | 0        | 12                                                                                                 | 15   | 0           | 12    | 15    |  |

| β        | 0        | 12                                                                                                 | 15   | 0           | 12    | 15    |  |

|          | n Limits | n Limits MIN  n p A .093 A2 .088 A1 .004 E .394 E1 .288 D .695 h .010 L .016 φ 0 c .009 B .014 α 0 | Nome | Nome        | Name  | Name  |  |

<sup>\*</sup> Controlling Parameter

#### Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-013

Drawing No. C04-052

<sup>§</sup> Significant Characteristic

| I                                                   |          | Instruction Set | 211 |

|-----------------------------------------------------|----------|-----------------|-----|

| I/O Ports                                           | 87       | ADDLW           | 217 |

| I <sup>2</sup> C (MSSP Module)                      |          | ADDWF           | 217 |

| ACK Pulse                                           | 139      | ADDWFC          | 218 |

| Read/Write Bit Information (R/W Bit)                |          | ANDLW           | 218 |

| I <sup>2</sup> C (SSP Module)                       |          | ANDWF           | 219 |

| ACK Pulse                                           | 138      | BC              | 219 |

| I <sup>2</sup> C Master Mode Reception              |          | BCF             | 220 |

| I <sup>2</sup> C Mode                               |          | BN              | 220 |

| Clock Stretching                                    | 144      | BNC             | 221 |

| I <sup>2</sup> C Mode (MSSP Module)                 |          | BNN             | 221 |

| Registers                                           |          | BNOV            |     |

| I <sup>2</sup> C Module                             |          | BNZ             |     |

| ACK Pulse                                           | 138, 139 | BOV             |     |

| Acknowledge Sequence Timing                         |          | BRA             |     |

| Baud Rate Generator                                 |          | BSF             |     |

| Bus Collision                                       |          | BTFSC           |     |

| Repeated START Condition                            | 162      | BTFSS           |     |

| START Condition                                     |          | BTG             |     |

| Clock Arbitration                                   | 152      | BZ              |     |

| Effect of a RESET                                   | 159      | CALL            |     |

| General Call Address Support                        | 148      | CLRF            |     |

| Master Mode                                         | 149      | CLRWDT          |     |

| Operation                                           | 150      | COMF            |     |

| Repeated START Condition Timing                     | 154      | CPFSEQ          |     |

| Master Mode START Condition                         | 153      | CPFSGT          |     |

| Master Mode Transmission                            | 155      | CPFSLT          |     |

| Multi-Master Communication, Bus Collision           |          | DAW             |     |

| and Arbitration                                     | 159      | DCFSNZ<br>DECF  | -   |

| Multi-Master Mode                                   |          | DECFSZ          |     |

| Operation                                           | 138      | GOTO            |     |

| Read/Write Bit Information (R/W Bit)                |          | INCF            | -   |

| Serial Clock (RC3/SCK/SCL)                          | 139      | INCFSZ          |     |

| Slave Mode                                          | 138      | INFSNZ          |     |

| Addressing                                          |          | IORLW           |     |

| Reception                                           | 139      | IORWF           |     |

| Transmission                                        | 139      | LFSR            |     |

| Slave Mode Timing (10-bit Reception,                |          | MOVF            |     |

| SEN = 0)                                            | 142      | MOVFF           |     |

| Slave Mode Timing (10-bit Reception,                |          | MOVLB           |     |

| SEN = 1)                                            |          | MOVLW           |     |

| Slave Mode Timing (10-bit Transmission)             | 143      | MOVWF           | -   |

| Slave Mode Timing (7-bit Reception,                 |          | MULLW           |     |

| SEN = 0)                                            | 140      | MULWF           |     |

| Slave Mode Timing (7-bit Reception,                 |          | NEGF            |     |

| SEN = 1)                                            |          | NOP             |     |

| Slave Mode Timing (7-bit Transmission)              |          | POP             |     |

| SLEEP Operation                                     |          | PUSH            | 240 |

| STOP Condition Timing                               |          | RCALL           |     |

| ICEPIC In-Circuit Emulator                          |          | RESET           | 241 |

| ID Locations                                        |          | RETFIE          |     |

| INCF                                                |          | RETLW           | 242 |

| INCFSZ                                              |          | RETURN          | 243 |

| In-Circuit Debugger                                 |          | RLCF            | 243 |

| In-Circuit Serial Programming (ICSP)                |          | RLNCF           | 244 |

| Indirect Addressing                                 |          | RRCF            | 244 |

| INDF and FSR RegistersIndirect Addressing Operation |          | RRNCF           | 245 |

| Indirect Addressing OperationIndirect File Operand  |          | SETF            | 245 |

| INFSNZINFSNZ                                        |          | SLEEP           | 246 |

| Instruction Cycle                                   |          | SUBFWB          | 246 |

| Instruction GydeInstruction Flow/Pipelining         |          | SUBLW           | 247 |

| Instruction Format                                  |          | SUBWF           | 247 |

|                                                     | 210      | SUBWFB          | 248 |

|                                                     |          | SWAPF           | 248 |

| TELWT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| STFSZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 125 |

| XORLW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 120 |

| Non-Wissels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| Summary Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| Instructions in Program Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 45  |

| Memory Programming Requirements   Memory Programming Requirements   Migration from Baseline to Enhanced Devices   Migration from High-End to Enhanced Devices  |     |

| INT Interrupt (HBUNIN). See Interrupt Sources   INTOON Register   90   INTCON Register   90   INTO MOVF   90   INTO MOVE   90   INTO MPLAB C18 C Compilers   90   INTO MPLAB C18 C MOVLE   90   INTO MPLAB C18 C Compilers   90   INTO MPLAB C18 C MOVLE   90   INTO MPLAB C18 C MOVLE   90   INTO MPLAB C18 C MOVLE   90   INTO MPLAB C |     |

| NTCON Register   Self Bit   Sel |     |