Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 40MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                              |

| Number of I/O              | 34                                                                      |

| Program Memory Size        | 32KB (16K x 16)                                                         |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 256 x 8                                                                 |

| RAM Size                   | 1.5K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                             |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

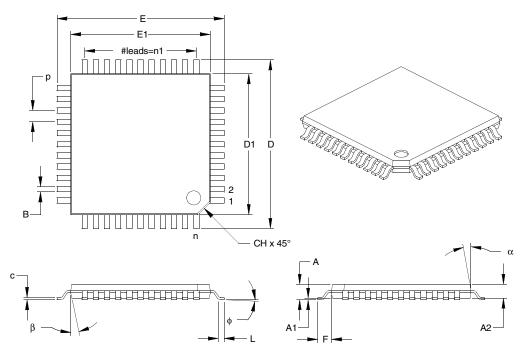

| Package / Case             | 44-LCC (J-Lead)                                                         |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f452-i-l |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- · Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, PowerSmart, rfPIC and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Migratable Memory, MXDEV, MXLAB, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Linear Active Thermistor, Mindi, MiWi, MPASM, MPLIB, MPLINK, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, rfPICDEM, Select Mode, Smart Serial, SmartTel, Total Endurance, UNI/O, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2006, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

QUALITY MANAGEMENT SYSTEM

CERTIFIED BY DNV

ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and water fabrication facilities in Chandler and Tempe, Arizona, Gresham, Oregon and Mountain View, California. The Company's quality system processes and procedures are for its PICmicro® 8-bit MCUs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# 28/40-pin High Performance, Enhanced FLASH Microcontrollers with 10-Bit A/D

#### **High Performance RISC CPU:**

- · C compiler optimized architecture/instruction set

- Source code compatible with the PIC16 and PIC17 instruction sets

- Linear program memory addressing to 32 Kbytes

- · Linear data memory addressing to 1.5 Kbytes

| Device    |                  | hip Program<br>Memory      | On-Chip<br>RAM | Data<br>EEPROM |  |

|-----------|------------------|----------------------------|----------------|----------------|--|

| Device    | FLASH<br>(bytes) | # Single Word Instructions | (bytes)        | (bytes)        |  |

| PIC18F242 | 16K              | 8192                       | 768            | 256            |  |

| PIC18F252 | 32K              | 16384                      | 1536           | 256            |  |

| PIC18F442 | 16K              | 8192                       | 768            | 256            |  |

| PIC18F452 | 32K              | 16384                      | 1536           | 256            |  |

- Up to 10 MIPs operation:

- DC 40 MHz osc./clock input

- 4 MHz 10 MHz osc./clock input with PLL active

- 16-bit wide instructions, 8-bit wide data path

- Priority levels for interrupts

- 8 x 8 Single Cycle Hardware Multiplier

#### **Peripheral Features:**

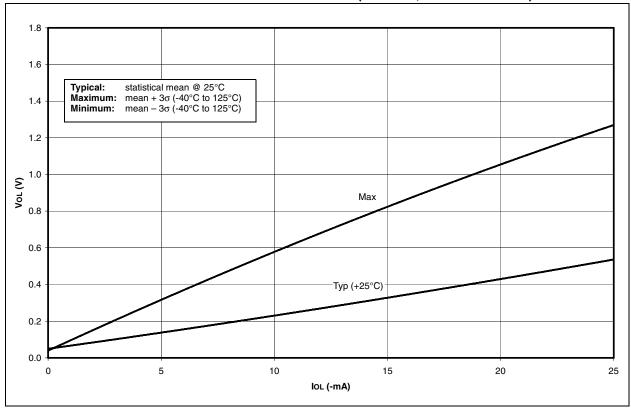

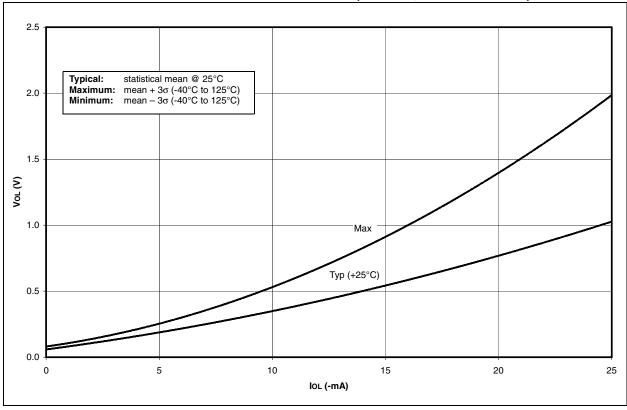

- High current sink/source 25 mA/25 mA

- Three external interrupt pins

- Timer0 module: 8-bit/16-bit timer/counter with 8-bit programmable prescaler

- Timer1 module: 16-bit timer/counter

- Timer2 module: 8-bit timer/counter with 8-bit period register (time-base for PWM)

- Timer3 module: 16-bit timer/counter

- Secondary oscillator clock option Timer1/Timer3

- Two Capture/Compare/PWM (CCP) modules. CCP pins that can be configured as:

- Capture input: capture is 16-bit, max. resolution 6.25 ns (Tcy/16)

- Compare is 16-bit, max. resolution 100 ns (Tcy)

- PWM output: PWM resolution is 1- to 10-bit, max. PWM freq. @: 8-bit resolution = 156 kHz 10-bit resolution = 39 kHz

- Master Synchronous Serial Port (MSSP) module, Two modes of operation:

- 3-wire SPI™ (supports all 4 SPI modes)

- I<sup>2</sup>C™ Master and Slave mode

#### Peripheral Features (Continued):

- · Addressable USART module:

- Supports RS-485 and RS-232

- Parallel Slave Port (PSP) module

#### **Analog Features:**

- Compatible 10-bit Analog-to-Digital Converter module (A/D) with:

- Fast sampling rate

- Conversion available during SLEEP

- Linearity ≤ 1 LSb

- Programmable Low Voltage Detection (PLVD)

- Supports interrupt on-Low Voltage Detection

- Programmable Brown-out Reset (BOR)

#### **Special Microcontroller Features:**

- 100,000 erase/write cycle Enhanced FLASH program memory typical

- 1,000,000 erase/write cycle Data EEPROM memory

- FLASH/Data EEPROM Retention: > 40 years

- Self-reprogrammable under software control

- Power-on Reset (POR), Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Watchdog Timer (WDT) with its own On-Chip RC Oscillator for reliable operation

- Programmable code protection

- · Power saving SLEEP mode

- Selectable oscillator options including:

- 4X Phase Lock Loop (of primary oscillator)

- Secondary Oscillator (32 kHz) clock input

- Single supply 5V In-Circuit Serial Programming™ (ICSP™) via two pins

- · In-Circuit Debug (ICD) via two pins

#### **CMOS Technology:**

- Low power, high speed FLASH/EEPROM technology

- Fully static design

- Wide operating voltage range (2.0V to 5.5V)

- Industrial and Extended temperature ranges

- Low power consumption:

- < 1.6 mA typical @ 5V, 4 MHz

- 25 μA typical @ 3V, 32 kHz

- < 0.2 μA typical standby current

TABLE 1-3: PIC18F4X2 PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name                | Pi     | n Numb | er    | Pin  | Buffer              | Description                                                                                                                                                                |

|-------------------------|--------|--------|-------|------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pili Name               | DIP    | PLCC   | TQFP  | Туре | Type                | Description                                                                                                                                                                |

|                         |        |        |       |      |                     | PORTD is a bi-directional I/O port, or a Parallel Slave Port (PSP) for interfacing to a microprocessor port. These pins have TTL input buffers when PSP module is enabled. |

| RD0/PSP0                | 19     | 21     | 38    | I/O  | ST<br>TTL           | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                  |

| RD1/PSP1                | 20     | 22     | 39    | I/O  | ST<br>TTL           | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                  |

| RD2/PSP2                | 21     | 23     | 40    | I/O  | ST<br>TTL           | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                  |

| RD3/PSP3                | 22     | 24     | 41    | I/O  | ST<br>TTL           | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                  |

| RD4/PSP4                | 27     | 30     | 2     | I/O  | ST<br>TTL           | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                  |

| RD5/PSP5                | 28     | 31     | 3     | I/O  | ST<br>TTL           | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                  |

| RD6/PSP6                | 29     | 32     | 4     | I/O  | ST<br>TTL           | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                  |

| RD7/PSP7                | 30     | 33     | 5     | I/O  | ST<br>TTL           | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                  |

| RE0/RD/AN5<br>RE0<br>RD | 8      | 9      | 25    | I/O  | ST<br>TTL           | PORTE is a bi-directional I/O port.  Digital I/O.  Read control for parallel slave port (see also WR and CS pins).                                                         |

| AN5<br>RE1/WR/AN6       | 9      | 10     | 26    | I/O  | Analog              | Analog input 5.                                                                                                                                                            |

| RE1<br>WR               |        |        | -     |      | ST<br>TTL<br>Analog | Digital I/O. Write control for parallel slave port (see CS and RD pins). Analog input 6.                                                                                   |

| RE2/CS/AN7<br>RE2       | 10     | 11     | 27    | I/O  | ST                  | Digital I/O.                                                                                                                                                               |

| CS                      |        |        |       |      | TTL                 | Chip Select control for parallel slave port (see related RD and WR).                                                                                                       |

| AN7                     |        |        |       |      | Analog              | Analog input 7.                                                                                                                                                            |

| Vss                     |        | 13, 34 |       | Р    | _                   | Ground reference for logic and I/O pins.                                                                                                                                   |

| VDD                     | 11, 32 | 12, 35 | 7, 28 | Р    | _                   | Positive supply for logic and I/O pins.                                                                                                                                    |

Legend: TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

O = Output

OD = Open Drain (no P diode to VDD)

CMOS = CMOS compatible input or output

I = Input

P = Power

TABLE 4-2: REGISTER FILE SUMMARY (CONTINUED)

| File Name            | Bit 7                | Bit 6                                   | Bit 5          | Bit 4         | Bit 3         | Bit 2                   | Bit 1          | Bit 0  | Value on POR, BOR | Details on page: |

|----------------------|----------------------|-----------------------------------------|----------------|---------------|---------------|-------------------------|----------------|--------|-------------------|------------------|

| IPR2                 | _                    | _                                       |                |               |               |                         |                | 1 1111 | 83                |                  |

| PIR2                 | _                    | _                                       | _              | 0 0000        | 79            |                         |                |        |                   |                  |

| PIE2                 | _                    | -                                       | -              | EEIE          | BCLIE         | LVDIE                   | TMR3IE         | CCP2IE | 0 0000            | 81               |

| IPR1                 | PSPIP <sup>(3)</sup> | ADIP                                    | RCIP           | TXIP          | SSPIP         | CCP1IP                  | TMR2IP         | TMR1IP | 1111 1111         | 82               |

| PIR1                 | PSPIF <sup>(3)</sup> | ADIF                                    | RCIF           | TXIF          | SSPIF         | CCP1IF                  | TMR2IF         | TMR1IF | 0000 0000         | 78               |

| PIE1                 | PSPIE <sup>(3)</sup> | ADIE                                    | RCIE           | TXIE          | SSPIE         | CCP1IE                  | TMR2IE         | TMR1IE | 0000 0000         | 80               |

| TRISE(3)             | IBF                  | OBF                                     | IBOV           | PSPMODE       | _             | Data Direction          | on bits for PC | RTE    | 0000 -111         | 98               |

| TRISD(3)             | Data Directi         | on Control Re                           | egister for PC | RTD           |               |                         |                |        | 1111 1111         | 96               |

| TRISC                | Data Directi         | on Control Re                           | egister for PC | RTC           |               |                         |                |        | 1111 1111         | 93               |

| TRISB                | Data Directi         | on Control Re                           | egister for PC | RTB           |               |                         |                |        | 1111 1111         | 90               |

| TRISA                | _                    | TRISA6 <sup>(1)</sup>                   | Data Direction | on Control Re | gister for PO | RTA                     |                |        | -111 1111         | 87               |

| LATE <sup>(3)</sup>  | _                    | _                                       | _              | _             | _             | Read PORT<br>Write PORT |                | *      | xxx               | 99               |

| LATD <sup>(3)</sup>  | Read PORT            | D Data Latch                            | , Write POR    | ΓD Data Latch | 1             |                         |                |        | xxxx xxxx         | 95               |

| LATC                 | Read PORT            | C Data Latch                            | , Write POR    | ΓC Data Latch | 1             |                         |                |        | xxxx xxxx         | 93               |

| LATB                 | Read PORT            | B Data Latch                            | , Write POR    | TB Data Latch | 1             |                         |                |        | xxxx xxxx         | 90               |

| LATA                 | _                    | LATA6 <sup>(1)</sup>                    | Read PORT      | A Data Latch, | Write PORT    | A Data Latch            | (1)            |        | -xxx xxxx         | 87               |

| PORTE <sup>(3)</sup> | Read PORT            | Read PORTE pins, Write PORTE Data Latch |                |               |               |                         |                |        |                   |                  |

| PORTD <sup>(3)</sup> | Read PORT            |                                         | xxxx xxxx      | 95            |               |                         |                |        |                   |                  |

| PORTC                | Read PORT            |                                         | xxxx xxxx      | 93            |               |                         |                |        |                   |                  |

| PORTB                | Read PORT            | B pins, Write                           | ·              | xxxx xxxx     | 90            |                         |                |        |                   |                  |

| PORTA                | _                    | RA6 <sup>(1)</sup>                      | Read PORT      | A pins, Write | PORTA Data    | Latch <sup>(1)</sup>    |                |        | -x0x 0000         | 87               |

$\label{eq:local_local_local} \textbf{Legend:} \quad \textbf{x} = \textbf{unknown}, \, \textbf{u} = \textbf{unchanged}, \, \textbf{-} = \textbf{unimplemented}, \, \textbf{q} = \textbf{value depends on condition}$

Note 1: RA6 and associated bits are configured as port pins in RCIO and ECIO Oscillator mode only and read '0' in all other Oscillator modes.

<sup>2:</sup> Bit 21 of the TBLPTRU allows access to the device configuration bits.

<sup>3:</sup> These registers and bits are reserved on the PIC18F2X2 devices; always maintain these clear.

NOTES:

#### REGISTER 6-1: EECON1 REGISTER (ADDRESS FA6h)

| R/W-x | R/W-x | U-0 | R/W-0 | R/W-x | R/W-0 | R/S-0 | R/S-0 |

|-------|-------|-----|-------|-------|-------|-------|-------|

| EEPGD | CFGS  | _   | FREE  | WRERR | WREN  | WR    | RD    |

| bit 7 |       |     |       |       |       |       | bit 0 |

bit 7 **EEPGD:** FLASH Program or Data EEPROM Memory Select bit

1 = Access FLASH Program memory 0 = Access Data EEPROM memory

bit 6 CFGS: FLASH Program/Data EE or Configuration Select bit

1 = Access Configuration or Calibration registers

0 = Access FLASH Program or Data EEPROM memory

bit 5 **Unimplemented:** Read as '0'

bit 4 FREE: FLASH Row Erase Enable bit

1 = Erase the program memory row addressed by TBLPTR on the next WR command (cleared by completion of erase operation)

0 = Perform write only

bit 3 WRERR: FLASH Program/Data EE Error Flag bit

1 = A write operation is prematurely terminated (any  $\overline{\text{MCLR}}$  or any WDT Reset during self-timed programming in normal operation)

0 = The write operation completed

**Note:** When a WRERR occurs, the EEPGD or FREE bits are not cleared. This allows tracing of the error condition.

bit 2 WREN: FLASH Program/Data EE Write Enable bit

1 = Allows write cycles

0 = Inhibits write to the EEPROM

bit 1 WR: Write Control bit

1 = Initiates a data EEPROM erase/write cycle or a program memory erase cycle or write cycle. (The operation is self-timed and the bit is cleared by hardware once write is complete. The WR bit can only be set (not cleared) in software.)

0 = Write cycle to the EEPROM is complete

bit 0 RD: Read Control bit

1 = Initiates an EEPROM read

(Read takes one cycle. RD is cleared in hardware. The RD bit can only be set (not cleared) in software. RD bit cannot be set when EEPGD = 1.)

0 = Does not initiate an EEPROM read

Legend:

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as '0'

n = Value at POR

'1' = Bit is set

'0' = Bit is cleared x = Bit is unknown

TABLE 9-1: PORTA FUNCTIONS

| Name             | Bit# | Buffer | Function                                                                                                     |

|------------------|------|--------|--------------------------------------------------------------------------------------------------------------|

| RA0/AN0          | bit0 | TTL    | Input/output or analog input.                                                                                |

| RA1/AN1          | bit1 | TTL    | Input/output or analog input.                                                                                |

| RA2/AN2/VREF-    | bit2 | TTL    | Input/output or analog input or VREF                                                                         |

| RA3/AN3/VREF+    | bit3 | TTL    | Input/output or analog input or VREF+.                                                                       |

| RA4/T0CKI        | bit4 | ST     | Input/output or external clock input for Timer0. Output is open drain type.                                  |

| RA5/SS/AN4/LVDIN | bit5 | TTL    | Input/output or slave select input for synchronous serial port or analog input, or low voltage detect input. |

| OSC2/CLKO/RA6    | bit6 | TTL    | OSC2 or clock output or I/O pin.                                                                             |

Legend: TTL = TTL input, ST = Schmitt Trigger input

TABLE 9-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Name   | Bit 7 | Bit 6    | Bit 5       | Bit 4       | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | Value on<br>All Other<br>RESETS |

|--------|-------|----------|-------------|-------------|-------|-------|-------|-------|-------------------------|---------------------------------|

| PORTA  | _     | RA6      | RA5         | RA4         | RA3   | RA2   | RA1   | RA0   | -x0x 0000               | -u0u 0000                       |

| LATA   | _     | LATA Dat | a Output F  | Register    |       |       |       |       | -xxx xxxx               | -uuu uuuu                       |

| TRISA  | _     | PORTA D  | ata Directi | on Register |       |       |       |       | -111 1111               | -111 1111                       |

| ADCON1 | ADFM  | ADCS2    | -           |             | PCFG3 | PCFG2 | PCFG1 | PCFG0 | 00 0000                 | 00 0000                         |

$\label{eq:locations} \textbf{Legend:} \quad \textbf{x} = \textbf{unknown}, \ \textbf{u} = \textbf{unchanged}, \ \textbf{-} = \textbf{unimplemented locations read as '0'}. \ \textbf{Shaded cells are not used by PORTA}.$

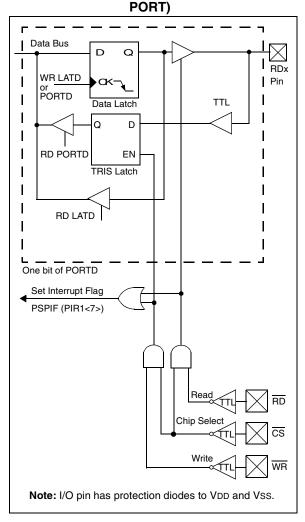

#### 9.6 Parallel Slave Port

The Parallel Slave Port is implemented on the 40-pin devices only (PIC18F4X2).

PORTD operates as an 8-bit wide Parallel Slave Port, or microprocessor port when control bit, PSPMODE (TRISE<4>) is set. It is asynchronously readable and writable by the external world through RD control input pin, RE0/RD and WR control input pin, RE1/WR.

It can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting bit PSPMODE enables port pin RE0/RD to be the  $\overline{RD}$  input,  $\overline{RE1/WR}$  to be the  $\overline{WR}$  input and RE2/ $\overline{CS}$  to be the  $\overline{CS}$  (chip select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set). The A/D port configuration bits PCFG2:PCFG0 (ADCON1<2:0>) must be set, which will configure pins RE2:RE0 as digital I/O.

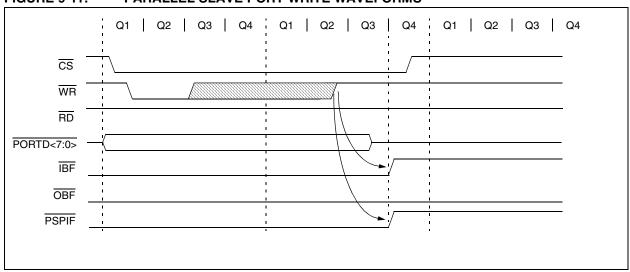

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$  lines are first detected low. A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low.

The PORTE I/O pins become control inputs for the microprocessor port when bit PSPMODE (TRISE<4>) is set. In this mode, the user must make sure that the TRISE<2:0> bits are set (pins are configured as digital inputs), and the ADCON1 is configured for digital I/O. In this mode, the input buffers are TTL.

FIGURE 9-10: PORTD AND PORTE BLOCK DIAGRAM (PARALLEL SLAVE

FIGURE 9-11: PARALLEL SLAVE PORT WRITE WAVEFORMS

#### 14.5.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

TABLE 14-4: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 40 MHz

| PWM Frequency              | 2.44 kHz | 9.77 kHz | 39.06 kHz | 156.25 kHz | 312.50 kHz | 416.67 kHz |

|----------------------------|----------|----------|-----------|------------|------------|------------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1          | 1          | 1          |

| PR2 Value                  | 0xFF     | 0xFF     | 0xFF      | 0x3F       | 0x1F       | 0x17       |

| Maximum Resolution (bits)  | 14       | 12       | 10        | 8          | 7          | 6.58       |

TABLE 14-5: REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Name    | Bit 7                                                          | Bit 6         | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Valu<br>POR, | e on<br>BOR | All C | e on<br>Other<br>SETS |

|---------|----------------------------------------------------------------|---------------|-------------|---------|---------|--------|---------|---------|--------------|-------------|-------|-----------------------|

| INTCON  | GIE/GIEH                                                       | PEIE/GIEL     | TMR0IE      | INT0IE  | RBIE    | TMR0IF | INT0IF  | RBIF    | 0000         | 000x        | 0000  | 000u                  |

| PIR1    | PSPIF <sup>(1)</sup> ADIF RCIF TXIF SSPIF CCP1IF TMR2IF TMR1IF |               |             |         |         |        |         |         | 0000         | 0000        | 0000  | 0000                  |

| PIE1    | PSPIE <sup>(1)</sup>                                           | ADIE          | RCIE        | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000         | 0000        | 0000  | 0000                  |

| IPR1    | PSPIP <sup>(1)</sup>                                           | ADIP          | RCIP        | TXIP    | SSPIP   | CCP1IP | TMR2IP  | TMR1IP  | 0000         | 0000        | 0000  | 0000                  |

| TRISC   | PORTC Da                                                       | ata Direction | Register    |         |         |        |         |         | 1111         | 1111        | 1111  | 1111                  |

| TMR2    | Timer2 Mo                                                      | dule Registe  | er          |         |         |        |         |         | 0000         | 0000        | 0000  | 0000                  |

| PR2     | Timer2 Mo                                                      | dule Period   | Register    |         |         |        |         |         | 1111         | 1111        | 1111  | 1111                  |

| T2CON   | 1                                                              | TOUTPS3       | TOUTPS2     | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000         | 0000        | -000  | 0000                  |

| CCPR1L  | Capture/Co                                                     | ompare/PWI    | M Register1 | (LSB)   |         |        |         |         | xxxx         | xxxx        | uuuu  | uuuu                  |

| CCPR1H  | Capture/Co                                                     | ompare/PWI    | M Register1 | (MSB)   |         |        |         |         | xxxx         | xxxx        | uuuu  | uuuu                  |

| CCP1CON | - DC1B1 DC1B0 CCP1M3 CCP1M2 CCP1M1 CCP1M0                      |               |             |         |         |        |         |         |              | 0000        | 00    | 0000                  |

| CCPR2L  | Capture/Compare/PWM Register2 (LSB)                            |               |             |         |         |        |         |         |              | xxxx        | uuuu  | uuuu                  |

| CCPR2H  | Capture/Compare/PWM Register2 (MSB)                            |               |             |         |         |        |         |         |              |             | uuuu  | uuuu                  |

| CCP2CON | DC2B1 DC2B0 CCP2M3 CCP2M2 CCP2M1 CCP2M                         |               |             |         |         |        |         |         | 00           | 0000        | 00    | 0000                  |

$\label{eq:local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_$

Note 1: The PSPIF, PSPIE and PSPIP bits are reserved on the PIC18F2X2 devices; always maintain these bits clear.

### 15.4.10 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address, or the other half of a 10-bit address is accomplished by simply writing a value to the SSPBUF register. This action will set the buffer full flag bit, BF, and allow the baud rate generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted (see data hold time specification parameter 106). SCL is held low for one baud rate generator rollover count (TBRG). Data should be valid before SCL is released high (see data setup time specification parameter 107). When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time if an address match occurred or if data was received properly. The status of ACK is written into the ACKDT bit on the falling edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPIF bit is set and the master clock (baud rate generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 15-21).

After the write to the SSPBUF, each bit of address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will de-assert the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT status bit (SSPCON2<6>). Following the falling edge of the ninth clock transmission of the address, the SSPIF is set, the BF flag is cleared and the baud rate generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

#### 15.4.10.1 BF Status Flag

In Transmit mode, the BF bit (SSPSTAT<0>) is set when the CPU writes to SSPBUF and is cleared when all 8 bits are shifted out.

#### 15.4.10.2 WCOL Status Flag

If the user writes the SSPBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

WCOL must be cleared in software.

#### 15.4.10.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit (SSPCON2<6>) is cleared when the slave has sent an Acknowledge (ACK = 0), and is set when the slave does not Acknowledge (ACK = 1). A slave sends an Acknowledge when it has recognized its address (including a general call) or when the slave has properly received its data.

#### 15.4.11 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the receive enable bit, RCEN (SSPCON2<3>).

**Note:** In the MSSP module, the RCEN bit must be set after the ACK sequence or the RCEN bit will be disregarded.

The baud rate generator begins counting, and on each rollover, the state of the SCL pin changes (high to low/ low to high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag bit is set, the SSPIF flag bit is set and the baud rate generator is suspended from counting, holding SCL low. The MSSP is now in IDLE state, awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception, by setting the Acknowledge sequence enable bit, (SSPCON2<4>).

#### 15.4.11.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when the SSPBUF register is read.

#### 15.4.11.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when 8 bits are received into the SSPSR and the BF flag bit is already set from a previous reception.

#### 15.4.11.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

#### 16.4 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the RC6/TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

### 16.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes are identical, except in the case of the SLEEP mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- If enable bit TXIE is set, the interrupt will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector.

To set up a Synchronous Slave Transmission:

- Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- Clear bits CREN and SREN.

- 3. If interrupts are desired, set enable bit TXIE.

- 4. If 9-bit transmission is desired, set bit TX9.

- Enable the transmission by setting enable bit TXEN.

- If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- Start transmission by loading data to the TXREG register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

TABLE 16-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

| Name   | Bit 7                             | Bit 6         | Bit 5      | Bit 4  | Bit 3     | Bit 2     | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |

|--------|-----------------------------------|---------------|------------|--------|-----------|-----------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE/<br>GIEH                      | PEIE/<br>GIEL | TMR0IE     | INT0IE | RBIE      | TMR0IF    | INTOIF | RBIF   | 0000 000x            | 0000 000u                       |

| PIR1   | PSPIF <sup>(1)</sup>              | ADIF          | RCIF       | TXIF   | SSPIF     | CCP1IF    | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| PIE1   | PSPIE <sup>(1)</sup>              | ADIE          | RCIE       | TXIE   | SSPIE     | CCP1IE    | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| IPR1   | PSPIP <sup>(1)</sup>              | ADIP          | RCIP       | TXIP   | SSPIP     | CCP1IP    | TMR2IP | TMR1IP | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN                              | RX9           | SREN       | CREN   | ADDEN     | FERR      | OERR   | RX9D   | 0000 -00x            | 0000 -00x                       |

| TXREG  | USART T                           | ransmit F     | Register   |        |           |           |        |        | 0000 0000            | 0000 0000                       |

| TXSTA  | CSRC TX9 TXEN SYNC — BRGH TRMT TX |               |            |        |           |           |        | TX9D   | 0000 -010            | 0000 -010                       |

| SPBRG  | Baud Rate                         | e Genera      | tor Regist |        | 0000 0000 | 0000 0000 |        |        |                      |                                 |

Legend: x = unknown, - = unimplemented, read as '0'.

Shaded cells are not used for Synchronous Slave Transmission.

**Note 1:** The PSPIF, PSPIE and PSPIP bits are reserved on the PIC18F2X2 devices; always maintain these bits clear.

### 16.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical, except in the case of the SLEEP mode and bit SREN, which is a "don't care" in Slave mode.

If receive is enabled by setting bit CREN prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR register will transfer the data to the RCREG register, and if enable bit RCIE bit is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector.

To set up a Synchronous Slave Reception:

- Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, set enable bit RCIE.

- 3. If 9-bit reception is desired, set bit RX9.

- 4. To enable reception, set enable bit CREN.

- Flag bit RCIF will be set when reception is complete. An interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit CREN.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set

TABLE 16-11: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

| Name   | Bit 7                              | Bit 6         | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR |      | Valu<br>All C<br>RES | ther |

|--------|------------------------------------|---------------|--------|--------|-------|--------|--------|--------|----------------------|------|----------------------|------|

| INTCON | GIE/<br>GIEH                       | PEIE/<br>GIEL | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF   | 0000                 | 000x | 0000                 | 000u |

| PIR1   | PSPIF <sup>(1)</sup>               | ADIF          | RCIF   | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000                 | 0000 | 0000                 | 0000 |

| PIE1   | PSPIE <sup>(1)</sup>               | ADIE          | RCIE   | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000                 | 0000 | 0000                 | 0000 |

| IPR1   | PSPIP <sup>(1)</sup>               | ADIP          | RCIP   | TXIP   | SSPIP | CCP1IP | TMR2IP | TMR1IP | 0000                 | 0000 | 0000                 | 0000 |

| RCSTA  | SPEN                               | RX9           | SREN   | CREN   | ADDEN | FERR   | OERR   | RX9D   | 0000                 | -00x | 0000                 | -00x |

| RCREG  | USART Receive Register             |               |        |        |       |        |        |        | 0000                 | 0000 | 0000                 | 0000 |

| TXSTA  | CSRC TX9 TXEN SYNC — BRGH TRMT TX9 |               |        |        |       |        |        |        | 0000                 | -010 | 0000                 | -010 |

| SPBRG  | Baud Rate                          | Generat       |        | 0000   | 0000  | 0000   | 0000   |        |                      |      |                      |      |

Legend: x = unknown, - = unimplemented, read as '0'.

Shaded cells are not used for Synchronous Slave Reception.

Note 1: The PSPIF, PSPIE and PSPIP bits are reserved on the PIC18F2X2 devices; always maintain these bits clear.

#### 18.1 Control Register

The Low Voltage Detect Control register controls the operation of the Low Voltage Detect circuitry.

#### REGISTER 18-1: LVDCON REGISTER

| U-0   | U-0 | R-0   | R/W-0 | R/W-0 | R/W-1 | R/W-0 | R/W-1 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| _     | _   | IRVST | LVDEN | LVDL3 | LVDL2 | LVDL1 | LVDL0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

bit 7-6 Unimplemented: Read as '0'

bit 5 IRVST: Internal Reference Voltage Stable Flag bit

- 1 = Indicates that the Low Voltage Detect logic will generate the interrupt flag at the specified voltage range

- 0 = Indicates that the Low Voltage Detect logic will not generate the interrupt flag at the specified voltage range and the LVD interrupt should not be enabled

- bit 4 LVDEN: Low Voltage Detect Power Enable bit

- 1 = Enables LVD, powers up LVD circuit

- 0 = Disables LVD, powers down LVD circuit

- bit 3-0 LVDL3:LVDL0: Low Voltage Detection Limit bits

- 1111 = External analog input is used (input comes from the LVDIN pin)

- 1110 = 4.5V 4.77V

- 1101 = 4.2V 4.45V

- 1100 = 4.0V 4.24V

- 1011 = 3.8V 4.03V

- 1010 = 3.6V 3.82V

- 1001 = 3.5V 3.71V

- 1000 = 3.3V 3.50V

- 0111 = 3.0V 3.18V0110 = 2.8V - 2.97V

- 0110 = 2.00 2.97 V

- 0101 = 2.7V 2.86V

- 0100 = 2.5V 2.65V0011 = 2.4V - 2.54V

- 0011 2.11 2.011

- 0010 = 2.2V 2.33V0001 = 2.0V - 2.12V

- 0000 = Reserved

**Note:** LVDL3:LVDL0 modes which result in a trip point below the valid operating voltage of the device are not tested.

Legend:

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as '0'

n = Value at POR

'1' = Bit is set

'0' = Bit is cleared x = Bit is unknown

ΒZ **Branch if Zero**

Syntax: [label] BZ n Operands:  $-128 \le n \le 127$ Operation: if Zero bit is '1'

$(PC) + 2 + 2n \rightarrow PC$

Status Affected: None

Encoding: 1110 0000 nnnn nnnn

Description: If the Zero bit is '1', then the pro-

gram will branch.

The 2's complement number '2n' is added to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC+2+2n. This instruction is then

a two-cycle instruction.

1 Words: Cycles: 1(2)

Q Cycle Activity: If Jump:

| Q1        | Q2           | Q3        | Q4          |

|-----------|--------------|-----------|-------------|

| Decode    | Read literal | Process   | Write to PC |

|           | 'n'          | Data      |             |

| No        | No           | No        | No          |

| operation | operation    | operation | operation   |

If No Jump:

| Q1     | Q2           | Q3      | Q4        |  |

|--------|--------------|---------|-----------|--|

| Decode | Read literal | Process | No        |  |

|        | 'n'          | Data    | operation |  |

Example: HERE BZJump

Before Instruction

PC address (HERE)

After Instruction

If Zero

PC address (Jump) If Zero

РC address (HERE+2) **CALL Subroutine Call**

Syntax: [label] CALL k[,s]

Operands:  $0 \leq k \leq 1048575$

$s \in [0,1]$

Operation:  $(PC) + 4 \rightarrow TOS$ ,

$k \rightarrow PC < 20:1>$ if s = 1

$(W) \rightarrow WS$ ,

$(STATUS) \rightarrow STATUSS,$

$(BSR) \rightarrow BSRS$

Status Affected: None

Encodina:

kkkk<sub>0</sub> 1st word (k<7:0>) 1110 110s k<sub>7</sub>kkk kkkk<sub>8</sub> 2nd word(k<19:8>) 1111 k<sub>19</sub>kkk kkkk

Description: Subroutine call of entire 2 Mbyte

> memory range. First, return address (PC+4) is pushed onto the return stack. If 's' = 1, the W, STATUS and BSR registers are also pushed into their respective shadow registers, WS, STATUSS and BSRS. If 's' = 0, no update occurs (default). Then, the 20-bit value 'k' is loaded into PC<20:1>.

CALL is a two-cycle instruction.

2 Words: 2 Cycles:

Q Cycle Activity:

| Q1        | Q2           | Q3         | Q4           |

|-----------|--------------|------------|--------------|

| Decode    | Read literal | Push PC to | Read literal |

|           | 'k'<7:0>,    | stack      | 'k'<19:8>,   |

|           |              |            | Write to PC  |

| No        | No           | No         | No           |

| operation | operation    | operation  | operation    |

Example: HERE CALL THERE, 1

Before Instruction

PC address (HERE)

After Instruction

PC TOS address (THERE) address (HERE + 4)

WS W **BSRS BSR**

STATUSS= **STATUS**

| COMF                 | Complem                                                                                                                   | ent f                                                                                                                                                                                                                                                                                                         |           |                     | CF   | PFSEQ                 |

|----------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------|------|-----------------------|

| Syntax:              | [label] C                                                                                                                 | COMF                                                                                                                                                                                                                                                                                                          | f [,d [,a | ι]                  | Sy   | ntax:                 |

| Operands:            | $0 \le f \le 255$ $d \in [0,1]$                                                                                           | 5                                                                                                                                                                                                                                                                                                             |           |                     | Ор   | erands:               |

| Operation:           | $a \in [0,1]$ $(\overline{f}) \rightarrow d\epsilon$                                                                      | est                                                                                                                                                                                                                                                                                                           |           |                     | Op   | eration:              |

| Status Affected:     | N, Z                                                                                                                      |                                                                                                                                                                                                                                                                                                               |           |                     | - 0. |                       |

| Encoding:            | 0001                                                                                                                      | 11da                                                                                                                                                                                                                                                                                                          | ffff      | ffff                | Sta  | atus Affected:        |

| Description:  Words: | plemented<br>stored in N<br>stored back<br>'a' is 0, the<br>selected, of<br>If 'a' = 1, the<br>selected and<br>(default). | contents of register 'f' are com- lented. If 'd' is 0, the result is led in W. If 'd' is 1, the result is led back in register 'f' (default). If led 0, the Access Bank will be leted, overriding the BSR value.  In then the bank will be leted as per the BSR value leted as per the BSR value leted ault). |           |                     |      | coding:<br>scription: |

| Cycles:              | 1                                                                                                                         |                                                                                                                                                                                                                                                                                                               |           |                     |      |                       |

| Q Cycle Activity:    |                                                                                                                           |                                                                                                                                                                                                                                                                                                               |           |                     |      |                       |

| Q1                   | Q2                                                                                                                        | Q3                                                                                                                                                                                                                                                                                                            |           | Q4                  | _ Wo | ords:                 |

| Decode               | Read<br>register 'f'                                                                                                      | Proces<br>Data                                                                                                                                                                                                                                                                                                | -         | Write to estination | Су   | cles:                 |

| Example:             | COMF                                                                                                                      | REG, 0                                                                                                                                                                                                                                                                                                        | ), 0      |                     |      |                       |

| Before Instru<br>REG | ection<br>= 0x13                                                                                                          |                                                                                                                                                                                                                                                                                                               |           |                     | Q    | Cycle Activity:<br>Q1 |

| After Instruct       | tion<br>= 0x13                                                                                                            |                                                                                                                                                                                                                                                                                                               |           |                     |      | Decode                |

0xEC

| CPFSEQ                                                                   | PFSEQ Compare f with W, skip if f = W                                                     |                                                                                                                                                                                                                                                                                                                                                                                              |        |     |      |  |  |  |

|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|------|--|--|--|

| Syntax:                                                                  | [ label ]                                                                                 | CPFSEC                                                                                                                                                                                                                                                                                                                                                                                       | ] f [  | ,a] |      |  |  |  |

| Operands:                                                                | $0 \le f \le 2$ $a \in [0,1]$                                                             |                                                                                                                                                                                                                                                                                                                                                                                              |        |     |      |  |  |  |

| Operation:                                                               | (f) – (W)<br>skip if (f<br>(unsigne                                                       |                                                                                                                                                                                                                                                                                                                                                                                              | rison) |     |      |  |  |  |

| Status Affected:                                                         | None                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                              |        |     |      |  |  |  |

| Encoding:                                                                | 0110                                                                                      | 001a                                                                                                                                                                                                                                                                                                                                                                                         | fff    | f   | ffff |  |  |  |

| Description:                                                             | memory of W by subtract If 'f' = W tion is d cuted in cycle ins Access riding th the bank | Compares the contents of data memory location 'f' to the contents of W by performing an unsigned subtraction.  If 'f' = W, then the fetched instruction is discarded and a NOP is executed instead, making this a two-cycle instruction. If 'a' is 0, the Access Bank will be selected, overriding the BSR value. If 'a' = 1, then the bank will be selected as per the BSR value (default). |        |     |      |  |  |  |

| Nords:                                                                   | 1                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                              |        |     |      |  |  |  |

| Cycles: 1(2)  Note: 3 cycles if skip and follow by a 2-word instruction. |                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                              |        |     |      |  |  |  |

| Q Cycle Activity:                                                        |                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                              |        |     |      |  |  |  |

| Q1                                                                       | Q2                                                                                        | Q                                                                                                                                                                                                                                                                                                                                                                                            | 3      |     | Q4   |  |  |  |

| Decode                                                                   | Read                                                                                      | Proce                                                                                                                                                                                                                                                                                                                                                                                        | ess    |     | No   |  |  |  |

| Q1     | Q2           | Q3      | Q4        |

|--------|--------------|---------|-----------|

| Decode | Read         | Process | No        |

|        | register 'f' | Data    | operation |

### If skip:

| Q1        | Q2        | Q3        | Q4        |

|-----------|-----------|-----------|-----------|

| No        | No        | No        | No        |

| operation | operation | operation | operation |

#### If skip and followed by 2-word instruction:

| Q1        | Q2        | Q3        | Q4        |

|-----------|-----------|-----------|-----------|

| No        | No        | No        | No        |

| operation | operation | operation | operation |

| No        | No        | No        | No        |

| operation | operation | operation | operation |

| Example:                                                     | HERE<br>NEQUAL<br>EQUAL |                                | EQ REG, 0 |  |

|--------------------------------------------------------------|-------------------------|--------------------------------|-----------|--|

| Before Instruct<br>PC Addres<br>W<br>REG<br>After Instructio | S =<br>=<br>=           | HERE<br>?<br>?                 |           |  |

| If REG<br>PC<br>If REG<br>PC                                 | =<br>=<br>≠<br>=        | W;<br>Address<br>W;<br>Address | (EQUAL)   |  |

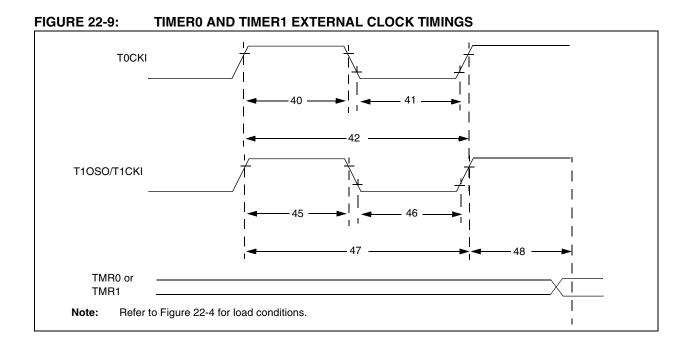

TABLE 22-8: TIMERO AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Symbol    |                          | Characteristic        |                     | Min                                          | Max    | Units | Conditions                               |  |

|--------------|-----------|--------------------------|-----------------------|---------------------|----------------------------------------------|--------|-------|------------------------------------------|--|

| 40           | Tt0H      | T0CKI High Pu            | ılse Width            | No Prescaler        | 0.5Tcy + 20                                  | _      | ns    |                                          |  |

|              |           |                          |                       | With Prescaler      | 10                                           |        | ns    |                                          |  |

| 41           | Tt0L      | T0CKI Low Pu             | lse Width             | No Prescaler        | 0.5Tcy + 20                                  |        | ns    |                                          |  |

|              |           |                          |                       | With Prescaler      | 10                                           |        | ns    |                                          |  |

| 42           | Tt0P      | T0CKI Period             |                       | No Prescaler        | Tcy + 10                                     |        | ns    |                                          |  |

|              |           |                          |                       | With Prescaler      | Greater of:<br>20 ns or <u>Tcy + 40</u><br>N | _      | ns    | N = prescale<br>value<br>(1, 2, 4,, 256) |  |

| 45           | Tt1H      | T1CKI High               | Synchronous, no       | prescaler           | 0.5Tcy + 20                                  | _      | ns    |                                          |  |

|              |           | Time                     | Synchronous,          | PIC18FXXX           | 10                                           | _      | ns    |                                          |  |

|              |           |                          | with prescaler        | PIC18 <b>LF</b> XXX | 25                                           | _      | ns    |                                          |  |

|              |           |                          | Asynchronous          | PIC18FXXX           | 30                                           | _      | ns    |                                          |  |

|              |           |                          |                       | PIC18 <b>LF</b> XXX | 50                                           | _      | ns    |                                          |  |

| 46           | Tt1L      | T1CKI Low                | Synchronous, no       | prescaler           | 0.5Tcy + 5                                   |        | ns    |                                          |  |

|              |           | Time                     | Synchronous,          | PIC18FXXX           | 10                                           |        | ns    |                                          |  |

|              |           |                          | V                     | with prescaler      | PIC18 <b>LF</b> XXX                          | 25     |       | ns                                       |  |

|              |           |                          | Asynchronous          | PIC18FXXX           | 30                                           |        | ns    |                                          |  |

|              |           |                          |                       | PIC18 <b>LF</b> XXX | 50                                           |        | ns    |                                          |  |

| 47           | Tt1P      | T1CKI input period       | Synchronous           |                     | Greater of:<br>20 ns or <u>Tcy + 40</u><br>N | _      | ns    | N = prescale<br>value<br>(1, 2, 4, 8)    |  |

|              |           |                          | Asynchronous          |                     | 60                                           | _      | ns    |                                          |  |

|              | Ft1       | T1CKI oscillato          | or input frequency ra | ange                | DC                                           | 50     | kHz   |                                          |  |

| 48           | Tcke2tmrl | Delay from ext increment | ernal T1CKI clock e   | edge to timer       | 2 Tosc                                       | 7 Tosc | _     |                                          |  |

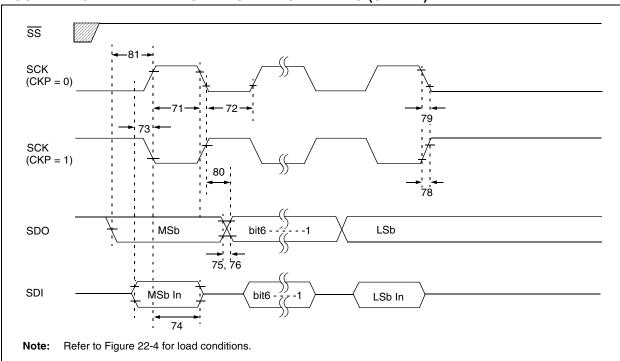

FIGURE 22-13: EXAMPLE SPI MASTER MODE TIMING (CKE = 1)

TABLE 22-12: EXAMPLE SPI MODE REQUIREMENTS (MASTER MODE, CKE = 1)

| Param.<br>No. | Symbol                | Characteristic                          |                                         | Min           | Max | Units | Conditions |

|---------------|-----------------------|-----------------------------------------|-----------------------------------------|---------------|-----|-------|------------|

| 71            | TscH                  | SCK input high time                     | Continuous                              | 1.25 Tcy + 30 | _   | ns    |            |

| 71A           |                       | (Slave mode)                            | Single Byte                             | 40            | _   | ns    | (Note 1)   |

| 72            | TscL                  | SCK input low time                      | Continuous                              | 1.25 Tcy + 30 | _   | ns    |            |

| 72A           |                       | (Slave mode)                            | Single Byte                             | 40            | _   | ns    | (Note 1)   |

| 73            | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to SCK     | edge                                    | 100           | _   | ns    |            |

| 73A           | Тв2в                  | Last clock edge of Byte1 to the 1st clo | ock edge of Byte2                       | 1.5 Tcy + 40  | _   | ns    | (Note 2)   |

| 74            | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK of   | Hold time of SDI data input to SCK edge |               |     | ns    |            |

| 75            | TdoR                  | SDO data output rise time               | PIC18FXXX                               | _             | 25  | ns    |            |

|               |                       |                                         | PIC18 <b>LF</b> XXX                     | _             | 60  | ns    | VDD = 2V   |

| 76            | TdoF                  | SDO data output fall time               | PIC18FXXX                               | _             | 25  | ns    |            |

|               |                       |                                         | PIC18 <b>LF</b> XXX                     | _             | 60  | ns    | VDD = 2V   |

| 78            | TscR                  | SCK output rise time (Master mode)      | PIC18FXXX                               | _             | 25  | ns    |            |

|               |                       |                                         | PIC18 <b>LF</b> XXX                     | _             | 60  | ns    | VDD = 2V   |

| 79            | TscF                  | SCK output fall time (Master mode)      | PIC18FXXX                               | _             | 25  | ns    |            |

|               |                       |                                         | PIC18 <b>LF</b> XXX                     | _             | 60  | ns    | VDD = 2V   |

| 80            | TscH2doV,             | SDO data output valid after SCK         | PIC18FXXX                               | _             | 50  | ns    |            |

|               | TscL2doV              | edge                                    | PIC18 <b>LF</b> XXX                     | _             | 150 | ns    | VDD = 2V   |

| 81            | TdoV2scH,<br>TdoV2scL | SDO data output setup to SCK edge       | •                                       | Tcy           | _   | ns    |            |

Note 1: Requires the use of Parameter # 73A.

2: Only if Parameter # 71A and # 72A are used.

#### **TABLE 22-22: A/D CONVERSION REQUIREMENTS**

| Param<br>No. | Symbol | Characte                                   | eristic           | Min     | Max               | Units    | Conditions                             |

|--------------|--------|--------------------------------------------|-------------------|---------|-------------------|----------|----------------------------------------|

| 130          | TAD    | A/D clock period                           | PIC18FXXX         | 1.6     | 20 <sup>(4)</sup> | μs       | Tosc based                             |

|              |        |                                            | PIC18FXXX         | 2.0     | 6.0               | μs       | A/D RC mode                            |

| 131          | TCNV   | Conversion time (not including acquisition | on time) (Note 1) | 11      | 12                | TAD      |                                        |