Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

|                            |                                                                          |

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                               |

| Number of I/O              | 34                                                                       |

| Program Memory Size        | 32KB (16K x 16)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 1.5K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-VQFN Exposed Pad                                                      |

| Supplier Device Package    | 44-QFN (8x8)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f452-i-ml |

### 1.0 DEVICE OVERVIEW

This document contains device specific information for the following devices:

PIC18F242PIC18F442PIC18F252PIC18F452

These devices come in 28-pin and 40/44-pin packages. The 28-pin devices do not have a Parallel Slave Port (PSP) implemented and the number of Analog-to-Digital (A/D) converter input channels is reduced to 5. An overview of features is shown in Table 1-1.

The following two figures are device block diagrams sorted by pin count: 28-pin for Figure 1-1 and 40/44-pin for Figure 1-2. The 28-pin and 40/44-pin pinouts are listed in Table 1-2 and Table 1-3, respectively.

TABLE 1-1: DEVICE FEATURES

| Features                           | PIC18F242                                                                        | PIC18F252                                                                        | PIC18F442                                                                        | PIC18F452                                                                        |  |

|------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--|

| Operating Frequency                | DC - 40 MHz                                                                      |  |

| Program Memory (Bytes)             | 16K                                                                              | 32K                                                                              | 16K                                                                              | 32K                                                                              |  |

| Program Memory (Instructions)      | 8192                                                                             | 16384                                                                            | 8192                                                                             | 16384                                                                            |  |

| Data Memory (Bytes)                | 768                                                                              | 1536                                                                             | 768                                                                              | 1536                                                                             |  |

| Data EEPROM Memory (Bytes)         | 256                                                                              | 256                                                                              | 256                                                                              | 256                                                                              |  |

| Interrupt Sources                  | 17                                                                               | 17                                                                               | 18                                                                               | 18                                                                               |  |

| I/O Ports                          | Ports A, B, C                                                                    | Ports A, B, C                                                                    | Ports A, B, C, D, E                                                              | Ports A, B, C, D, E                                                              |  |

| Timers                             | 4                                                                                | 4                                                                                | 4                                                                                | 4                                                                                |  |

| Capture/Compare/PWM Modules        | 2                                                                                | 2                                                                                | 2                                                                                | 2                                                                                |  |

| Serial Communications              | MSSP,<br>Addressable<br>USART                                                    | MSSP,<br>Addressable<br>USART                                                    | MSSP,<br>Addressable<br>USART                                                    | MSSP,<br>Addressable<br>USART                                                    |  |

| Parallel Communications            | _                                                                                | _                                                                                | PSP                                                                              | PSP                                                                              |  |

| 10-bit Analog-to-Digital Module    | 5 input channels                                                                 | 5 input channels                                                                 | 8 input channels                                                                 | 8 input channels                                                                 |  |

| RESETS (and Delays)                | POR, BOR,<br>RESET Instruction,<br>Stack Full,<br>Stack Underflow<br>(PWRT, OST) |  |

| Programmable Low Voltage<br>Detect | Yes                                                                              | Yes                                                                              | Yes                                                                              | Yes                                                                              |  |

| Programmable Brown-out Reset       | Yes                                                                              | Yes                                                                              | Yes                                                                              | Yes                                                                              |  |

| Instruction Set                    | 75 Instructions                                                                  | 75 Instructions                                                                  | 75 Instructions                                                                  | 75 Instructions                                                                  |  |

| Packages                           | 28-pin DIP<br>28-pin SOIC                                                        | 28-pin DIP<br>28-pin SOIC                                                        | 40-pin DIP<br>44-pin PLCC<br>44-pin TQFP                                         | 40-pin DIP<br>44-pin PLCC<br>44-pin TQFP                                         |  |

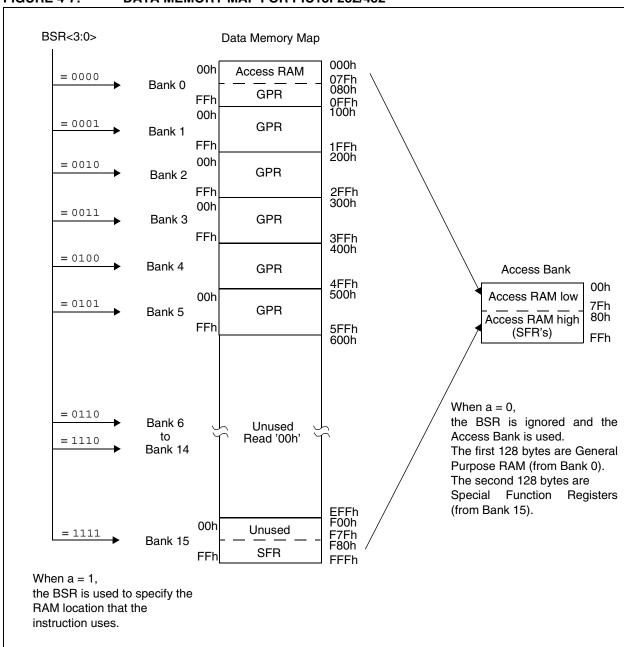

FIGURE 4-7: DATA MEMORY MAP FOR PIC18F252/452

NOTES:

NOTES:

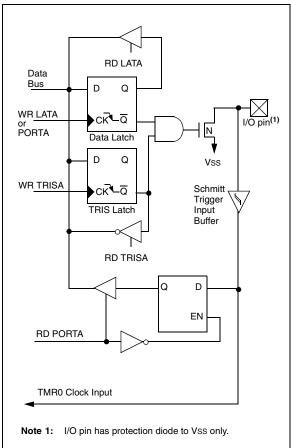

FIGURE 9-2: BLOCK DIAGRAM OF RA4/T0CKI PIN

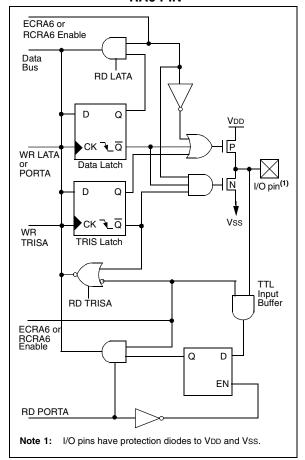

FIGURE 9-3: BLOCK DIAGRAM OF RA6 PIN

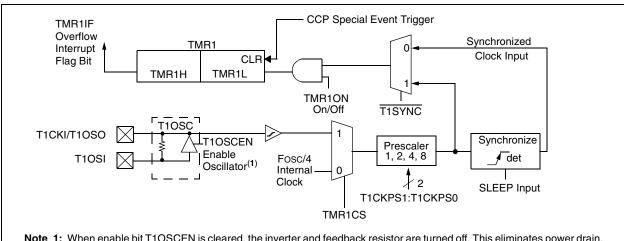

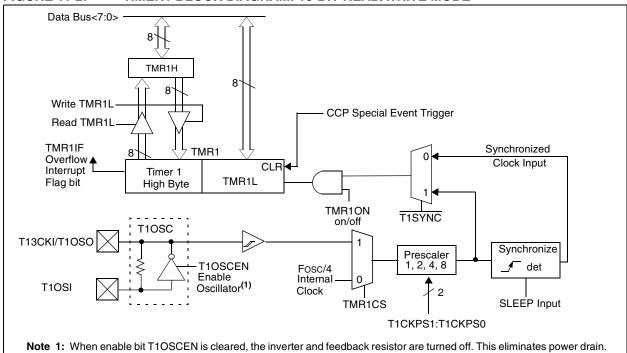

### 11.1 **Timer1 Operation**

Timer1 can operate in one of these modes:

- · As a timer

- · As a synchronous counter

- · As an asynchronous counter

The Operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

When TMR1CS = 0, Timer1 increments every instruction cycle. When TMR1CS = 1, Timer1 increments on every rising edge of the external clock input or the Timer1 oscillator, if enabled.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI and RC0/T1OSO/T1CKI pins become inputs. That is, the TRISC<1:0> value is ignored, and the pins are read as '0'.

Timer1 also has an internal "RESET input". This RESET can be generated by the CCP module (Section 14.0).

### **FIGURE 11-1: TIMER1 BLOCK DIAGRAM**

Note 1: When enable bit T1OSCEN is cleared, the inverter and feedback resistor are turned off. This eliminates power drain.

### FIGURE 11-2: TIMER1 BLOCK DIAGRAM: 16-BIT READ/WRITE MODE

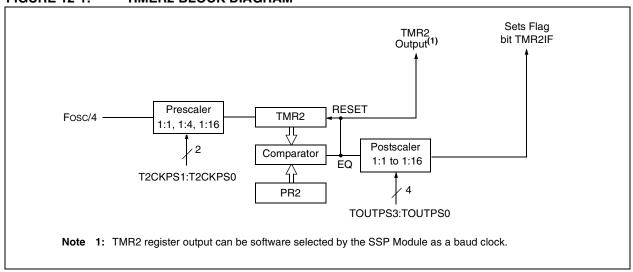

### 12.2 Timer2 Interrupt

The Timer2 module has an 8-bit period register, PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon RESET.

## 12.3 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the Synchronous Serial Port module, which optionally uses it to generate the shift clock.

FIGURE 12-1: TIMER2 BLOCK DIAGRAM

TABLE 12-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Name   | Bit 7                  | Bit 6         | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |

|--------|------------------------|---------------|---------|---------|---------|--------|---------|---------|----------------------|---------------------------------|

| INTCON | GIE/GIEH               | PEIE/GIEL     | TMR0IE  | INT0IE  | RBIE    | TMR0IF | INT0IF  | RBIF    | 0000 000x            | 0000 000u                       |

| PIR1   | PSPIF <sup>(1)</sup>   | ADIF          | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000            | 0000 0000                       |

| PIE1   | PSPIE <sup>(1)</sup>   | ADIE          | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000            | 0000 0000                       |

| IPR1   | PSPIP <sup>(1)</sup>   | ADIP          | RCIP    | TXIP    | SSPIP   | CCP1IP | TMR2IP  | TMR1IP  | 0000 0000            | 0000 0000                       |

| TMR2   | Timer2 Mod             | dule Register | r       |         |         |        |         |         | 0000 0000            | 0000 0000                       |

| T2CON  |                        | TOUTPS3       | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000            | -000 0000                       |

| PR2    | Timer2 Period Register |               |         |         |         |        |         |         |                      | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer2 module.

Note 1: The PSPIF, PSPIE and PSPIP bits are reserved on the PIC18F2X2 devices; always maintain these bits clear.

### 16.2 USART Asynchronous Mode

In this mode, the USART uses standard non-return-to-zero (NRZ) format (one START bit, eight or nine data bits and one STOP bit). The most common data format is 8-bits. An on-chip dedicated 8-bit baud rate generator can be used to derive standard baud rate frequencies from the oscillator. The USART transmits and receives the LSb first. The USART's transmitter and receiver are functionally independent, but use the same data format and baud rate. The baud rate generator produces a clock, either x16 or x64 of the bit shift rate, depending on bit BRGH (TXSTA<2>). Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during SLEEP.

Asynchronous mode is selected by clearing bit SYNC (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- · Baud Rate Generator

- · Sampling Circuit

- · Asynchronous Transmitter

- · Asynchronous Receiver

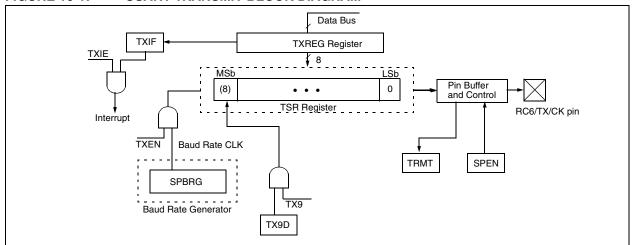

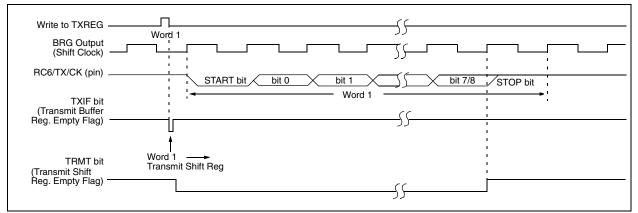

## 16.2.1 USART ASYNCHRONOUS TRANSMITTER

The USART transmitter block diagram is shown in Figure 16-1. The heart of the transmitter is the Transmit (serial) Shift Register (TSR). The shift register obtains its data from the read/write transmit buffer, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the STOP bit has been transmitted from the previous load. As soon as the STOP bit is transmitted, the TSR is loaded with new data from the TXREG register (if available). Once the TXREG register transfers the data to the TSR register (occurs in one Tcy), the TXREG register is empty and

flag bit TXIF (PIR1<4>) is set. This interrupt can be enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set, regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicated the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. Status bit TRMT is a read-only bit, which is set when the TSR register is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty.

- **Note 1:** The TSR register is not mapped in data memory, so it is not available to the user.

- 2: Flag bit TXIF is set when enable bit TXEN is set.

To set up an asynchronous transmission:

- Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH (Section 16.1).

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, set enable bit TXIE.

- If 9-bit transmission is desired, set transmit bit TX9. Can be used as address/data bit.

- Enable the transmission by setting bit TXEN, which will also set bit TXIF.

- If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Load data to the TXREG register (starts transmission).

Note: TXIF is not cleared immediately upon loading data into the transmit buffer TXREG.

The flag bit becomes valid in the second instruction cycle following the load instruction.

FIGURE 16-1: USART TRANSMIT BLOCK DIAGRAM

FIGURE 16-2: ASYNCHRONOUS TRANSMISSION

FIGURE 16-3: ASYNCHRONOUS TRANSMISSION (BACK TO BACK)

TABLE 16-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Name   | Bit 7                           | Bit 6        | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR |      | Value on<br>All Other<br>RESETS |      |

|--------|---------------------------------|--------------|--------|--------|-------|--------|--------|--------|----------------------|------|---------------------------------|------|

| INTCON | GIE/GIEH                        | PEIE/GIEL    | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF   | 0000                 | 000x | 0000                            | 000u |

| PIR1   | PSPIF <sup>(1)</sup>            | ADIF         | RCIF   | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000                 | 0000 | 0000                            | 0000 |

| PIE1   | PSPIE <sup>(1)</sup>            | ADIE         | RCIE   | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000                 | 0000 | 0000                            | 0000 |

| IPR1   | PSPIP <sup>(1)</sup>            | ADIP         | RCIP   | TXIP   | SSPIP | CCP1IP | TMR2IP | TMR1IP | 0000                 | 0000 | 0000                            | 0000 |

| RCSTA  | SPEN                            | RX9          | SREN   | CREN   | ADDEN | FERR   | OERR   | RX9D   | 0000 -               | -00x | 0000                            | -00x |

| TXREG  | USART Tra                       | ınsmit Regis | ter    |        |       |        |        |        | 0000                 | 0000 | 0000                            | 0000 |

| TXSTA  | CSRC                            | TX9          | TXEN   | SYNC   |       | BRGH   | TRMT   | TX9D   | 0000 -               | -010 | 0000                            | -010 |

| SPBRG  | RG Baud Rate Generator Register |              |        |        |       |        |        |        |                      | 0000 | 0000                            | 0000 |

Legend: x = unknown, - = unimplemented locations read as '0'.

Shaded cells are not used for Asynchronous Transmission.

Note 1: The PSPIF, PSPIE and PSPIP bits are reserved on the PIC18F2X2 devices; always maintain these bits clear.

To calculate the minimum acquisition time, Equation 17-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

## **EQUATION 17-1: ACQUISITION TIME**

```

TACQ = Amplifier Settling Time + Holding Capacitor Charging Time + Temperature Coefficient

= TAMP + TC + TCOFF

```

### **EQUATION 17-2: A/D MINIMUM CHARGING TIME**

```

\begin{array}{lll} V_{HOLD} &=& (V_{REF} - (V_{REF}/2048)) \bullet (1 - e^{(-T_C/C_{HOLD}(R_{IC} + R_{SS} + R_S))}) \\ \text{or} \\ T_C &=& -(120 \text{ pF})(1 \text{ k}\Omega + R_{SS} + R_S) \ln(1/2048) \end{array}

```

Example 17-1 shows the calculation of the minimum required acquisition time, TACQ. This calculation is based on the following application system assumptions:

$\begin{array}{lll} \bullet & \mathsf{CHOLD} & = & 120 \ \mathsf{pF} \\ \bullet & \mathsf{Rs} & = & 2.5 \ \mathsf{k}\Omega \\ \bullet & \mathsf{Conversion Error} & \leq & 1/2 \ \mathsf{LSb} \\ \end{array}$

• VDD =  $5V \rightarrow Rss = 7 \text{ k}\Omega$ • Temperature =  $50^{\circ}\text{C}$  (system max.) • VHOLD = 0V @ time = 0

### **EXAMPLE 17-1: CALCULATING THE MINIMUM REQUIRED ACQUISITION TIME**

```

\begin{array}{lll} TACQ & = & TAMP + TC + TCOFF \\ Temperature coefficient is only required for temperatures > 25^{\circ}C. \\ TACQ & = & 2~\mu s + TC + \left[ (Temp - 25^{\circ}C)(0.05~\mu s/^{\circ}C) \right] \\ TC & = & -CHOLD \left( RIC + Rss + Rs \right) \ln(1/2048) \\ & & -120~pF \left( 1~k\Omega + 7~k\Omega + 2.5~k\Omega \right) \ln(0.0004883) \\ & & -120~pF \left( 10.5~k\Omega \right) \ln(0.0004883) \\ & & -1.26~\mu s \left( -7.6246 \right) \\ & & 9.61~\mu s \\ \\ TACQ & = & 2~\mu s + 9.61~\mu s + \left[ (50^{\circ}C - 25^{\circ}C)(0.05~\mu s/^{\circ}C) \right] \\ & & 11.61~\mu s + 1.25~\mu s \\ & & 12.86~\mu s \\ \\ \end{array}

```

# 19.4 Program Verification and Code Protection

The overall structure of the code protection on the PIC18 FLASH devices differs significantly from other PICmicro devices.

The user program memory is divided into five blocks. One of these is a boot block of 512 bytes. The remainder of the memory is divided into four blocks on binary boundaries.

Each of the five blocks has three code protection bits associated with them. They are:

- Code Protect bit (CPn)

- Write Protect bit (WRTn)

- External Block Table Read bit (EBTRn)

Figure 19-3 shows the program memory organization for 16- and 32-Kbyte devices, and the specific code protection bit associated with each block. The actual locations of the bits are summarized in Table 19-3.

FIGURE 19-3: CODE PROTECTED PROGRAM MEMORY FOR PIC18F2XX/4XX

| MEMORY S                  | IZE/DEVICE                |                    |                                         |

|---------------------------|---------------------------|--------------------|-----------------------------------------|

| 16 Kbytes<br>(PIC18FX42)  | 32 Kbytes<br>(PIC18FX52)  | Address<br>Range   | Block Code Protection<br>Controlled By: |

| Boot Block                | Boot Block                | 000000h<br>0001FFh | CPB, WRTB, EBTRB                        |

| Block 0                   | Block 0                   | 000200h<br>001FFFh | CP0, WRT0, EBTR0                        |

| Block 1                   | Block 1                   | 002000h<br>003FFFh | CP1, WRT1, EBTR1                        |

| Unimplemented<br>Read 0's | Block 2                   | 004000h<br>005FFFh | CP2, WRT2, EBTR2                        |

| Unimplemented<br>Read 0's | Block 3                   | 006000h<br>007FFFh | CP3, WRT3, EBTR3                        |

| Unimplemented<br>Read 0's | Unimplemented<br>Read 0's | 008000h            | (Unimplemented Memory Space)            |

TABLE 19-3: SUMMARY OF CODE PROTECTION REGISTERS

| File Name |          | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----------|----------|-------|-------|-------|-------|-------|-------|-------|-------|

| 300008h   | CONFIG5L |       | _     | _     | _     | CP3   | CP2   | CP1   | CP0   |

| 300009h   | CONFIG5H | CPD   | СРВ   | _     | _     | _     | _     | _     | _     |

| 30000Ah   | CONFIG6L | _     | _     | _     | _     | WRT3  | WRT2  | WRT1  | WRT0  |

| 30000Bh   | CONFIG6H | WRTD  | WRTB  | WRTC  | _     | _     | _     | _     | _     |

| 30000Ch   | CONFIG7L | _     | _     | _     | _     | EBTR3 | EBTR2 | EBTR1 | EBTR0 |

| 30000Dh   | CONFIG7H | _     | EBTRB | _     | _     | _     | _     | _     | _     |

Legend: Shaded cells are unimplemented.

| CPFSGT             | Compare                                                                                                                                        | f with W, sk                                                                          | (ip if f > W                                                                        | CPFSI                                                                                                                                                                                                                     | LT                 | Compare                                  | f with W, sk                                                                                                                | ip if f < W                                                                                                                  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:            | [label] (                                                                                                                                      | CPFSGT f[                                                                             | ,a]                                                                                 | Syntax                                                                                                                                                                                                                    | (:                 | [label] (                                | CPFSLT f[,                                                                                                                  | a]                                                                                                                           |  |

| Operands:          | $0 \le f \le 255$ $a \in [0,1]$                                                                                                                | 5                                                                                     |                                                                                     | Opera                                                                                                                                                                                                                     | nds:               | $0 \le f \le 258$ $a \in [0,1]$          | 5                                                                                                                           |                                                                                                                              |  |

| Operation:         | (f) – (W),<br>skip if (f) ><br>(unsigned                                                                                                       | · (W)<br>comparison                                                                   | )                                                                                   | Operat                                                                                                                                                                                                                    | tion:              | (f) – (W),<br>skip if (f) <<br>(unsigned | (W)<br>comparison)                                                                                                          | )                                                                                                                            |  |

| Status Affected:   | None                                                                                                                                           |                                                                                       |                                                                                     | Status                                                                                                                                                                                                                    | Status Affected:   |                                          |                                                                                                                             |                                                                                                                              |  |

| Encoding:          | 0110                                                                                                                                           | 010a ff:                                                                              | ff ffff                                                                             | Encodi                                                                                                                                                                                                                    | ing:               | 0110                                     | 000a ffi                                                                                                                    | ff ffff                                                                                                                      |  |

| Description:       | memory lo<br>of the W b<br>unsigned<br>If the conter<br>fetched in:<br>a NOP is e<br>this a two-<br>0, the Acc<br>selected, o<br>If 'a' = 1, t | nts of WREG<br>struction is di<br>executed instruc-<br>cycle instruc-<br>ess Bank wil | greater than, then the iscarded and ead, making etion. If 'a' is il be e BSR value. | of W by performing a subtraction.  If the contents of 'f' are the contents of W, the and instruction is discarded ing is executed instead, received instruction.  Access Bank will be seen in the BSR will not (default). |                    |                                          | ocation 'f' to therforming and n.  ents of 'f' are nots of W, there is discarded dinstead, mainstruction. If ank will be se | he contents<br>unsigned<br>eless than<br>in the fetched<br>d and a NOP<br>aking this a<br>f 'a' is 0, the<br>elected. If 'a' |  |

|                    | (default).                                                                                                                                     | is per the be                                                                         | or i value                                                                          | Words                                                                                                                                                                                                                     |                    | 1                                        |                                                                                                                             |                                                                                                                              |  |

| Words:             | 1                                                                                                                                              |                                                                                       |                                                                                     | Cycles                                                                                                                                                                                                                    | s:                 | 1(2)<br><b>Note:</b> 3 (                 | cycles if skip                                                                                                              | and follows                                                                                                                  |  |

| Cycles:            | 1(2)                                                                                                                                           | 1(2)                                                                                  |                                                                                     |                                                                                                                                                                                                                           |                    |                                          | a 2-word ins                                                                                                                |                                                                                                                              |  |

| - <b>,</b>         | . ,                                                                                                                                            | cycles if skip                                                                        | and followed                                                                        | Q Cvc                                                                                                                                                                                                                     | cle Activity:      | -                                        |                                                                                                                             |                                                                                                                              |  |

|                    | by                                                                                                                                             | a 2-word ins                                                                          | struction.                                                                          | ۵,0,1                                                                                                                                                                                                                     | Q1                 | Q2                                       | Q3                                                                                                                          | Q4                                                                                                                           |  |

| Q Cycle Activity:  |                                                                                                                                                |                                                                                       |                                                                                     |                                                                                                                                                                                                                           | Decode             | Read                                     | Process                                                                                                                     | No                                                                                                                           |  |

| Q1                 | Q2                                                                                                                                             | Q3                                                                                    | Q4                                                                                  |                                                                                                                                                                                                                           |                    | register 'f'                             | Data                                                                                                                        | operation                                                                                                                    |  |

| Decode             | Read                                                                                                                                           | Process<br>Data                                                                       | No operation                                                                        | If skip                                                                                                                                                                                                                   | :                  |                                          |                                                                                                                             |                                                                                                                              |  |

| If okin:           | register 'f'                                                                                                                                   | Dala                                                                                  | operation                                                                           | _                                                                                                                                                                                                                         | Q1                 | Q2                                       | Q3                                                                                                                          | Q4                                                                                                                           |  |

| If skip:<br>Q1     | Q2                                                                                                                                             | Q3                                                                                    | Q4                                                                                  |                                                                                                                                                                                                                           | No                 | No                                       | No                                                                                                                          | No                                                                                                                           |  |

| No                 | No                                                                                                                                             | No No                                                                                 | No No                                                                               |                                                                                                                                                                                                                           | operation          | operation                                | operation                                                                                                                   | operation                                                                                                                    |  |

| operation          | operation                                                                                                                                      | operation                                                                             | operation                                                                           | іт ѕкір                                                                                                                                                                                                                   |                    | -                                        | d instruction:                                                                                                              |                                                                                                                              |  |

| If skip and follow | ed by 2-wor                                                                                                                                    | d instruction:                                                                        | <u> </u>                                                                            |                                                                                                                                                                                                                           | Q1                 | Q2                                       | Q3                                                                                                                          | Q4                                                                                                                           |  |

| Q1                 | Q2                                                                                                                                             | Q3                                                                                    | Q4                                                                                  |                                                                                                                                                                                                                           | No<br>operation    | No operation                             | No operation                                                                                                                | No operation                                                                                                                 |  |

| No                 | No                                                                                                                                             | No                                                                                    | No                                                                                  |                                                                                                                                                                                                                           | No                 | No                                       | No                                                                                                                          | No                                                                                                                           |  |

| operation          | operation                                                                                                                                      | operation                                                                             | operation                                                                           | (                                                                                                                                                                                                                         | operation          | operation                                | operation                                                                                                                   | operation                                                                                                                    |  |

| No operation       | No<br>operation                                                                                                                                | No operation                                                                          | No operation                                                                        | Examp                                                                                                                                                                                                                     | ole:               | HERE                                     | CPFSLT REG,                                                                                                                 | 1                                                                                                                            |  |

| Example:           | HERE<br>NGREATER<br>GREATER                                                                                                                    | CPFSGT RE                                                                             | EG, 0                                                                               | ·                                                                                                                                                                                                                         | efore Instru<br>PC | NLESS<br>LESS<br>uction                  | :<br>:<br>:<br> dress (HERE                                                                                                 |                                                                                                                              |  |

| Before Instru      |                                                                                                                                                | droce (HEDE                                                                           | ١                                                                                   | Δf                                                                                                                                                                                                                        | W<br>ter Instruc   | = ?<br>tion                              |                                                                                                                             |                                                                                                                              |  |

After Instruction

If REG

< W; PC = Address (LESS)

If REG \geq W;

PC = Address (NLESS)

PC If REG PC

PC W

After Instruction If REG

= Address (HERE)

= ?

W;

= Address (GREATER)

≤ W;

Address (NGREATER)

| DAW                | Decimal A         | Adjust W Re                  | gister       | DECF             | Dec         |

|--------------------|-------------------|------------------------------|--------------|------------------|-------------|

| Syntax:            | [label] [         | DAW                          |              | Syntax:          | [ lai       |

| Operands:          | None              |                              |              | Operands:        | 0 ≤         |

| Operation:         |                   | >9] or [DC =                 |              |                  | d∈          |

|                    |                   | $+ 6 \rightarrow W < 3:0$    | 0>;          | 0                | a∈<br>«     |

|                    | else<br>(W<3:0>)  | → W<3:0>;                    |              | Operation:       | (f) -       |

|                    |                   |                              |              | Status Affected: | C, [        |

|                    |                   | >9] or [C =                  | -            | Encoding:        | 0           |

|                    | (VV<7:4>)<br>else | $+6 \rightarrow W<7$ :       | 4>;          | Description:     | Dec         |

|                    |                   | → W<7:4>;                    |              |                  | res         |

| Status Affected:   | С                 |                              |              |                  | (de         |

| Encoding:          | 0000              | 0000 000                     | 00 0111      |                  | Bar<br>the  |

| Description:       | DAW adjus         | sts the eight-               | bit value in |                  | bar         |

|                    |                   | ng from the e                |              |                  | BS          |

|                    |                   | variables (e<br>CD format) a | Words:       | 1                |             |

|                    | •                 | packed BCD                   | Cycles:      | 1                |             |

| Words:             | 1                 |                              |              | Q Cycle Activity | r <b>:</b>  |

| Cycles:            | 1                 |                              |              | Q1               |             |

| Q Cycle Activity   | :                 |                              |              | Decode           | Re<br>regis |

| Q1                 | Q2                | Q3                           | Q4           |                  | Togic       |

| Decode             | Read              | Process                      | Write        | Example:         | DEC         |

|                    | register W        | Data                         | W            | Before Instr     | uction      |

| Example1:          | DAW<br>           |                              |              | CNT<br>Z         | = =         |

| Before Instru<br>W |                   |                              |              | After Instruc    |             |

| С                  | = 0xA5<br>= 0     |                              |              | CNT              | =           |

| DC                 | = 0               |                              |              | Z                | =           |

| After Instruc      | นon<br>= 0x05     |                              |              |                  |             |

| С                  | = 1               |                              |              |                  |             |

| DC<br>Example 2:   | = 0               |                              |              |                  |             |

| Before Instru      | uction            |                              |              |                  |             |

| W                  | = 0xCE            |                              |              |                  |             |

| C<br>DC            | = 0<br>= 0        |                              |              |                  |             |

| After Instruc      | •                 |                              |              |                  |             |

| W                  | = 0x34            |                              |              |                  |             |

| C<br>DC            | = 1<br>= 0        |                              |              |                  |             |

|                    | -                 |                              |              |                  |             |

| DEC                                                                                                                                                                                                                                                                                                 | F              | Decreme                                             | nt f          |          |                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------------------------------------|---------------|----------|--------------------|

| Synt                                                                                                                                                                                                                                                                                                | ax:            | [label] [                                           | DECF 1        | [,d [,a] |                    |

| Oper                                                                                                                                                                                                                                                                                                | rands:         | $0 \le f \le 258$<br>$d \in [0,1]$<br>$a \in [0,1]$ | 5             |          |                    |

| Oper                                                                                                                                                                                                                                                                                                | ration:        | $(f)-1\to 0$                                        | dest          |          |                    |

| Statu                                                                                                                                                                                                                                                                                               | ıs Affected:   | C, DC, N,                                           | OV, Z         |          |                    |

| Enco                                                                                                                                                                                                                                                                                                | oding:         | 0000                                                | 01da          | ffff     | ffff               |

| Description:  Decrement register 'f'. If 'd' is 0, the result is stored in W. If 'd' is 1, the result is stored back in register 'f' (default). If 'a' is 0, the Access Bank will be selected, overriding the BSR value. If 'a' = 1, then the bank will be selected as per the BSR value (default). |                |                                                     |               |          |                    |

| Word                                                                                                                                                                                                                                                                                                | ds:            | 1                                                   |               |          |                    |

| Cycle                                                                                                                                                                                                                                                                                               | es:            | 1                                                   |               |          |                    |

| QC                                                                                                                                                                                                                                                                                                  | ycle Activity: |                                                     |               |          |                    |

|                                                                                                                                                                                                                                                                                                     | Q1             | Q2                                                  | Q3            | 3        | Q4                 |

|                                                                                                                                                                                                                                                                                                     | Decode         | Read register 'f'                                   | Proce<br>Data |          | Write to stination |

RCALL Relative Call

Syntax: [label] RCALL n

Operands:  $-1024 \le n \le 1023$ Operation: (PC)  $+ 2 \rightarrow TOS$ ,

$(PC) + 2 + 2n \rightarrow PC$

Status Affected: None

Encoding: 1101 1nnn nnnn nnnn

Description: Subroutine call with a jump up to 1K from the current location. First, return address (PC+2) is pushed onto the stack. Then, add the 2's complement number '2n' to the PC.

complement number '2n' to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC+2+2n. This instruction is a two-cycle

instruction.

Words: 1 Cycles: 2

Q Cycle Activity:

| Q1        | Q2                  | Q3              | Q4          |

|-----------|---------------------|-----------------|-------------|

| Decode    | Read literal<br>'n' | Process<br>Data | Write to PC |

|           | Push PC to stack    |                 |             |

| No        | No                  | No              | No          |

| operation | operation           | operation       | operation   |

Example: HERE RCALL Jump

Before Instruction

PC = Address (HERE)

After Instruction

PC = Address (Jump) TOS = Address (HERE+2)

| RES   | ET              | Reset                  |          |   |     |      |  |  |  |

|-------|-----------------|------------------------|----------|---|-----|------|--|--|--|

| Synt  | ax:             | [ label ]              | RESET    |   |     |      |  |  |  |

| Ope   | rands:          | None                   |          |   |     |      |  |  |  |

| Ope   | ration:         | Reset all are affected | _        |   | _ ~ |      |  |  |  |

| Statu | us Affected:    | All                    |          |   |     |      |  |  |  |

| Enco  | oding:          | 0000                   | 0000 113 |   | .1  | 1111 |  |  |  |

| Des   | cription:       | This instruexecute a   |          |   |     | •    |  |  |  |

| Wor   | ds:             | 1                      |          |   |     |      |  |  |  |

| Cycl  | es:             | 1                      | 1        |   |     |      |  |  |  |

| QC    | Cycle Activity: |                        |          |   |     |      |  |  |  |

|       | Q1              | Q2                     | Q3       | 3 |     | Q4   |  |  |  |

|       | Decode          | Start                  | No       |   |     | No   |  |  |  |

Example: RESET

After Instruction

Registers = Reset Value Flags\* = Reset Value

reset

operation

operation

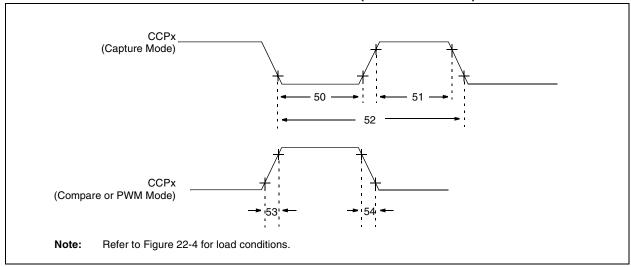

FIGURE 22-10: CAPTURE/COMPARE/PWM TIMINGS (CCP1 AND CCP2)

TABLE 22-9: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP1 AND CCP2)

| Param.<br>No. | Symbol               | Characteristic           |              |                     | Min                    | Max | Units | Conditions                        |

|---------------|----------------------|--------------------------|--------------|---------------------|------------------------|-----|-------|-----------------------------------|

| 50            | TccL                 | CCPx input low           | No Prescaler |                     | 0.5 Tcy + 20           |     | ns    |                                   |

|               | time                 | time                     | With         | PIC18FXXX           | 10                     | _   | ns    |                                   |

|               |                      |                          | Prescaler    | PIC18 <b>LF</b> XXX | 20                     |     | ns    |                                   |

| 51            | TccH CCPx input No P |                          | No Prescal   | er                  | 0.5 Tcy + 20           |     | ns    |                                   |

|               |                      | high time                | With         | PIC18FXXX           | 10                     | _   | ns    |                                   |

|               |                      |                          | Prescaler    | PIC18 <b>LF</b> XXX | 20                     | _   | ns    |                                   |

| 52            | TccP                 | CCPx input perio         | od           |                     | <u>3 Tcy + 40</u><br>N |     | ns    | N = prescale<br>value (1,4 or 16) |

| 53            | TccR                 | CCPx output fall         | time         | PIC18FXXX           | _                      | 25  | ns    |                                   |

|               |                      | PIC1                     |              | PIC18 <b>LF</b> XXX | _                      | 60  | ns    | VDD = 2V                          |

| 54            | TccF                 | cF CCPx output fall time |              | PIC18FXXX           |                        | 25  | ns    |                                   |

|               |                      |                          |              | PIC18 <b>LF</b> XXX |                        | 60  | ns    | VDD = 2V                          |

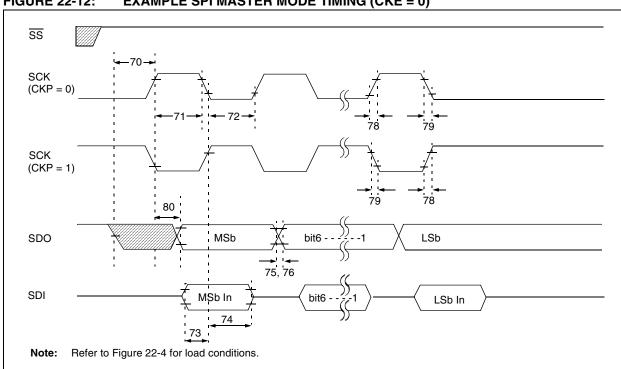

**EXAMPLE SPI MASTER MODE TIMING (CKE = 0) FIGURE 22-12:**

TABLE 22-11: EXAMPLE SPI MODE REQUIREMENTS (MASTER MODE, CKE = 0)

| Param.<br>No. | Symbol                | Characteristic                                          |                     | Min           | Max | Units    | Conditions |

|---------------|-----------------------|---------------------------------------------------------|---------------------|---------------|-----|----------|------------|

| 70            | TssL2scH,<br>TssL2scL | SS↓ to SCK↓ or SCK↑ input                               |                     | Tcy           | _   | ns       |            |

| 71            | TscH                  | SCK input high time                                     | Continuous          | 1.25 Tcy + 30 | _   | ns       |            |

| 71A           |                       | (Slave mode)                                            | Single Byte         | 40            | _   | ns       | (Note 1)   |

| 72            | TscL                  | SCK input low time                                      | Continuous          | 1.25 Tcy + 30 | _   | ns       |            |

| 72A           |                       | (Slave mode)                                            | Single Byte         | 40            | _   | ns       | (Note 1)   |

| 73            | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to SCK edge                |                     | 100           | _   | ns       |            |

| 73A           | Тв2в                  | Last clock edge of Byte1 to the 1st clock edge of Byte2 |                     | 1.5 Tcy + 40  | _   | ns       | (Note 2)   |

| 74            | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge                 |                     | 100           | _   | ns       |            |

| 75            | TdoR                  | SDO data output rise time                               | PIC18FXXX           | _             | 25  | ns       |            |

|               |                       | PIC18 <b>LF</b> XXX                                     | _                   | 60            | ns  | VDD = 2V |            |

| 76            | TdoF                  | SDO data output fall time                               | PIC18FXXX           | _             | 25  | ns       |            |

|               |                       |                                                         | PIC18 <b>LF</b> XXX | _             | 60  | ns       | VDD = 2V   |

| 78            | TscR                  | (NA = = 4 = 11 = 11 = 1 = 1                             | PIC18FXXX           | _             | 25  | ns       |            |

|               |                       |                                                         | PIC18 <b>LF</b> XXX | _             | 60  | ns       | VDD = 2V   |

| 79            | TscF                  | SCK output fall time (Master mode)                      | PIC18FXXX           | _             | 25  | ns       |            |

|               |                       |                                                         | PIC18 <b>LF</b> XXX | _             | 60  | ns       | VDD = 2V   |

| 80            | TscH2doV,             | SDO data output valid after SCK                         | PIC18FXXX           | _             | 50  | ns       |            |

|               | TscL2doV edge         |                                                         | PIC18 <b>LF</b> XXX | _             | 150 | ns       | VDD = 2V   |

Note 1: Requires the use of Parameter # 73A.

2: Only if Parameter # 71A and # 72A are used.

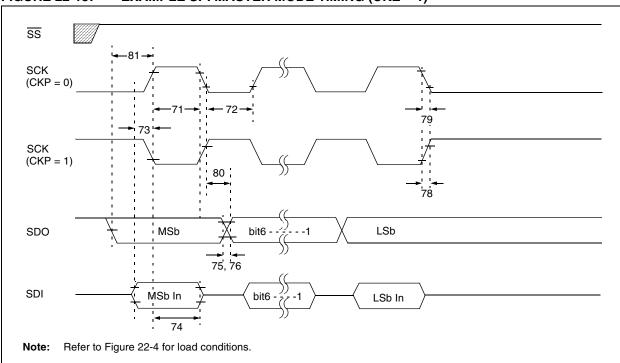

FIGURE 22-13: EXAMPLE SPI MASTER MODE TIMING (CKE = 1)

TABLE 22-12: EXAMPLE SPI MODE REQUIREMENTS (MASTER MODE, CKE = 1)

| Param.<br>No. | Symbol                | Characteristic                          |                     | Min           | Max | Units    | Conditions |

|---------------|-----------------------|-----------------------------------------|---------------------|---------------|-----|----------|------------|

| 71            | TscH                  | SCK input high time                     | Continuous          | 1.25 Tcy + 30 | _   | ns       |            |

| 71A           |                       | (Slave mode)                            | Single Byte         | 40            | _   | ns       | (Note 1)   |

| 72            | TscL                  | SCK input low time                      | Continuous          | 1.25 Tcy + 30 | _   | ns       |            |

| 72A           |                       | (Slave mode)                            | Single Byte         | 40            | _   | ns       | (Note 1)   |

| 73            | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to SCK     | edge                | 100           | _   | ns       |            |

| 73A           | Тв2в                  | Last clock edge of Byte1 to the 1st clo | ck edge of Byte2    | 1.5 Tcy + 40  | _   | ns       | (Note 2)   |

| 74            | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge |                     | 100           | _   | ns       |            |

| 75            | TdoR                  | SDO data output rise time               | PIC18FXXX           | _             | 25  | ns       |            |

|               |                       |                                         | PIC18 <b>LF</b> XXX | _             | 60  | ns       | VDD = 2V   |

| 76            | TdoF                  | SDO data output fall time               | PIC18FXXX           | _             | 25  | ns       |            |

|               | 1                     | PIC18 <b>LF</b> XXX                     | _                   | 60            | ns  | VDD = 2V |            |

| 78 TscR       |                       | SCK output rise time (Master mode)      | PIC18FXXX           | _             | 25  | ns       |            |

|               |                       |                                         | PIC18 <b>LF</b> XXX | _             | 60  | ns       | VDD = 2V   |

| 79            | TscF                  | SCK output fall time (Master mode)      | PIC18FXXX           | _             | 25  | ns       |            |

|               |                       |                                         | PIC18 <b>LF</b> XXX | _             | 60  | ns       | VDD = 2V   |

| 80 TscH2doV,  |                       | SDO data output valid after SCK         | PIC18FXXX           | _             | 50  | ns       |            |

|               | TscL2doV edge         |                                         | PIC18 <b>LF</b> XXX | _             | 150 | ns       | VDD = 2V   |

| 81            | TdoV2scH,<br>TdoV2scL | SDO data output setup to SCK edge       | •                   | Tcy           | _   | ns       |            |

Note 1: Requires the use of Parameter # 73A.

2: Only if Parameter # 71A and # 72A are used.

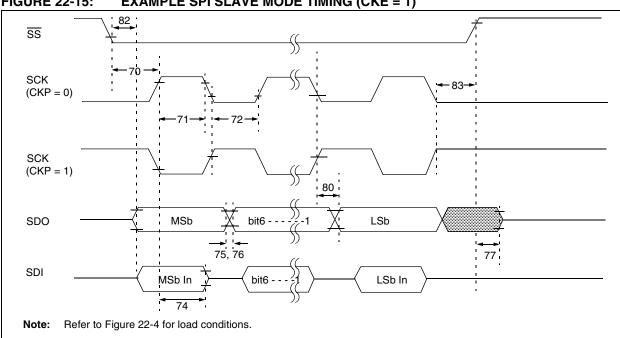

FIGURE 22-15: **EXAMPLE SPI SLAVE MODE TIMING (CKE = 1)**

TABLE 22-14: EXAMPLE SPI SLAVE MODE REQUIREMENTS (CKE = 1)

| Param. No. | Symbol                                    | Characteristic                                   |                     | Min           | Max | Units | Conditions |

|------------|-------------------------------------------|--------------------------------------------------|---------------------|---------------|-----|-------|------------|

| 70         | TssL2scH,<br>TssL2scL                     | SS↓ to SCK↓ or SCK↑ input                        |                     | Tcy           | _   | ns    |            |

| 71         | TscH                                      | SCK input high time                              | Continuous          | 1.25 Tcy + 30 | _   | ns    |            |

| 71A        |                                           | (Slave mode)                                     | Single Byte         | 40            | _   | ns    | (Note 1)   |

| 72         | TscL                                      | SCK input low time                               | Continuous          | 1.25 Tcy + 30 | _   | ns    |            |

| 72A        |                                           | (Slave mode)                                     | Single Byte         | 40            | _   | ns    | (Note 1)   |

| 73A        | Тв2в                                      | Last clock edge of Byte1 to the first cloc       | k edge of Byte2     | 1.5 Tcy + 40  | _   | ns    | (Note 2)   |

| 74         | TscH2diL,<br>TscL2diL                     | Hold time of SDI data input to SCK edge          |                     | 100           | _   | ns    |            |

| 75         | TdoR                                      | SDO data output rise time                        | PIC18FXXX           | _             | 25  | ns    |            |

|            |                                           |                                                  | PIC18 <b>LF</b> XXX | _             | 60  | ns    | VDD = 2V   |

| 76         | TdoF                                      | SDO data output fall time                        | PIC18FXXX           | _             | 25  | ns    |            |

|            |                                           |                                                  | PIC18 <b>LF</b> XXX | _             | 60  | ns    | VDD = 2V   |

| 77         | TssH2doZ                                  | SS↑ to SDO output hi-impedance                   |                     | 10            | 50  | ns    |            |

| 78         | TscR                                      | SCK output rise time (Master mode)               | PIC18FXXX           | _             | 25  | ns    |            |

|            |                                           |                                                  | PIC18 <b>LF</b> XXX | _             | 60  | ns    | VDD = 2V   |

| 79         | TscF                                      | SCK output fall time (Master mode)               | PIC18FXXX           | _             | 25  | ns    |            |

|            |                                           |                                                  | PIC18 <b>LF</b> XXX | _             | 60  | ns    | VDD = 2V   |

| 80         | TscH2doV, SDO data output valid after SCK | PIC18FXXX                                        | _                   | 50            | ns  |       |            |

|            | TscL2doV                                  | edge                                             | PIC18 <b>LF</b> XXX | _             | 150 | ns    | VDD = 2V   |

| 82         | TssL2doV                                  | SDO data output valid after <del>SS</del> ↓ edge | PIC18FXXX           | _             | 50  | ns    |            |

|            |                                           |                                                  | PIC18 <b>LF</b> XXX | _             | 150 | ns    | VDD = 2V   |

| 83         | TscH2ssH,<br>TscL2ssH                     | SS ↑ after SCK edge                              | 1                   | 1.5 Tcy + 40  | _   | ns    |            |

Note 1: Requires the use of Parameter # 73A.

2: Only if Parameter # 71A and # 72A are used.

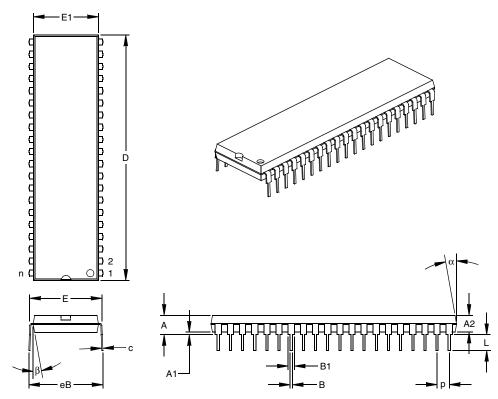

## 40-Lead Plastic Dual In-line (P) - 600 mil Body (PDIP)

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                      |           |       | INCHES* |       | MILLIMETERS |       |       |

|----------------------------|-----------|-------|---------|-------|-------------|-------|-------|

| Dimensi                    | on Limits | MIN   | NOM     | MAX   | MIN         | NOM   | MAX   |

| Number of Pins             | n         |       | 40      |       |             | 40    |       |

| Pitch                      | р         |       | .100    |       |             | 2.54  |       |

| Top to Seating Plane       | Α         | .160  | .175    | .190  | 4.06        | 4.45  | 4.83  |

| Molded Package Thickness   | A2        | .140  | .150    | .160  | 3.56        | 3.81  | 4.06  |

| Base to Seating Plane      |           | .015  |         |       | 0.38        |       |       |

| Shoulder to Shoulder Width |           | .595  | .600    | .625  | 15.11       | 15.24 | 15.88 |

| Molded Package Width E     |           | .530  | .545    | .560  | 13.46       | 13.84 | 14.22 |

| Overall Length             |           | 2.045 | 2.058   | 2.065 | 51.94       | 52.26 | 52.45 |

| Tip to Seating Plane       | L         | .120  | .130    | .135  | 3.05        | 3.30  | 3.43  |

| Lead Thickness             | С         | .008  | .012    | .015  | 0.20        | 0.29  | 0.38  |

| Upper Lead Width           | B1        | .030  | .050    | .070  | 0.76        | 1.27  | 1.78  |

| Lower Lead Width B         |           | .014  | .018    | .022  | 0.36        | 0.46  | 0.56  |

| Overall Row Spacing §      | eB        | .620  | .650    | .680  | 15.75       | 16.51 | 17.27 |

| Mold Draft Angle Top       | α         | 5     | 10      | 15    | 5           | 10    | 15    |

| Mold Draft Angle Bottom β  |           | 5     | 10      | 15    | 5           | 10    | 15    |

### Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MO-011

Drawing No. C04-016

<sup>\*</sup> Controlling Parameter § Significant Characteristic

| W                          |               |

|----------------------------|---------------|

| Wake-up from SLEEP         | 195, 205      |

| Using Interrupts           | 205           |

| Watchdog Timer (WDT)       | 195, 203      |

| Associated Registers       | 204           |

| Control Register           | 203           |

| Postscaler                 | 203, 204      |

| Programming Considerations | 203           |

| RC Oscillator              | 203           |

| Time-out Period            | 203           |

| WCOL                       | 153           |

| WCOL Status Flag           | 153, 155, 158 |

|                            |               |

WWW, On-Line Support .....5

| X     |        |

|-------|--------|

| XORLW | <br>25 |

| XORWF | <br>25 |

|       |        |

|       |        |

|       |        |

|       |        |

|       |        |