Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                               |

| Number of I/O              | 34                                                                       |

| Program Memory Size        | 16KB (8K x 16)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 768 × 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

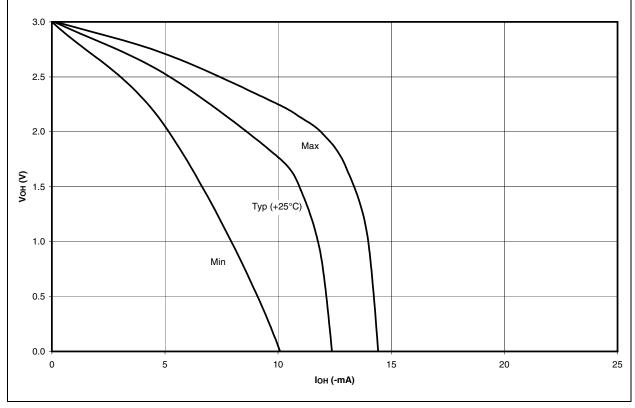

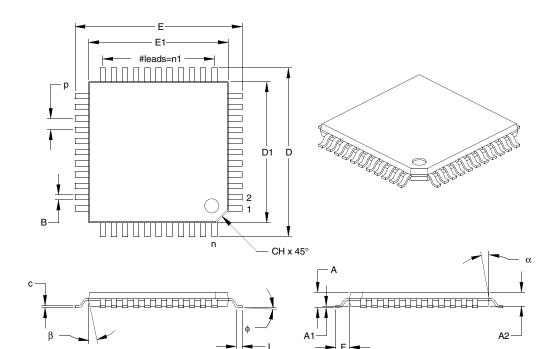

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-LCC (J-Lead)                                                          |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf442-i-l |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### PIC18F4X2 PINOUT I/O DESCRIPTIONS (CONTINUED) **TABLE 1-3:**

| Din Neme                              | Pi    | Pin Number |                |        | Buffer              | Description                                                                                                                                                                         |  |  |  |

|---------------------------------------|-------|------------|----------------|--------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name                              | DIP   | PLCC       | TQFP           | Туре   | Туре                | Description                                                                                                                                                                         |  |  |  |

|                                       |       |            |                |        |                     | PORTD is a bi-directional I/O port, or a Parallel Slave<br>Port (PSP) for interfacing to a microprocessor port.<br>These pins have TTL input buffers when PSP module<br>is enabled. |  |  |  |

| RD0/PSP0                              | 19    | 21         | 38             | I/O    | ST<br>TTL           | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                           |  |  |  |

| RD1/PSP1                              | 20    | 22         | 39             | I/O    | ST<br>TTL           | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                           |  |  |  |

| RD2/PSP2                              | 21    | 23         | 40             | I/O    | ST<br>TTL           | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                           |  |  |  |

| RD3/PSP3                              | 22    | 24         | 41             | I/O    | ST<br>TTL           | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                           |  |  |  |

| RD4/PSP4                              | 27    | 30         | 2              | I/O    | ST<br>TTL           | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                           |  |  |  |

| RD5/PSP5                              | 28    | 31         | 3              | I/O    | ST<br>TTL           | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                           |  |  |  |

| RD6/PSP6                              | 29    | 32         | 4              | I/O    | ST<br>TTL           | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                           |  |  |  |

| RD7/PSP7                              | 30    | 33         | 5              | I/O    | ST<br>TTL           | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                           |  |  |  |

| RE0/RD/AN5<br>RE0<br>RD               | 8     | 9          | 25             | I/O    | ST<br>TTL           | PORTE is a bi-directional I/O port.<br>Digital I/O.<br>Read control for parallel slave port<br>(see also WR and CS pins).                                                           |  |  |  |

| AN5<br>RE1/WR/AN6<br><u>RE1</u><br>WR | 9     | 10         | 26             | I/O    | Analog<br>ST<br>TTL | Analog input 5.<br>Digital I/O.<br>Write control for parallel slave port                                                                                                            |  |  |  |

| AN6<br>RE2/ <del>CS</del> /AN7<br>RE2 | 10    | 11         | 27             | I/O    | Analog<br>ST        | (see CS and RD pins).<br>Analog input 6.<br>Digital I/O.                                                                                                                            |  |  |  |

| CS<br>AN7                             |       |            |                |        | TTL                 | Chip Select control for parallel slave port (see related $\overline{RD}$ and $\overline{WR}$ ).                                                                                     |  |  |  |

| Vss                                   | 12 21 | 13, 34     | 6 29           | Р      | Analog              | Analog input 7.<br>Ground reference for logic and I/O pins.                                                                                                                         |  |  |  |

| VDD                                   |       |            | 0, 29<br>7, 28 | г<br>Р |                     | Positive supply for logic and I/O pins.                                                                                                                                             |  |  |  |

| Legend: TTL = TTL                     |       |            |                | l .    | L                   | CMOS = CMOS compatible input or output                                                                                                                                              |  |  |  |

ST = Schmitt Trigger input with CMOS levels

O = Output OD = Open Drain (no P diode to VDD) I = Input

P = Power

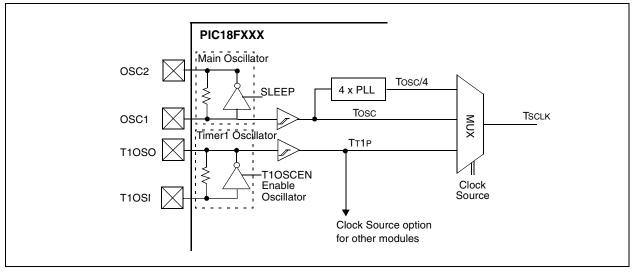

### 2.6 Oscillator Switching Feature

The PIC18FXX2 devices include a feature that allows the system clock source to be switched from the main oscillator to an alternate low frequency clock source. For the PIC18FXX2 devices, this alternate clock source is the Timer1 oscillator. If a low frequency crystal (32 kHz, for example) has been attached to the Timer1 oscillator pins and the Timer1 oscillator has been enabled, the device can switch to a Low Power Execution mode. Figure 2-7 shows a block diagram of the system clock sources. The clock switching feature is enabled <u>by programming the Oscillator Switching</u> Enable (OSCSEN) bit in Configuration Register1H to a '0'. Clock switching is disabled in an erased device. See Section 11.0 for further details of the Timer1 oscillator. See Section 19.0 for Configuration Register details.

#### FIGURE 2-7: DEVICE CLOCK SOURCES

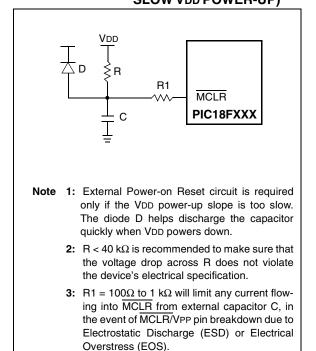

#### 3.1 Power-On Reset (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected. To take advantage of the POR circuitry, just tie the MCLR pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset delay. A minimum rise rate for VDD is specified (parameter D004). For a slow rise time, see Figure 3-2.

When the device starts normal operation (i.e., exits the RESET condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met.

FIGURE 3-2: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

#### 3.2 Power-up Timer (PWRT)

The Power-up Timer provides a fixed nominal time-out (parameter 33) only on power-up from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip-to-chip due to VDD, temperature and process variation. See DC parameter D033 for details.

### 3.3 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over (parameter 32). This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

#### 3.4 PLL Lock Time-out

With the PLL enabled, the time-out sequence following a Power-on Reset is different from other Oscillator modes. A portion of the Power-up Timer is used to provide a fixed time-out that is sufficient for the PLL to lock to the main oscillator frequency. This PLL lock time-out (TPLL) is typically 2 ms and follows the oscillator start-up time-out (OST).

#### 3.5 Brown-out Reset (BOR)

A configuration bit, BOREN, can disable (if clear/ programmed), or enable (if set) the Brown-out Reset circuitry. If VDD falls below parameter D005 for greater than parameter 35, the brown-out situation will reset the chip. A RESET may not occur if VDD falls below parameter D005 for less than parameter 35. The chip will remain in Brown-out Reset until VDD rises above BVDD. If the Power-up Timer is enabled, it will be invoked after VDD rises above BVDD; it then will keep the chip in RESET for an additional time delay (parameter 33). If VDD drops below BVDD while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be initialized. Once VDD rises above BVDD, the Power-up Timer will execute the additional time delay.

#### 3.6 Time-out Sequence

On power-up, the time-out sequence is as follows: First, PWRT time-out is invoked after the POR time delay has expired. Then, OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 3-3, Figure 3-4, Figure 3-5, Figure 3-6 and Figure 3-7 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 3-5). This is useful for testing purposes or to synchronize more than one PIC18FXXX device operating in parallel.

Table 3-2 shows the RESET conditions for some Special Function Registers, while Table 3-3 shows the RESET conditions for all the registers.

NOTES:

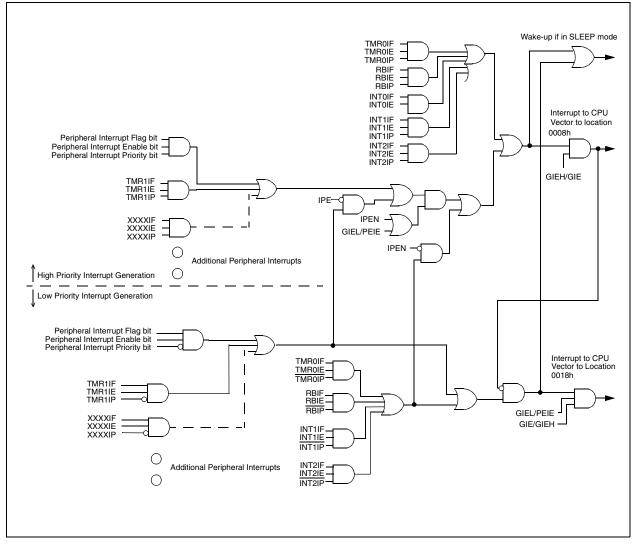

#### REGISTER 8-3: INTCON3 REGISTER

|       |                            |                                              |                |            | -            |           |              | -       |  |  |  |  |  |

|-------|----------------------------|----------------------------------------------|----------------|------------|--------------|-----------|--------------|---------|--|--|--|--|--|

|       | R/W-1                      | R/W-1                                        | U-0            | R/W-0      | R/W-0        | U-0       | R/W-0        | R/W-0   |  |  |  |  |  |

|       | INT2IP                     | INT1IP                                       | _              | INT2IE     | INT1IE       | —         | INT2IF       | INT1IF  |  |  |  |  |  |

|       | bit 7                      |                                              |                |            |              |           |              | bit 0   |  |  |  |  |  |

|       |                            |                                              |                |            |              |           |              |         |  |  |  |  |  |

| bit 7 | INT2IP: IN                 | INT2IP: INT2 External Interrupt Priority bit |                |            |              |           |              |         |  |  |  |  |  |

|       | 0 1                        | 1 = High priority                            |                |            |              |           |              |         |  |  |  |  |  |

|       | 0 = Low pr                 | 0 = Low priority                             |                |            |              |           |              |         |  |  |  |  |  |

| bit 6 | INT1IP: IN                 | INT1IP: INT1 External Interrupt Priority bit |                |            |              |           |              |         |  |  |  |  |  |

|       | • •                        | 1 = High priority                            |                |            |              |           |              |         |  |  |  |  |  |

|       | •                          | 0 = Low priority                             |                |            |              |           |              |         |  |  |  |  |  |

| bit 5 | Unimplemented: Read as '0' |                                              |                |            |              |           |              |         |  |  |  |  |  |

| bit 4 | INT2IE: IN                 | INT2IE: INT2 External Interrupt Enable bit   |                |            |              |           |              |         |  |  |  |  |  |

|       |                            | s the INT2 ex                                |                | •          |              |           |              |         |  |  |  |  |  |

|       |                            | es the INT2 e                                |                | •          |              |           |              |         |  |  |  |  |  |

| bit 3 |                            | T1 External I                                | -              |            |              |           |              |         |  |  |  |  |  |

|       |                            | s the INT1 ex                                |                |            |              |           |              |         |  |  |  |  |  |

|       |                            | es the INT1 e                                |                | upt        |              |           |              |         |  |  |  |  |  |

| bit 2 | -                          | ented: Read                                  |                |            |              |           |              |         |  |  |  |  |  |

| bit 1 |                            | T2 External I                                |                |            |              |           |              |         |  |  |  |  |  |

|       |                            | T2 external ir                               |                | <b>`</b>   | e cleared in | software) |              |         |  |  |  |  |  |

|       |                            | T2 external ir                               | •              |            |              |           |              |         |  |  |  |  |  |

| bit 0 |                            | T1 External I                                |                |            |              |           |              |         |  |  |  |  |  |

|       |                            | T1 external ir                               | •              | •          | e cleared in | software) |              |         |  |  |  |  |  |

|       | 0 = 1 ne IN                | T1 external ir                               | nterrupt did n | lot occur  |              |           |              |         |  |  |  |  |  |

|       |                            |                                              |                |            |              |           |              |         |  |  |  |  |  |

|       | Legend:                    |                                              |                |            |              |           |              |         |  |  |  |  |  |

|       | R = Reada                  | ble bit                                      | W = Wr         | itable bit | U = Unimp    | lemented  | bit, read as | '0'     |  |  |  |  |  |

|       | - n = Value                | at POR                                       | '1' = Bit      | is set     | '0' = Bit is | cleared   | x = Bit is ι | inknown |  |  |  |  |  |

**Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

| TABLE 9-5: | PORTC FUNCTIONS |

|------------|-----------------|

|            |                 |

| Name            | Bit# | Buffer Type | Function                                                                                                                               |

|-----------------|------|-------------|----------------------------------------------------------------------------------------------------------------------------------------|

| RC0/T1OSO/T1CKI | bit0 | ST          | Input/output port pin or Timer1 oscillator output/Timer1 clock input.                                                                  |

| RC1/T1OSI/CCP2  | bit1 | ST          | Input/output port pin, Timer1 oscillator input, or Capture2 input/<br>Compare2 output/PWM output when CCP2MX configuration bit is set. |

| RC2/CCP1        | bit2 | ST          | Input/output port pin or Capture1 input/Compare1 output/PWM1 output.                                                                   |

| RC3/SCK/SCL     | bit3 | ST          | RC3 can also be the synchronous serial clock for both SPI and $I^2C$ modes.                                                            |

| RC4/SDI/SDA     | bit4 | ST          | RC4 can also be the SPI Data In (SPI mode) or Data I/O ( $I^2$ C mode).                                                                |

| RC5/SDO         | bit5 | ST          | Input/output port pin or Synchronous Serial Port data output.                                                                          |

| RC6/TX/CK       | bit6 | ST          | Input/output port pin, Addressable USART Asynchronous Transmit, or Addressable USART Synchronous Clock.                                |

| RC7/RX/DT       | bit7 | ST          | Input/output port pin, Addressable USART Asynchronous Receive, or Addressable USART Synchronous Data.                                  |

Legend: ST = Schmitt Trigger input

#### TABLE 9-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Name  | Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |             |             |           |           |           |  |  | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |

|-------|-------------------------------------------------|-------------|-------------|-----------|-----------|-----------|--|--|----------------------|---------------------------------|

| PORTC | RC7                                             | RC6         | xxxx xxxx   | uuuu uuuu |           |           |  |  |                      |                                 |

| LATC  | LATC Da                                         | ta Output F |             | xxxx xxxx | uuuu uuuu |           |  |  |                      |                                 |

| TRISC | PORTC I                                         | Data Direct | ion Registe |           | 1111 1111 | 1111 1111 |  |  |                      |                                 |

Legend: x = unknown, u = unchanged

| Name       | Bit# | Buffer Type           | Function                                                                                                                                                                                          |

|------------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RE0/RD/AN5 | bit0 | ST/TTL <sup>(1)</sup> | Input/output port pin or read control input in Parallel Slave Port mode<br>or analog input:<br>RD                                                                                                 |

|            |      |                       | <ul><li>1 = Not a read operation</li><li>0 = Read operation. Reads PORTD register (if chip selected).</li></ul>                                                                                   |

| RE1/WR/AN6 | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or write control input in Parallel Slave Port mode<br>or analog input:<br>WR<br>1 = Not a write operation<br>0 = Write operation. Writes PORTD register (if chip selected). |

| RE2/CS/AN7 | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or chip select control input in Parallel Slave Port<br>mode or analog input:<br><u>CS</u><br>1 = Device is not selected<br>0 = Device is selected                           |

| TABLE 9-9: FURTE FUNCTIONS | <b>TABLE 9-9:</b> | PORTE FUNCTIONS |

|----------------------------|-------------------|-----------------|

|----------------------------|-------------------|-----------------|

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2 Bit 1 Bit 0 |              | Bit 0 | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |

|--------|-------|-------|-------|---------|-------|-------------------|--------------|-------|----------------------|---------------------------------|

| PORTE  | _     | —     | _     | _       | _     | RE2 RE1 RE0       |              | 000   | 000                  |                                 |

| LATE   | _     | _     |       | —       | _     | LATE Data         | Output Reg   | ister | xxx                  | uuu                             |

| TRISE  | IBF   | OBF   | IBOV  | PSPMODE | _     | PORTE Da          | ta Direction | bits  | 0000 -111            | 0000 -111                       |

| ADCON1 | ADFM  | ADCS2 | _     | _       | PCFG3 | PCFG2             | PCFG1        | PCFG0 | 00 0000              | 00 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTE.

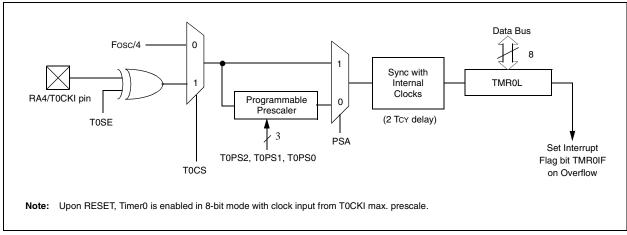

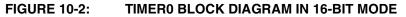

#### FIGURE 10-1: TIMER0 BLOCK DIAGRAM IN 8-BIT MODE

NOTES:

#### 13.2 Timer1 Oscillator

The Timer1 oscillator may be used as the clock source for Timer3. The Timer1 oscillator is enabled by setting the T1OSCEN (T1CON<3>) bit. The oscillator is a low power oscillator rated up to 200 KHz. See Section 11.0 for further details.

#### 13.3 Timer3 Interrupt

The TMR3 Register pair (TMR3H:TMR3L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR3 Interrupt, if enabled, is generated on overflow, which is latched in interrupt flag bit, TMR3IF (PIR2<1>). This interrupt can be enabled/disabled by setting/clearing TMR3 interrupt enable bit, TMR3IE (PIE2<1>).

#### 13.4 Resetting Timer3 Using a CCP Trigger Output

If the CCP module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer3.

| Note: | The special event triggers from the CCP |  |  |  |  |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|--|--|--|--|

|       | module will not set interrupt flag bit, |  |  |  |  |  |  |  |  |  |

|       | TMR3IF (PIR1<0>).                       |  |  |  |  |  |  |  |  |  |

Timer3 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer3 is running in Asynchronous Counter mode, this RESET operation may not work. In the event that a write to Timer3 coincides with a special event trigger from CCP1, the write will take precedence. In this mode of operation, the CCPR1H:CCPR1L registers pair effectively becomes the period register for Timer3.

| Name   | Bit 7                                               | Bit 6          | Bit 5     | Bit 4     | Bit 3     | Bit 2         | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |

|--------|-----------------------------------------------------|----------------|-----------|-----------|-----------|---------------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE/<br>GIEH                                        | PEIE/<br>GIEL  | TMR0IE    | INTOIE    | RBIE      | TMR0IF        | INTOIF | RBIF   | 0000 000x            | 0000 000u                       |

| PIR2   | EEIF BCLIF LVDIF TMR3IF CCP2IF                      |                |           |           |           |               |        |        | 0 0000               | 0 0000                          |

| PIE2   | EEIE BCLIE LVDIE TMR3IE CCP2IE                      |                |           |           |           |               |        |        | 0 0000               | 0 0000                          |

| IPR2   | EEIP BCLIP LVDIP TMR3IP CCP2IP                      |                |           |           |           |               |        | 1 1111 | 1 1111               |                                 |

| TMR3L  | Holding F                                           |                | xxxx xxxx | uuuu uuuu |           |               |        |        |                      |                                 |

| TMR3H  | Holding F                                           | Register for t |           | xxxx xxxx | uuuu uuuu |               |        |        |                      |                                 |

| T1CON  | RD16 — T1CKPS1 T1CKPS0 T1OSCEN T1SYNC TMR1CS TMR1ON |                |           |           |           |               |        |        | 0-00 0000            | u-uu uuuu                       |

| T3CON  | RD16                                                | T3CCP2         | T3CKPS1   | T3CKPS0   | T3CCP1    | <b>T3SYNC</b> | TMR3CS | TMR3ON | 0000 0000            | uuuu uuuu                       |

#### TABLE 13-1: REGISTERS ASSOCIATED WITH TIMER3 AS A TIMER/COUNTER

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

### 17.4 A/D Conversions

Figure 17-3 shows the operation of the A/D converter after the GO bit has been set. Clearing the GO/DONE bit during a conversion will abort the current conversion. The A/D result register pair will NOT be updated with the partially completed A/D conversion sample. That is, the ADRESH:ADRESL registers will continue to contain the value of the last completed conversion (or the last value written to the ADRESH:ADRESL registers). After the A/D conversion is aborted, a 2 TAD wait is required before the next acquisition is started. After this 2 TAD wait, acquisition on the selected channel is automatically started. The GO/DONE bit can then be set to start the conversion.

Note: The GO/DONE bit should NOT be set in the same instruction that turns on the A/D.

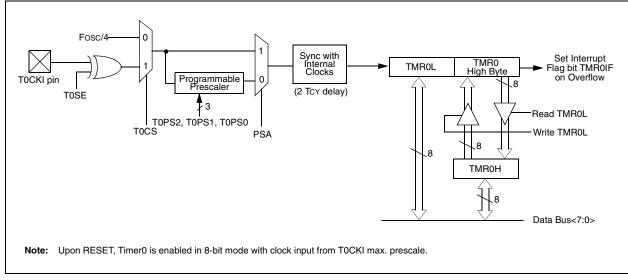

FIGURE 17-3: A/D CONVERSION TAD CYCLES

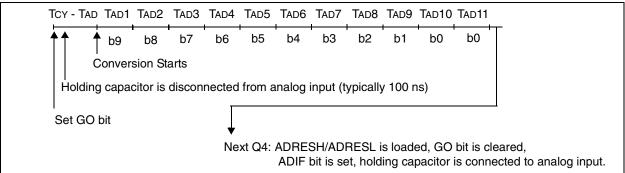

#### 17.4.1 A/D RESULT REGISTERS

The ADRESH:ADRESL register pair is the location where the 10-bit A/D result is loaded at the completion of the A/D conversion. This register pair is 16-bits wide. The A/D module gives the flexibility to left or right justify the 10-bit result in the 16-bit result register. The A/D Format Select bit (ADFM) controls this justification. Figure 17-4 shows the operation of the A/D result justification. The extra bits are loaded with '0's. When an A/D result will not overwrite these locations (A/D disable), these registers may be used as two general purpose 8-bit registers.

FIGURE 17-4: A/D RESULT JUSTIFICATION

| COMF                                                 | Complem                                                                                 | ent f                                                                                                                         |                                                                    |                                                                 |  |  |

|------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------|--|--|

| Syntax:                                              | [label] C                                                                               | [ <i>label</i> ] COMF f [,d [,a]                                                                                              |                                                                    |                                                                 |  |  |

| Operands:                                            | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                     |                                                                                                                               |                                                                    |                                                                 |  |  |

| Operation:                                           | $(\overline{f}) \rightarrow de$                                                         | est                                                                                                                           |                                                                    |                                                                 |  |  |

| Status Affected:                                     | N, Z                                                                                    |                                                                                                                               |                                                                    |                                                                 |  |  |

| Encoding:                                            | 0001                                                                                    | 11da f                                                                                                                        | Efff                                                               | ffff                                                            |  |  |

| Description:                                         | plemented<br>stored in V<br>stored bac<br>'a' is 0, the<br>selected, o<br>If 'a' = 1, t | nts of regis<br>J. If 'd' is 0,<br>W. If 'd' is 1<br>kk in registe<br>e Access E<br>overriding t<br>hen the ba<br>s per the E | , the re<br>I, the r<br>er 'f' (de<br>Bank w<br>the BS<br>ink will | esult is<br>esult is<br>efault). If<br>ill be<br>R value.<br>be |  |  |

| Words:                                               | 1                                                                                       |                                                                                                                               |                                                                    |                                                                 |  |  |

| Cycles:                                              | 1                                                                                       |                                                                                                                               |                                                                    |                                                                 |  |  |

| Q Cycle Activity:                                    |                                                                                         |                                                                                                                               |                                                                    |                                                                 |  |  |

| Q1                                                   | Q2                                                                                      | Q3                                                                                                                            |                                                                    | Q4                                                              |  |  |

| Decode                                               | Read<br>register 'f'                                                                    | Process<br>Data                                                                                                               |                                                                    | /rite to<br>stination                                           |  |  |

| Example:                                             | COMF                                                                                    | REG, 0,                                                                                                                       | 0                                                                  |                                                                 |  |  |

| Before Instruc<br>REG<br>After Instructi<br>REG<br>W | = 0x13                                                                                  |                                                                                                                               |                                                                    |                                                                 |  |  |

| CPFSEQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Compare                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                         | -                                                                                                                          |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                           | [ <i>label</i> ] CPFSEQ f[,a]                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                            |  |  |  |

| Operands:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0 ≤ f ≤ 25<br>a ∈ [0,1]                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                            |  |  |  |

| Operation:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | (f) – (W),<br>skip if (f)                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                            |  |  |  |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                           | d compariso                                                                                                                                                                                                                                                                                                                                                                                             | n)                                                                                                                         |  |  |  |

| Status Affecte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                           | None                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                            |  |  |  |

| Encoding:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                           | 0110 001a ffff ff                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                            |  |  |  |

| Description:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | memory<br>of W by p<br>subtraction<br>If 'f' = W,<br>tion is dis<br>cuted ins<br>cycle ins<br>Access E<br>riding the<br>the bank                                                                                                                          | Compares the contents of data<br>memory location 'f' to the contents<br>of W by performing an unsigned<br>subtraction.<br>If 'f' = W, then the fetched instruc-<br>tion is discarded and a NOP is exe<br>cuted instead, making this a two-<br>cycle instruction. If 'a' is 0, the<br>Access Bank will be selected, over<br>riding the BSR value. If 'a' = 1, the<br>the bank will be selected as per th |                                                                                                                            |  |  |  |

| Words:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | BSR valu<br>1                                                                                                                                                                                                                                             | ie (default).                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                            |  |  |  |

| Cycles:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                            |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1/0                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                            |  |  |  |

| Cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1(2)<br>Note: 3                                                                                                                                                                                                                                           | cycles if ski                                                                                                                                                                                                                                                                                                                                                                                           | p and follow                                                                                                               |  |  |  |

| Cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Note: 3                                                                                                                                                                                                                                                   | cycles if ski<br>y a 2-word ir                                                                                                                                                                                                                                                                                                                                                                          | p and follow                                                                                                               |  |  |  |

| Q Cycle Activ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Note: 3<br>b                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                            |  |  |  |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Note: 3<br>b<br>vity:<br>Q2                                                                                                                                                                                                                               | y a 2-word ir<br>Q3                                                                                                                                                                                                                                                                                                                                                                                     | nstruction.                                                                                                                |  |  |  |

| Q Cycle Activ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Note: 3<br>b<br>vity:<br>Q2<br>Read                                                                                                                                                                                                                       | y a 2-word ir<br>Q3<br>Process                                                                                                                                                                                                                                                                                                                                                                          | Q4<br>No                                                                                                                   |  |  |  |

| Q Cycle Activ<br>Q1<br>Decode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Note: 3<br>b<br>vity:<br>Q2                                                                                                                                                                                                                               | y a 2-word ir<br>Q3                                                                                                                                                                                                                                                                                                                                                                                     | nstruction.                                                                                                                |  |  |  |

| Q Cycle Activ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Note: 3<br>b<br>vity:<br>Q2<br>Read                                                                                                                                                                                                                       | y a 2-word ir<br>Q3<br>Process<br>Data                                                                                                                                                                                                                                                                                                                                                                  | Q4<br>No                                                                                                                   |  |  |  |

| Q Cycle Activ<br>Q1<br>Decode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Note: 3<br>b<br>vity:<br>Q2<br>Read<br>register 'f'                                                                                                                                                                                                       | y a 2-word ir<br>Q3<br>Process                                                                                                                                                                                                                                                                                                                                                                          | Q4<br>No<br>operation                                                                                                      |  |  |  |

| Q Cycle Activ<br>Q1<br>Decode<br>If skip:<br>Q1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Note: 3<br>b<br>vity:<br>Q2<br>Read<br>register 'f'<br>Q2<br>No                                                                                                                                                                                           | y a 2-word ir<br>Q3<br>Process<br>Data<br>Q3                                                                                                                                                                                                                                                                                                                                                            | Anstruction.<br>Q4<br>No<br>operation<br>Q4                                                                                |  |  |  |