Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40MHz                                                                    |

| Connectivity               | I²C, SPI, UART/USART                                                     |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                               |

| Number of I/O              | 34                                                                       |

| Program Memory Size        | 16KB (8K x 16)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 768 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf442-i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

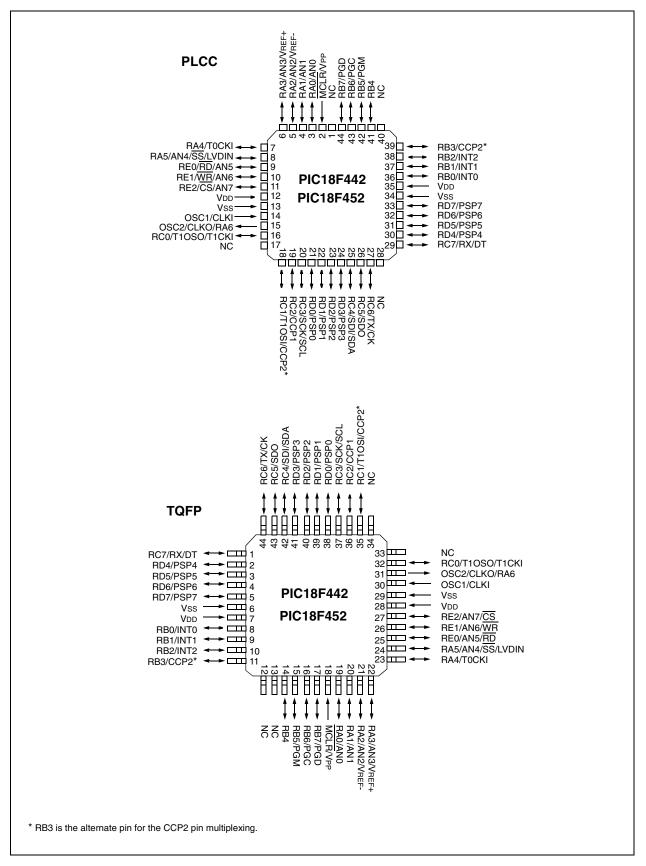

#### **Pin Diagrams**

## TABLE 1-2: PIC18F2X2 PINOUT I/O DESCRIPTIONS (CONTINUED)

| Din Nome            | Pin N | umber | Pin  | Buffer | Description                                                     |  |  |  |  |

|---------------------|-------|-------|------|--------|-----------------------------------------------------------------|--|--|--|--|

| Pin Name            | DIP   | SOIC  | Туре | Туре   | Description                                                     |  |  |  |  |

|                     |       |       |      |        | PORTC is a bi-directional I/O port.                             |  |  |  |  |

| RC0/T1OSO/T1CKI     | 11    | 11    |      |        |                                                                 |  |  |  |  |

| RC0                 |       |       | I/O  | ST     | Digital I/O.                                                    |  |  |  |  |

| T1OSO               |       |       | 0    | _      | Timer1 oscillator output.                                       |  |  |  |  |

| T1CKI               |       |       | I.   | ST     | Timer1/Timer3 external clock input.                             |  |  |  |  |

| RC1/T1OSI/CCP2      | 12    | 12    |      |        |                                                                 |  |  |  |  |

| RC1                 |       |       | I/O  | ST     | Digital I/O.                                                    |  |  |  |  |

| T1OSI               |       |       | I.   | CMOS   | Timer1 oscillator input.                                        |  |  |  |  |

| CCP2                |       |       | I/O  | ST     | Capture2 input, Compare2 output, PWM2 output.                   |  |  |  |  |

| RC2/CCP1            | 13    | 13    |      |        |                                                                 |  |  |  |  |

| RC2                 |       |       | I/O  | ST     | Digital I/O.                                                    |  |  |  |  |

| CCP1                |       |       | I/O  | ST     | Capture1 input/Compare1 output/PWM1 output.                     |  |  |  |  |

| RC3/SCK/SCL         | 14    | 14    |      |        |                                                                 |  |  |  |  |

| RC3                 |       |       | I/O  | ST     | Digital I/O.                                                    |  |  |  |  |

| SCK                 |       |       | I/O  | ST     | Synchronous serial clock input/output for SPI mode.             |  |  |  |  |

| SCL                 |       |       | I/O  | ST     | Synchronous serial clock input/output for I <sup>2</sup> C mode |  |  |  |  |

| RC4/SDI/SDA         | 15    | 15    |      |        |                                                                 |  |  |  |  |

| RC4                 |       |       | I/O  | ST     | Digital I/O.                                                    |  |  |  |  |

| SDI                 |       |       | I.   | ST     | SPI Data In.                                                    |  |  |  |  |

| SDA                 |       |       | I/O  | ST     | I <sup>2</sup> C Data I/O.                                      |  |  |  |  |

| RC5/SDO             | 16    | 16    |      |        |                                                                 |  |  |  |  |

| RC5                 |       | _     | I/O  | ST     | Digital I/O.                                                    |  |  |  |  |

| SDO                 |       |       | 0    | _      | SPI Data Out.                                                   |  |  |  |  |

| RC6/TX/CK           | 17    | 17    |      |        |                                                                 |  |  |  |  |

| RC6                 |       | -     | I/O  | ST     | Digital I/O.                                                    |  |  |  |  |

| ТХ                  |       |       | 0    | _      | USART Asynchronous Transmit.                                    |  |  |  |  |

| СК                  |       |       | I/O  | ST     | USART Synchronous Clock (see related RX/DT).                    |  |  |  |  |

| RC7/RX/DT           | 18    | 18    |      |        |                                                                 |  |  |  |  |

| RC7                 |       |       | I/O  | ST     | Digital I/O.                                                    |  |  |  |  |

| RX                  |       |       | Ι    | ST     | USART Asynchronous Receive.                                     |  |  |  |  |

| DT                  |       |       | I/O  | ST     | USART Synchronous Data (see related TX/CK).                     |  |  |  |  |

| Vss                 | 8, 19 | 8, 19 | Р    | —      | Ground reference for logic and I/O pins.                        |  |  |  |  |

| Vdd                 | 20    | 20    | Р    |        | Positive supply for logic and I/O pins.                         |  |  |  |  |

| Legend: TTL = TTL o |       |       |      |        | CMOS = CMOS compatible input or output                          |  |  |  |  |

ST = Schmitt Trigger input with CMOS levels

I = Input P = Power

O = Output OD = Open Drain (no P diode to VDD)

| TABLE 3-3:             |     | INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |        |     |                                    |                                                               |                                 |  |  |  |  |  |  |

|------------------------|-----|---------------------------------------------------------|--------|-----|------------------------------------|---------------------------------------------------------------|---------------------------------|--|--|--|--|--|--|

| Register               | Арг | olicabl                                                 | e Devi | ces | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset<br>RESET Instruction<br>Stack Resets | Wake-up via WDT<br>or Interrupt |  |  |  |  |  |  |

| IPR2                   | 242 | 442                                                     | 252    | 452 | 1 1111                             | 1 1111                                                        | u uuuu                          |  |  |  |  |  |  |

| PIR2                   | 242 | 442                                                     | 252    | 452 | 0 0000                             | 0 0000                                                        | u uuuu <b>(1)</b>               |  |  |  |  |  |  |

| PIE2                   | 242 | 442                                                     | 252    | 452 | 0 0000                             | 0 0000                                                        | u uuuu                          |  |  |  |  |  |  |

| IPR1                   | 242 | 442                                                     | 252    | 452 | 1111 1111                          | 1111 1111                                                     | uuuu uuuu                       |  |  |  |  |  |  |

| IFRI                   | 242 | 442                                                     | 252    | 452 | -111 1111                          | -111 1111                                                     | -uuu uuuu                       |  |  |  |  |  |  |

|                        | 242 | 442                                                     | 252    | 452 | 0000 0000                          | 0000 0000                                                     | uuuu uuuu <b>(1)</b>            |  |  |  |  |  |  |

| PIR1                   | 242 | 442                                                     | 252    | 452 | -000 0000                          | -000 0000                                                     | -uuu uuuu <b>(1)</b>            |  |  |  |  |  |  |

|                        | 242 | 442                                                     | 252    | 452 | 0000 0000                          | 0000 0000                                                     | uuuu uuuu                       |  |  |  |  |  |  |

| PIE1                   | 242 | 442                                                     | 252    | 452 | -000 0000                          | -000 0000                                                     | -uuu uuuu                       |  |  |  |  |  |  |

| TRISE                  | 242 | 442                                                     | 252    | 452 | 0000 -111                          | 0000 -111                                                     | uuuu -uuu                       |  |  |  |  |  |  |

| TRISD                  | 242 | 442                                                     | 252    | 452 | 1111 1111                          | 1111 1111                                                     | uuuu uuuu                       |  |  |  |  |  |  |

| TRISC                  | 242 | 442                                                     | 252    | 452 | 1111 1111                          | 1111 1111                                                     | սսսս սսսս                       |  |  |  |  |  |  |

| TRISB                  | 242 | 442                                                     | 252    | 452 | 1111 1111                          | 1111 1111                                                     | սսսս սսսս                       |  |  |  |  |  |  |

| TRISA <sup>(5,6)</sup> | 242 | 442                                                     | 252    | 452 | -111 1111 <b>(5)</b>               | -111 1111 <b>(5)</b>                                          | -uuu uuuu <b>(5)</b>            |  |  |  |  |  |  |

| LATE                   | 242 | 442                                                     | 252    | 452 | xxx                                | uuu                                                           | uuu                             |  |  |  |  |  |  |

| LATD                   | 242 | 442                                                     | 252    | 452 | XXXX XXXX                          | uuuu uuuu                                                     | սսսս սսսս                       |  |  |  |  |  |  |

| LATC                   | 242 | 442                                                     | 252    | 452 | xxxx xxxx                          | uuuu uuuu                                                     | uuuu uuuu                       |  |  |  |  |  |  |

| LATB                   | 242 | 442                                                     | 252    | 452 | xxxx xxxx                          | uuuu uuuu                                                     | uuuu uuuu                       |  |  |  |  |  |  |

| LATA <sup>(5,6)</sup>  | 242 | 442                                                     | 252    | 452 | -xxx xxxx(5)                       | -uuu uuuu <b>(5)</b>                                          | -uuu uuuu <b>(5)</b>            |  |  |  |  |  |  |

| PORTE                  | 242 | 442                                                     | 252    | 452 | 000                                | 000                                                           | uuu                             |  |  |  |  |  |  |

| PORTD                  | 242 | 442                                                     | 252    | 452 | xxxx xxxx                          | uuuu uuuu                                                     | սսսս սսսս                       |  |  |  |  |  |  |

| PORTC                  | 242 | 442                                                     | 252    | 452 | xxxx xxxx                          | uuuu uuuu                                                     | սսսս սսսս                       |  |  |  |  |  |  |

| PORTB                  | 242 | 442                                                     | 252    | 452 | xxxx xxxx                          | uuuu uuuu                                                     | սսսս սսսս                       |  |  |  |  |  |  |

| PORTA <sup>(5,6)</sup> | 242 | 442                                                     | 252    | 452 | -x0x 0000 <b>(5)</b>               | -u0u 0000 <b>(5)</b>                                          | -uuu uuuu <b>(5)</b>            |  |  |  |  |  |  |

TABLE 3-3:

INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

**Note 1:** One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- **3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 4: See Table 3-2 for RESET value for specific condition.

- 5: Bit 6 of PORTA, LATA, and TRISA are enabled in ECIO and RCIO Oscillator modes only. In all other Oscillator modes, they are disabled and read '0'.

- 6: Bit 6 of PORTA, LATA and TRISA are not available on all devices. When unimplemented, they are read '0'.

| File Name | Bit 7                    | Bit 6          | Bit 5                     | Bit 4           | Bit 3         | Bit 2          | Bit 1                   | Bit 0   | Value on POR, BOR | Details<br>on page: |

|-----------|--------------------------|----------------|---------------------------|-----------------|---------------|----------------|-------------------------|---------|-------------------|---------------------|

| OSCCON    | —                        | —              | —                         | —               | —             | —              | —                       | SCS     | 0                 | 21                  |

| LVDCON    | _                        | —              | IRVST                     | LVDEN           | LVDL3         | LVDL2          | LVDL1                   | LVDL0   | 00 0101           | 191                 |

| WDTCON    | _                        | —              | —                         | —               | _             | —              | —                       | SWDTE   | 0                 | 203                 |

| RCON      | IPEN                     | _              | _                         | RI              | TO            | PD             | POR                     | BOR     | 01 11qq           | 53, 28, 84          |

| TMR1H     | Timer1 Reg               | xxxx xxxx      | 107                       |                 |               |                |                         |         |                   |                     |

| TMR1L     | Timer1 Reg               | xxxx xxxx      | 107                       |                 |               |                |                         |         |                   |                     |

| T1CON     | RD16                     |                | T1CKPS1                   | T1CKPS0         | T1OSCEN       | T1SYNC         | TMR1CS                  | TMR10N  | 0-00 0000         | 107                 |

| TMR2      | Timer2 Reg               | ister          |                           |                 |               |                |                         |         | 0000 0000         | 111                 |

| PR2       | Timer2 Peri              | od Register    |                           |                 |               |                |                         |         | 1111 1111         | 112                 |

| T2CON     | _                        | TOUTPS3        | TOUTPS2                   | TOUTPS1         | TOUTPS0       | TMR2ON         | T2CKPS1                 | T2CKPS0 | -000 0000         | 111                 |

| SSPBUF    | SSP Receiv               | e Buffer/Tran  | smit Register             | ſ               |               | •              | •                       |         | xxxx xxxx         | 125                 |

| SSPADD    | SSP Addres               | ss Register in | I <sup>2</sup> C Slave me | ode. SSP Bau    | ud Rate Reloa | ad Register ir | I <sup>2</sup> C Master | mode.   | 0000 0000         | 134                 |

| SSPSTAT   | SMP                      | CKE            | D/A                       | Р               | S             | R/W            | UA                      | BF      | 0000 0000         | 126                 |

| SSPCON1   | WCOL                     | SSPOV          | SSPEN                     | CKP             | SSPM3         | SSPM2          | SSPM1                   | SSPM0   | 0000 0000         | 127                 |

| SSPCON2   | GCEN                     | ACKSTAT        | ACKDT                     | ACKEN           | RCEN          | PEN            | RSEN                    | SEN     | 0000 0000         | 137                 |

| ADRESH    | A/D Result               | Register High  | Byte                      | •               | •             | •              | •                       | •       | xxxx xxxx         | 187,188             |

| ADRESL    | A/D Result               | Register Low   | Byte                      |                 |               |                |                         |         | xxxx xxxx         | 187,188             |

| ADCON0    | ADCS1                    | ADCS0          | CHS2                      | CHS1            | CHS0          | GO/DONE        |                         | ADON    | 0000 00-0         | 181                 |

| ADCON1    | ADFM                     | ADCS2          | —                         | —               | PCFG3         | PCFG2          | PCFG1                   | PCFG0   | 00 0000           | 182                 |

| CCPR1H    | Capture/Co               | mpare/PWM      | Register1 Hig             | h Byte          |               | •              | •                       |         | xxxx xxxx         | 121, 123            |

| CCPR1L    | Capture/Co               | mpare/PWM      | Register1 Lov             | w Byte          |               |                |                         |         | xxxx xxxx         | 121, 123            |

| CCP1CON   |                          |                | DC1B1                     | DC1B0           | CCP1M3        | CCP1M2         | CCP1M1                  | CCP1M0  | 00 0000           | 117                 |

| CCPR2H    | Capture/Co               | mpare/PWM      | Register2 Hig             | gh Byte         |               | •              | •                       |         | xxxx xxxx         | 121, 123            |

| CCPR2L    | Capture/Co               | mpare/PWM      | Register2 Lov             | w Byte          |               |                |                         |         | xxxx xxxx         | 121, 123            |

| CCP2CON   | —                        | _              | DC2B1                     | DC2B0           | CCP2M3        | CCP2M2         | CCP2M1                  | CCP2M0  | 00 0000           | 117                 |

| TMR3H     | Timer3 Reg               | ister High Byt | e                         |                 |               |                |                         |         | xxxx xxxx         | 113                 |

| TMR3L     | Timer3 Reg               | ister Low Byte | e                         |                 |               |                |                         |         | xxxx xxxx         | 113                 |

| T3CON     | RD16                     | T3CCP2         | T3CKPS1                   | T3CKPS0         | T3CCP1        | T3SYNC         | TMR3CS                  | TMR3ON  | 0000 0000         | 113                 |

| SPBRG     | USART1 Ba                | aud Rate Gen   | erator                    | •               |               | •              | •                       |         | 0000 0000         | 168                 |

| RCREG     | USART1 Re                | eceive Regist  | ər                        |                 |               |                |                         |         | 0000 0000         | 175, 178,<br>180    |

| TXREG     | USART1 Transmit Register |                |                           |                 |               |                |                         |         | 0000 0000         | 173, 176,<br>179    |

| TXSTA     | CSRC                     | TX9            | TXEN                      | SYNC            | —             | BRGH           | TRMT                    | TX9D    | 0000 -010         | 166                 |

| RCSTA     | SPEN                     | RX9            | SREN                      | CREN            | ADDEN         | FERR           | OERR                    | RX9D    | 0000 000x         | 167                 |

| EEADR     | Data EEPR                | OM Address     | Register                  |                 | •             |                |                         | •       | 0000 0000         | 65, 69              |

| EEDATA    | Data EEPR                | OM Data Reg    | ister                     |                 |               |                |                         |         | 0000 0000         | 69                  |

| EECON2    | Data EEPR                | OM Control R   | legister 2 (no            | t a physical re | egister)      |                |                         |         |                   | 65, 69              |

| EECON1    | EEPGD                    | CFGS           | _                         | FREE            | WRERR         | WREN           | WR                      | RD      | xx-0 x000         | 66                  |

Legend: x = unknown, u = unchanged, - = unimplemented, q = value depends on condition Note 1: RA6 and associated bits are configured as port pins in RCIO and ECIO Oscillator mode only and read '0' in all other Oscillator modes. 2: Bit 21 of the TBLPTRU allows access to the device configuration bits.

3: These registers and bits are reserved on the PIC18F2X2 devices; always maintain these clear.

## 5.2 Control Registers

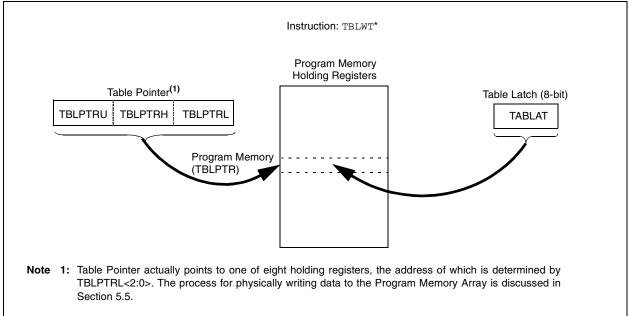

Several control registers are used in conjunction with the TBLRD and TBLWT instructions. These include the:

- EECON1 register

- EECON2 register

- TABLAT register

- TBLPTR registers

## 5.2.1 EECON1 AND EECON2 REGISTERS

EECON1 is the control register for memory accesses.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the memory write and erase sequences.

Control bit EEPGD determines if the access will be a program or data EEPROM memory access. When clear, any subsequent operations will operate on the data EEPROM memory. When set, any subsequent operations will operate on the program memory.

Control bit CFGS determines if the access will be to the configuration registers or to program memory/data EEPROM memory. When set, subsequent operations will operate on configuration registers, regardless of EEPGD (see "Special Features of the CPU", Section 19.0). When clear, memory selection access is determined by EEPGD.

The FREE bit, when set, will allow a program memory erase operation. When the FREE bit is set, the erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a MCLR Reset or a WDT Time-out Reset during normal operation. In these situations, the user can check the WRERR bit and rewrite the location. It is necessary to reload the data and address registers (EEDATA and EEADR), due to RESET values of zero.

Control bit WR initiates write operations. This bit cannot be cleared, only set, in software. It is cleared in hardware at the completion of the write operation. The inability to clear the WR bit in software prevents the accidental or premature termination of a write operation.

Note: Interrupt flag bit EEIF, in the PIR2 register, is set when the write is complete. It must be cleared in software.

|         | U-0                                                                                                                                               | U-0                             | U-0           | R/W-0          | R/W-0         | R/W-0       | R/W-0  | R/W-0  |  |  |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------|----------------|---------------|-------------|--------|--------|--|--|--|

|         | —                                                                                                                                                 |                                 |               | EEIF           | BCLIF         | LVDIF       | TMR3IF | CCP2IF |  |  |  |

|         | bit 7                                                                                                                                             |                                 |               |                |               |             |        | bit 0  |  |  |  |

|         |                                                                                                                                                   |                                 |               |                |               |             |        |        |  |  |  |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                        |                                 |               |                |               |             |        |        |  |  |  |

| bit 4   | EEIF: Data                                                                                                                                        | a EEPROM/F                      | LASH Write    | Operation Int  | terrupt Flag  | bit         |        |        |  |  |  |

|         |                                                                                                                                                   | rite operation                  |               |                |               |             |        |        |  |  |  |

|         |                                                                                                                                                   | rite operation                  | •             |                | ot been sta   | rted        |        |        |  |  |  |

| bit 3   |                                                                                                                                                   | s Collision In                  |               |                | <b>.</b>      |             |        |        |  |  |  |

|         |                                                                                                                                                   | collision occu<br>collision occ | •             | e cleared in s | software)     |             |        |        |  |  |  |

| bit 2   |                                                                                                                                                   | w Voltage De                    |               | Elog bit       |               |             |        |        |  |  |  |

|         |                                                                                                                                                   | /oltage condi                   |               | •              | eared in soft | ware)       |        |        |  |  |  |

|         |                                                                                                                                                   | vice voltage                    |               |                |               |             |        |        |  |  |  |

| bit 1   | TMR3IF: T                                                                                                                                         | MR3 Overflo                     | w Interrupt F | lag bit        | -             | -           |        |        |  |  |  |

|         | 1 = TMR3                                                                                                                                          | register over                   | lowed (must   | be cleared in  | n software)   |             |        |        |  |  |  |

|         | 0 <b>= TMR3</b>                                                                                                                                   | register did n                  | ot overflow   |                |               |             |        |        |  |  |  |

| bit 0   | CCP2IF: C                                                                                                                                         | CPx Interrup                    | t Flag bit    |                |               |             |        |        |  |  |  |

|         | Capture m                                                                                                                                         |                                 |               |                |               |             |        |        |  |  |  |

|         |                                                                                                                                                   | 1 register ca                   |               |                | leared in so  | oftware)    |        |        |  |  |  |

|         |                                                                                                                                                   | R1 register c                   | apture occur  | red            |               |             |        |        |  |  |  |

|         | $\frac{\text{Compare r}}{1 - \Lambda \text{TMB}}$                                                                                                 |                                 | mnare match   | occurred (m    | ust ha claa   | rad in coft | ware)  |        |  |  |  |

|         | <ul> <li>1 = A TMR1 register compare match occurred (must be cleared in software)</li> <li>0 = No TMR1 register compare match occurred</li> </ul> |                                 |               |                |               |             |        |        |  |  |  |

|         | PWM mod                                                                                                                                           | •                               |               |                |               |             |        |        |  |  |  |

|         | Unused in                                                                                                                                         | this mode                       |               |                |               |             |        |        |  |  |  |

|         |                                                                                                                                                   |                                 |               |                |               |             |        |        |  |  |  |

|         | Legend:                                                                                                                                           |                                 |               |                |               |             |        |        |  |  |  |

W = Writable bit

'1' = Bit is set

## REGISTER 8-5: PIR2: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2

R = Readable bit

- n = Value at POR

U = Unimplemented bit, read as '0'

x = Bit is unknown

'0' = Bit is cleared

## TABLE 9-1: PORTA FUNCTIONS

| Name             | Bit# | Buffer | Function                                                                                                     |

|------------------|------|--------|--------------------------------------------------------------------------------------------------------------|

| RA0/AN0          | bit0 | TTL    | Input/output or analog input.                                                                                |

| RA1/AN1          | bit1 | TTL    | Input/output or analog input.                                                                                |

| RA2/AN2/VREF-    | bit2 | TTL    | Input/output or analog input or VREF                                                                         |

| RA3/AN3/VREF+    | bit3 | TTL    | Input/output or analog input or VREF+.                                                                       |

| RA4/T0CKI        | bit4 | ST     | Input/output or external clock input for Timer0.<br>Output is open drain type.                               |

| RA5/SS/AN4/LVDIN | bit5 | TTL    | Input/output or slave select input for synchronous serial port or analog input, or low voltage detect input. |

| OSC2/CLKO/RA6    | bit6 | TTL    | OSC2 or clock output or I/O pin.                                                                             |

Legend: TTL = TTL input, ST = Schmitt Trigger input

## TABLE 9-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Name   | Bit 7 | Bit 6    | Bit 5       | Bit 4      | Bit 3 | Bit 2 | Bit 1 | Bit 0     | Value on<br>POR,<br>BOR | Value on<br>All Other<br>RESETS |

|--------|-------|----------|-------------|------------|-------|-------|-------|-----------|-------------------------|---------------------------------|

| PORTA  |       | RA6      | RA5         | RA4        | RA3   | RA2   | RA1   | RA0       | -x0x 0000               | -u0u 0000                       |

| LATA   |       | LATA Dat | a Output F  | legister   |       |       |       |           | -xxx xxxx               | -uuu uuuu                       |

| TRISA  | _     | PORTA D  | ata Directi | on Registe | er    |       |       | -111 1111 | -111 1111               |                                 |

| ADCON1 | ADFM  | ADCS2    | _           | _          | PCFG3 | PCFG2 | PCFG1 | PCFG0     | 00 0000                 | 00 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

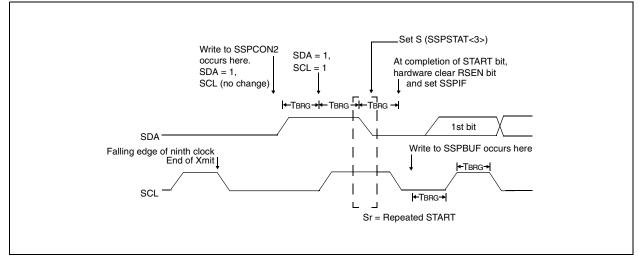

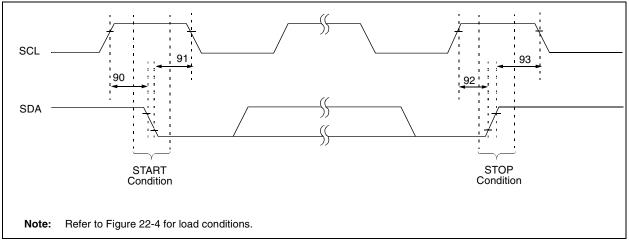

## 15.4.9 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated START condition occurs when the RSEN bit (SSPCON2<1>) is programmed high and the I<sup>2</sup>C logic module is in the IDLE state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the baud rate generator is loaded with the contents of SSPADD<5:0> and begins counting. The SDA pin is released (brought high) for one baud rate generator count (TBRG). When the baud rate generator times out, if SDA is sampled high, the SCL pin will be de-asserted (brought high). When SCL is sampled high, the baud rate generator is reloaded with the contents of SSPADD<6:0> and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. Following this, the RSEN bit (SSPCON2<1>) will be automatically cleared and the baud rate generator will not be reloaded, leaving the SDA pin held low. As soon as a START condition is detected on the SDA and SCL pins, the S bit (SSPSTAT<3>) will be set. The SSPIF bit will not be set until the baud rate generator has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- 2: A bus collision during the Repeated START condition occurs if:

- SDA is sampled low when SCL goes from low to high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data "1".

Immediately following the SSPIF bit getting set, the user may write the SSPBUF with the 7-bit address in 7-bit mode, or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode) or eight bits of data (7-bit mode).

#### 15.4.9.1 WCOL Status Flag

If the user writes the SSPBUF when a Repeated START sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing of the lower 5 bits of SSPCON2 is disabled until the Repeated START condition is complete.

## FIGURE 15-20: REPEAT START CONDITION WAVEFORM

## 16.1 USART Baud Rate Generator (BRG)

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. In Asynchronous mode, bit BRGH (TXSTA<2>) also controls the baud rate. In Synchronous mode, bit BRGH is ignored. Table 16-1 shows the formula for computation of the baud rate for different USART modes, which only apply in Master mode (internal clock).

Given the desired baud rate and Fosc, the nearest integer value for the SPBRG register can be calculated using the formula in Table 16-1. From this, the error in baud rate can be determined. Example 16-1 shows the calculation of the baud rate error for the following conditions:

- Fosc = 16 MHz

- Desired Baud Rate = 9600

- BRGH = 0

- SYNC = 0

It may be advantageous to use the high baud rate (BRGH = 1) even for slower baud clocks. This is because the FOSC/(16(X + 1)) equation can reduce the baud rate error in some cases.

Writing a new value to the SPBRG register causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

#### 16.1.1 SAMPLING

The data on the RC7/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin.

## EXAMPLE 16-1: CALCULATING BAUD RATE ERROR

| Desired Baud Rate    | = Fosc / (64 (X + 1))                                                                                                                    |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Solving for X:       |                                                                                                                                          |

| X<br>X<br>X          | = ((Fosc / Desired Baud Rate) / 64) - 1<br>= ((16000000 / 9600) / 64) - 1<br>= [25.042] = 25                                             |

| Calculated Baud Rate | = 1600000 / (64 (25 + 1)) = 9615                                                                                                         |

| Error                | <ul> <li><u>(Calculated Baud Rate – Desired Baud Rate)</u><br/>Desired Baud Rate</li> <li>(9615 – 9600) / 9600</li> <li>0.16%</li> </ul> |

|                      |                                                                                                                                          |

#### TABLE 16-1: BAUD RATE FORMULA

| SYNC | BRGH = 0 (Low Speed)                      | BRGH = 1 (High Speed)      |

|------|-------------------------------------------|----------------------------|

| 0    | (Asynchronous) Baud Rate = FOSC/(64(X+1)) | Baud Rate = Fosc/(16(X+1)) |

| 1    | (Synchronous) Baud Rate = Fosc/(4(X+1))   | N/A                        |

Legend: X = value in SPBRG (0 to 255)

#### TABLE 16-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Name  | Bit 7   | Bit 6     | Bit 5      | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |

|-------|---------|-----------|------------|-------|-------|-------|-------|-------|----------------------|---------------------------------|

| TXSTA | CSRC    | TX9       | TXEN       | SYNC  |       | BRGH  | TRMT  | TX9D  | 0000 -010            | 0000 -010                       |

| RCSTA | SPEN    | RX9       | SREN       | CREN  | ADDEN | FERR  | OERR  | RX9D  | x00- 0000            | 0000 -00x                       |

| SPBRG | Baud Ra | te Genera | ator Regis | ster  |       |       |       |       | 0000 0000            | 0000 0000                       |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used by the BRG.

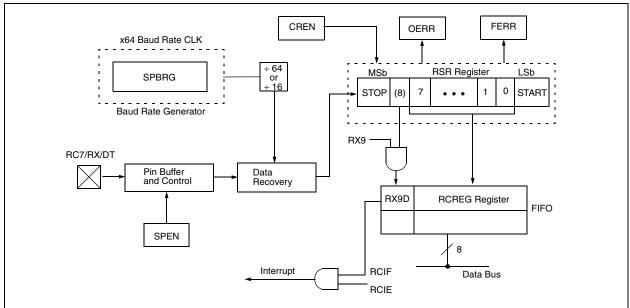

## 16.2.2 USART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 16-4. The data is received on the RC7/RX/DT pin and drives the data recovery block. The data recovery block is actually a high speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at Fosc. This mode would typically be used in RS-232 systems.

To set up an Asynchronous Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH (Section 16.1).

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, set enable bit RCIE.

- 4. If 9-bit reception is desired, set bit RX9.

- 5. Enable the reception by setting bit CREN.

- 6. Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 7. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

## 16.2.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is required, set the BRGH bit.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are required, set the RCEN bit and select the desired priority level with the RCIP bit.

- 4. Set the RX9 bit to enable 9-bit reception.

- 5. Set the ADDEN bit to enable address detect.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF bit will be set when reception is complete. The interrupt will be acknowledged if the RCIE and GIE bits are set.

- 8. Read the RCSTA register to determine if any error occurred during reception, as well as read bit 9 of data (if applicable).

- 9. Read RCREG to determine if the device is being addressed.

- 10. If any error occurred, clear the CREN bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and interrupt the CPU.

## FIGURE 16-4: USART RECEIVE BLOCK DIAGRAM

| BTG                    | Bit Toggl                                                                               | e f                                         |                              |                                 |  |  |  |  |  |

|------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------|------------------------------|---------------------------------|--|--|--|--|--|

| Syntax:                | [ <i>label</i> ] B                                                                      | [label] BTG f,b[,a]                         |                              |                                 |  |  |  |  |  |

| Operands:              | $\begin{array}{l} 0 \leq f \leq 25 \\ 0 \leq b \leq 7 \\ a \in [0,1] \end{array}$       | • = • = ·                                   |                              |                                 |  |  |  |  |  |

| Operation:             | $(\overline{f} < b >) \to f$                                                            | <b></b>                                     |                              |                                 |  |  |  |  |  |

| Status Affected:       | None                                                                                    |                                             |                              |                                 |  |  |  |  |  |

| Encoding:              | 0111                                                                                    | bbba                                        | ffff                         | ffff                            |  |  |  |  |  |

| Description:           | Bit 'b' in da<br>inverted. I<br>will be sel<br>value. If 'a<br>selected a<br>(default). | f 'a' is 0, t<br>ected, ove<br>t' = 1, thei | he Acces<br>erriding the ban | ss Bank<br>he BSR<br>ik will be |  |  |  |  |  |

| Words:                 | 1                                                                                       | 1                                           |                              |                                 |  |  |  |  |  |

| Cycles:                | 1                                                                                       | 1                                           |                              |                                 |  |  |  |  |  |

| Q Cycle Activity:      |                                                                                         |                                             |                              |                                 |  |  |  |  |  |

| Q1                     | Q2                                                                                      | Q3                                          | (                            | Q4                              |  |  |  |  |  |

| Decode                 | Read<br>register 'f'                                                                    | Process<br>Data                             |                              | /rite<br>ster 'f'               |  |  |  |  |  |

| Example:               | BTG I                                                                                   | PORTC,                                      | 4, 0                         |                                 |  |  |  |  |  |

| Before Instru<br>PORTC |                                                                                         | 0101 <b>[0x7</b>                            | 5]                           |                                 |  |  |  |  |  |

| After Instruc<br>PORTC | tion:<br>= 0110 (                                                                       | 0101 <b>[0x6</b>                            | 5]                           |                                 |  |  |  |  |  |

| Syntax:      |                 | [ <i>label</i> ] B                                                             | [ <i>label</i> ] BOV n                                                                                                                                                                                                                                                                 |      |                       |  |  |

|--------------|-----------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------|--|--|

| -            | rands:          | -128 ≤ n ≤                                                                     | 127                                                                                                                                                                                                                                                                                    |      |                       |  |  |

| Operation:   |                 |                                                                                | if overflow bit is '1'<br>(PC) + 2 + 2n $\rightarrow$ PC                                                                                                                                                                                                                               |      |                       |  |  |

| Statu        | us Affected:    | None                                                                           |                                                                                                                                                                                                                                                                                        |      |                       |  |  |

| Enco         | oding:          | 1110                                                                           | 0100                                                                                                                                                                                                                                                                                   | nnnn | nnnn                  |  |  |

| Description: |                 | program v<br>The 2's co<br>added to t<br>have incre<br>instruction<br>PC+2+2n. | If the Overflow bit is '1', then the<br>program will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will<br>have incremented to fetch the next<br>instruction, the new address will be<br>PC+2+2n. This instruction is then<br>a two-cycle instruction. |      |                       |  |  |

| Wor          | ds:             | 1                                                                              |                                                                                                                                                                                                                                                                                        |      |                       |  |  |

| Cycl         | es:             | 1(2)                                                                           |                                                                                                                                                                                                                                                                                        |      |                       |  |  |

|              | Cycle Activity  | _                                                                              | 00                                                                                                                                                                                                                                                                                     |      | 04                    |  |  |

|              | Q1<br>Decode    | Q2<br>Read literal                                                             | Q3<br>Process                                                                                                                                                                                                                                                                          |      | Q4<br>Vrite to PC     |  |  |

|              | Decode          | 'n'                                                                            | Data                                                                                                                                                                                                                                                                                   |      | while to r C          |  |  |

|              | No<br>operation | No<br>operation                                                                | No<br>operation                                                                                                                                                                                                                                                                        |      | No<br>operation       |  |  |

|              |                 |                                                                                |                                                                                                                                                                                                                                                                                        |      |                       |  |  |

| lf N         | o Jump:         |                                                                                |                                                                                                                                                                                                                                                                                        |      |                       |  |  |

| lf N         | o Jump:<br>Q1   | Q2                                                                             | Q3                                                                                                                                                                                                                                                                                     |      | Q4                    |  |  |

| lf N         | -               | Q2<br>Read literal<br>'n'                                                      | Q3<br>Proces<br>Data                                                                                                                                                                                                                                                                   | SS   | Q4<br>No<br>operation |  |  |

|              | Q1              | Read literal                                                                   | Proces<br>Data                                                                                                                                                                                                                                                                         | SS   | No                    |  |  |

| IORLW            | Inclusive                            | OR lite       | ral with | w        |

|------------------|--------------------------------------|---------------|----------|----------|

| Syntax:          | [ label ]                            | IORLW         | k        |          |

| Operands:        | $0 \le k \le 25$                     | 5             |          |          |

| Operation:       | (W) .OR.                             | $k \to W$     |          |          |

| Status Affected: | N, Z                                 |               |          |          |

| Encoding:        | 0000                                 | 1001          | kkkk     | kkkk     |

| Description:     | The conte<br>the eight-<br>placed in | bit literal   |          | •••      |

| Words:           | 1                                    |               |          |          |

| Cycles:          | 1                                    |               |          |          |

| Q Cycle Activity | :                                    |               |          |          |

| Q1               | Q2                                   | Q3            | 3        | Q4       |

| Decode           | Read<br>literal 'k'                  | Proce<br>Data |          | ite to W |

| Example:         | IORLW                                | 0x35          |          |          |

| Before Instru    | uction                               |               |          |          |

| W                | = 0x9A                               |               |          |          |

| After Instruc    | tion                                 |               |          |          |

| W                | = 0xBF                               |               |          |          |

|                  |                                      |               |          |          |

| IORWF                   | Inclusive                                                          | OR W with                                                                                                                | f                                                            |  |  |

|-------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--|--|

| Syntax:                 | [ label ]                                                          | IORWF f[                                                                                                                 | ,d [,a]                                                      |  |  |

| Operands:               | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                              |                                                                                                                          |                                                              |  |  |

| Operation:              | (W) .OR.                                                           | (f) $\rightarrow$ dest                                                                                                   |                                                              |  |  |

| Status Affected:        | N, Z                                                               |                                                                                                                          |                                                              |  |  |

| Encoding:               | 0001                                                               | 00da ff                                                                                                                  | ff ffff                                                      |  |  |

|                         | is 1, the re<br>register 'f'<br>Access B<br>riding the<br>the bank | esult is place<br>esult is place<br>(default). If '<br>ank will be se<br>BSR value. I<br>will be selecte<br>e (default). | d back in<br>a' is 0, the<br>elected, ove<br>f 'a' = 1, ther |  |  |

| Words:                  | 1                                                                  |                                                                                                                          |                                                              |  |  |

| Cycles:                 | 1                                                                  |                                                                                                                          |                                                              |  |  |

| Q Cycle Activity:       |                                                                    |                                                                                                                          |                                                              |  |  |

| Q1                      | Q2                                                                 | Q3                                                                                                                       | Q4                                                           |  |  |

| Decode                  | Read<br>register 'f'                                               | Process<br>Data                                                                                                          | Write to destination                                         |  |  |

| <u>Example</u> :        | IORWF R                                                            | ESULT, 0, 1                                                                                                              | L                                                            |  |  |

| Before Instru<br>RESULT |                                                                    |                                                                                                                          |                                                              |  |  |

| Delote instruction |   |      |  |  |  |

|--------------------|---|------|--|--|--|

| RESULT             | = | 0x13 |  |  |  |

| W                  | = | 0x91 |  |  |  |

| After Instruction  |   |      |  |  |  |

| DECULT             | _ | 0v12 |  |  |  |

| RESULT | = | 0x13 |

|--------|---|------|

| W      | = | 0x93 |

| SLEEP                                        | Enter SL                                                       | EEP mode                        |         | SUBFWB         | Subtrac         | t f from W w                      | ith borrow                         |

|----------------------------------------------|----------------------------------------------------------------|---------------------------------|---------|----------------|-----------------|-----------------------------------|------------------------------------|

| Syntax:                                      | [ label ]                                                      | SLEEP                           |         | Syntax:        | [ label ]       | SUBFWB                            | f [,d [,a]                         |

| Operands:                                    | None                                                           | None                            |         | Operands:      |                 | $0 \le f \le 255$                 |                                    |

| Operation:                                   | $00h \rightarrow W$                                            |                                 |         |                | d ∈ [0,1]       |                                   |                                    |

|                                              |                                                                | T postscaler,                   |         | Operation      | a ∈ [0,1]       |                                   | .+                                 |

|                                              | $1 \rightarrow \underline{TO}, \\ 0 \rightarrow \overline{PD}$ |                                 |         | Operation:     |                 | $-(\overline{C}) \rightarrow des$ | il                                 |

| Status Affected:                             | TO, PD                                                         |                                 |         | Status Affecte | · ·             | <u>г</u>                          |                                    |

| Encoding:                                    | 0000                                                           | 0000 000                        | 00 0011 | Encoding:      | 0101            |                                   | ff ffff                            |

| Description:                                 |                                                                | er-down statu                   |         | Description:   |                 | register 'f' an from W (2's o     |                                    |

| Description.                                 |                                                                | The time-out                    |         |                |                 | If 'd' is 0, the                  |                                    |

|                                              |                                                                | et. Watchdog                    |         |                |                 | W. If 'd' is 1,                   |                                    |

|                                              |                                                                | aler are clea<br>essor is put i |         |                |                 |                                   | efault). If 'a' is II be selected, |

|                                              |                                                                | the oscillate                   |         |                |                 |                                   | lue. If 'a' is 1,                  |

| Words:                                       | 1                                                              |                                 |         |                |                 | bank will be s                    |                                    |

| Cycles:                                      | 1                                                              |                                 |         |                | -               | SR value (de                      | etault).                           |

| Q Cycle Activity:                            |                                                                |                                 |         | Words:         | 1               |                                   |                                    |

| Q1                                           | Q2                                                             | Q3                              | Q4      | Cycles:        | 1               |                                   |                                    |

| Decode                                       | No                                                             | Process                         | Go to   | Q Cycle Acti   | -               | 0.0                               | <i></i>                            |

|                                              | operation                                                      | Data                            | sleep   | Q1<br>Decode   | Q2<br>Read      | Q3<br>Process                     | Q4<br>Write to                     |

| Example:                                     | SLEEP                                                          |                                 |         | Decou          | register 'f'    | Data                              | destination                        |

| Before Instru                                |                                                                |                                 |         | Example 1:     | SUBFWB          | REG, 1,                           | 0                                  |

| <u>TO</u> =<br>PD =                          | ?                                                              |                                 |         |                | struction       |                                   |                                    |

| PD =<br>After Instruct                       | -                                                              |                                 |         | REG            |                 |                                   |                                    |

| $\frac{\overline{TO}}{\overline{PD}} = PD =$ | 1†                                                             |                                 |         | W<br>C         | = 2<br>= 1      |                                   |                                    |

| PD =                                         | 0                                                              |                                 |         | After Ins      | -               |                                   |                                    |

| † If WDT causes                              | s wake-up, tl                                                  | his bit is clea                 | red.    | REG            |                 |                                   |                                    |

|                                              |                                                                |                                 |         | W<br>C         | = 2<br>= 0      |                                   |                                    |

|                                              |                                                                |                                 |         | Z              | = 0<br>= 1 : re | esult is negativ                  | /e                                 |

|                                              |                                                                |                                 |         | Example 2:     | SUBFWB          | REG, 0,                           |                                    |

|                                              |                                                                |                                 |         | Before Ir      | struction       |                                   |                                    |

|                                              |                                                                |                                 |         | REG            |                 |                                   |                                    |

|                                              |                                                                |                                 |         | W<br>C         | = 5<br>= 1      |                                   |                                    |

|                                              |                                                                |                                 |         | After Ins      |                 |                                   |                                    |

|                                              |                                                                |                                 |         | REG<br>W       | = 2<br>= 3      |                                   |                                    |

|                                              |                                                                |                                 |         | С              | = 1             |                                   |                                    |

|                                              |                                                                |                                 |         | Z<br>N         | = 0<br>= 0 ; re | esult is positiv                  | е                                  |

|                                              |                                                                |                                 |         | Example 3:     | SUBFWB          | REG, 1,                           | 0                                  |

|                                              |                                                                |                                 |         |                | struction       |                                   |                                    |

|                                              |                                                                |                                 |         | REG            | = 1             |                                   |                                    |

W 2 = С = 0 After Instruction REG = 0 W = 2 C Z N = = 1 1 ; result is zero ò =

| XORWF                    | Exclusive                                                                                                                    | e OR W v                                                                                                | vith f                                                                                   |                                                         |  |  |  |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------|--|--|--|

| Syntax:                  | [ label ] )                                                                                                                  | [label] XORWF f[,d[,a]                                                                                  |                                                                                          |                                                         |  |  |  |

| Operands:                | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                                                                                        |                                                                                                         |                                                                                          |                                                         |  |  |  |

| Operation:               | (W) .XOR                                                                                                                     | . (f) $\rightarrow$ de                                                                                  | st                                                                                       |                                                         |  |  |  |

| Status Affected          | l: N, Z                                                                                                                      |                                                                                                         |                                                                                          |                                                         |  |  |  |