Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 34                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 768 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

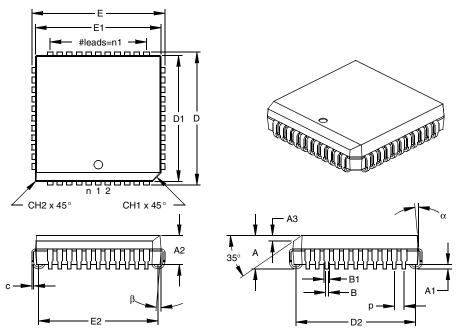

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf442t-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

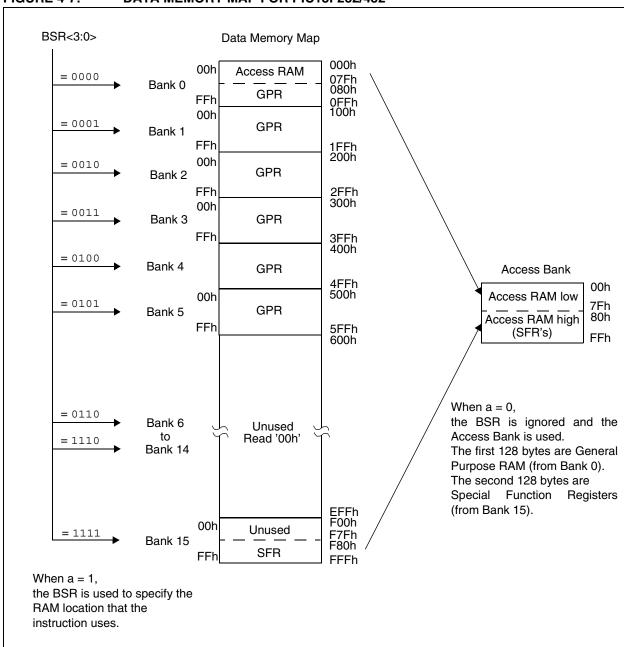

FIGURE 4-7: DATA MEMORY MAP FOR PIC18F252/452

#### **EXAMPLE 5-3: WRITING TO FLASH PROGRAM MEMORY (CONTINUED)**

| PROGRAM_ME | MORY                           |               |   |                               |

|------------|--------------------------------|---------------|---|-------------------------------|

|            | BSF                            | EECON1, EEPGD | ; | point to FLASH program memory |

|            | BCF                            | EECON1, CFGS  | ; | access FLASH program memory   |

|            | BSF EECON1,WREN BCF INTCON,GIE |               | ; | enable write to memory        |

|            |                                |               | ; | disable interrupts            |

|            | MOVLW 55h                      |               |   |                               |

| Required   | MOVWF                          | EECON2        | ; | write 55h                     |

| Sequence   | MOVLW                          | AAh           |   |                               |

|            | MOVWF                          | EECON2        | ; | write AAh                     |

|            | BSF                            | EECON1,WR     | ; | start program (CPU stall)     |

|            | BSF                            | INTCON, GIE   | ; | re-enable interrupts          |

|            | DECFSZ                         | COUNTER_HI    | ; | loop until done               |

|            | BRA                            | PROGRAM_LOOP  |   |                               |

|            | BCF                            | EECON1, WREN  | ; | disable write to memory       |

|            |                                |               |   |                               |

#### 5.5.2 WRITE VERIFY

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

# 5.5.3 UNEXPECTED TERMINATION OF WRITE OPERATION

If a write is terminated by an unplanned event, such as loss of power or an unexpected RESET, the memory location just programmed should be verified and reprogrammed if needed. The WRERR bit is set when a write operation is interrupted by a MCLR Reset, or a WDT Time-out Reset during normal operation. In these situations, users can check the WRERR bit and rewrite the location.

# 5.5.4 PROTECTION AGAINST SPURIOUS WRITES

To protect against spurious writes to FLASH program memory, the write initiate sequence must also be followed. See "Special Features of the CPU" (Section 19.0) for more detail.

# 5.6 FLASH Program Operation During Code Protection

See "Special Features of the CPU" (Section 19.0) for details on code protection of FLASH program memory.

TABLE 5-2: REGISTERS ASSOCIATED WITH PROGRAM FLASH MEMORY

| Address | Name    | Bit 7        | Bit 6         | Bit 5       | Bit 4     | Bit 3                 | Bit 2      | Bit 1      | Bit 0  | Value on:<br>POR, BOR | Value on<br>All Other<br>RESETS |

|---------|---------|--------------|---------------|-------------|-----------|-----------------------|------------|------------|--------|-----------------------|---------------------------------|

| FF8h    | TBLPTRU | _            | _             | bit21       | J         | Memory T<br>R<20:16>) | able Point | er Upper B | yte    | 00 0000               | 00 0000                         |

| FF7h    | TBPLTRH | Program I    | Memory Ta     | able Pointe | er High B | yte (TBLP             | ΓR<15:8>)  |            |        | 0000 0000             | 0000 0000                       |

| FF6h    | TBLPTRL | Program I    | Memory Ta     | able Point  | er High B | yte (TBLP             | ΓR<7:0>)   |            |        | 0000 0000             | 0000 0000                       |

| FF5h    | TABLAT  | Program I    | Memory Ta     | ble Latch   |           |                       |            |            |        | 0000 0000             | 0000 0000                       |

| FF2h    | INTCON  | GIE/<br>GIEH | PEIE/<br>GIEL | TMR0IE      | INTE      | RBIE                  | TMR0IF     | INTF       | RBIF   | 0000 000x             | 0000 000u                       |

| FA7h    | EECON2  | EEPROM       | Control R     | egister2 (  | not a phy | sical regist          | er)        |            |        | _                     | _                               |

| FA6h    | EECON1  | EEPGD        | CFGS          | _           | FREE      | WRERR                 | WREN       | WR         | RD     | xx-0 x000             | uu-0 u000                       |

| FA2h    | IPR2    | _            | _             | -           | EEIP      | BCLIP                 | LVDIP      | TMR3IP     | CCP2IP | 1 1111                | 1 1111                          |

| FA1h    | PIR2    | _            | _             | _           | EEIF      | BCLIF                 | LVDIF      | TMR3IF     | CCP2IF | 0 0000                | 0 0000                          |

| FA0h    | PIE2    | _            | _             | _           | EEIE      | BCLIE                 | LVDIE      | TMR3IE     | CCP2IE | 0 0000                | 0 0000                          |

Legend: x = unknown, u = unchanged, r = reserved, - = unimplemented read as '0'. Shaded cells are not used during FLASH/EEPROM access.

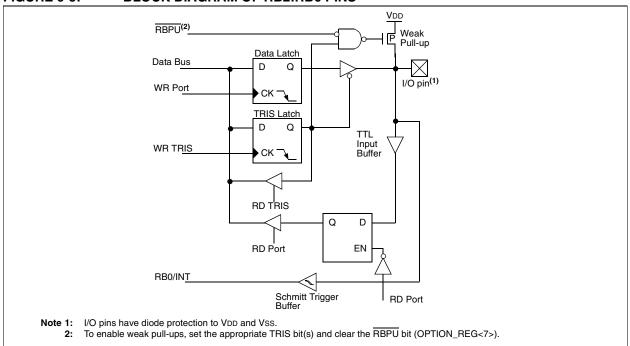

### FIGURE 9-5: BLOCK DIAGRAM OF RB2:RB0 PINS

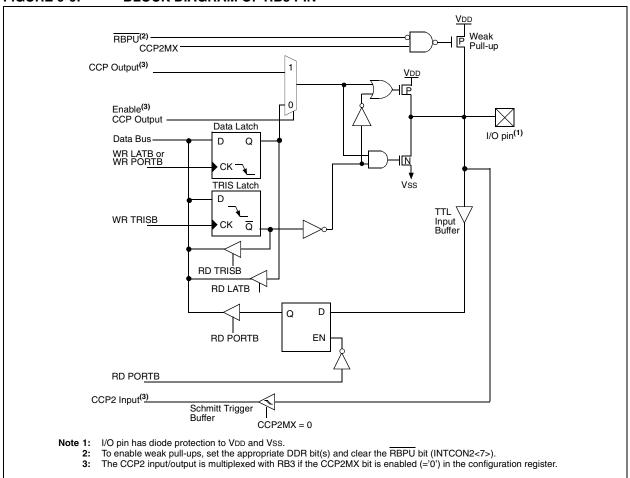

### FIGURE 9-6: BLOCK DIAGRAM OF RB3 PIN

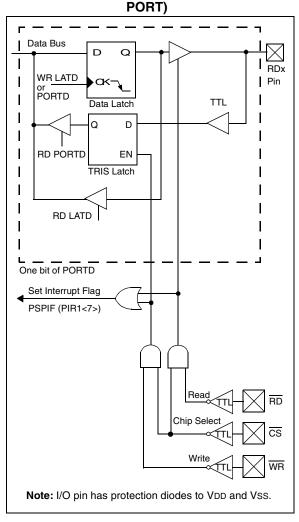

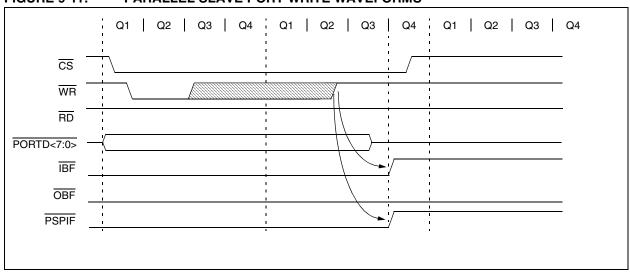

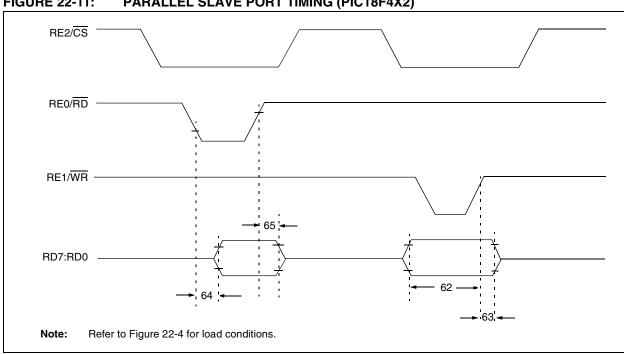

#### 9.6 Parallel Slave Port

The Parallel Slave Port is implemented on the 40-pin devices only (PIC18F4X2).

PORTD operates as an 8-bit wide Parallel Slave Port, or microprocessor port when control bit, PSPMODE (TRISE<4>) is set. It is asynchronously readable and writable by the external world through RD control input pin, RE0/RD and WR control input pin, RE1/WR.

It can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting bit PSPMODE enables port pin RE0/RD to be the  $\overline{RD}$  input,  $\overline{RE1/WR}$  to be the  $\overline{WR}$  input and RE2/ $\overline{CS}$  to be the  $\overline{CS}$  (chip select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set). The A/D port configuration bits PCFG2:PCFG0 (ADCON1<2:0>) must be set, which will configure pins RE2:RE0 as digital I/O.

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$  lines are first detected low. A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low.

The PORTE I/O pins become control inputs for the microprocessor port when bit PSPMODE (TRISE<4>) is set. In this mode, the user must make sure that the TRISE<2:0> bits are set (pins are configured as digital inputs), and the ADCON1 is configured for digital I/O. In this mode, the input buffers are TTL.

FIGURE 9-10: PORTD AND PORTE BLOCK DIAGRAM (PARALLEL SLAVE

FIGURE 9-11: PARALLEL SLAVE PORT WRITE WAVEFORMS

#### 11.0 TIMER1 MODULE

The Timer1 module timer/counter has the following features:

- 16-bit timer/counter (two 8-bit registers; TMR1H and TMR1L)

- Readable and writable (both registers)

- · Internal or external clock select

- Interrupt-on-overflow from FFFFh to 0000h

- · RESET from CCP module special event trigger

Figure 11-1 is a simplified block diagram of the Timer1 module.

Register 11-1 details the Timer1 control register. This register controls the Operating mode of the Timer1 module, and contains the Timer1 oscillator enable bit (T1OSCEN). Timer1 can be enabled or disabled by setting or clearing control bit TMR1ON (T1CON<0>).

#### REGISTER 11-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0 | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|---------|---------|---------|--------|--------|--------|

| RD16  | _   | T1CKPS1 | T1CKPS0 | T10SCEN | T1SYNC | TMR1CS | TMR10N |

| bit 7 |     |         |         |         |        |        | bit 0  |

- bit 7 RD16: 16-bit Read/Write Mode Enable bit

- 1 = Enables register Read/Write of Timer1 in one 16-bit operation

- 0 = Enables register Read/Write of Timer1 in two 8-bit operations

- bit 6 Unimplemented: Read as '0'

- bit 5-4 T1CKPS1:T1CKPS0: Timer1 Input Clock Prescale Select bits

- 11 = 1:8 Prescale value

- 10 = 1:4 Prescale value

- 01 = 1:2 Prescale value

- 00 = 1:1 Prescale value

- bit 3 T10SCEN: Timer1 Oscillator Enable bit

- 1 = Timer1 Oscillator is enabled

- 0 = Timer1 Oscillator is shut-off

The oscillator inverter and feedback resistor are turned off to eliminate power drain.

bit 2 T1SYNC: Timer1 External Clock Input Synchronization Select bit

#### When TMR1CS = 1:

- 1 = Do not synchronize external clock input

- 0 = Synchronize external clock input

#### When TMR1CS = 0:

This bit is ignored. Timer1 uses the internal clock when TMR1CS = 0.

- bit 1 TMR1CS: Timer1 Clock Source Select bit

- 1 = External clock from pin RC0/T1OSO/T13CKI (on the rising edge)

- 0 = Internal clock (Fosc/4)

- bit 0 TMR10N: Timer1 On bit

- 1 = Enables Timer1

- 0 = Stops Timer1

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### 18.1 Control Register

The Low Voltage Detect Control register controls the operation of the Low Voltage Detect circuitry.

#### REGISTER 18-1: LVDCON REGISTER

| U-0   | U-0 | R-0   | R/W-0 | R/W-0 | R/W-1 | R/W-0 | R/W-1 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| _     | _   | IRVST | LVDEN | LVDL3 | LVDL2 | LVDL1 | LVDL0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

bit 7-6 Unimplemented: Read as '0'

bit 5 IRVST: Internal Reference Voltage Stable Flag bit

- 1 = Indicates that the Low Voltage Detect logic will generate the interrupt flag at the specified voltage range

- 0 = Indicates that the Low Voltage Detect logic will not generate the interrupt flag at the specified voltage range and the LVD interrupt should not be enabled

- bit 4 LVDEN: Low Voltage Detect Power Enable bit

- 1 = Enables LVD, powers up LVD circuit

- 0 = Disables LVD, powers down LVD circuit

- bit 3-0 LVDL3:LVDL0: Low Voltage Detection Limit bits

- 1111 = External analog input is used (input comes from the LVDIN pin)

- 1110 = 4.5V 4.77V

- 1101 = 4.2V 4.45V

- 1100 = 4.0V 4.24V

- 1011 = 3.8V 4.03V

- 1010 = 3.6V 3.82V

- 1001 = 3.5V 3.71V

- 1000 = 3.3V 3.50V

- 0111 = 3.0V 3.18V

- 0110 = 2.8V 2.97V

- 0101 = 2.7V 2.86V

- 0100 = 2.5V 2.65V

- 0011 = 2.4V 2.54V

- 0010 = 2.2V 2.33V

- 0001 = 2.0V 2.12V

- 0000 = Reserved

**Note:** LVDL3:LVDL0 modes which result in a trip point below the valid operating voltage of the device are not tested.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### REGISTER 19-10: CONFIGURATION REGISTER 7 LOW (CONFIG7L: BYTE ADDRESS 30000Ch)

| U-0   | U-0 | U-0 | U-0 | R/C-1                | R/C-1                | R/C-1 | R/C-1 |

|-------|-----|-----|-----|----------------------|----------------------|-------|-------|

| _     | _   | _   | _   | EBTR3 <sup>(1)</sup> | EBTR2 <sup>(1)</sup> | EBTR1 | EBTR0 |

| bit 7 |     |     |     |                      |                      |       | bit 0 |

bit 7-4 Unimplemented: Read as '0'

bit 3 **EBTR3:** Table Read Protection bit<sup>(1)</sup>

1 = Block 3 (006000-007FFFh) not protected from Table Reads executed in other blocks 0 = Block 3 (006000-007FFFh) protected from Table Reads executed in other blocks

bit 2 **EBTR2:** Table Read Protection bit<sup>(1)</sup>

1 = Block 2 (004000-005FFFh) not protected from Table Reads executed in other blocks 0 = Block 2 (004000-005FFFh) protected from Table Reads executed in other blocks

bit 1 EBTR1: Table Read Protection bit

1 = Block 1 (002000-003FFFh) not protected from Table Reads executed in other blocks 0 = Block 1 (002000-003FFFh) protected from Table Reads executed in other blocks

bit 0 **EBTR0:** Table Read Protection bit

1 = Block 0 (000200h-001FFFh) not protected from Table Reads executed in other blocks

0 = Block 0 (000200h-001FFFh) protected from Table Reads executed in other blocks

Note 1: Unimplemented in PIC18FX42 devices; maintain this bit set.

### REGISTER 19-11: CONFIGURATION REGISTER 7 HIGH (CONFIG7H: BYTE ADDRESS 30000Dh)

| U-0   | R/C-1 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-----|-----|-----|-----|-----|-------|

| _     | EBTRB | _   | _   | _   | _   | _   | _     |

| bit 7 |       |     |     |     |     |     | bit 0 |

bit 7 Unimplemented: Read as '0'

bit 6 EBTRB: Boot Block Table Read Protection bit

1 = Boot Block (000000-0001FFh) not protected from Table Reads executed in other blocks

$_{0}$  = Boot Block (000000-0001FFh) protected from Table Reads executed in other blocks

bit 5-0 **Unimplemented:** Read as '0'

BRA Unconditional Branch

Syntax: [label] BRA n Operands:  $-1024 \le n \le 1023$

Operation:  $(PC) + 2 + 2n \rightarrow PC$

Status Affected: None

Encoding: 1101 0nnn nnnn nnnn

Description: Add the 2's complement number

Add the 2's complement number '2n' to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC+2+2n. This instruction is a

two-cycle instruction.

Words: 1 Cycles: 2

Q Cycle Activity:

| Q1        | Q2           | Q3        | Q4          |  |

|-----------|--------------|-----------|-------------|--|

| Decode    | Read literal | Process   | Write to PC |  |

|           | 'n'          | Data      |             |  |

| No        | No           | No        | No          |  |

| operation | operation    | operation | operation   |  |

Example: HERE BRA Jump

Before Instruction

PC = address (HERE)

After Instruction

PC = address (Jump)

BSF Bit Set f

Syntax: [ label ] BSF f,b[,a]

Operands:  $0 \le f \le 255$

$0 \le b \le 7$  $a \in [0,1]$

Operation:  $1 \rightarrow f < b >$

Status Affected: None

Encoding: 1000 bbba ffff ffff

Description: Bit 'b' in register 'f' is set. If 'a' is 0

Access Bank will be selected, overriding the BSR value. If 'a' = 1, then

the bank will be selected as per the

BSR value.

Words: 1 Cycles: 1

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4           |  |

|--------|--------------|---------|--------------|--|

| Decode | Read         | Process | Write        |  |

|        | register 'f' | Data    | register 'f' |  |

Example: BSF FLAG\_REG, 7, 1

Before Instruction

$FLAG_REG = 0x0A$

After Instruction

$FLAG_REG = 0x8A$

# PIC18FXX2

| RLNCF                | Rotate L                                                                     | eft f (no car                                                       | ry)                                         | RRCF                    | Rotate R                                                                                             | ight f throu                                                                       | gh Carry                                                                                                                     |

|----------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Syntax:              | [ label ]                                                                    | RLNCF f                                                             | [,d [,a]                                    | Syntax:                 | [ label ]                                                                                            | RRCF f[                                                                            | d [,a]                                                                                                                       |

| Operands:            | $0 \le f \le 25$<br>$d \in [0,1]$<br>$a \in [0,1]$                           | 55                                                                  |                                             | Operands:               | $0 \le f \le 25$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                   | 5                                                                                  |                                                                                                                              |

| Operation:           | $ \begin{array}{l} (f{<}n{>}) \to \\ (f{<}7{>}) \to \end{array} $            | dest <n+1>,<br/>dest&lt;0&gt;</n+1>                                 |                                             | Operation:              | $(f<0>) \rightarrow$                                                                                 |                                                                                    |                                                                                                                              |

| Status Affected:     | N, Z                                                                         |                                                                     |                                             |                         | $(C) \rightarrow de$                                                                                 | st                                                                                 |                                                                                                                              |

| Encoding:            | 0100                                                                         | 01da f                                                              | fff ffff                                    | Status Affected:        | C, N, Z                                                                                              |                                                                                    |                                                                                                                              |

| Description:         |                                                                              | ents of regis                                                       |                                             | Encoding:               | 0011                                                                                                 | 00da f                                                                             | fff ffff                                                                                                                     |

| Words:               | the result<br>the result<br>'f' (defaul<br>Bank will<br>the BSR<br>bank will | t is placed in<br>t is stored ba<br>t). If 'a' is 0,<br>be selected | , overriding<br>s 1, then the<br>as per the | Description:            | rotated or<br>the Carry<br>is placed<br>is placed<br>(default).<br>Bank will<br>the BSR<br>bank will | Flag. If 'd' i<br>in W. If 'd' is<br>back in reg<br>If 'a' is 0, th<br>be selected | right through<br>s 0, the result<br>s 1, the result<br>ister 'f'<br>e Access<br>I, overriding<br>s 1, then the<br>as per the |

| Cycles:              | 1                                                                            |                                                                     |                                             | Words:                  |                                                                                                      |                                                                                    |                                                                                                                              |

| Q Cycle Activity     | :                                                                            |                                                                     |                                             |                         | 1                                                                                                    |                                                                                    |                                                                                                                              |

| Q1                   | Q2                                                                           | Q3                                                                  | Q4                                          | Cycles:                 | 1                                                                                                    |                                                                                    |                                                                                                                              |

| Decode               | Read register 'f'                                                            | Process<br>Data                                                     | Write to destination                        | Q Cycle Activity:<br>Q1 | Q2                                                                                                   | Q3                                                                                 | Q4                                                                                                                           |

|                      | register i                                                                   | Data                                                                | destination                                 | Decode                  | Read                                                                                                 | Process                                                                            | Write to                                                                                                                     |

| Example:             | RLNCF                                                                        | REG, 1,                                                             | 0                                           | 200040                  | register 'f'                                                                                         | Data                                                                               | destination                                                                                                                  |

| Before Instru<br>REG | uction<br>= 1010 1                                                           | 1011                                                                |                                             | Example:                | RRCF                                                                                                 | REG, 0,                                                                            | 0                                                                                                                            |

| After Instruc        |                                                                              |                                                                     |                                             | Before Instru           |                                                                                                      |                                                                                    |                                                                                                                              |

| REG                  | = 0101 0                                                                     | )111                                                                |                                             | REG                     | = 1110                                                                                               | 0110                                                                               |                                                                                                                              |

After Instruction

**REG** = 1110 0110

= 0111 0011 = 0 **TSTFSZ** Test f, skip if 0

Syntax: [ label ] TSTFSZ f [,a]

Operands:  $0 \le f \le 255$

$a \in [0,1]$

Operation: skip if f = 0

Status Affected: None

Encoding: 0110 ffff ffff

Description: If f' = 0, the next instruction,

> fetched during the current instruction execution, is discarded and a NOP is executed, making this a twocycle instruction. If 'a' is 0, the Access Bank will be selected, overriding the BSR value. If 'a' is 1, then the bank will be selected as per the BSR value (default).

011a

Words: 1 1(2) Cycles:

Note: 3 cycles if skip and followed

by a 2-word instruction.

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4        |

|--------|--------------|---------|-----------|

| Decode | Read         | Process | No        |

|        | register 'f' | Data    | operation |

If skip:

| Q1        | Q2        | Q3        | Q4        |

|-----------|-----------|-----------|-----------|

| No        | No        | No        | No        |

| operation | operation | operation | operation |

If skip and followed by 2-word instruction:

| Q1        | Q2        | Q3        | Q4        |

|-----------|-----------|-----------|-----------|

| No        | No        | No        | No        |

| operation | operation | operation | operation |

| No        | No        | No        | No        |

| operation | operation | operation | operation |

Example: HERE TSTFSZ CNT, 1

> NZERO ZERO

Before Instruction

PC = Address (HERE)

After Instruction

If CNT 0x00,

Address (ZERO)

If CNT 0x00,

Address (NZERO)

**XORLW Exclusive OR literal with W**

Syntax: [label] XORLW k

Operands:  $0 \le k \le 255$

(W) .XOR.  $k \rightarrow W$ Operation:

Status Affected: N, Z

Encoding: 0000 1010 kkkk kkkk

The contents of W are XORed Description:

with the 8-bit literal 'k'. The result

is placed in W.

Words: 1 Cycles: 1

Q Cycle Activity:

| Q1     | Q2          | Q3      | Q4         |

|--------|-------------|---------|------------|

| Decode | Read        | Process | Write to W |

|        | literal 'k' | Data    |            |

Example: XORLW 0xAF

Before Instruction

W 0xB5

After Instruction

W 0x1A

### 21.8 MPLAB ICD In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD, is a powerful, low cost, run-time development tool. This tool is based on the FLASH PICmicro MCUs and can be used to develop for this and other PICmicro microcontrollers. The MPLAB ICD utilizes the in-circuit debugging capability built into the FLASH devices. This feature, along with Microchip's In-Circuit Serial Programming™ protocol, offers cost-effective in-circuit FLASH debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by watching variables, single-stepping and setting break points. Running at full speed enables testing hardware in real-time.

# 21.9 PRO MATE II Universal Device Programmer

The PRO MATE II universal device programmer is a full-featured programmer, capable of operating in stand-alone mode, as well as PC-hosted mode. The PRO MATE II device programmer is CE compliant.

The PRO MATE II device programmer has programmable VDD and VPP supplies, which allow it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for instructions and error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In stand-alone mode, the PRO MATE II device programmer can read, verify, or program PICmicro devices. It can also set code protection in this mode.

# 21.10 PICSTART Plus Entry Level Development Programmer

The PICSTART Plus development programmer is an easy-to-use, low cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient.

The PICSTART Plus development programmer supports all PICmicro devices with up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant.

# 21.11 PICDEM 1 Low Cost PICmicro Demonstration Board

The PICDEM 1 demonstration board is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42. PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The user can program the sample microcontrollers provided with the PICDEM 1 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The user can also connect the PICDEM 1 demonstration board to the MPLAB ICE incircuit emulator and download the firmware to the emulator for testing. A prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push button switches and eight LEDs connected to PORTB.

# 21.12 PICDEM 2 Low Cost PIC16CXX Demonstration Board

The PICDEM 2 demonstration board is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 2 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a serial EEPROM to demonstrate usage of the I<sup>2</sup>C<sup>™</sup> bus and separate headers for connection to an LCD module and a keypad.

**DEVELOPMENT TOOLS FROM MICROCHIP TABLE 21-1:**

| MPLAB® OTTO Compiler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                             | PIC12CXXX   | PIC14000 | PIC16C5X | PIC16C6X | PIC16CXXX   | PIC16F62X   | PIC16C7X    | PIC16C7XX   | PIC16F8X | PIC16F8XX | PIC16C9XX   | PIC17C4X | XXTOTIO     | PIC18CXX2 | PIC18FXXX | 93CXX<br>Secxx\ | нсеххх | WCEEXXX | WCP2510     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------|----------|----------|----------|-------------|-------------|-------------|-------------|----------|-----------|-------------|----------|-------------|-----------|-----------|-----------------|--------|---------|-------------|

| MPLABY CTR Compiler MPLABY CTR Compiler MPLABY CTR Compiler MPLABY CECOmpiler MPLABY CECOmpiler MPLABY CECOmpiler MPLABY CECOmpiler MPLABY CECOmpiler MPLABY CENTER Thinker MPLA |                                                             | >           | >        | >        | >        | >           | >           | >           | >           | >        | >         | >           | >        | >           | >         | >         |                 |        |         |             |

| MPLAB** C to Complier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                             |             |          |          |          |             |             |             |             |          |           |             | >        | >           |           |           |                 |        |         |             |

| MPALANE' Delection that seamender                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                             |             |          |          |          |             |             |             |             |          |           |             |          |             | `         | ^         |                 |        |         |             |

| NPLAB®*ICE In-Circuit Emulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                             | >           | >        | >        | >        | <b>&gt;</b> | <i>&gt;</i> | <b>&gt;</b> | ^           | >        | >         | ^           | >        | <b>&gt;</b> | >         | ^         | ^               | >      |         |             |

| ICEPIC# In-Circuit Emulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                             | >           | `        | >        | >        | ^           | **^         | `           | <b>&gt;</b> | ^        | ^         | `           | `        | >           | >         | ^         |                 |        |         |             |

| Natural Age   CD In-Circuit   Plotogram   Natural Age   CD In-Circuit   Plotogram   Natural Age   CD In-Circuit   Natural Development Programmer   Natural Age   Natural Development Programmer   Natural Development   Natural Devel   |                                                             | >           |          | >        | >        | >           |             | >           | >           | >        |           | >           |          |             |           |           |                 |        |         |             |

| PICSTART® Plus Entry Level         Comment of the                                 | MPLAB® ICD In-Circuit<br>Debugger                           |             |          |          | *        |             |             | *           |             |          | >         |             |          |             |           | >         |                 |        |         |             |

| PRO MATE® III         Universal Device Programmer         Image: Log Foundation of the Programmer                                          |                                                             | >           | >        | >        | >        | >           | **^         | >           | >           | >        | >         | >           | >        | >           | >         | >         |                 |        |         |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                             | <b>&gt;</b> | >        | >        | >        | >           | **>         | >           | >           | >        | >         | <b>&gt;</b> | >        | >           | >         | >         | >               | >      |         |             |

| PICDEM™ 2 Demonstration         √1         √1         √2         √3         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4         √4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PICDEM™ 1 Demonstration<br>Board                            |             |          | >        |          | >           |             | ₹,          |             | >        |           |             | >        |             |           |           |                 |        |         |             |

| PICDEM™ 3 Demonstration         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PICDEM™ 2 Demonstration<br>Board                            |             |          |          | 7        |             |             | +           |             |          |           |             |          |             | >         | >         |                 |        |         |             |

| PICDEM™ 14A Demonstration         V         Picchem™ 14A Demonstration           Board         PICDEM™ 17 Demonstration         V         N           PICDEM™ 17 Demonstration         V         N         N           KEELOo® Evaluation Kit         N         N         N           KEELOo® Transponder Kit         N         N         N           microID™ Programmer's Kit         N         N         N           125 kHz Anticollision microID™ Developer's Kit         N         N         N           Developer's Kit         N         N         N           microID™ Developer's Kit         N         N         N           MCP2510 CAN Developer's Kit         N         N         N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                             |             |          |          |          |             |             |             |             |          |           | >           |          |             |           |           |                 |        |         |             |

| PICDEM™ 17 Demonstration         Composition MicrolD™         Compo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                             |             | >        |          |          |             |             |             |             |          |           |             |          |             |           |           |                 |        |         |             |

| KEELOQ® Evaluation Kit         KEELOQ® Transponder Kit         V         V           microID™ Programmer's Kit         125 kHz microID™         N         V           125 kHz microID™         Developer's Kit         N         V           125 kHz Anticollision microID™         Developer's Kit         N         V           13.56 kHz Anticollision microID™ Developer's Kit         N         V           13.56 kHz Anticollision microID™ Developer's Kit         N         V           MCP2510 CAN Developer's Kit         N         V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                             |             |          |          |          |             |             |             |             |          |           |             |          | >           |           |           |                 |        |         |             |

| KEELOG® Transponder Kit         KEELOG® Transponder Kit         C           microID™ Programmer's Kit         7           125 kHz microID™ Developer's Kit         7           125 kHz microID™ Developer's Kit         7           125 kHz microID™ Developer's Kit         7           13.56 MHz Anticollision microID™ Developer's Kit         7           MCP2510 CAN Developer's Kit         7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                             |             |          |          |          |             |             |             |             |          |           |             |          |             |           |           |                 | >      |         |             |

| microID™ Programmer's Kit         /           125 kHz microID™         /           125 kHz microID™         /           125 kHz Anticollision microID™         /           Developer's Kit         /           13.56 MHz Anticollision microID™ Developer's Kit         /           microID™ Developer's Kit         /           MCP2510 CAN Developer's Kit         /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                             |             |          |          |          |             |             |             |             |          |           |             |          |             |           |           |                 | >      |         |             |

| 125 kHz microID™         /           Developer's Kit         /           125 kHz Anticollision microID™         /           Developer's Kit         /           13.56 MHz Anticollision microID™ Developer's Kit         /           MCP2510 CAN Developer's Kit         /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                             |             |          |          |          |             |             |             |             |          |           |             |          |             |           |           |                 |        | >       |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                             |             |          |          |          |             |             |             |             |          |           |             |          |             |           |           |                 |        | >       |             |

| ` \                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 125 kHz Anticollision microlD <sup>TM</sup> Developer's Kit |             |          |          |          |             |             |             |             |          |           |             |          |             |           |           |                 |        | >       |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13.56 MHz Anticollision<br>microlD™ Developer's Kit         |             |          |          |          |             |             |             |             |          |           |             |          |             |           |           |                 |        | >       |             |