Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                               |

| Number of I/O              | 34                                                                       |

| Program Memory Size        | 32KB (16K x 16)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 1.5K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-LCC (J-Lead)                                                          |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf452-i-l |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

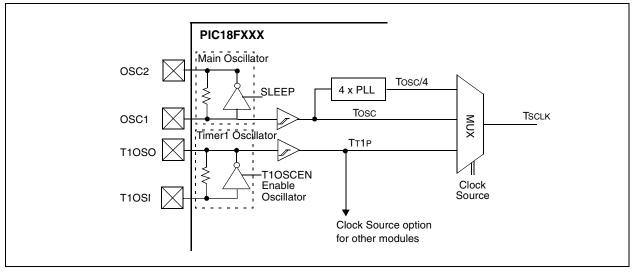

# 2.6 Oscillator Switching Feature

The PIC18FXX2 devices include a feature that allows the system clock source to be switched from the main oscillator to an alternate low frequency clock source. For the PIC18FXX2 devices, this alternate clock source is the Timer1 oscillator. If a low frequency crystal (32 kHz, for example) has been attached to the Timer1 oscillator pins and the Timer1 oscillator has been enabled, the device can switch to a Low Power Execution mode. Figure 2-7 shows a block diagram of the system clock sources. The clock switching feature is enabled <u>by programming the Oscillator Switching</u> Enable (OSCSEN) bit in Configuration Register1H to a '0'. Clock switching is disabled in an erased device. See Section 11.0 for further details of the Timer1 oscillator. See Section 19.0 for Configuration Register details.

### FIGURE 2-7: DEVICE CLOCK SOURCES

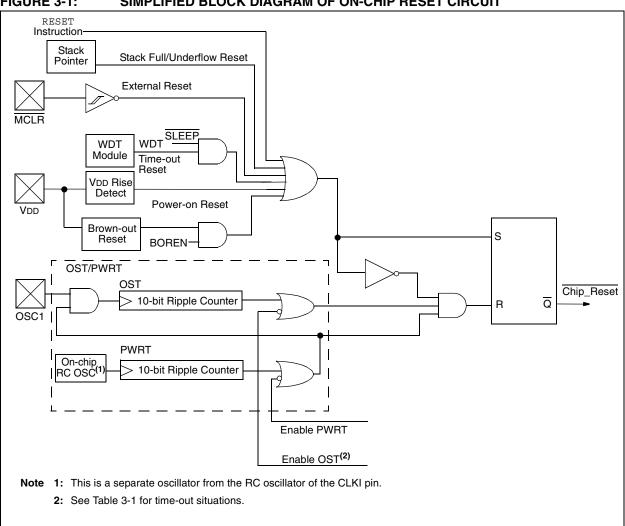

#### 3.0 RESET

The PIC18FXXX differentiates between various kinds of RESET:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- C) MCLR Reset during SLEEP

- Watchdog Timer (WDT) Reset (during normal d) operation)

- e) Programmable Brown-out Reset (BOR)

- f) **RESET** Instruction

- g) Stack Full Reset

- Stack Underflow Reset h)

Most registers are unaffected by a RESET. Their status is unknown on POR and unchanged by all other RESETS. The other registers are forced to a "RESET state" on Power-on Reset, MCLR, WDT Reset, Brownout Reset, MCLR Reset during SLEEP and by the RESET instruction.

Most registers are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. Status bits from the RCON register, RI, TO, PD, POR and BOR, are set or cleared differently in different RESET situations, as indicated in Table 3-2. These bits are used in software to determine the nature of the RESET. See Table 3-3 for a full description of the RESET states of all registers.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 3-1.

The Enhanced MCU devices have a MCLR noise filter in the MCLR Reset path. The filter will detect and ignore small pulses.

The MCLR pin is not driven low by any internal RESETS, including the WDT.

#### FIGURE 3-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

| TABLE 3-3:          |     | IIIALI  |        |     |                                    | L REGISTERS (CONTI                                            | NUED)                           |

|---------------------|-----|---------|--------|-----|------------------------------------|---------------------------------------------------------------|---------------------------------|

| Register            | Арр | olicabl | e Devi | ces | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset<br>RESET Instruction<br>Stack Resets | Wake-up via WDT<br>or Interrupt |

| FSR1H               | 242 | 442     | 252    | 452 | xxxx                               | uuuu                                                          | uuuu                            |

| FSR1L               | 242 | 442     | 252    | 452 | xxxx xxxx                          | uuuu uuuu                                                     | uuuu uuuu                       |

| BSR                 | 242 | 442     | 252    | 452 | 0000                               | 0000                                                          | uuuu                            |

| INDF2               | 242 | 442     | 252    | 452 | N/A                                | N/A                                                           | N/A                             |

| POSTINC2            | 242 | 442     | 252    | 452 | N/A                                | N/A                                                           | N/A                             |

| POSTDEC2            | 242 | 442     | 252    | 452 | N/A                                | N/A                                                           | N/A                             |

| PREINC2             | 242 | 442     | 252    | 452 | N/A                                | N/A                                                           | N/A                             |

| PLUSW2              | 242 | 442     | 252    | 452 | N/A                                | N/A                                                           | N/A                             |

| FSR2H               | 242 | 442     | 252    | 452 | xxxx                               | uuuu                                                          | uuuu                            |

| FSR2L               | 242 | 442     | 252    | 452 | xxxx xxxx                          | uuuu uuuu                                                     | uuuu uuuu                       |

| STATUS              | 242 | 442     | 252    | 452 | x xxxx                             | u uuuu                                                        | u uuuu                          |

| TMR0H               | 242 | 442     | 252    | 452 | 0000 0000                          | uuuu uuuu                                                     | uuuu uuuu                       |

| TMR0L               | 242 | 442     | 252    | 452 | xxxx xxxx                          | uuuu uuuu                                                     | uuuu uuuu                       |

| T0CON               | 242 | 442     | 252    | 452 | 1111 1111                          | 1111 1111                                                     | uuuu uuuu                       |

| OSCCON              | 242 | 442     | 252    | 452 | 0                                  | 0                                                             | u                               |

| LVDCON              | 242 | 442     | 252    | 452 | 00 0101                            | 00 0101                                                       | uu uuuu                         |

| WDTCON              | 242 | 442     | 252    | 452 | 0                                  | 0                                                             | u                               |

| RCON <sup>(4)</sup> | 242 | 442     | 252    | 452 | 0q 11qq                            | 0q qquu                                                       | uu qquu                         |

| TMR1H               | 242 | 442     | 252    | 452 | xxxx xxxx                          | uuuu uuuu                                                     | uuuu uuuu                       |

| TMR1L               | 242 | 442     | 252    | 452 | xxxx xxxx                          | uuuu uuuu                                                     | uuuu uuuu                       |

| T1CON               | 242 | 442     | 252    | 452 | 0-00 0000                          | u-uu uuuu                                                     | u-uu uuuu                       |

| TMR2                | 242 | 442     | 252    | 452 | 0000 0000                          | 0000 0000                                                     | uuuu uuuu                       |

| PR2                 | 242 | 442     | 252    | 452 | 1111 1111                          | 1111 1111                                                     | 1111 1111                       |

| T2CON               | 242 | 442     | 252    | 452 | -000 0000                          | -000 0000                                                     | -uuu uuuu                       |

| SSPBUF              | 242 | 442     | 252    | 452 | xxxx xxxx                          | uuuu uuuu                                                     | uuuu uuuu                       |

| SSPADD              | 242 | 442     | 252    | 452 | 0000 0000                          | 0000 0000                                                     | uuuu uuuu                       |

| SSPSTAT             | 242 | 442     | 252    | 452 | 0000 0000                          | 0000 0000                                                     | uuuu uuuu                       |

| SSPCON1             | 242 | 442     | 252    | 452 | 0000 0000                          | 0000 0000                                                     | uuuu uuuu                       |

| SSPCON2             | 242 | 442     | 252    | 452 | 0000 0000                          | 0000 0000                                                     | uuuu uuuu                       |

TABLE 3-3:

INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

- Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- 2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- **3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 4: See Table 3-2 for RESET value for specific condition.

- 5: Bit 6 of PORTA, LATA, and TRISA are enabled in ECIO and RCIO Oscillator modes only. In all other Oscillator modes, they are disabled and read '0'.

- 6: Bit 6 of PORTA, LATA and TRISA are not available on all devices. When unimplemented, they are read '0'.

### 5.2.2 TABLAT - TABLE LATCH REGISTER

The Table Latch (TABLAT) is an 8-bit register mapped into the SFR space. The Table Latch is used to hold 8-bit data during data transfers between program memory and data RAM.

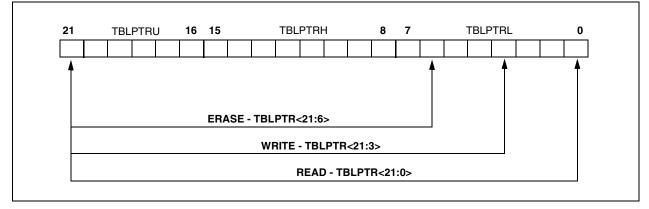

#### 5.2.3 TBLPTR - TABLE POINTER REGISTER

The Table Pointer (TBLPTR) addresses a byte within the program memory. The TBLPTR is comprised of three SFR registers: Table Pointer Upper Byte, Table Pointer High Byte and Table Pointer Low Byte (TBLPTRU:TBLPTRH:TBLPTRL). These three registers join to form a 22-bit wide pointer. The low order 21 bits allow the device to address up to 2 Mbytes of program memory space. The 22nd bit allows access to the Device ID, the User ID and the Configuration bits.

The table pointer, TBLPTR, is used by the TBLRD and TBLWT instructions. These instructions can update the TBLPTR in one of four ways based on the table operation. These operations are shown in Table 5-1. These operations on the TBLPTR only affect the low order 21 bits.

#### 5.2.4 TABLE POINTER BOUNDARIES

TBLPTR is used in reads, writes, and erases of the FLASH program memory.

When a TBLRD is executed, all 22 bits of the Table Pointer determine which byte is read from program memory into TABLAT.

When a TBLWT is executed, the three LSbs of the Table Pointer (TBLPTR<2:0>) determine which of the eight program memory holding registers is written to. When the timed write to program memory (long write) begins, the 19 MSbs of the Table Pointer, TBLPTR (TBLPTR<21:3>), will determine which program memory block of 8 bytes is written to. For more detail, see Section 5.5 ("Writing to FLASH Program Memory").

When an erase of program memory is executed, the 16 MSbs of the Table Pointer (TBLPTR<21:6>) point to the 64-byte block that will be erased. The Least Significant bits (TBLPTR<5:0>) are ignored.

Figure 5-3 describes the relevant boundaries of TBLPTR based on FLASH program memory operations.

### TABLE 5-1: TABLE POINTER OPERATIONS WITH TBLRD AND TBLWT INSTRUCTIONS

| Example            | Operation on Table Pointer                  |

|--------------------|---------------------------------------------|

| TBLRD*<br>TBLWT*   | TBLPTR is not modified                      |

| TBLRD*+<br>TBLWT*+ | TBLPTR is incremented after the read/write  |

| TBLRD*-<br>TBLWT*- | TBLPTR is decremented after the read/write  |

| TBLRD+*<br>TBLWT+* | TBLPTR is incremented before the read/write |

#### FIGURE 5-3: TABLE POINTER BOUNDARIES BASED ON OPERATION

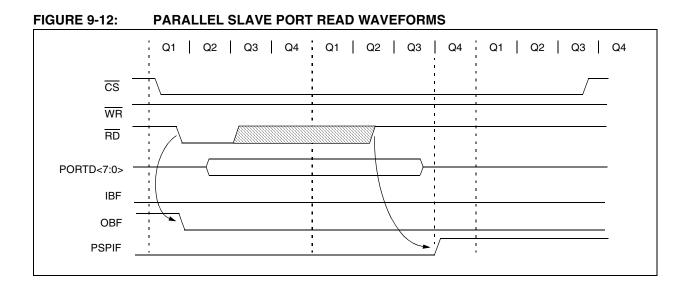

TABLE 9-11: REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Name   | Bit 7        | Bit 6         | Bit 5         | Bit 4          | Bit 3 | Bit 2     | Bit 1         | Bit 0  | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |

|--------|--------------|---------------|---------------|----------------|-------|-----------|---------------|--------|----------------------|---------------------------------|

| PORTD  | Port Data    | Latch whe     | en written; F | Port pins wher | read  |           |               |        | xxxx xxxx            | uuuu uuuu                       |

| LATD   | LATD Data    | a Output b    | its           |                |       |           |               |        | xxxx xxxx            | uuuu uuuu                       |

| TRISD  | PORTD D      | ata Directi   | on bits       |                |       |           |               |        | 1111 1111            | 1111 1111                       |

| PORTE  | _            | _             | _             | —              | _     | RE2       | RE1           | RE0    | 000                  | 000                             |

| LATE   | _            | _             | _             | _              | _     | LATE Data | a Output bits | 5      | xxx                  | uuu                             |

| TRISE  | IBF          | OBF           | IBOV          | PSPMODE        | —     | PORTE D   | ata Direction | n bits | 0000 -111            | 0000 -111                       |

| INTCON | GIE/<br>GIEH | PEIE/<br>GIEL | TMR0IF        | INTOIE         | RBIE  | TMR0IF    | INTOIF        | RBIF   | 0000 000x            | 0000 000u                       |

| PIR1   | PSPIF        | ADIF          | RCIF          | TXIF           | SSPIF | CCP1IF    | TMR2IF        | TMR1IF | 0000 0000            | 0000 0000                       |

| PIE1   | PSPIE        | ADIE          | RCIE          | TXIE           | SSPIE | CCP1IE    | TMR2IE        | TMR1IE | 0000 0000            | 0000 0000                       |

| IPR1   | PSPIP        | ADIP          | RCIP          | TXIP           | SSPIP | CCP1IP    | TMR2IP        | TMR1IP | 0000 0000            | 0000 0000                       |

| ADCON1 | ADFM         | ADCS2         | _             | _              | PCFG3 | PCFG2     | PCFG1         | PCFG0  | 00 0000              | 00 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Parallel Slave Port.

# 10.1 Timer0 Operation

Timer0 can operate as a timer or as a counter.

Timer mode is selected by clearing the T0CS bit. In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0L register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0L register.

Counter mode is selected by setting the T0CS bit. In Counter mode, Timer0 will increment, either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit (T0SE). Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed below.

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization.

# 10.2 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module. The prescaler is not readable or writable.

The PSA and T0PS2:T0PS0 bits determine the prescaler assignment and prescale ratio.

Clearing bit PSA will assign the prescaler to the Timer0 module. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4,..., 1:256 are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0L register (e.g., CLRF TMR0, MOVWF TMR0, BSF TMR0, x....etc.) will clear the prescaler count.

| Note: | Writing to TMR0L when the prescaler is      |

|-------|---------------------------------------------|

|       | assigned to Timer0 will clear the prescaler |

|       | count, but will not change the prescaler    |

|       | assignment.                                 |

#### 10.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control, (i.e., it can be changed "on-the-fly" during program execution).

# 10.3 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h in 8-bit mode, or FFFFh to 0000h in 16-bit mode. This overflow sets the TMR0IF bit. The interrupt can be masked by clearing the TMR0IE bit. The TMR0IE bit must be cleared in software by the Timer0 module Interrupt Service Routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP, since the timer is shut-off during SLEEP.

# 10.4 16-Bit Mode Timer Reads and Writes

TMR0H is not the high byte of the timer/counter in 16-bit mode, but is actually a buffered version of the high byte of Timer0 (refer to Figure 10-2). The high byte of the Timer0 counter/timer is not directly readable nor writable. TMR0H is updated with the contents of the high byte of Timer0 during a read of TMR0L. This provides the ability to read all 16-bits of Timer0 without having to verify that the read of the high and low byte were valid due to a rollover between successive reads of the high and low byte.

A write to the high byte of Timer0 must also take place through the TMR0H buffer register. Timer0 high byte is updated with the contents of TMR0H when a write occurs to TMR0L. This allows all 16-bits of Timer0 to be updated at once.

| Name   | Bit 7       | Bit 6           | Bit 5       | Bit 4    | Bit 3 | Bit 2  | Bit 1         | Bit 0 | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |

|--------|-------------|-----------------|-------------|----------|-------|--------|---------------|-------|----------------------|---------------------------------|

| TMR0L  | Timer0 Modu | ule Low Byte F  | Register    |          |       |        |               |       | xxxx xxxx            | uuuu uuuu                       |

| TMR0H  | Timer0 Modu | ule High Byte I | Register    |          |       |        |               |       | 0000 0000            | 0000 0000                       |

| INTCON | GIE/GIEH    | PEIE/GIEL       | TMR0IE      | INT0IE   | RBIE  | TMR0IF | <b>INT0IF</b> | RBIF  | 0000 000x            | 0000 000u                       |

| T0CON  | TMR0ON      | T08BIT          | TOCS        | T0SE     | PSA   | T0PS2  | T0PS1         | T0PS0 | 1111 1111            | 1111 1111                       |

| TRISA  | _           | PORTA Data      | Direction F | Register |       |        |               |       | -111 1111            | -111 1111                       |

# TABLE 10-1: REGISTERS ASSOCIATED WITH TIMER0

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

# 13.2 Timer1 Oscillator

The Timer1 oscillator may be used as the clock source for Timer3. The Timer1 oscillator is enabled by setting the T1OSCEN (T1CON<3>) bit. The oscillator is a low power oscillator rated up to 200 KHz. See Section 11.0 for further details.

# 13.3 Timer3 Interrupt

The TMR3 Register pair (TMR3H:TMR3L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR3 Interrupt, if enabled, is generated on overflow, which is latched in interrupt flag bit, TMR3IF (PIR2<1>). This interrupt can be enabled/disabled by setting/clearing TMR3 interrupt enable bit, TMR3IE (PIE2<1>).

# 13.4 Resetting Timer3 Using a CCP Trigger Output

If the CCP module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer3.

| Note: | The special event triggers from the CCP |

|-------|-----------------------------------------|

|       | module will not set interrupt flag bit, |

|       | TMR3IF (PIR1<0>).                       |

Timer3 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer3 is running in Asynchronous Counter mode, this RESET operation may not work. In the event that a write to Timer3 coincides with a special event trigger from CCP1, the write will take precedence. In this mode of operation, the CCPR1H:CCPR1L registers pair effectively becomes the period register for Timer3.

| Name   | Bit 7        | Bit 6                                                                                                   | Bit 5   | Bit 4   | Bit 3   | Bit 2         | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |

|--------|--------------|---------------------------------------------------------------------------------------------------------|---------|---------|---------|---------------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE/<br>GIEH | PEIE/<br>GIEL                                                                                           | TMR0IE  | INTOIE  | RBIE    | TMR0IF        | INTOIF | RBIF   | 0000 000x            | 0000 000u                       |

| PIR2   | —            | _                                                                                                       | _       | EEIF    | BCLIF   | LVDIF         | TMR3IF | CCP2IF | 0 0000               | 0 0000                          |

| PIE2   | —            | _                                                                                                       | _       | EEIE    | BCLIE   | LVDIE         | TMR3IE | CCP2IE | 0 0000               | 0 0000                          |

| IPR2   | _            | -                                                                                                       | -       | EEIP    | BCLIP   | LVDIP         | TMR3IP | CCP2IP | 1 1111               | 1 1111                          |

| TMR3L  | Holding F    | ding Register for the Least Significant Byte of the 16-bit TMR3 Register xxxx xxxx uuuu uuuu            |         |         |         |               |        |        |                      |                                 |

| TMR3H  | Holding F    | ding Register for the Most Significant Byte of the 16-bit TMR3 Register       xxxx xxxx       uuuu uuuu |         |         |         |               |        |        |                      |                                 |

| T1CON  | RD16         |                                                                                                         | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC        | TMR1CS | TMR10N | 0-00 0000            | u-uu uuuu                       |

| T3CON  | RD16         | T3CCP2                                                                                                  | T3CKPS1 | T3CKPS0 | T3CCP1  | <b>T3SYNC</b> | TMR3CS | TMR3ON | 0000 0000            | uuuu uuuu                       |

### TABLE 13-1: REGISTERS ASSOCIATED WITH TIMER3 AS A TIMER/COUNTER

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

#### 15.3.3 ENABLING SPI I/O

To enable the serial port, SSP Enable bit, SSPEN (SSPCON1<5>), must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, re-initialize the SSPCON registers, and then set the SSPEN bit. This configures the SDI, SDO, SCK, and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed. That is:

- SDI is automatically controlled by the SPI module

- SDO must have TRISC<5> bit cleared

- SCK (Master mode) must have TRISC<3> bit cleared

- SCK (Slave mode) must have TRISC<3> bit set

- SS must have TRISC<4> bit set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

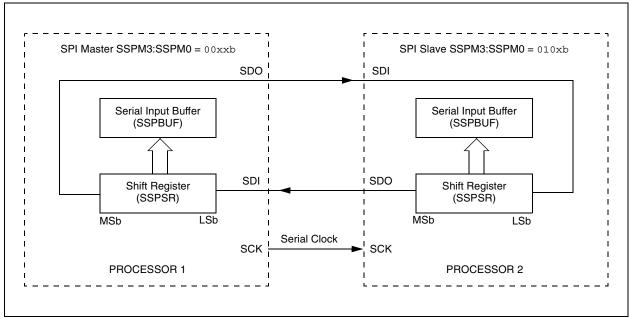

### 15.3.4 TYPICAL CONNECTION

Figure 15-2 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge, and latched on the opposite edge of the clock. Both processors should be programmed to the same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- Master sends data Slave sends dummy data

- Master sends data Slave sends data

- Master sends dummy data Slave sends data

#### FIGURE 15-2: SPI MASTER/SLAVE CONNECTION

PIC18FXX2

#### 15.4.4 CLOCK STRETCHING

Both 7- and 10-bit Slave modes implement automatic clock stretching during a transmit sequence.

The SEN bit (SSPCON2<0>) allows clock stretching to be enabled during receives. Setting SEN will cause the SCL pin to be held low at the end of each data receive sequence.

#### 15.4.4.1 Clock Stretching for 7-bit Slave Receive Mode (SEN = 1)

In 7-bit Slave Receive mode, on the falling edge of the ninth clock at the end of the ACK sequence, if the BF bit is set, the CKP bit in the SSPCON1 register is automatically cleared, forcing the SCL output to be held low. The CKP being cleared to '0' will assert the SCL line low. The CKP bit must be set in the user's ISR before reception is allowed to continue. By holding the SCL line low, the user has time to service the ISR and read the contents of the SSPBUF before the master device can initiate another receive sequence. This will prevent buffer overruns from occurring (see Figure 15-13).

- Note 1: If the user reads the contents of the SSPBUF before the falling edge of the ninth clock, thus clearing the BF bit, the CKP bit will not be cleared and clock stretching will not occur.

- 2: The CKP bit can be set in software, regardless of the state of the BF bit. The user should be careful to clear the BF bit in the ISR before the next receive sequence, in order to prevent an overflow condition.

#### 15.4.4.2 Clock Stretching for 10-bit Slave Receive Mode (SEN = 1)

In 10-bit Slave Receive mode, during the address sequence, clock stretching automatically takes place but CKP is not cleared. During this time, if the UA bit is set after the ninth clock, clock stretching is initiated. The UA bit is set after receiving the upper byte of the 10-bit address, and following the receive of the second byte of the 10-bit address with the R/W bit cleared to '0'. The release of the clock line occurs upon updating SSPADD. Clock stretching will occur on each data receive sequence as described in 7-bit mode.

**Note:** If the user polls the UA bit and clears it by updating the SSPADD register before the falling edge of the ninth clock occurs, and if the user hasn't cleared the BF bit by reading the SSPBUF register before that time, then the CKP bit will still NOT be asserted low. Clock stretching on the basis of the state of the BF bit only occurs during a data sequence, not an address sequence.

#### 15.4.4.3 Clock Stretching for 7-bit Slave Transmit Mode

7-bit Slave Transmit mode implements clock stretching by clearing the CKP bit after the falling edge of the ninth clock, if the BF bit is clear. This occurs, regardless of the state of the SEN bit.

The user's ISR must set the CKP bit before transmission is allowed to continue. By holding the SCL line low, the user has time to service the ISR and load the contents of the SSPBUF before the master device can initiate another transmit sequence (see Figure 15-9).

Note 1: If the user loads the contents of SSPBUF, setting the BF bit before the falling edge of the ninth clock, the CKP bit will not be cleared and clock stretching will not occur.

2: The CKP bit can be set in software, regardless of the state of the BF bit.

#### 15.4.4.4 Clock Stretching for 10-bit Slave Transmit Mode

In 10-bit Slave Transmit mode, clock stretching is controlled during the first two address sequences by the state of the UA bit, just as it is in 10-bit Slave Receive mode. The first two addresses are followed by a third address sequence, which contains the high order bits of the 10-bit address and the R/W bit set to '1'. After the third address sequence is performed, the UA bit is not set, the module is now configured in Transmit mode, and clock stretching is controlled by the BF flag, as in 7-bit Slave Transmit mode (see Figure 15-11).

# 15.4.10 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address, or the other half of a 10-bit address is accomplished by simply writing a value to the SSPBUF register. This action will set the buffer full flag bit, BF, and allow the baud rate generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted (see data hold time specification parameter 106). SCL is held low for one baud rate generator rollover count (TBRG). Data should be valid before SCL is released high (see data setup time specification parameter 107). When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time if an address match occurred or if data was received properly. The status of ACK is written into the ACKDT bit on the falling edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPIF bit is set and the master clock (baud rate generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 15-21).

After the write to the SSPBUF, each bit of address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will de-assert the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT status bit (SSPCON2<6>). Following the falling edge of the ninth clock transmission of the address, the SSPIF is set, the BF flag is cleared and the baud rate generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

### 15.4.10.1 BF Status Flag

In Transmit mode, the BF bit (SSPSTAT<0>) is set when the CPU writes to SSPBUF and is cleared when all 8 bits are shifted out.

### 15.4.10.2 WCOL Status Flag

If the user writes the SSPBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

WCOL must be cleared in software.

# 15.4.10.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit (SSPCON2<6>) is cleared when the slave has sent an Acknowledge (ACK = 0), and is set when the slave does not Acknowledge (ACK = 1). A slave sends an Acknowledge when it has recognized its address (including a general call) or when the slave has properly received its data.

# 15.4.11 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the receive enable bit, RCEN (SSPCON2<3>).

Note: In the MSSP module, the RCEN bit must be set after the ACK sequence or the RCEN bit will be disregarded.

The baud rate generator begins counting, and on each rollover, the state of the SCL pin changes (high to low/ low to high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag bit is set, the SSPIF flag bit is set and the baud rate generator is suspended from counting, holding SCL low. The MSSP is now in IDLE state, awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception, by setting the Acknowledge sequence enable bit, ACKEN (SSPCON2<4>).

### 15.4.11.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when the SSPBUF register is read.

### 15.4.11.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when 8 bits are received into the SSPSR and the BF flag bit is already set from a previous reception.

### 15.4.11.3 WCOL Status Flag

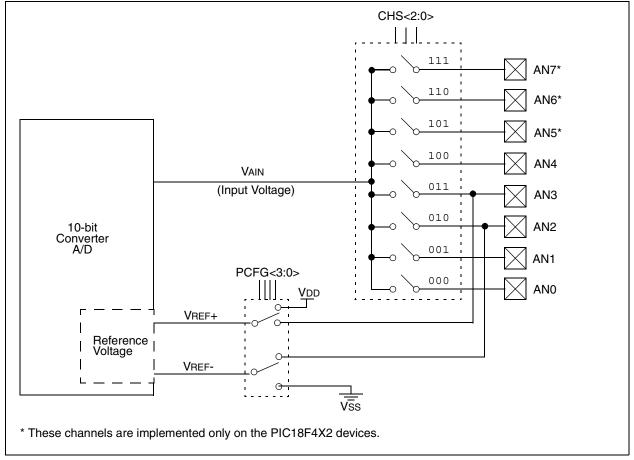

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur). The analog reference voltage is software selectable to either the device's positive and negative supply voltage (VDD and Vss), or the voltage level on the RA3/AN3/ VREF+ pin and RA2/AN2/VREF- pin.

The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode. To operate in SLEEP, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

The output of the sample and hold is the input into the converter, which generates the result via successive approximation.

A device RESET forces all registers to their RESET state. This forces the A/D module to be turned off and any conversion is aborted.

Each port pin associated with the A/D converter can be configured as an analog input (RA3 can also be a voltage reference) or as a digital I/O.

The ADRESH and ADRESL registers contain the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the ADRESH/ ADRESL registers, the GO/DONE bit (ADCON0<2>) is cleared, and A/D interrupt flag bit, ADIF is set. The block diagram of the A/D module is shown in Figure 17-1.

### FIGURE 17-1: A/D BLOCK DIAGRAM

| Byte-oriented file register operations     Example Instruction       15     10     9     8     7     0       OPCODE     d     a     f (FILE #)     ADDWF MYREG, W, B                                                                                                                                                  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| OPCODE d a f (FILE #) ADDWF MYREG, W, B                                                                                                                                                                                                                                                                               |  |

| d = 0 for result destination to be WREG register<br>d = 1 for result destination to be file register (f)<br>a = 0 to force Access Bank<br>a = 1 for BSR to select bank<br>f = 8-bit file register address                                                                                                             |  |

| Byte to Byte move operations (2-word)                                                                                                                                                                                                                                                                                 |  |

| 15       12       11       0         OPCODE       f (Source FILE #)       MOVFF MYREG1, MYREG2         15       12       11       0         1111       f (Destination FILE #)       f = 12-bit file register address                                                                                                  |  |

| Bit-oriented file register operations                                                                                                                                                                                                                                                                                 |  |

| 15       12 11       9 8 7       0         OPCODE       b (BIT #)       a       f (FILE #)       BSF MYREG, bit, B         b = 3-bit position of bit in file register (f)       a = 0 to force Access Bank       a = 1 for BSR to select bank         f = 8-bit file register address       f       BSF MYREG, bit, B |  |

| Literal operations                                                                                                                                                                                                                                                                                                    |  |

| 15         8         7         0           OPCODE         k (literal)         MOVLW 0x7F           k = 8-bit immediate value         K                                                                                                                                                                                |  |

| Control operations                                                                                                                                                                                                                                                                                                    |  |

| CALL, GOTO and Branch operations                                                                                                                                                                                                                                                                                      |  |

| 15     8     7     0       OPCODE     n<7:0> (literal)     GOTO Label       15     12     11     0       1111     n<19:8> (literal)     1111                                                                                                                                                                          |  |

| n = 20-bit immediate value                                                                                                                                                                                                                                                                                            |  |

| 15     8     7     0       OPCODE     S     n<7:0> (literal)     CALL MYFUNC       15     12     11     0       n<19:8> (literal)     S     = Fast bit                                                                                                                                                                |  |

| 15     11     10     0       OPCODE     n<10:0> (literal)     BRA MYFUNC                                                                                                                                                                                                                                              |  |

| 15         8         7         0           OPCODE         n<7:0> (literal)         BC MYFUNC                                                                                                                                                                                                                          |  |

# PIC18FXX2

| BTF   | sc                                                 | Bit Test Fi                                                                                                                                     | le, Skip if Cle                                                                                                                                                                                          | ear                                                                                               | BT         | FSS                                                | Bit Test F                                                                                                           | ile, Skip if Se                                                                                                                                                                                                 | ŧ                                                |

|-------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| Synt  | ax:                                                | [label] B                                                                                                                                       | FSC f,b[,a]                                                                                                                                                                                              |                                                                                                   | Syr        | itax:                                              | [label] B                                                                                                            | TFSS f,b[,a]                                                                                                                                                                                                    |                                                  |

| Ope   | rands:                                             | $\begin{array}{l} 0 \leq f \leq 255 \\ 0 \leq b \leq 7 \\ a \in [0,1] \end{array}$                                                              |                                                                                                                                                                                                          |                                                                                                   | Оре        | erands:                                            | 0 ≤ f ≤ 255<br>0 ≤ b ≤ 7<br>a ∈ [0,1]                                                                                |                                                                                                                                                                                                                 |                                                  |

| Ope   | ration:                                            | skip if (f <b< td=""><td>&gt;) = 0</td><td></td><td>Ope</td><td>eration:</td><td>skip if (f<b< td=""><td>&gt;) = 1</td><td></td></b<></td></b<> | >) = 0                                                                                                                                                                                                   |                                                                                                   | Ope        | eration:                                           | skip if (f <b< td=""><td>&gt;) = 1</td><td></td></b<>                                                                | >) = 1                                                                                                                                                                                                          |                                                  |

| Statu | us Affected:                                       | None                                                                                                                                            |                                                                                                                                                                                                          |                                                                                                   | Sta        | tus Affected:                                      | None                                                                                                                 |                                                                                                                                                                                                                 |                                                  |

| Enco  | oding:                                             | 1011                                                                                                                                            | bbba ff                                                                                                                                                                                                  | ff ffff                                                                                           | Enc        | oding:                                             | 1010                                                                                                                 | bbba ff                                                                                                                                                                                                         | ff                                               |

| Desc  | cription:                                          | next instruct<br>If bit 'b' is C<br>fetched du<br>execution i<br>cycle instruct<br>Access Ba<br>riding the E                                    | egister 'f' is 0<br>ction is skippe<br>), then the nex<br>ring the current<br>s discarded, a<br>nstead, makin<br>uction. If 'a' is<br>nk will be sele<br>3SR value. If<br>'ill be selected<br>(default). | ed.<br>At instruction<br>and a NOP is<br>ag this a two-<br>0, the<br>ected, over-<br>a' = 1, then | De         | scription:                                         | next instru<br>If bit 'b' is f<br>fetched du<br>tion execu<br>NOP is exe<br>a two-cycle<br>Access Ba<br>riding the I | register 'f' is 1<br>ction is skippe<br>I, then the ner<br>ring the curre<br>tion, is discare<br>cuted instead<br>e instruction. I<br>nk will be sele<br>3SR value. If<br><i>i</i> II be selected<br>(default). | ed.<br>xt i<br>ded<br>, m<br>If 'a<br>ect<br>'a' |

| Wor   | ds:                                                | 1                                                                                                                                               |                                                                                                                                                                                                          |                                                                                                   | Wo         | rds:                                               | 1                                                                                                                    |                                                                                                                                                                                                                 |                                                  |

| Cycl  | es:                                                |                                                                                                                                                 | ycles if skip a<br>a 2-word inst                                                                                                                                                                         |                                                                                                   | Сус        | cles:                                              |                                                                                                                      | cycles if skip a<br>a 2-word ins                                                                                                                                                                                |                                                  |

| QC    | ycle Activity:                                     |                                                                                                                                                 |                                                                                                                                                                                                          |                                                                                                   | Q          | Cycle Activity:                                    |                                                                                                                      |                                                                                                                                                                                                                 |                                                  |

|       | Q1                                                 | Q2                                                                                                                                              | Q3                                                                                                                                                                                                       | Q4                                                                                                |            | Q1                                                 | Q2                                                                                                                   | Q3                                                                                                                                                                                                              | -                                                |

|       | Decode                                             | Read<br>register 'f'                                                                                                                            | Process Data                                                                                                                                                                                             | No<br>operation                                                                                   |            | Decode                                             | Read<br>register 'f'                                                                                                 | Process Data                                                                                                                                                                                                    | (                                                |

| lf sk | kip:                                               |                                                                                                                                                 |                                                                                                                                                                                                          |                                                                                                   | lf s       | skip:                                              |                                                                                                                      |                                                                                                                                                                                                                 |                                                  |

|       | Q1                                                 | Q2                                                                                                                                              | Q3                                                                                                                                                                                                       | Q4                                                                                                |            | Q1                                                 | Q2                                                                                                                   | Q3                                                                                                                                                                                                              |                                                  |

|       | No<br>operation                                    | No<br>operation                                                                                                                                 | No<br>operation                                                                                                                                                                                          | No<br>operation                                                                                   |            | No<br>operation                                    | No<br>operation                                                                                                      | No<br>operation                                                                                                                                                                                                 | (                                                |

| lf sk | ip and follow                                      | -                                                                                                                                               |                                                                                                                                                                                                          |                                                                                                   | lf s       | kip and follow                                     | ed by 2-word                                                                                                         | d instruction:                                                                                                                                                                                                  |                                                  |

|       | Q1                                                 | Q2                                                                                                                                              | Q3                                                                                                                                                                                                       | Q4                                                                                                |            | Q1                                                 | Q2                                                                                                                   | Q3                                                                                                                                                                                                              | -                                                |

|       | No<br>operation                                    | No<br>operation                                                                                                                                 | No<br>operation                                                                                                                                                                                          | No<br>operation                                                                                   |            | No<br>operation                                    | No<br>operation                                                                                                      | No<br>operation                                                                                                                                                                                                 |                                                  |

|       | No<br>operation                                    | No<br>operation                                                                                                                                 | No<br>operation                                                                                                                                                                                          | No<br>operation                                                                                   |            | No                                                 | No                                                                                                                   | No<br>operation                                                                                                                                                                                                 |                                                  |

|       | <u>nple</u> :<br>Before Instru<br>PC               | FALSE :<br>TRUE :<br>ction                                                                                                                      | IFSC FLAG                                                                                                                                                                                                | , 1, 0                                                                                            | <u>Exa</u> | umple:<br>Before Instru<br>PC                      | FALSE :<br>TRUE :                                                                                                    | TFSS FLAG<br>dress (here)                                                                                                                                                                                       | ,                                                |

|       | After Instruct<br>If FLAG<<br>PC<br>If FLAG<<br>PC | 1> = 0;<br>= ado<br>1> = 1;                                                                                                                     | iress (true)                                                                                                                                                                                             |                                                                                                   |            | After Instruct<br>If FLAG<<br>PC<br>If FLAG<<br>PC | ion<br>1> = 0;<br>= ado<br>1> = 1;                                                                                   | dress (FALSE)<br>dress (TRUE)                                                                                                                                                                                   | )                                                |

|      |                    | a ∈ [0,1]                                                                                                                                                   |                                                                                                                                |                                                                                                                      |                                                                               |

|------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| per  | ation:             | skip if (f <t< td=""><td>) = <b>1</b></td><td></td><td></td></t<>                                                                                           | ) = <b>1</b>                                                                                                                   |                                                                                                                      |                                                                               |

| tatu | s Affected:        | None                                                                                                                                                        |                                                                                                                                |                                                                                                                      |                                                                               |

| nco  | ding:              | 1010                                                                                                                                                        | bbba                                                                                                                           | ffff                                                                                                                 | ffff                                                                          |

| esc  | ription:           | If bit 'b' in<br>next instru<br>If bit 'b' is<br>fetched du<br>tion execu<br>NOP is exe<br>a two-cycl<br>Access Ba<br>riding the<br>the bank v<br>BSR value | uction is s<br>1, then th<br>uring the o<br>ttion, is di<br>ecuted ins<br>e instruct<br>ank will be<br>BSR valu<br>will be sel | kipped.<br>e next ins<br>current in<br>scarded a<br>tead, ma<br>ion. If 'a'<br>e selected<br>e. If 'a' =<br>ected as | struction<br>struc-<br>and a<br>king this<br>is 0, the<br>d, over-<br>1, then |

| /orc | ls:                | 1                                                                                                                                                           |                                                                                                                                |                                                                                                                      |                                                                               |

| ycle | es:                |                                                                                                                                                             | cycles if a<br>y a 2-wor                                                                                                       |                                                                                                                      |                                                                               |

| C    | ycle Activity:     |                                                                                                                                                             |                                                                                                                                |                                                                                                                      |                                                                               |

| r    | Q1                 | Q2                                                                                                                                                          | Q3                                                                                                                             |                                                                                                                      | Q4                                                                            |

|      | Decode             | Read<br>register 'f'                                                                                                                                        | Process                                                                                                                        |                                                                                                                      | No<br>eration                                                                 |

| fsk  | ip:                |                                                                                                                                                             |                                                                                                                                |                                                                                                                      |                                                                               |

|      | Q1                 | Q2                                                                                                                                                          | Q3                                                                                                                             |                                                                                                                      | Q4                                                                            |

|      | No<br>operation    | No<br>operation                                                                                                                                             | No<br>operati                                                                                                                  | ion op                                                                                                               | No<br>eration                                                                 |

| f sk | ip and follow      | ed by 2-wor                                                                                                                                                 | d instruct                                                                                                                     | ion:                                                                                                                 |                                                                               |

| _    | Q1                 | Q2                                                                                                                                                          | Q3                                                                                                                             |                                                                                                                      | Q4                                                                            |

|      | No<br>operation    | No<br>operation                                                                                                                                             | No<br>operati                                                                                                                  | on op                                                                                                                | No<br>eration                                                                 |

|      | No<br>operation    | No<br>operation                                                                                                                                             | No<br>operati                                                                                                                  | on op                                                                                                                | No<br>eration                                                                 |

| xan  | <u>nple</u> :      | HERE H<br>FALSE :<br>TRUE :                                                                                                                                 | :                                                                                                                              | FLAG, 1,                                                                                                             | . 0                                                                           |

| I    | Before Instruction |                                                                                                                                                             | dress (HI                                                                                                                      | ERE)                                                                                                                 |                                                                               |

# TABLE 21-1: DEVELOPMENT TOOLS FROM MICROCHIP

| MPLAB® Cite Complete<br>MPLAB® Cite Complete         Not Magated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | N       N       N       N       N       N       N       N       N         N       N       N       N       N       N       N       N       N         N       N       N       N       N       N       N       N       N         N       N       N       N       N       N       N       N       N         N       N       N       N       N       N       N       N       N         N       N       N       N       N       N       N       N       N         N       N       N       N       N       N       N       N       N       N         N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |