Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                               |

| Number of I/O              | 34                                                                       |

| Program Memory Size        | 32KB (16K x 16)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 1.5K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf452-i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, PowerSmart, rfPIC and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Migratable Memory, MXDEV, MXLAB, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Linear Active Thermistor, Mindi, MiWi, MPASM, MPLIB, MPLINK, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, rfPICDEM, Select Mode, Smart Serial, SmartTel, Total Endurance, UNI/O, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2006, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona, Gresham, Oregon and Mountain View, California. The Company's quality system processes and procedures are for its PICmicro® 8-bit MCUs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# 4.9 Data Memory Organization

The data memory is implemented as static RAM. Each register in the data memory has a 12-bit address, allowing up to 4096 bytes of data memory. Figure 4-6 and Figure 4-7 show the data memory organization for the PIC18FXX2 devices.

The data memory map is divided into as many as 16 banks that contain 256 bytes each. The lower 4 bits of the Bank Select Register (BSR<3:0>) select which bank will be accessed. The upper 4 bits for the BSR are not implemented.

The data memory contains Special Function Registers (SFR) and General Purpose Registers (GPR). The SFRs are used for control and status of the controller and peripheral functions, while GPRs are used for data storage and scratch pad operations in the user's application. The SFRs start at the last location of Bank 15 (0xFFF) and extend downwards. Any remaining space beyond the SFRs in the Bank may be implemented as GPRs. GPRs start at the first location of Bank 0 and grow upwards. Any read of an unimplemented location will read as '0's.

The entire data memory may be accessed directly or indirectly. Direct addressing may require the use of the BSR register. Indirect addressing requires the use of a File Select Register (FSRn) and a corresponding Indirect File Operand (INDFn). Each FSR holds a 12-bit address value that can be used to access any location in the Data Memory map without banking.

The instruction set and architecture allow operations across all banks. This may be accomplished by indirect addressing or by the use of the MOVFF instruction. The MOVFF instruction is a two-word/two-cycle instruction that moves a value from one register to another.

To ensure that commonly used registers (SFRs and select GPRs) can be accessed in a single cycle, regardless of the current BSR values, an Access Bank is implemented. A segment of Bank 0 and a segment of Bank 15 comprise the Access RAM. Section 4.10 provides a detailed description of the Access RAM.

#### 4.9.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly or indirectly. Indirect addressing operates using a File Select Register and corresponding Indirect File Operand. The operation of indirect addressing is shown in Section 4.12.

Enhanced MCU devices may have banked memory in the GPR area. GPRs are not initialized by a Power-on Reset and are unchanged on all other RESETS.

Data RAM is available for use as GPR registers by all instructions. The top half of Bank 15 (0xF80 to 0xFFF) contains SFRs. All other banks of data memory contain GPR registers, starting with Bank 0.

#### 4.9.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 4-1 and Table 4-2.

The SFRs can be classified into two sets; those associated with the "core" function and those related to the peripheral functions. Those registers related to the "core" are described in this section, while those related to the operation of the peripheral features are described in the section of that peripheral feature.

The SFRs are typically distributed among the peripherals whose functions they control.

The unused SFR locations will be unimplemented and read as '0's. See Table 4-1 for addresses for the SFRs.

# 5.2 Control Registers

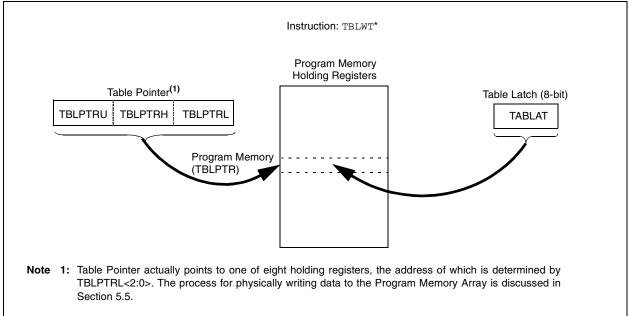

Several control registers are used in conjunction with the TBLRD and TBLWT instructions. These include the:

- EECON1 register

- EECON2 register

- TABLAT register

- TBLPTR registers

## 5.2.1 EECON1 AND EECON2 REGISTERS

EECON1 is the control register for memory accesses.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the memory write and erase sequences.

Control bit EEPGD determines if the access will be a program or data EEPROM memory access. When clear, any subsequent operations will operate on the data EEPROM memory. When set, any subsequent operations will operate on the program memory.

Control bit CFGS determines if the access will be to the configuration registers or to program memory/data EEPROM memory. When set, subsequent operations will operate on configuration registers, regardless of EEPGD (see "Special Features of the CPU", Section 19.0). When clear, memory selection access is determined by EEPGD.

The FREE bit, when set, will allow a program memory erase operation. When the FREE bit is set, the erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a MCLR Reset or a WDT Time-out Reset during normal operation. In these situations, the user can check the WRERR bit and rewrite the location. It is necessary to reload the data and address registers (EEDATA and EEADR), due to RESET values of zero.

Control bit WR initiates write operations. This bit cannot be cleared, only set, in software. It is cleared in hardware at the completion of the write operation. The inability to clear the WR bit in software prevents the accidental or premature termination of a write operation.

Note: Interrupt flag bit EEIF, in the PIR2 register, is set when the write is complete. It must be cleared in software.

# 12.0 TIMER2 MODULE

The Timer2 module timer has the following features:

- 8-bit timer (TMR2 register)

- 8-bit period register (PR2)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMR2 match of PR2

- SSP module optional use of TMR2 output to generate clock shift

Timer2 has a control register shown in Register 12-1. Timer2 can be shut-off by clearing control bit TMR2ON (T2CON<2>) to minimize power consumption. Figure 12-1 is a simplified block diagram of the Timer2 module. Register 12-1 shows the Timer2 control register. The prescaler and postscaler selection of Timer2 are controlled by this register.

# 12.1 Timer2 Operation

Timer2 can be used as the PWM time-base for the PWM mode of the CCP module. The TMR2 register is readable and writable, and is cleared on any device RESET. The input clock (Fosc/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>). The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR2 interrupt (latched in flag bit TMR2IF, (PIR1<1>)).

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR2 register

- a write to the T2CON register

- any device RESET (Power-on Reset, MCLR Reset, Watchdog Timer Reset, or Brown-out Reset)

TMR2 is not cleared when T2CON is written.

# REGISTER 12-1: T2CON: TIMER2 CONTROL REGISTER

| U-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0   | R/W-0   |

|-------|---------|---------|---------|---------|--------|---------|---------|

|       | TOUTPS3 | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 |

| bit 7 |         |         |         |         |        |         | bit 0   |

#### bit 7 Unimplemented: Read as '0'

bit 6-3 **TOUTPS3:TOUTPS0**: Timer2 Output Postscale Select bits

| 0001 | = 1:2 Postscale |

|------|-----------------|

| •    |                 |

- •

- •

bit 2

1111 = 1:16 Postscale

#### TMR2ON: Timer2 On bit

- 1 = Timer2 is on

- 0 = Timer2 is off

- bit 1-0 T2CKPS1:T2CKPS0: Timer2 Clock Prescale Select bits

- 00 = Prescaler is 1

- 01 = Prescaler is 4

- 1x = Prescaler is 16

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

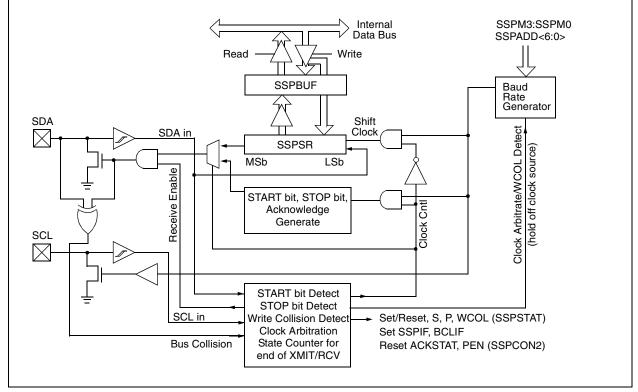

### 15.4.6 MASTER MODE

Master mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON1 and by setting the SSPEN bit. In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

Master mode of operation is supported by interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a RESET or when the MSSP module is disabled. Control of the  $l^2C$  bus may be taken when the P bit is set or the bus is IDLE, with both the S and P bits clear.

In Firmware Controlled Master mode, user code conducts all  $I^2C$  bus operations based on START and STOP bit conditions.

Once Master mode is enabled, the user has six options.

- 1. Assert a START condition on SDA and SCL.

- 2. Assert a Repeated START condition on SDA and SCL.

- 3. Write to the SSPBUF register initiating transmission of data/address.

- 4. Configure the I<sup>2</sup>C port to receive data.

- 5. Generate an Acknowledge condition at the end of a received byte of data.

- 6. Generate a STOP condition on SDA and SCL.

**Note:** The MSSP Module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a START condition and immediately write the SSPBUF register to initiate transmission before the START condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur.

The following events will cause SSP interrupt flag bit, SSPIF, to be set (SSP interrupt if enabled):

- START condition

- STOP condition

- Data transfer byte transmitted/received

- Acknowledge Transmit

- Repeated START

# FIGURE 15-16: MSSP BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE)

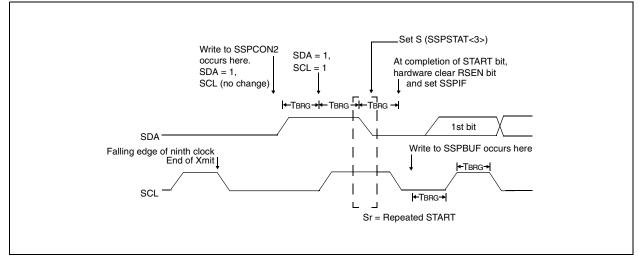

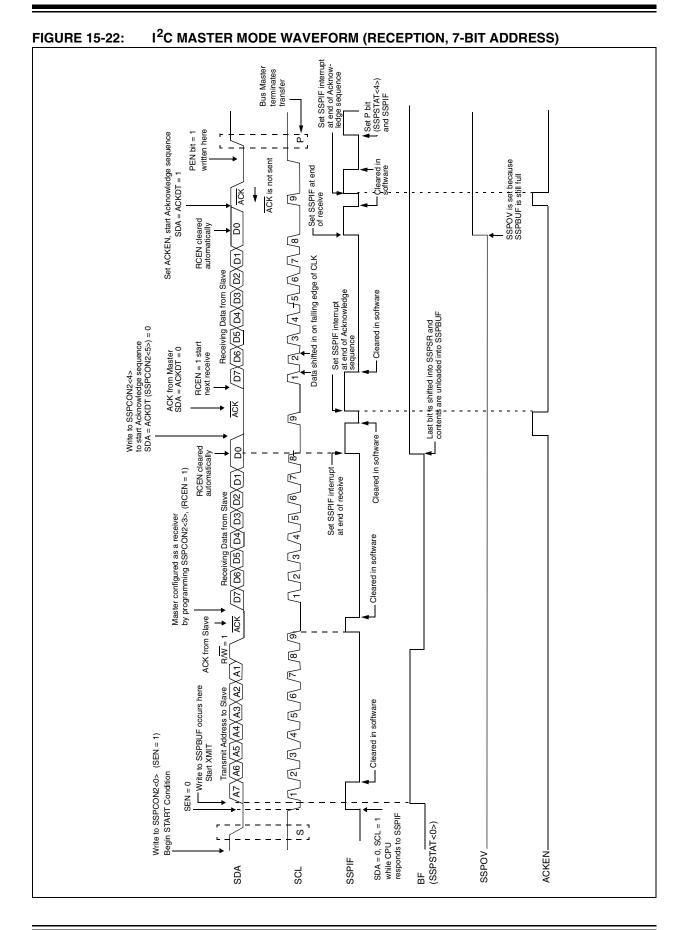

# 15.4.9 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated START condition occurs when the RSEN bit (SSPCON2<1>) is programmed high and the I<sup>2</sup>C logic module is in the IDLE state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the baud rate generator is loaded with the contents of SSPADD<5:0> and begins counting. The SDA pin is released (brought high) for one baud rate generator count (TBRG). When the baud rate generator times out, if SDA is sampled high, the SCL pin will be de-asserted (brought high). When SCL is sampled high, the baud rate generator is reloaded with the contents of SSPADD<6:0> and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. Following this, the RSEN bit (SSPCON2<1>) will be automatically cleared and the baud rate generator will not be reloaded, leaving the SDA pin held low. As soon as a START condition is detected on the SDA and SCL pins, the S bit (SSPSTAT<3>) will be set. The SSPIF bit will not be set until the baud rate generator has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- 2: A bus collision during the Repeated START condition occurs if:

- SDA is sampled low when SCL goes from low to high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data "1".

Immediately following the SSPIF bit getting set, the user may write the SSPBUF with the 7-bit address in 7-bit mode, or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode) or eight bits of data (7-bit mode).

### 15.4.9.1 WCOL Status Flag

If the user writes the SSPBUF when a Repeated START sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing of the lower 5 bits of SSPCON2 is disabled until the Repeated START condition is complete.

# FIGURE 15-20: REPEAT START CONDITION WAVEFORM

|       | R/W-0                                          | R/W-0                                            | R/W-0             | R/W-0      | U-0          | R/W-0      | R-1          | R/W-0  |

|-------|------------------------------------------------|--------------------------------------------------|-------------------|------------|--------------|------------|--------------|--------|

|       | CSRC                                           | TX9                                              | TXEN              | SYNC       |              | BRGH       | TRMT         | TX9D   |

|       | bit 7                                          |                                                  |                   |            |              |            |              | bit 0  |

| bit 7 | <b>CSRC:</b> Clo<br><u>Asynchron</u>           | ck Source Se                                     | elect bit         |            |              |            |              |        |

|       | Don't care                                     | <u>Jus mode.</u>                                 |                   |            |              |            |              |        |

|       |                                                | <u>us mode:</u><br>mode (clock<br>node (clock fi |                   |            | n BRG)       |            |              |        |

| bit 6 | <b>TX9</b> : 9-bit 1<br>1 = Selects            | Fransmit Ena<br>9-bit transm<br>8-bit transm     | ble bit<br>ission | ,          |              |            |              |        |

| bit 5 | <b>TXEN</b> : Tran<br>1 = Transm<br>0 = Transm |                                                  | bit               |            |              |            |              |        |

|       | Note:                                          | SREN/CREM                                        | l overrides T     | XEN in SYN | C mode.      |            |              |        |

| bit 4 | 1 = Synchr                                     | ART Mode So<br>onous mode<br>pronous mode        |                   |            |              |            |              |        |

| bit 3 | Unimplem                                       | ented: Read                                      | as '0'            |            |              |            |              |        |

| bit 2 | BRGH: Hig                                      | h Baud Rate                                      | Select bit        |            |              |            |              |        |

|       | Asynchrono<br>1 = High sp<br>0 = Low sp        | beed                                             |                   |            |              |            |              |        |

|       | Synchrono<br>Unused in t                       | <u>us mode:</u>                                  |                   |            |              |            |              |        |

| bit 1 | <b>TRMT</b> : Trar<br>1 = TSR er<br>0 = TSR fu |                                                  | egister Statu     | s bit      |              |            |              |        |

| bit 0 |                                                | bit of Transm<br>dress/Data bi                   |                   | oit.       |              |            |              |        |

|       | Legend:                                        |                                                  |                   |            |              |            |              |        |

|       | R = Reada                                      | ble bit                                          | W = Wr            | itable bit | U = Unimp    | lemented b | oit, read as | '0'    |

|       | - n = Value                                    | at POR                                           | '1' = Bit         | is set     | '0' = Bit is | cleared    | x = Bit is u | nknown |

### REGISTER 16-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER

| BAUD           | Fosc = | 40 MHz     | SPBRG              | BRG 33 MHz SPBRG 25 MHz |            | SPBRG              | 20 MHz |            | SPBRG              |        |            |                    |

|----------------|--------|------------|--------------------|-------------------------|------------|--------------------|--------|------------|--------------------|--------|------------|--------------------|

| RATE<br>(Kbps) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD                   | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) |

| 0.3            | NA     | -          | -                  | NA                      | -          | -                  | NA     | -          | -                  | NA     | -          | -                  |

| 1.2            | NA     | -          | -                  | NA                      | -          | -                  | NA     | -          | -                  | NA     | -          | -                  |

| 2.4            | NA     | -          | -                  | NA                      | -          | -                  | NA     | -          | -                  | NA     | -          | -                  |

| 9.6            | NA     | -          | -                  | NA                      | -          | -                  | NA     | -          | -                  | NA     | -          | -                  |

| 19.2           | NA     | -          | -                  | NA                      | -          | -                  | NA     | -          | -                  | NA     | -          | -                  |

| 76.8           | 76.92  | +0.16      | 129                | 77.10                   | +0.39      | 106                | 77.16  | +0.47      | 80                 | 76.92  | +0.16      | 64                 |

| 96             | 96.15  | +0.16      | 103                | 95.93                   | -0.07      | 85                 | 96.15  | +0.16      | 64                 | 96.15  | +0.16      | 51                 |

| 300            | 303.03 | +1.01      | 32                 | 294.64                  | -1.79      | 27                 | 297.62 | -0.79      | 20                 | 294.12 | -1.96      | 16                 |

| 500            | 500    | 0          | 19                 | 485.30                  | -2.94      | 16                 | 480.77 | -3.85      | 12                 | 500    | 0          | 9                  |

| HIGH           | 10000  | -          | 0                  | 8250                    | -          | 0                  | 6250   | -          | 0                  | 5000   | -          | 0                  |

| LOW            | 39.06  | -          | 255                | 32.23                   | -          | 255                | 24.41  | -          | 255                | 19.53  | -          | 255                |

|  | TABLE 16-3: | BAUD RATES FOR SYNCHRONOUS MODE |

|--|-------------|---------------------------------|

|--|-------------|---------------------------------|

| BAUD           | Fosc = | c = 16 MHz SPBRG |                    | 10 MHz SPBRG |            | 7.1590             | 9 MHz   | SPBRG      | 5.0688 MHz         |         | SPBRG      |                    |  |

|----------------|--------|------------------|--------------------|--------------|------------|--------------------|---------|------------|--------------------|---------|------------|--------------------|--|

| RATE<br>(Kbps) | KBAUD  | %<br>ERROR       | value<br>(decimal) | KBAUD        | %<br>ERROR | value<br>(decimal) | KBAUD   | %<br>ERROR | value<br>(decimal) | KBAUD   | %<br>ERROR | value<br>(decimal) |  |

| 0.3            | NA     | -                | -                  | NA           | -          | -                  | NA      | -          | -                  | NA      | -          | -                  |  |

| 1.2            | NA     | -                | -                  | NA           | -          | -                  | NA      | -          | -                  | NA      | -          | -                  |  |

| 2.4            | NA     | -                | -                  | NA           | -          | -                  | NA      | -          | -                  | NA      | -          | -                  |  |

| 9.6            | NA     | -                | -                  | NA           | -          | -                  | 9.62    | +0.23      | 185                | 9.60    | 0          | 131                |  |

| 19.2           | 19.23  | +0.16            | 207                | 19.23        | +0.16      | 129                | 19.24   | +0.23      | 92                 | 19.20   | 0          | 65                 |  |

| 76.8           | 76.92  | +0.16            | 51                 | 75.76        | -1.36      | 32                 | 77.82   | +1.32      | 22                 | 74.54   | -2.94      | 16                 |  |

| 96             | 95.24  | -0.79            | 41                 | 96.15        | +0.16      | 25                 | 94.20   | -1.88      | 18                 | 97.48   | +1.54      | 12                 |  |

| 300            | 307.70 | +2.56            | 12                 | 312.50       | +4.17      | 7                  | 298.35  | -0.57      | 5                  | 316.80  | +5.60      | 3                  |  |

| 500            | 500    | 0                | 7                  | 500          | 0          | 4                  | 447.44  | -10.51     | 3                  | 422.40  | -15.52     | 2                  |  |

| HIGH           | 4000   | -                | 0                  | 2500         | -          | 0                  | 1789.80 | -          | 0                  | 1267.20 | -          | 0                  |  |

| LOW            | 15.63  | -                | 255                | 9.77         | -          | 255                | 6.99    | -          | 255                | 4.95    | -          | 255                |  |

| BAUD           | Fosc = | 4 MHz      | SPBRG              | 3.5795 | 579545 MHz SPBRG |                    | 1 MHz |            | 5                  |       | SPBRG      | 32.76              | 8 kHz | SPBRG |

|----------------|--------|------------|--------------------|--------|------------------|--------------------|-------|------------|--------------------|-------|------------|--------------------|-------|-------|

| RATE<br>(Kbps) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR       | value<br>(decimal) | KBAUD | %<br>ERROR | value<br>(decimal) | KBAUD | %<br>ERROR | value<br>(decimal) |       |       |

| 0.3            | NA     | -          | -                  | NA     | -                | -                  | NA    | -          | -                  | 0.30  | +1.14      | 26                 |       |       |

| 1.2            | NA     | -          | -                  | NA     | -                | -                  | 1.20  | +0.16      | 207                | 1.17  | -2.48      | 6                  |       |       |

| 2.4            | NA     | -          | -                  | NA     | -                | -                  | 2.40  | +0.16      | 103                | 2.73  | +13.78     | 2                  |       |       |

| 9.6            | 9.62   | +0.16      | 103                | 9.62   | +0.23            | 92                 | 9.62  | +0.16      | 25                 | 8.20  | -14.67     | 0                  |       |       |

| 19.2           | 19.23  | +0.16      | 51                 | 19.04  | -0.83            | 46                 | 19.23 | +0.16      | 12                 | NA    | -          | -                  |       |       |

| 76.8           | 76.92  | +0.16      | 12                 | 74.57  | -2.90            | 11                 | 83.33 | +8.51      | 2                  | NA    | -          | -                  |       |       |

| 96             | 1000   | +4.17      | 9                  | 99.43  | +3.57            | 8                  | 83.33 | -13.19     | 2                  | NA    | -          | -                  |       |       |

| 300            | 333.33 | +11.11     | 2                  | 298.30 | -0.57            | 2                  | 250   | -16.67     | 0                  | NA    | -          | -                  |       |       |

| 500            | 500    | 0          | 1                  | 447.44 | -10.51           | 1                  | NA    | -          | -                  | NA    | -          | -                  |       |       |

| HIGH           | 1000   | -          | 0                  | 894.89 | -                | 0                  | 250   | -          | 0                  | 8.20  | -          | 0                  |       |       |

| LOW            | 3.91   | -          | 255                | 3.50   | -                | 255                | 0.98  | -          | 255                | 0.03  | -          | 255                |       |       |

# 17.4 A/D Conversions

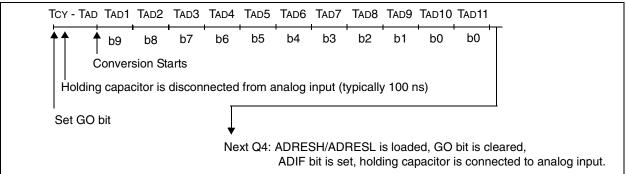

Figure 17-3 shows the operation of the A/D converter after the GO bit has been set. Clearing the GO/DONE bit during a conversion will abort the current conversion. The A/D result register pair will NOT be updated with the partially completed A/D conversion sample. That is, the ADRESH:ADRESL registers will continue to contain the value of the last completed conversion (or the last value written to the ADRESH:ADRESL registers). After the A/D conversion is aborted, a 2 TAD wait is required before the next acquisition is started. After this 2 TAD wait, acquisition on the selected channel is automatically started. The GO/DONE bit can then be set to start the conversion.

Note: The GO/DONE bit should NOT be set in the same instruction that turns on the A/D.

FIGURE 17-3: A/D CONVERSION TAD CYCLES

# 17.4.1 A/D RESULT REGISTERS

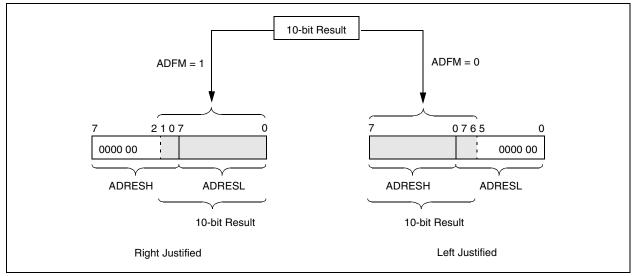

The ADRESH:ADRESL register pair is the location where the 10-bit A/D result is loaded at the completion of the A/D conversion. This register pair is 16-bits wide. The A/D module gives the flexibility to left or right justify the 10-bit result in the 16-bit result register. The A/D Format Select bit (ADFM) controls this justification. Figure 17-4 shows the operation of the A/D result justification. The extra bits are loaded with '0's. When an A/D result will not overwrite these locations (A/D disable), these registers may be used as two general purpose 8-bit registers.

FIGURE 17-4: A/D RESULT JUSTIFICATION

# 19.3 Power-down Mode (SLEEP)

Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If enabled, the Watchdog Timer will be cleared, but keeps running, the  $\overline{PD}$  bit (RCON<3>) is cleared, the  $\overline{TO}$  (RCON<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, low or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD or Vss, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D and disable external clocks. Pull all I/O pins that are hi-impedance inputs, high or low externally, to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or Vss for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

#### 19.3.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External RESET input on MCLR pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change or a Peripheral Interrupt.

The following peripheral interrupts can wake the device from SLEEP:

- 1. PSP read or write.

- 2. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 3. TMR3 interrupt. Timer3 must be operating as an asynchronous counter.

- 4. CCP Capture mode interrupt.

- 5. Special event trigger (Timer1 in Asynchronous mode using an external clock).

- 6. MSSP (START/STOP) bit detect interrupt.

- MSSP transmit or receive in Slave mode (SPI/I<sup>2</sup>C).

- 8. USART RX or TX (Synchronous Slave mode).

- 9. A/D conversion (when A/D clock source is RC).

- 10. EEPROM write operation complete.

- 11. LVD interrupt.

Other peripherals cannot generate interrupts, since during SLEEP, no on-chip clocks are present.

External MCLR Reset will cause a device RESET. All other events are considered a continuation of program execution and will cause a "wake-up". The TO and PD bits in the RCON register can be used to determine the cause of the device RESET. The PD bit, which is set on power-up, is cleared when SLEEP is invoked. The TO bit is cleared, if a WDT time-out occurred (and caused wake-up).

When the SLEEP instruction is being executed, the next instruction (PC + 2) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

#### 19.3.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If an interrupt condition (interrupt flag bit and interrupt enable bits are set) occurs before the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt condition occurs during or after the execution of a SLEEP instruction, the device will immediately wake-up from SLEEP. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

### TABLE 20-2: PIC18FXXX INSTRUCTION SET (CONTINUED)

| Mnem      | onic,  | Description                     | Cycles | 16   | 6-Bit Ins | truction | Word | Status          | Notes |

|-----------|--------|---------------------------------|--------|------|-----------|----------|------|-----------------|-------|

| Operands  |        | Description                     | Cycles | MSb  |           |          | LSb  | Affected        | Notes |

| LITERAL ( | OPERAT | IONS                            |        |      |           |          |      |                 |       |

| ADDLW     | k      | Add literal and WREG            | 1      | 0000 | 1111      | kkkk     | kkkk | C, DC, Z, OV, N |       |

| ANDLW     | k      | AND literal with WREG           | 1      | 0000 | 1011      | kkkk     | kkkk | Z, N            |       |

| IORLW     | k      | Inclusive OR literal with WREG  | 1      | 0000 | 1001      | kkkk     | kkkk | Z, N            |       |

| LFSR      | f, k   | Move literal (12-bit) 2nd word  | 2      | 1110 | 1110      | 00ff     | kkkk | None            |       |

|           |        | to FSRx 1st word                |        | 1111 | 0000      | kkkk     | kkkk |                 |       |

| MOVLB     | k      | Move literal to BSR<3:0>        | 1      | 0000 | 0001      | 0000     | kkkk | None            |       |

| MOVLW     | k      | Move literal to WREG            | 1      | 0000 | 1110      | kkkk     | kkkk | None            |       |

| MULLW     | k      | Multiply literal with WREG      | 1      | 0000 | 1101      | kkkk     | kkkk | None            |       |

| RETLW     | k      | Return with literal in WREG     | 2      | 0000 | 1100      | kkkk     | kkkk | None            |       |

| SUBLW     | k      | Subtract WREG from literal      | 1      | 0000 | 1000      | kkkk     | kkkk | C, DC, Z, OV, N |       |

| XORLW     | k      | Exclusive OR literal with WREG  | 1      | 0000 | 1010      | kkkk     | kkkk | Z, N            |       |

| DATA MEN  | MORY ↔ | PROGRAM MEMORY OPERATION        | s      |      |           |          |      |                 |       |

| TBLRD*    |        | Table Read                      | 2      | 0000 | 0000      | 0000     | 1000 | None            |       |

| TBLRD*+   |        | Table Read with post-increment  |        | 0000 | 0000      | 0000     | 1001 | None            |       |

| TBLRD*-   |        | Table Read with post-decrement  |        | 0000 | 0000      | 0000     | 1010 | None            |       |

| TBLRD+*   |        | Table Read with pre-increment   |        | 0000 | 0000      | 0000     | 1011 | None            |       |

| TBLWT*    |        | Table Write                     | 2 (5)  | 0000 | 0000      | 0000     | 1100 | None            |       |

| TBLWT*+   |        | Table Write with post-increment |        | 0000 | 0000      | 0000     | 1101 | None            |       |

| TBLWT*-   |        | Table Write with post-decrement |        | 0000 | 0000      | 0000     | 1110 | None            |       |

| TBLWT+*   |        | Table Write with pre-increment  |        | 0000 | 0000      | 0000     | 1111 | None            |       |

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are 2-word instructions. The second word of these instructions will be executed as a NOP, unless the first word of the instruction retrieves the information embedded in these 16-bits. This ensures that all program memory locations have a valid instruction.

5: If the Table Write starts the write cycle to internal memory, the write will continue until terminated.

| CPF                                                                             | SGT             | Compare                                                                                                                                           | f with W,                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | skip if | f > W         |  |  |  |  |

|---------------------------------------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------|--|--|--|--|

| Synt                                                                            | ax:             | [label] C                                                                                                                                         | PFSGT                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | f [,a]  |               |  |  |  |  |

| Ope                                                                             | rands:          | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                                          | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |               |  |  |  |  |

| Ope                                                                             | ration:         | (f) – (W),<br>skip if (f) >                                                                                                                       | · (W)                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |               |  |  |  |  |

|                                                                                 |                 | (unsigned                                                                                                                                         | (unsigned comparison)                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |               |  |  |  |  |

| Statu                                                                           | us Affected:    | None                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |               |  |  |  |  |

| Enco                                                                            | oding:          | 0110                                                                                                                                              | 010a                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ffff    | ffff          |  |  |  |  |

| Desc                                                                            | cription:       | memory lo<br>of the W b<br>unsigned a<br>If the conter<br>fetched ins<br>a NOP is e<br>this a two-<br>0, the Acc<br>selected, o<br>If 'a' = 1, th | Compares the contents of data<br>memory location 'f' to the contents<br>of the W by performing an<br>unsigned subtraction.<br>If the contents of 'f' are greater than<br>the contents of WREG, then the<br>fetched instruction is discarded and<br>a NOP is executed instead, making<br>this a two-cycle instruction. If 'a' is<br>0, the Access Bank will be<br>selected, overriding the BSR value.<br>If 'a' = 1, then the bank will be<br>selected as per the BSR value |         |               |  |  |  |  |

| Wor                                                                             | de.             | 1                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |               |  |  |  |  |

| Cycles: 1(2)<br>Note: 3 cycles if skip and followed<br>by a 2-word instruction. |                 |                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |               |  |  |  |  |

| 00                                                                              | cycle Activity: | -                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |               |  |  |  |  |

|                                                                                 | Q1              | Q2                                                                                                                                                | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         | Q4            |  |  |  |  |

|                                                                                 | Decode          | Read                                                                                                                                              | Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         | No            |  |  |  |  |

|                                                                                 |                 | register 'f'                                                                                                                                      | Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ор      | eration       |  |  |  |  |

| lf sk                                                                           |                 |                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         | <u>.</u>      |  |  |  |  |

|                                                                                 | Q1<br>No        | Q2<br>No                                                                                                                                          | Q3<br>No                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         | Q4<br>No      |  |  |  |  |

|                                                                                 | operation       | operation                                                                                                                                         | operatior                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | n op    | eration       |  |  |  |  |

| lf sł                                                                           | kip and follow  |                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |               |  |  |  |  |

|                                                                                 | Q1              | Q2                                                                                                                                                | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         | Q4            |  |  |  |  |

|                                                                                 | No              | No                                                                                                                                                | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         | No            |  |  |  |  |

|                                                                                 | operation       | operation                                                                                                                                         | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | n op    | eration       |  |  |  |  |

|                                                                                 | No<br>operation | No<br>operation                                                                                                                                   | No<br>operatior                                                                                                                                                                                                                                                                                                                                                                                                                                                            | n op    | No<br>eration |  |  |  |  |

| <u>Exar</u>                                                                     | <u>mple</u> :   | HERE<br>NGREATER<br>GREATER                                                                                                                       | CPFSGT<br>:<br>:                                                                                                                                                                                                                                                                                                                                                                                                                                                           | REG,    | 0             |  |  |  |  |

| Before Instruction<br>PC = Address (HERE)<br>W = ?                              |                 |                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |               |  |  |  |  |

|                                                                                 | After Instruct  | tion                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |               |  |  |  |  |

|                                                                                 | If REG<br>PC    |                                                                                                                                                   | dress (GR                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | EATER)  |               |  |  |  |  |

|                                                                                 | If REG<br>PC    | ≤ W;<br>= Ad                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | REATEF  | 2)            |  |  |  |  |

| CPF                                                                                                                                                                                                                                                                                                                                                                                                                                        | SLT                  | Compare                  | f with W, sk          | ip if f < W  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------|-----------------------|--------------|--|--|--|--|--|--|

| Synt                                                                                                                                                                                                                                                                                                                                                                                                                                       | ax:                  | [label] C                | CPFSLT f[,            | a]           |  |  |  |  |  |  |

| Ope                                                                                                                                                                                                                                                                                                                                                                                                                                        | rands:               | 0 ≤ f ≤ 255<br>a ∈ [0,1] | 5                     |              |  |  |  |  |  |  |

| Ope                                                                                                                                                                                                                                                                                                                                                                                                                                        | ration:              |                          | (f) - (W),            |              |  |  |  |  |  |  |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                          |                      | skip if (f) <            |                       |              |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      |                          | (unsigned comparison) |              |  |  |  |  |  |  |

| Statu                                                                                                                                                                                                                                                                                                                                                                                                                                      | us Affected:         | None                     | None                  |              |  |  |  |  |  |  |

| Enco                                                                                                                                                                                                                                                                                                                                                                                                                                       | oding:               | 0110                     | 000a fff              | ff ffff      |  |  |  |  |  |  |

| Description:<br>Compares the contents of data<br>memory location 'f' to the contents<br>of W by performing an unsigned<br>subtraction.<br>If the contents of 'f' are less than<br>the contents of W, then the fetched<br>instruction is discarded and a NOP<br>is executed instead, making this a<br>two-cycle instruction. If 'a' is 0, the<br>Access Bank will be selected. If 'a'<br>is 1, the BSR will not be overridder<br>(default). |                      |                          |                       |              |  |  |  |  |  |  |

| Wor                                                                                                                                                                                                                                                                                                                                                                                                                                        | ds:                  | 1                        |                       |              |  |  |  |  |  |  |

| Cycl                                                                                                                                                                                                                                                                                                                                                                                                                                       |                      | 1(2)                     |                       |              |  |  |  |  |  |  |

| 0,0                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      | ( )                      | cycles if skip        | and followed |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      | by                       | a 2-word ins          | struction.   |  |  |  |  |  |  |

| QC                                                                                                                                                                                                                                                                                                                                                                                                                                         | Cycle Activity:      | _                        | 0.0                   | <u> </u>     |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                            | Q1<br>Decode         | Q2<br>Read               | Q3<br>Process         | Q4<br>No     |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                            | Decoue               | register 'f'             | Data                  | operation    |  |  |  |  |  |  |

| lf sł                                                                                                                                                                                                                                                                                                                                                                                                                                      | kip:                 |                          |                       |              |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                            | Q1                   | Q2                       | Q3                    | Q4           |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                            | No                   | No                       | No                    | No           |  |  |  |  |  |  |

| lf al                                                                                                                                                                                                                                                                                                                                                                                                                                      | operation            | operation                | operation             | operation    |  |  |  |  |  |  |

| II Sr                                                                                                                                                                                                                                                                                                                                                                                                                                      | kip and follow<br>Q1 | Q2                       | Q3                    | Q4           |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                            | No                   | No                       | No                    | No           |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                            | operation            | operation                | operation             | operation    |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                            | No                   | No                       | No                    | No           |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                            | operation            | operation                | operation             | operation    |  |  |  |  |  |  |

| <u>Exa</u>                                                                                                                                                                                                                                                                                                                                                                                                                                 | <u>mple</u> :        | NLESS                    | CPFSLT REG,<br>:<br>: | 1            |  |  |  |  |  |  |

| Before Instruction                                                                                                                                                                                                                                                                                                                                                                                                                         |                      |                          |                       |              |  |  |  |  |  |  |