Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I²C, SPI, UART/USART                                                      |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 34                                                                        |

| Program Memory Size        | 32KB (16K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1.5K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-TQFP                                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf452-i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

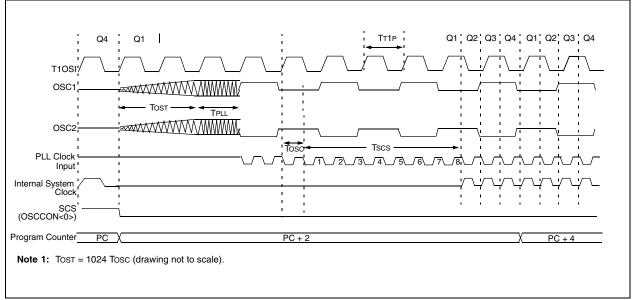

If the main oscillator is configured for HS-PLL mode, an oscillator start-up time (TOST) plus an additional PLL time-out (TPLL) will occur. The PLL time-out is typically 2 ms and allows the PLL to lock to the main oscillator frequency. A timing diagram indicating the transition from the Timer1 oscillator to the main oscillator for HS-PLL mode is shown in Figure 2-10.

FIGURE 2-10: TIMING FOR TRANSITION BETWEEN TIMER1 AND OSC1 (HS WITH PLL)

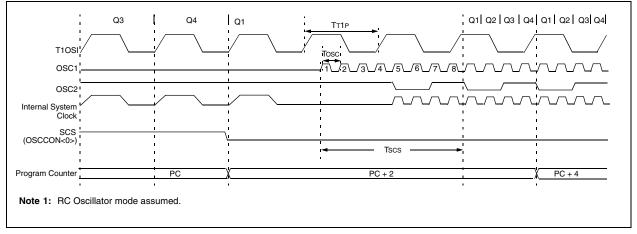

If the main oscillator is configured in the RC, RCIO, EC or ECIO modes, there is no oscillator start-up time-out. Operation will resume after eight cycles of the main oscillator have been counted. A timing diagram, indicating the transition from the Timer1 oscillator to the main oscillator for RC, RCIO, EC and ECIO modes, is shown in Figure 2-11.

### FIGURE 2-11: TIMING FOR TRANSITION BETWEEN TIMER1 AND OSC1 (RC, EC)

### 4.7.1 TWO-WORD INSTRUCTIONS

The PIC18FXX2 devices have four two-word instructions: MOVFF, CALL, GOTO and LFSR. The second word of these instructions has the 4 MSBs set to 1's and is a special kind of NOP instruction. The lower 12 bits of the second word contain data to be used by the instruction. If the first word of the instruction is executed, the data in the second word is accessed. If the second word of the instruction is executed by itself (first word was skipped), it will execute as a NOP. This action is necessary when the two-word instruction is preceded by a conditional instruction that changes the PC. A program example that demonstrates this concept is shown in Example 4-3. Refer to Section 20.0 for further details of the instruction set.

| EXAMPLE 4-3: | <b>TWO-WORD INSTRUCTIONS</b> |

|--------------|------------------------------|

|              |                              |

| CASE 1:                 |                                                   |  |  |  |  |  |  |  |

|-------------------------|---------------------------------------------------|--|--|--|--|--|--|--|

| Object Code Source Code |                                                   |  |  |  |  |  |  |  |

| 0110 0110 0000 0000     | TSTFSZ REG1 ; is RAM location 0?                  |  |  |  |  |  |  |  |

| 1100 0001 0010 0011     | MOVFF REG1, REG2 ; No, execute 2-word instruction |  |  |  |  |  |  |  |

| 1111 0100 0101 0110     | ; 2nd operand holds address of REG2               |  |  |  |  |  |  |  |

| 0010 0100 0000 0000     | ADDWF REG3 ; continue code                        |  |  |  |  |  |  |  |

|                         |                                                   |  |  |  |  |  |  |  |

| CASE 2:                 |                                                   |  |  |  |  |  |  |  |

| Object Code             | Source Code                                       |  |  |  |  |  |  |  |

| 0110 0110 0000 0000     | TSTFSZ REG1 ; is RAM location 0?                  |  |  |  |  |  |  |  |

| 1100 0001 0010 0011     | MOVFF REG1, REG2 ; Yes                            |  |  |  |  |  |  |  |

| 1111 0100 0101 0110     | ; 2nd operand becomes NOP                         |  |  |  |  |  |  |  |

| 0010 0100 0000 0000     | ADDWF REG3 ; continue code                        |  |  |  |  |  |  |  |

## 4.8 Lookup Tables

Lookup tables are implemented two ways. These are:

- Computed GOTO

- Table Reads

### 4.8.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF  $\,$  PCL).

A lookup table can be formed with an ADDWF PCL instruction and a group of RETLW 0xnn instructions. WREG is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW 0xnn instructions, that returns the value 0xnn to the calling function.

The offset value (value in WREG) specifies the number of bytes that the program counter should advance.

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

Note: The ADDWF PCL instruction does not update PCLATH and PCLATU. A read operation on PCL must be performed to update PCLATH and PCLATU.

## 4.8.2 TABLE READS/TABLE WRITES

A better method of storing data in program memory allows 2 bytes of data to be stored in each instruction location.

Lookup table data may be stored 2 bytes per program word by using table reads and writes. The table pointer (TBLPTR) specifies the byte address and the table latch (TABLAT) contains the data that is read from, or written to program memory. Data is transferred to/from program memory, one byte at a time.

A description of the Table Read/Table Write operation is shown in Section 3.0.

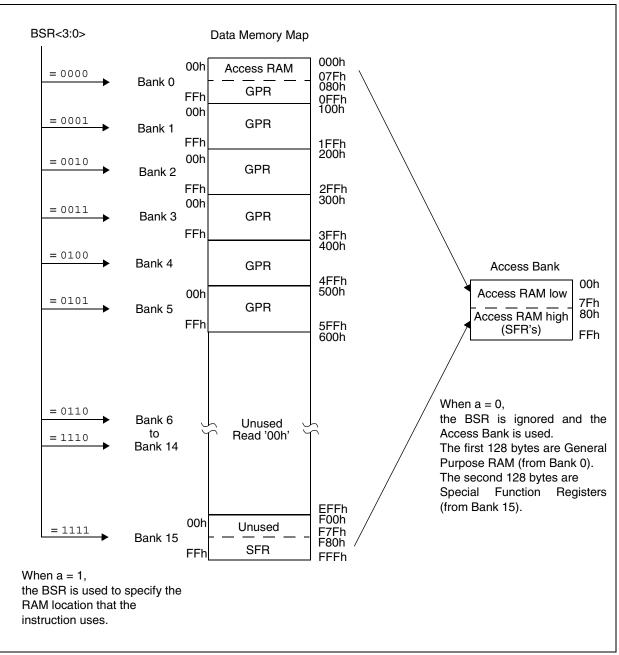

### FIGURE 4-7: DATA MEMORY MAP FOR PIC18F252/452

## REGISTER 5-1: EECON1 REGISTER (ADDRESS FA6h)

|       | R/W-x             | R/W-x                       | U-0          | R/W-0               | R/W-x                            | R/W-0        | R/S-0        | R/S-0       |

|-------|-------------------|-----------------------------|--------------|---------------------|----------------------------------|--------------|--------------|-------------|

|       | EEPGD             | CFGS                        | —            | FREE                | WRERR                            | WREN         | WR           | RD          |

|       | bit 7             |                             |              |                     |                                  |              |              | bit 0       |

| L:1 7 |                   |                             |              |                     | Assess Only at                   | L 14         |              |             |

| bit 7 |                   | •                           |              |                     | lemory Select                    | DI           |              |             |

|       |                   | FLASH Pro                   |              |                     |                                  |              |              |             |

| bit 6 | CFGS: FL/         | ASH Progra                  | m/Data EE    | or Configura        | ation Select bit                 |              |              |             |

|       |                   | Configurati                 |              |                     |                                  |              |              |             |

|       | 0 = Access        | FLASH Pro                   | ogram or Da  | ata EEPRON          | /I memory                        |              |              |             |

| bit 5 | Unimplem          | ented: Rea                  | d as '0'     |                     |                                  |              |              |             |

| bit 4 |                   | ASH Row Er                  |              |                     |                                  |              |              |             |

|       |                   |                             |              |                     | d by TBLPTR c                    | on the next  | WR comma     | and         |

|       |                   | n write only                | tion of eras | e operation)        |                                  |              |              |             |

| bit 3 | WRERR: F          | LASH Prog                   | ram/Data E   | E Error Flag        | ı bit                            |              |              |             |

|       |                   | -                           |              | ly terminate        |                                  |              |              |             |

|       |                   |                             |              |                     | ng in normal op                  | eration)     |              |             |

|       |                   | ite operatior               | •            |                     |                                  |              |              |             |

|       |                   | nen a WRE⊦<br>cing of the € |              |                     | and CFGS bits                    | are not cle  | eared. This  | allows      |

|       | i u               |                             |              | 011.                |                                  |              |              |             |

| bit 2 | WREN: FL          | ASH Progra                  | ım/Data EE   | Write Enab          | le bit                           |              |              |             |

|       |                   | write cycles                |              |                     |                                  |              |              |             |

|       |                   | write to the                | EEPROM       |                     |                                  |              |              |             |

| bit 1 | WR: Write         |                             |              | ,                   |                                  |              |              |             |

|       |                   |                             |              |                     | or a program m<br>leared by hard |              |              |             |

|       | · · ·             |                             |              | eared) in sof       | •                                | ware once    |              | ipiele. The |

|       |                   | ycle to the E               |              |                     | ,                                |              |              |             |

| bit 0 | RD: Read          | Control bit                 |              |                     |                                  |              |              |             |

|       |                   | s an EEPRC                  |              |                     |                                  |              |              |             |

|       |                   |                             |              |                     | rdware. The RI                   | D bit can or | ly be set (n | ot cleared) |

|       |                   | ot initiate ar              |              | set when EE<br>read | :PGD = 1.)                       |              |              |             |

|       | 0 – <b>2000</b> H | et anitato ul               |              |                     |                                  |              |              |             |

|       | Legend:           |                             |              |                     |                                  |              |              |             |

|       | Logona            |                             |              |                     |                                  |              |              |             |

W = Writable bit

'1' = Bit is set

R = Readable bit

- n = Value at POR

x = Bit is unknown

U = Unimplemented bit, read as '0'

'0' = Bit is cleared

| TABLE 9-5: | PORTC FUNCTIONS |

|------------|-----------------|

|            |                 |

| Name            | Bit# | Buffer Type | Function                                                                                                                               |

|-----------------|------|-------------|----------------------------------------------------------------------------------------------------------------------------------------|

| RC0/T1OSO/T1CKI | bit0 | ST          | Input/output port pin or Timer1 oscillator output/Timer1 clock input.                                                                  |

| RC1/T1OSI/CCP2  | bit1 | ST          | Input/output port pin, Timer1 oscillator input, or Capture2 input/<br>Compare2 output/PWM output when CCP2MX configuration bit is set. |

| RC2/CCP1        | bit2 | ST          | Input/output port pin or Capture1 input/Compare1 output/PWM1 output.                                                                   |

| RC3/SCK/SCL     | bit3 | ST          | RC3 can also be the synchronous serial clock for both SPI and $I^2C$ modes.                                                            |

| RC4/SDI/SDA     | bit4 | ST          | RC4 can also be the SPI Data In (SPI mode) or Data I/O ( $I^2$ C mode).                                                                |

| RC5/SDO         | bit5 | ST          | Input/output port pin or Synchronous Serial Port data output.                                                                          |

| RC6/TX/CK       | bit6 | ST          | Input/output port pin, Addressable USART Asynchronous Transmit, or Addressable USART Synchronous Clock.                                |

| RC7/RX/DT       | bit7 | ST          | Input/output port pin, Addressable USART Asynchronous Receive, or Addressable USART Synchronous Data.                                  |

Legend: ST = Schmitt Trigger input

## TABLE 9-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Name  | Bit 7                               | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0     | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |

|-------|-------------------------------------|-------|-------|-------|-------|-------|-------|-----------|----------------------|---------------------------------|

| PORTC | RC7                                 | RC6   | RC5   | RC4   | RC3   | RC2   | RC1   | RC0       | xxxx xxxx            | uuuu uuuu                       |

| LATC  | LATC Data Output Register           |       |       |       |       |       |       | xxxx xxxx | uuuu uuuu            |                                 |

| TRISC | IRISC PORTC Data Direction Register |       |       |       |       |       |       |           | 1111 1111            | 1111 1111                       |

Legend: x = unknown, u = unchanged

# 13.0 TIMER3 MODULE

The Timer3 module timer/counter has the following features:

- 16-bit timer/counter (two 8-bit registers; TMR3H and TMR3L)

- Readable and writable (both registers)

- Internal or external clock select

- Interrupt-on-overflow from FFFFh to 0000h

- RESET from CCP module trigger

Figure 13-1 is a simplified block diagram of the Timer3 module.

Register 13-1 shows the Timer3 control register. This register controls the Operating mode of the Timer3 module and sets the CCP clock source.

Register 11-1 shows the Timer1 control register. This register controls the Operating mode of the Timer1 module, as well as contains the Timer1 oscillator enable bit (T1OSCEN), which can be a clock source for Timer3.

### REGISTER 13-1: T3CON: TIMER3 CONTROL REGISTER

| R/W-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0  | R/W-0         | R/W-0  | R/W-0  |

|-------|--------|---------|---------|--------|---------------|--------|--------|

| RD16  | T3CCP2 | T3CKPS1 | T3CKPS0 | T3CCP1 | <b>T3SYNC</b> | TMR3CS | TMR3ON |

| bit 7 |        |         |         |        |               |        | bit 0  |

| bit 7   | RD16: 16-bit Read/Write N                            | Node Enable bit            |                      |                    |

|---------|------------------------------------------------------|----------------------------|----------------------|--------------------|

|         | 1 = Enables register Read                            | /Write of Timer3 in one    | e 16-bit operation   |                    |

|         | 0 = Enables register Read                            | /Write of Timer3 in two    | o 8-bit operations   |                    |

| bit 6-3 | T3CCP2:T3CCP1: Timer3                                | and Timer1 to CCPx         | Enable bits          |                    |

|         | 1x = Timer3 is the clock so                          | ource for compare/cap      | ture CCP modules     |                    |

|         | 01 = Timer3 is the clock so                          |                            |                      |                    |

|         |                                                      | ource for compare/cap      |                      |                    |

|         | 00 = Timer1 is the clock so                          | ource for compare/cap      | ture CCP modules     |                    |

| bit 5-4 | T3CKPS1:T3CKPS0: Time                                | er3 Input Clock Presca     | ale Select bits      |                    |

|         | 11 = 1:8 Prescale value                              |                            |                      |                    |

|         | 10 = 1:4 Prescale value                              |                            |                      |                    |

|         | 01 = 1:2 Prescale value                              |                            |                      |                    |

|         | 00 = 1:1 Prescale value                              |                            |                      |                    |

| bit 2   | T3SYNC: Timer3 External                              | • •                        |                      |                    |

|         | (Not usable if the system of                         | CIOCK COMES FROM TIME      | er i/Timer3)         |                    |

|         | <u>When TMR3CS = 1:</u><br>1 = Do not synchronize ex | tornal clock input         |                      |                    |

|         | 0 = Synchronize external of                          |                            |                      |                    |

|         | When TMR3CS = $0$ :                                  |                            |                      |                    |

|         | This bit is ignored. Timer3                          | uses the internal clock    | when TMB3CS - 0      |                    |

| bit 1   | TMR3CS: Timer3 Clock S                               |                            |                      |                    |

|         |                                                      |                            |                      |                    |

|         | 1 = External clock input fr                          | ter the first falling edge |                      |                    |

|         | 0 = Internal clock (Fosc/4                           |                            | ·)                   |                    |

| bit 0   | TMR3ON: Timer3 On bit                                | /                          |                      |                    |

| Sit 0   | 1 = Enables Timer3                                   |                            |                      |                    |

|         | 0 = Stops Timer3                                     |                            |                      |                    |

|         |                                                      |                            |                      |                    |

|         | Legend:                                              |                            |                      |                    |

|         | R = Readable bit                                     | W = Writable bit           | U = Unimplemented    | bit, read as '0'   |

|         | - n = Value at POR                                   | '1' = Bit is set           | '0' = Bit is cleared | x = Bit is unknown |

|         | ··· -                                                |                            |                      | -                  |

### 15.4.6.1 I<sup>2</sup>C Master Mode Operation

The master device generates all of the serial clock pulses and the START and STOP conditions. A transfer is ended with a STOP condition or with a Repeated START condition. Since the Repeated START condition is also the beginning of the next serial transfer, the  $I^2C$  bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an Acknowledge bit is received. START and STOP conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/W bit. In this case, the R/W bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an Acknowledge bit is transmitted. START and STOP conditions indicate the beginning and end of transmission.

The baud rate generator used for the SPI mode operation is used to set the SCL clock frequency for either 100 kHz, 400 kHz or 1 MHz  $I^2C$  operation. See Section 15.4.7 ("Baud Rate Generator"), for more detail. A typical transmit sequence would go as follows:

- 1. The user generates a START condition by setting the START enable bit, SEN (SSPCON2<0>).

- SSPIF is set. The MSSP module will wait the required start time before any other operation takes place.

- 3. The user loads the SSPBUF with the slave address to transmit.

- 4. Address is shifted out the SDA pin until all 8 bits are transmitted.

- 5. The MSSP Module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register (SSPCON2<6>).

- 6. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- 7. The user loads the SSPBUF with eight bits of data.

- 8. Data is shifted out the SDA pin until all 8 bits are transmitted.

- 9. The MSSP Module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register (SSPCON2<6>).

- 10. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- 11. The user generates a STOP condition by setting the STOP enable bit PEN (SSPCON2<2>).

- 12. Interrupt is generated once the STOP condition is complete.

NOTES:

| Byte-oriented file register operations Example Instruction   15 10 9 8 7 0   OPCODE d a f (FILE #) ADDWF MYREG, W, B                                                                                                                                          |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| OPCODE d a f (FILE #) ADDWF MYREG, W, B                                                                                                                                                                                                                       |  |

| d = 0 for result destination to be WREG register<br>d = 1 for result destination to be file register (f)<br>a = 0 to force Access Bank<br>a = 1 for BSR to select bank<br>f = 8-bit file register address                                                     |  |

| Byte to Byte move operations (2-word)                                                                                                                                                                                                                         |  |

| 15   12   11   0     OPCODE   f (Source FILE #)   MOVFF MYREG1, MYREG2     15   12   11   0     1111   f (Destination FILE #)   f = 12-bit file register address                                                                                              |  |

| Bit-oriented file register operations                                                                                                                                                                                                                         |  |

| 15   12 11   9 8 7   0     OPCODE   b (BIT #)   a   f (FILE #)   BSF MYREG, bit, B     b = 3-bit position of bit in file register (f)   a = 0 to force Access Bank   a = 1 for BSR to select bank     f = 8-bit file register address   f   BSF MYREG, bit, B |  |

| Literal operations                                                                                                                                                                                                                                            |  |

| 15     8     7     0       OPCODE     k (literal)     MOVLW 0x7F       k = 8-bit immediate value     K                                                                                                                                                        |  |

| Control operations                                                                                                                                                                                                                                            |  |

| CALL, GOTO and Branch operations                                                                                                                                                                                                                              |  |

| 15 8 7 0   OPCODE n<7:0> (literal) GOTO Label   15 12 11 0   1111 n<19:8> (literal) 1111                                                                                                                                                                      |  |

| n = 20-bit immediate value                                                                                                                                                                                                                                    |  |

| 15 8 7 0   OPCODE S n<7:0> (literal) CALL MYFUNC   15 12 11 0   n<19:8> (literal) S = Fast bit                                                                                                                                                                |  |

| 15 11 10 0   OPCODE n<10:0> (literal) BRA MYFUNC                                                                                                                                                                                                              |  |

| 15     8     7     0       OPCODE     n<7:0> (literal)     BC MYFUNC                                                                                                                                                                                          |  |

| CPFSGT Compare f with W, skip if f > V                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |                             |                  |                                                                           |               |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------|------------------|---------------------------------------------------------------------------|---------------|--|--|--|--|

| Synt                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ax:               | [label] C                   | PFSGT            | f [,a]                                                                    |               |  |  |  |  |

| Ope                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | rands:            | 0 ≤ f ≤ 255<br>a ∈ [0,1]    | 5                |                                                                           |               |  |  |  |  |

| Ope                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ration:           | (f) – (W),<br>skip if (f) > | · (W)            |                                                                           |               |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   | (unsigned                   | comparis         | on)                                                                       |               |  |  |  |  |

| Statu                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | us Affected:      | None                        | None             |                                                                           |               |  |  |  |  |

| Enco                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | oding:            | 0110                        | 010a             | ffff                                                                      | ffff          |  |  |  |  |

| Description:<br>Compares the contents of data<br>memory location 'f' to the contents<br>of the W by performing an<br>unsigned subtraction.<br>If the contents of 'f' are greater if<br>the contents of WREG, then th<br>fetched instruction is discarded<br>a NOP is executed instead, mail<br>this a two-cycle instruction. If 'a<br>0, the Access Bank will be<br>selected, overriding the BSR va-<br>If 'a' = 1, then the bank will be<br>selected as per the BSR value |                   |                             |                  | ater than<br>on the<br>ded and<br>making<br>. If 'a' is<br>R value.<br>be |               |  |  |  |  |

| Wor                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | de.               | (default).<br>1             |                  |                                                                           |               |  |  |  |  |

| Cycles: 1(2)<br>Note: 3 cycles if skip and followed<br>by a 2-word instruction.                                                                                                                                                                                                                                                                                                                                                                                            |                   |                             |                  |                                                                           |               |  |  |  |  |

| 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | cycle Activity:   | -                           |                  |                                                                           |               |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Q1                | Q2                          | Q3               |                                                                           | Q4            |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Decode            | Read                        | Process          |                                                                           | No            |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   | register 'f'                | Data             | ор                                                                        | eration       |  |  |  |  |

| lf sk                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |                             |                  |                                                                           |               |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Q1<br>No          | Q2<br>No                    | Q3<br>No         |                                                                           | Q4<br>No      |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | operation         | operation                   | operatior        | n op                                                                      | eration       |  |  |  |  |

| lf sł                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | kip and follow    |                             |                  |                                                                           |               |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Q1                | Q2                          | Q3               |                                                                           | Q4            |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | No                | No                          | No               |                                                                           | No            |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | operation         | operation                   | operation        | n op                                                                      | eration       |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | No<br>operation   | No<br>operation             | No<br>operatior  | n op                                                                      | No<br>eration |  |  |  |  |

| <u>Exar</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <u>nple</u> :     | HERE<br>NGREATER<br>GREATER | CPFSGT<br>:<br>: | REG,                                                                      | 0             |  |  |  |  |

| Before Instruction<br>PC = Address (HERE)<br>W = ?                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |                             |                  |                                                                           |               |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | After Instruction |                             |                  |                                                                           |               |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | If REG<br>PC      |                             | dress (GR        | EATER)                                                                    |               |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | If REG<br>PC      | ≤ W;<br>= Ad                |                  | REATEF                                                                    | 2)            |  |  |  |  |

| CPF                                       | SLT                                              | Compare                                                                                                                                                                                                                                                                                                                                                                                                                    | f with W, sk          | ip if f < W  |  |  |  |  |  |

|-------------------------------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------|--|--|--|--|--|

| Synt                                      | ax:                                              | [label] C                                                                                                                                                                                                                                                                                                                                                                                                                  | CPFSLT f[,            | a]           |  |  |  |  |  |

| Ope                                       | rands:                                           | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                   | 5                     |              |  |  |  |  |  |

| Ope                                       | ration:                                          | (f) - (W),                                                                                                                                                                                                                                                                                                                                                                                                                 |                       |              |  |  |  |  |  |

| •                                         |                                                  | skip if (f) <                                                                                                                                                                                                                                                                                                                                                                                                              |                       |              |  |  |  |  |  |

|                                           |                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                            | (unsigned comparison) |              |  |  |  |  |  |

| Statu                                     | tus Affected: None<br>coding: 0110 000a ffff fff |                                                                                                                                                                                                                                                                                                                                                                                                                            |                       |              |  |  |  |  |  |

| Enco                                      | oding:                                           | 0110                                                                                                                                                                                                                                                                                                                                                                                                                       | 000a fff              | ff ffff      |  |  |  |  |  |

| Des                                       | cription:                                        | Compares the contents of data<br>memory location 'f' to the contents<br>of W by performing an unsigned<br>subtraction.<br>If the contents of 'f' are less than<br>the contents of W, then the fetched<br>instruction is discarded and a NOP<br>is executed instead, making this a<br>two-cycle instruction. If 'a' is 0, the<br>Access Bank will be selected. If 'a'<br>is 1, the BSR will not be overridden<br>(default). |                       |              |  |  |  |  |  |

| Wor                                       | ds:                                              | 1                                                                                                                                                                                                                                                                                                                                                                                                                          |                       |              |  |  |  |  |  |

| Cycl                                      |                                                  | 1(2)                                                                                                                                                                                                                                                                                                                                                                                                                       |                       |              |  |  |  |  |  |

| 0,0                                       |                                                  | ( )                                                                                                                                                                                                                                                                                                                                                                                                                        | cycles if skip        | and followed |  |  |  |  |  |

|                                           |                                                  | by                                                                                                                                                                                                                                                                                                                                                                                                                         | a 2-word ins          | struction.   |  |  |  |  |  |

| QC                                        | Cycle Activity:                                  | _                                                                                                                                                                                                                                                                                                                                                                                                                          | 0.0                   | <u> </u>     |  |  |  |  |  |

|                                           | Q1<br>Decode                                     | Q2<br>Read                                                                                                                                                                                                                                                                                                                                                                                                                 | Q3<br>Process         | Q4<br>No     |  |  |  |  |  |

|                                           | Decoue                                           | register 'f'                                                                                                                                                                                                                                                                                                                                                                                                               | Data                  | operation    |  |  |  |  |  |

| lf sł                                     | kip:                                             |                                                                                                                                                                                                                                                                                                                                                                                                                            |                       |              |  |  |  |  |  |

|                                           | Q1                                               | Q2                                                                                                                                                                                                                                                                                                                                                                                                                         | Q3                    | Q4           |  |  |  |  |  |

|                                           | No                                               | No                                                                                                                                                                                                                                                                                                                                                                                                                         | No                    | No           |  |  |  |  |  |

| lf al                                     | operation                                        | operation                                                                                                                                                                                                                                                                                                                                                                                                                  | operation             | operation    |  |  |  |  |  |

| II Sr                                     | kip and follow<br>Q1                             | Q2                                                                                                                                                                                                                                                                                                                                                                                                                         | Q3                    | Q4           |  |  |  |  |  |

|                                           | No                                               | No                                                                                                                                                                                                                                                                                                                                                                                                                         | No                    | No           |  |  |  |  |  |

|                                           | operation                                        | operation                                                                                                                                                                                                                                                                                                                                                                                                                  | operation             | operation    |  |  |  |  |  |

|                                           | No                                               | No                                                                                                                                                                                                                                                                                                                                                                                                                         | No                    | No           |  |  |  |  |  |

|                                           | operation                                        | operation                                                                                                                                                                                                                                                                                                                                                                                                                  | operation             | operation    |  |  |  |  |  |

| Example: HERE CPFSLT<br>NLESS :<br>LESS : |                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                            |                       | 1            |  |  |  |  |  |

| Before Instruction                        |                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                            |                       |              |  |  |  |  |  |

| PC = Address (HERE)<br>W = ?              |                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                            |                       |              |  |  |  |  |  |

|                                           | After Instruction                                |                                                                                                                                                                                                                                                                                                                                                                                                                            |                       |              |  |  |  |  |  |

|                                           | If REG                                           | < W;                                                                                                                                                                                                                                                                                                                                                                                                                       | ;                     |              |  |  |  |  |  |

|                                           | PC                                               | = Ad                                                                                                                                                                                                                                                                                                                                                                                                                       | dress (LESS)          | )            |  |  |  |  |  |

|                                           | If REG<br>PC                                     | ≥ W;<br>= Ad                                                                                                                                                                                                                                                                                                                                                                                                               | ;<br>Idress (NLES:    | S)           |  |  |  |  |  |

|                                           |                                                  | , (0                                                                                                                                                                                                                                                                                                                                                                                                                       |                       |              |  |  |  |  |  |

|                                           |                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                            |                       |              |  |  |  |  |  |

| IORLW            | ral with                             | w             |      |          |

|------------------|--------------------------------------|---------------|------|----------|

| Syntax:          | [ label ]                            | IORLW         | k    |          |

| Operands:        | $0 \le k \le 25$                     | 5             |      |          |

| Operation:       | (W) .OR.                             | $k \to W$     |      |          |

| Status Affected: | N, Z                                 |               |      |          |

| Encoding:        | 0000                                 | 1001          | kkkk | kkkk     |

| Description:     | The conte<br>the eight-<br>placed in | bit literal   |      | •••      |

| Words:           | 1                                    |               |      |          |

| Cycles:          | 1                                    |               |      |          |

| Q Cycle Activity | :                                    |               |      |          |

| Q1               | Q2                                   | Q3            | 3    | Q4       |

| Decode           | Read<br>literal 'k'                  | Proce<br>Data |      | ite to W |

| Example:         | IORLW                                | 0x35          |      |          |

| Before Instru    | uction                               |               |      |          |

| W                | = 0x9A                               |               |      |          |

| After Instruc    | tion                                 |               |      |          |

| W                | = 0xBF                               |               |      |          |

|                  |                                      |               |      |          |

| IORWF Inclusive OR W with f         |                                                                                                                                                                                                                                                                            |                        |                      |  |  |  |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------|--|--|--|

| Syntax:                             | [ label ]                                                                                                                                                                                                                                                                  | IORWF f[               | ,d [,a]              |  |  |  |

| Operands:                           | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                        |                        |                      |  |  |  |

| Operation:                          | (W) .OR.                                                                                                                                                                                                                                                                   | (f) $\rightarrow$ dest |                      |  |  |  |

| Status Affected:                    | N, Z                                                                                                                                                                                                                                                                       |                        |                      |  |  |  |

| Encoding:                           | 0001                                                                                                                                                                                                                                                                       | 00da ff                | ff ffff              |  |  |  |

|                                     | is 0, the result is placed in W. If 'd'<br>is 1, the result is placed back in<br>register 'f' (default). If 'a' is 0, the<br>Access Bank will be selected, over-<br>riding the BSR value. If 'a' = 1, then<br>the bank will be selected as per the<br>BSR value (default). |                        |                      |  |  |  |

| Words:                              | 1                                                                                                                                                                                                                                                                          |                        |                      |  |  |  |

| Cycles:                             | 1                                                                                                                                                                                                                                                                          |                        |                      |  |  |  |

| Q Cycle Activity:                   |                                                                                                                                                                                                                                                                            |                        |                      |  |  |  |

| Q1                                  | Q2                                                                                                                                                                                                                                                                         | Q3                     | Q4                   |  |  |  |

| Decode                              | Read<br>register 'f'                                                                                                                                                                                                                                                       | Process<br>Data        | Write to destination |  |  |  |

| <u>Example</u> :                    | IORWF R                                                                                                                                                                                                                                                                    | ESULT, 0, 1            | L                    |  |  |  |

| Before Instruction<br>RESULT = 0x13 |                                                                                                                                                                                                                                                                            |                        |                      |  |  |  |

| Delote instruction |     |      |  |  |

|--------------------|-----|------|--|--|

| RESULT             | =   | 0x13 |  |  |

| W                  | =   | 0x91 |  |  |

| After Instruct     | ion |      |  |  |

| DECULT             | _   | 0v12 |  |  |

| RESULT | = | 0x13 |

|--------|---|------|

| W      | = | 0x93 |