Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 34                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1.5K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf452t-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

This document contains device specific information for the following devices:

- PIC18F242 PIC18F442

- PIC18F252 PIC18F452

These devices come in 28-pin and 40/44-pin packages. The 28-pin devices do not have a Parallel Slave Port (PSP) implemented and the number of Analog-to-Digital (A/D) converter input channels is reduced to 5. An overview of features is shown in Table 1-1.

#### TABLE 1-1: DEVICE FEATURES

Features **PIC18F242 PIC18F252** PIC18F442 PIC18F452 Operating Frequency DC - 40 MHz DC - 40 MHz DC - 40 MHz DC - 40 MHz Program Memory (Bytes) 16K 32K 16K 32K 16384 8192 16384 Program Memory (Instructions) 8192 Data Memory (Bytes) 768 1536 768 1536 Data EEPROM Memory (Bytes) 256 256 256 256 Interrupt Sources 17 17 18 18 I/O Ports Ports A, B, C Ports A, B, C Ports A, B, C, D, E Ports A, B, C, D, E Timers 4 4 4 4 Capture/Compare/PWM Modules 2 2 2 2 MSSP. MSSP. MSSP. MSSP. Serial Communications Addressable Addressable Addressable Addressable USART USART USART USART Parallel Communications PSP PSP 10-bit Analog-to-Digital Module 5 input channels 5 input channels 8 input channels 8 input channels POR. BOR. POR. BOR. POR. BOR. POR. BOR. RESET Instruction. RESET Instruction. RESET Instruction. RESET Instruction. RESETS (and Delays) Stack Full, Stack Full, Stack Full, Stack Full, Stack Underflow Stack Underflow Stack Underflow Stack Underflow (PWRT, OST) (PWRT, OST) (PWRT, OST) (PWRT, OST) Programmable Low Voltage Yes Yes Yes Yes Detect Yes Yes Yes Yes Programmable Brown-out Reset Instruction Set 75 Instructions 75 Instructions 75 Instructions 75 Instructions 40-pin DIP 40-pin DIP 28-pin DIP 28-pin DIP 44-pin PLCC 44-pin PLCC Packages 28-pin SOIC 28-pin SOIC 44-pin TQFP 44-pin TQFP

The following two figures are device block diagrams sorted by pin count: 28-pin for Figure 1-1 and 40/44-pin for Figure 1-2. The 28-pin and 40/44-pin pinouts are listed in Table 1-2 and Table 1-3, respectively.

# TABLE 1-2: PIC18F2X2 PINOUT I/O DESCRIPTIONS (CONTINUED)

| Din Nome            | Pin N    | umber | Pin  | Buffer | Description                                                     |  |  |  |

|---------------------|----------|-------|------|--------|-----------------------------------------------------------------|--|--|--|

| Pin Name            | DIP SOIC |       | Туре | Туре   | Description                                                     |  |  |  |

|                     |          |       |      |        | PORTC is a bi-directional I/O port.                             |  |  |  |

| RC0/T1OSO/T1CKI     | 11       | 11    |      |        |                                                                 |  |  |  |

| RC0                 |          |       | I/O  | ST     | Digital I/O.                                                    |  |  |  |

| T1OSO               |          |       | 0    | _      | Timer1 oscillator output.                                       |  |  |  |

| T1CKI               |          |       | I.   | ST     | Timer1/Timer3 external clock input.                             |  |  |  |

| RC1/T1OSI/CCP2      | 12       | 12    |      |        |                                                                 |  |  |  |

| RC1                 |          |       | I/O  | ST     | Digital I/O.                                                    |  |  |  |

| T1OSI               |          |       | I.   | CMOS   | Timer1 oscillator input.                                        |  |  |  |

| CCP2                |          |       | I/O  | ST     | Capture2 input, Compare2 output, PWM2 output.                   |  |  |  |

| RC2/CCP1            | 13       | 13    |      |        |                                                                 |  |  |  |

| RC2                 |          |       | I/O  | ST     | Digital I/O.                                                    |  |  |  |

| CCP1                |          |       | I/O  | ST     | Capture1 input/Compare1 output/PWM1 output.                     |  |  |  |

| RC3/SCK/SCL         | 14       | 14    |      |        |                                                                 |  |  |  |

| RC3                 |          |       | I/O  | ST     | Digital I/O.                                                    |  |  |  |

| SCK                 |          |       | I/O  | ST     | Synchronous serial clock input/output for SPI mode.             |  |  |  |

| SCL                 |          |       | I/O  | ST     | Synchronous serial clock input/output for I <sup>2</sup> C mode |  |  |  |

| RC4/SDI/SDA         | 15       | 15    |      |        |                                                                 |  |  |  |

| RC4                 |          |       | I/O  | ST     | Digital I/O.                                                    |  |  |  |

| SDI                 |          |       | I.   | ST     | SPI Data In.                                                    |  |  |  |

| SDA                 |          |       | I/O  | ST     | I <sup>2</sup> C Data I/O.                                      |  |  |  |

| RC5/SDO             | 16       | 16    |      |        |                                                                 |  |  |  |

| RC5                 |          | _     | I/O  | ST     | Digital I/O.                                                    |  |  |  |

| SDO                 |          |       | 0    | _      | SPI Data Out.                                                   |  |  |  |

| RC6/TX/CK           | 17       | 17    |      |        |                                                                 |  |  |  |

| RC6                 |          | -     | I/O  | ST     | Digital I/O.                                                    |  |  |  |

| ТХ                  |          |       | 0    | _      | USART Asynchronous Transmit.                                    |  |  |  |

| СК                  |          |       | I/O  | ST     | USART Synchronous Clock (see related RX/DT).                    |  |  |  |

| RC7/RX/DT           | 18       | 18    |      |        |                                                                 |  |  |  |

| RC7                 |          |       | I/O  | ST     | Digital I/O.                                                    |  |  |  |

| RX                  |          |       | Ι    | ST     | USART Asynchronous Receive.                                     |  |  |  |

| DT                  |          |       | I/O  | ST     | USART Synchronous Data (see related TX/CK).                     |  |  |  |

| Vss                 | 8, 19    | 8, 19 | Р    | —      | Ground reference for logic and I/O pins.                        |  |  |  |

| Vdd                 | 20       | 20    | Р    |        | Positive supply for logic and I/O pins.                         |  |  |  |

| Legend: TTL = TTL o |          |       |      |        | CMOS = CMOS compatible input or output                          |  |  |  |

ST = Schmitt Trigger input with CMOS levels

I = Input P = Power

O = Output OD = Open Drain (no P diode to VDD)

NOTES:

## 13.2 Timer1 Oscillator

The Timer1 oscillator may be used as the clock source for Timer3. The Timer1 oscillator is enabled by setting the T1OSCEN (T1CON<3>) bit. The oscillator is a low power oscillator rated up to 200 KHz. See Section 11.0 for further details.

### 13.3 Timer3 Interrupt

The TMR3 Register pair (TMR3H:TMR3L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR3 Interrupt, if enabled, is generated on overflow, which is latched in interrupt flag bit, TMR3IF (PIR2<1>). This interrupt can be enabled/disabled by setting/clearing TMR3 interrupt enable bit, TMR3IE (PIE2<1>).

### 13.4 Resetting Timer3 Using a CCP Trigger Output

If the CCP module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer3.

| Note: | The special event triggers from the CCP |

|-------|-----------------------------------------|

|       | module will not set interrupt flag bit, |

|       | TMR3IF (PIR1<0>).                       |

Timer3 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer3 is running in Asynchronous Counter mode, this RESET operation may not work. In the event that a write to Timer3 coincides with a special event trigger from CCP1, the write will take precedence. In this mode of operation, the CCPR1H:CCPR1L registers pair effectively becomes the period register for Timer3.

| Name   | Bit 7                                                                      | Bit 6          | Bit 5        | Bit 4         | Bit 3         | Bit 2         | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |

|--------|----------------------------------------------------------------------------|----------------|--------------|---------------|---------------|---------------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE/<br>GIEH                                                               | PEIE/<br>GIEL  | TMR0IE       | INTOIE        | RBIE          | TMR0IF        | INTOIF | RBIF   | 0000 000x            | 0000 000u                       |

| PIR2   | —                                                                          | _              | _            | EEIF          | BCLIF         | LVDIF         | TMR3IF | CCP2IF | 0 0000               | 0 0000                          |

| PIE2   | —                                                                          | _              | _            | EEIE          | BCLIE         | LVDIE         | TMR3IE | CCP2IE | 0 0000               | 0 0000                          |

| IPR2   | _                                                                          | -              | -            | EEIP          | BCLIP         | LVDIP         | TMR3IP | CCP2IP | 1 1111               | 1 1111                          |

| TMR3L  | Holding F                                                                  | legister for t | he Least Sig | gnificant Byt | e of the 16-b | it TMR3 Re    | gister |        | xxxx xxxx            | uuuu uuuu                       |

| TMR3H  | Holding Register for the Most Significant Byte of the 16-bit TMR3 Register |                |              |               |               |               |        |        | xxxx xxxx            | uuuu uuuu                       |

| T1CON  | RD16                                                                       |                | T1CKPS1      | T1CKPS0       | T1OSCEN       | T1SYNC        | TMR1CS | TMR10N | 0-00 0000            | u-uu uuuu                       |

| T3CON  | RD16                                                                       | T3CCP2         | T3CKPS1      | T3CKPS0       | T3CCP1        | <b>T3SYNC</b> | TMR3CS | TMR3ON | 0000 0000            | uuuu uuuu                       |

#### TABLE 13-1: REGISTERS ASSOCIATED WITH TIMER3 AS A TIMER/COUNTER

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

# 14.0 CAPTURE/COMPARE/PWM (CCP) MODULES

Each CCP (Capture/Compare/PWM) module contains a 16-bit register which can operate as a 16-bit Capture register, as a 16-bit Compare register or as a PWM Master/Slave Duty Cycle register. Table 14-1 shows the timer resources of the CCP Module modes. The operation of CCP1 is identical to that of CCP2, with the exception of the special event trigger. Therefore, operation of a CCP module in the following sections is described with respect to CCP1.

Table 14-2 shows the interaction of the CCP modules.

### REGISTER 14-1: CCP1CON REGISTER/CCP2CON REGISTER

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-------|-------|--------|--------|--------|--------|

| —     | —   | DCxB1 | DCxB0 | CCPxM3 | CCPxM2 | CCPxM1 | CCPxM0 |

| bit 7 |     |       |       |        |        |        | bit 0  |

- bit 7-6 Unimplemented: Read as '0'

- bit 5-4 DCxB1:DCxB0: PWM Duty Cycle bit1 and bit0

Capture mode: Unused

Compare mode: Unused

PWM mode:

These bits are the two LSbs (bit1 and bit0) of the 10-bit PWM duty cycle. The upper eight bits (DCx9:DCx2) of the duty cycle are found in CCPRxL.

#### bit 3-0 CCPxM3:CCPxM0: CCPx Mode Select bits

- 0000 = Capture/Compare/PWM disabled (resets CCPx module)

- 0001 = Reserved

- 0010 = Compare mode, toggle output on match (CCPxIF bit is set)

- 0011 = Reserved

- 0100 = Capture mode, every falling edge

- 0101 = Capture mode, every rising edge

- 0110 = Capture mode, every 4th rising edge

- 0111 = Capture mode, every 16th rising edge

- 1000 = Compare mode,

Initialize CCP pin Low, on compare match force CCP pin High (CCPIF bit is set)

- 1001 = Compare mode,

- Initialize CCP pin High, on compare match force CCP pin Low (CCPIF bit is set)

- 1010 = Compare mode,

- Generate software interrupt on compare match (CCPIF bit is set, CCP pin is unaffected) 1011 = Compare mode,

- Trigger special event (CCPIF bit is set)

- 11xx = PWM mode

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# REGISTER 15-3: SSPSTAT: MSSP STATUS REGISTER (I<sup>2</sup>C MODE)

|       | R/W-0                                      | R/W-0                           | R-0                                             | R-0                          | R-0                              | R-0                        | R-0                        | R-0             |

|-------|--------------------------------------------|---------------------------------|-------------------------------------------------|------------------------------|----------------------------------|----------------------------|----------------------------|-----------------|

|       | SMP                                        | CKE                             |                                                 | P                            | s                                | R/W                        | UA                         | BF              |

|       | bit 7                                      | ONE                             | Birt                                            | •                            | Ű                                | 1011                       | 0/1                        | bit 0           |

|       |                                            |                                 |                                                 |                              |                                  |                            |                            |                 |

| oit 7 | In Master of                               | Rate Control                    |                                                 | Standard Cn                  | and made (                       |                            | 1 MU-)                     |                 |

|       |                                            |                                 | enabled for H                                   |                              |                                  |                            | i iviriz)                  |                 |

| oit 6 | In Master of                               | us Select bi<br>or Slave moo    | de:                                             |                              |                                  |                            |                            |                 |

|       |                                            | SMBus spe<br>SMBus spe          |                                                 |                              |                                  |                            |                            |                 |

| oit 5 | D/A: Data/                                 | Address bit                     |                                                 |                              |                                  |                            |                            |                 |

|       | <u>In Master r</u><br>Reserved             | <u>node:</u>                    |                                                 |                              |                                  |                            |                            |                 |

|       | In Slave m                                 | ode:                            |                                                 |                              |                                  |                            |                            |                 |

|       |                                            |                                 | ast byte rece<br>ast byte rece                  |                              |                                  |                            |                            |                 |

| bit 4 | <b>P:</b> STOP b                           |                                 | OP bit has b                                    | oon dotocto                  | d last                           |                            |                            |                 |

|       |                                            |                                 | letected last                                   |                              | u last                           |                            |                            |                 |

|       | Note:                                      | This bit is c                   | leared on RE                                    | SET and w                    | hen SSPEN                        | is cleared.                |                            |                 |

| oit 3 |                                            | es that a sta                   | rt bit has bee<br>detected las                  |                              | last                             |                            |                            |                 |

|       | Note:                                      | This bit is c                   | leared on RE                                    | SET and w                    | hen SSPEN                        | is cleared.                |                            |                 |

| oit 2 | R/W: Read                                  | I/Write bit Int                 | formation (I <sup>2</sup>                       | C mode only                  | /)                               |                            |                            |                 |

|       | <u>In Slave m</u><br>1 = Read<br>0 = Write | ode:                            |                                                 |                              |                                  |                            |                            |                 |

|       | Note:                                      |                                 | ls the R/W bi<br>ne address m                   |                              |                                  |                            |                            |                 |

|       | <u>In Master r</u><br>1 = Transm           | <u>node:</u><br>nit is in progi | ress                                            |                              |                                  |                            |                            |                 |

|       | 0 = Transm                                 | nit is not in p                 |                                                 |                              |                                  |                            |                            |                 |

|       | Note:                                      | ORing this I                    | bit with SEN,<br>de.                            | RSEN, PE                     | N, RCEN, o                       | r ACKEN wil                | l indicate if t            | he MSSP is      |

| bit 1 | 1 = Indicate                               | es that the u                   | 10-bit Slave r<br>ser needs to<br>need to be up | update the                   | address in t                     | he SSPADD                  | register                   |                 |

| bit 0 | BF: Buffer                                 | Full Status b                   | oit                                             |                              |                                  |                            |                            |                 |

|       |                                            | e complete,                     | SSPBUF is t<br>ete, SSPBUF                      |                              |                                  |                            |                            |                 |

|       | In Receive                                 | -                               | ,                                               | ie empty                     |                                  |                            |                            |                 |

|       | 1 = Data training 0 = Data training 1      | ansmit in pro<br>ansmit comp    | ogress (does<br>blete (does n                   | not include<br>ot include th | th <u>e ACK</u> ar<br>ne ACK and | d STOP bits<br>STOP bits), | ), SSPBUF i<br>SSPBUF is ( | s full<br>empty |

|       | Legend:                                    |                                 |                                                 |                              |                                  |                            |                            |                 |

|       | R = Reada                                  | ble bit                         | W = Writab                                      | le bit                       | U = Unimp                        | lemented bit               | , read as '0'              |                 |

|       | - n = Value                                | at POR                          | '1' = Bit is s                                  | et                           | '0' = Bit is                     | cleared                    | x = Bit is ur              | nknown          |

# TABLE 16-4: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0)

| BAUD           | Fosc = | 40 MHz  | SPBRG              | 33     | MHz    | SPBRG              | 25     | MHz    | SPBRG              | 20 1   | ИНz    | SPBRG              |

|----------------|--------|---------|--------------------|--------|--------|--------------------|--------|--------|--------------------|--------|--------|--------------------|

| RATE           |        | %       | value              |        | %      | value              |        | %      | value              |        | %      | value              |

| (Kbps)         | KBAUD  | ERROR   | (decimal)          | KBAUD  | ERROR  | (decimal)          | KBAUD  | ERROR  | (decimal)          | KBAUD  | ERROR  | (decimal)          |

| 0.3            | NA     | -       | -                  | NA     | -      | -                  | NA     | -      | -                  | NA     | -      | -                  |

| 1.2            | NA     | -       | -                  | NA     | -      | -                  | NA     | -      | -                  | NA     | -      | -                  |

| 2.4            | NA     | -       | -                  | 2.40   | -0.07  | 214                | 2.40   | -0.15  | 162                | 2.40   | +0.16  | 129                |

| 9.6            | 9.62   | +0.16   | 64                 | 9.55   | -0.54  | 53                 | 9.53   | -0.76  | 40                 | 9.47   | -1.36  | 32                 |

| 19.2           | 18.94  | -1.36   | 32                 | 19.10  | -0.54  | 26                 | 19.53  | +1.73  | 19                 | 19.53  | +1.73  | 15                 |

| 76.8           | 78.13  | +1.73   | 7                  | 73.66  | -4.09  | 6                  | 78.13  | +1.73  | 4                  | 78.13  | +1.73  | 3                  |

| 96             | 89.29  | -6.99   | 6                  | 103.13 | +7.42  | 4                  | 97.66  | +1.73  | 3                  | 104.17 | +8.51  | 2                  |

| 300            | 312.50 | +4.17   | 1                  | 257.81 | -14.06 | 1                  | NA     | -      | -                  | 312.50 | +4.17  | 0                  |

| 500            | 625    | +25.00  | 0                  | NA     | -      | -                  | NA     | -      | -                  | NA     | -      | -                  |

| HIGH           | 625    | -       | 0                  | 515.63 | -      | 0                  | 390.63 | -      | 0                  | 312.50 | -      | 0                  |

| LOW            | 2.44   | -       | 255                | 2.01   | -      | 255                | 1.53   | -      | 255                | 1.22   | -      | 255                |

|                | _      |         |                    |        |        |                    |        |        |                    |        |        |                    |

| BAUD           | FOSC = | 16 MHz  | SPBRG              | 101    | MHz    | SPBRG              | 7.1590 | 9 MHz  | SPBRG              | 5.068  | 5 MHZ  | SPBRG              |

| RATE<br>(Kbps) |        | %       | value<br>(decimal) |        | %      | value<br>(decimal) |        | %      | value<br>(decimal) |        | %      | value<br>(decimal) |

| (1000)         | KBAUD  | ERROR   | (uconnai)          | KBAUD  | ERROR  | (uconnul)          | KBAUD  | ERROR  | (uconnul)          | KBAUD  | ERROR  | (uconnui)          |

| 0.3            | NA     | -       | -                  | NA     | -      | -                  | NA     | -      | -                  | NA     | -      | -                  |

| 1.2            | 1.20   | +0.16   | 207                | 1.20   | +0.16  | 129                | 1.20   | +0.23  | 92                 | 1.20   | 0      | 65                 |

| 2.4            | 2.40   | +0.16   | 103                | 2.40   | +0.16  | 64                 | 2.38   | -0.83  | 46                 | 2.40   | 0      | 32                 |

| 9.6            | 9.62   | +0.16   | 25                 | 9.77   | +1.73  | 15                 | 9.32   | -2.90  | 11                 | 9.90   | +3.13  | 7                  |

| 19.2           | 19.23  | +0.16   | 12                 | 19.53  | +1.73  | 7                  | 18.64  | -2.90  | 5                  | 19.80  | +3.13  | 3                  |

| 76.8           | 83.33  | +8.51   | 2                  | 78.13  | +1.73  | 1                  | 111.86 | +45.65 | 0                  | 79.20  | +3.13  | 0                  |

| 96             | 83.33  | -13.19  | 2                  | 78.13  | -18.62 | 1                  | NA     | -      | -                  | NA     | -      | -                  |

| 300            | 250    | -16.67  | 0                  | 156.25 | -47.92 | 0                  | NA     | -      | -                  | NA     | -      | -                  |

| 500            | NA     | -       | -                  | NA     | -      | -                  | NA     | -      | -                  | NA     | -      | -                  |

| HIGH           | 250    | -       | 0                  | 156.25 | -      | 0                  | 111.86 | -      | 0                  | 79.20  | -      | 0                  |

| LOW            | 0.98   | -       | 255                | 0.61   | -      | 255                | 0.44   | -      | 255                | 0.31   | -      | 255                |

| BAUD           | Fosc : | = 4 MHz | SPBRG              | 3.5795 | 45 MHz | SPBRG              | 11     | MHz    | SPBRG              | 32.76  | 8 kHz  | SPBRG              |

| RATE           |        | %       | value              |        | %      | value              |        | %      | value              |        | %      | value              |

| (Kbps)         | KBAUD  | ERROR   | (decimal)          | KBAUD  | ERROR  | (decimal)          | KBAUD  | ERROR  | (decimal)          | KBAUD  | ERROR  | (decimal)          |

| 0.3            | 0.30   | -0.16   | 207                | 0.30   | +0.23  | 185                | 0.30   | +0.16  | 51                 | 0.26   | -14.67 | 1                  |

| 1.2            | 1.20   | +1.67   | 51                 | 1.19   | -0.83  | 46                 | 1.20   | +0.16  | 12                 | NA     | -      | -                  |

| 2.4            | 2.40   | +1.67   | 25                 | 2.43   | +1.32  | 22                 | 2.23   | -6.99  | 6                  | NA     | -      | -                  |

| 9.6            | 8.93   | -6.99   | 6                  | 9.32   | -2.90  | 5                  | 7.81   | -18.62 | 1                  | NA     | -      | -                  |

| 19.2           | 20.83  | +8.51   | 2                  | 18.64  | -2.90  | 2                  | 15.63  | -18.62 | 0                  | NA     | -      | -                  |

| 76.8           | 62.50  | -18.62  | 0                  | 55.93  | -27.17 | 0                  | NA     | -      | -                  | NA     | -      | -                  |

| 96             | NA     | -       | -                  | NA     | -      | -                  | NA     | -      | -                  | NA     | -      | -                  |

| 300            | NA     | -       | -                  | NA     | -      | -                  | NA     | -      | -                  | NA     | -      | -                  |

| 500            | NA     | -       | -                  | NA     | -      | -                  | NA     | -      | -                  | NA     | -      | -                  |

| HIGH           | 62.50  | -       | 0                  | 55.93  | -      | 0                  | 15.63  | -      | 0                  | 0.51   | -      | 0                  |

| LOW            | 0.24   | -       | 255                | 0.22   | -      | 255                | 0.06   | -      | 255                | 0.002  | -      | 255                |

# 16.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical, except in the case of the SLEEP mode and bit SREN, which is a "don't care" in Slave mode.

If receive is enabled by setting bit CREN prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR register will transfer the data to the RCREG register, and if enable bit RCIE bit is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector.

To set up a Synchronous Slave Reception:

- Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, set enable bit RCIE.

- 3. If 9-bit reception is desired, set bit RX9.

- 4. To enable reception, set enable bit CREN.

- 5. Flag bit RCIF will be set when reception is complete. An interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit CREN.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| Name   | Bit 7                        | Bit 6         | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0     | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |

|--------|------------------------------|---------------|--------|--------|-------|--------|--------|-----------|----------------------|---------------------------------|

| INTCON | GIE/<br>GIEH                 | PEIE/<br>GIEL | TMR0IE | INTOIE | RBIE  | TMR0IF | INTOIF | RBIF      | 0000 000x            | 0000 000u                       |

| PIR1   | PSPIF <sup>(1)</sup>         | ADIF          | RCIF   | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF    | 0000 0000            | 0000 0000                       |

| PIE1   | PSPIE <sup>(1)</sup>         | ADIE          | RCIE   | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE    | 0000 0000            | 0000 0000                       |

| IPR1   | PSPIP <sup>(1)</sup>         | ADIP          | RCIP   | TXIP   | SSPIP | CCP1IP | TMR2IP | TMR1IP    | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN                         | RX9           | SREN   | CREN   | ADDEN | FERR   | OERR   | RX9D      | 0000 -00x            | 0000 -00x                       |

| RCREG  | USART Receive Register       |               |        |        |       |        |        | 0000 0000 | 0000 0000            |                                 |

| TXSTA  | CSRC                         | TX9           | TXEN   | SYNC   | _     | BRGH   | TRMT   | TX9D      | 0000 -010            | 0000 -010                       |

| SPBRG  | Baud Rate Generator Register |               |        |        |       |        |        |           | 0000 0000            | 0000 0000                       |

#### TABLE 16-11: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: x = unknown, - = unimplemented, read as '0'.

Shaded cells are not used for Synchronous Slave Reception.

Note 1: The PSPIF, PSPIE and PSPIP bits are reserved on the PIC18F2X2 devices; always maintain these bits clear.

To calculate the minimum acquisition time, Equation 17-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

#### EQUATION 17-1: ACQUISITION TIME

| TACQ | = | Amplifier Settling Time + Holding Capacitor Charging Time + Temperature Coefficient |

|------|---|-------------------------------------------------------------------------------------|

|      | = | TAMP + TC + TCOFF                                                                   |

### EQUATION 17-2: A/D MINIMUM CHARGING TIME

Example 17-1 shows the calculation of the minimum required acquisition time, TACQ. This calculation is based on the following application system assumptions:

| CHOLD | = | 120 pF |

|-------|---|--------|

| -     |   | 0.510  |

- Rs =  $2.5 \text{ k}\Omega$

- Conversion Error ≤ 1/2 LSb

- VDD =  $5V \rightarrow Rss = 7 k\Omega$

- Temperature =  $50^{\circ}$ C (system max.)

- VHOLD = 0V @ time = 0

#### EXAMPLE 17-1: CALCULATING THE MINIMUM REQUIRED ACQUISITION TIME

| TACQ =    | TAMP + TC + TCOFF                                                                                                                                                                                 |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Temperatu | re coefficient is only required for temperatures $> 25^{\circ}$ C.                                                                                                                                |

| TACQ =    | $2 \ \mu s + Tc + [(Temp - 25^{\circ}C)(0.05 \ \mu s/^{\circ}C)]$                                                                                                                                 |

| TC =      | -Chold (Ric + Rss + Rs) $\ln(1/2048)$<br>-120 pF (1 k $\Omega$ + 7 k $\Omega$ + 2.5 k $\Omega$ ) $\ln(0.0004883)$<br>-120 pF (10.5 k $\Omega$ ) $\ln(0.0004883)$<br>-1.26 µs (-7.6246)<br>9.61 µs |

| TACQ =    | 2 μs + 9.61 μs + [(50°C – 25°C)(0.05 μs/°C)]<br>11.61 μs + 1.25 μs<br>12.86 μs                                                                                                                    |

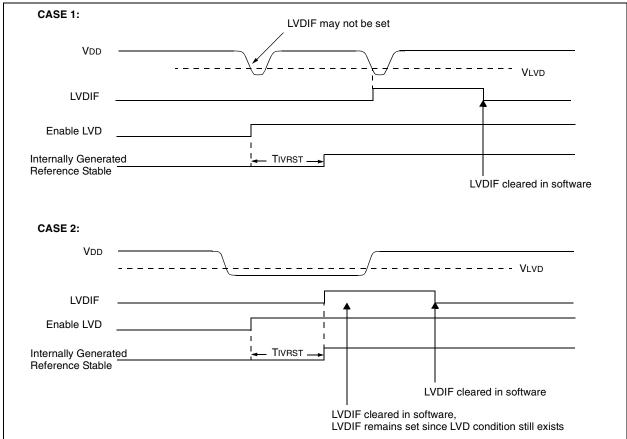

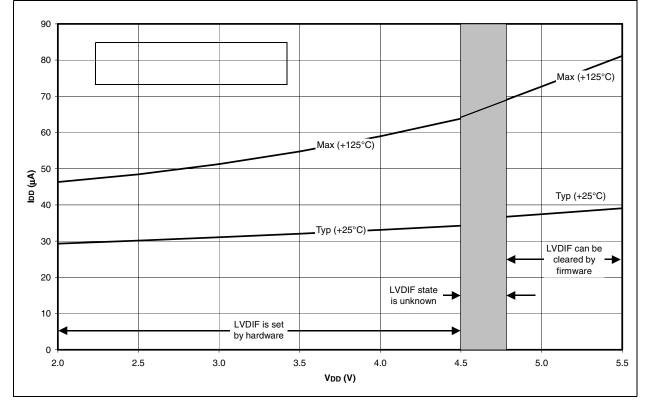

### 18.2 Operation

Depending on the power source for the device voltage, the voltage normally decreases relatively slowly. This means that the LVD module does not need to be constantly operating. To decrease the current requirements, the LVD circuitry only needs to be enabled for short periods, where the voltage is checked. After doing the check, the LVD module may be disabled.

Each time that the LVD module is enabled, the circuitry requires some time to stabilize. After the circuitry has stabilized, all status flags may be cleared. The module will then indicate the proper state of the system.

The following steps are needed to set up the LVD module:

- Write the value to the LVDL3:LVDL0 bits (LVDCON register), which selects the desired LVD Trip Point.

- 2. Ensure that LVD interrupts are disabled (the LVDIE bit is cleared or the GIE bit is cleared).

- 3. Enable the LVD module (set the LVDEN bit in the LVDCON register).

- 4. Wait for the LVD module to stabilize (the IRVST bit to become set).

- 5. Clear the LVD interrupt flag, which may have falsely become set until the LVD module has stabilized (clear the LVDIF bit).

- 6. Enable the LVD interrupt (set the LVDIE and the GIE bits).

Figure 18-4 shows typical waveforms that the LVD module may be used to detect.

#### FIGURE 18-4: LOW VOLTAGE DETECT WAVEFORMS

NOTES:

| TABLE 19-1: | CONFIGURATION BITS AND DEVICE IDS |

|-------------|-----------------------------------|

|-------------|-----------------------------------|

| File    | Name     | Bit 7 | Bit 6 | Bit 5  | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Default/<br>Unprogrammed<br>Value |

|---------|----------|-------|-------|--------|-------|--------|--------|--------|--------|-----------------------------------|

| 300001h | CONFIG1H | _     | _     | OSCSEN | _     | _      | FOSC2  | FOSC1  | FOSC0  | 1111                              |

| 300002h | CONFIG2L | _     | _     | _      | _     | BORV1  | BORV0  | BOREN  | PWRTEN | 1111                              |

| 300003h | CONFIG2H | _     |       | _      |       | WDTPS2 | WDTPS1 | WDTPS0 | WDTEN  | 1111                              |

| 300005h | CONFIG3H | —     | _     | _      | _     | _      | _      | _      | CCP2MX | 1                                 |

| 300006h | CONFIG4L | DEBUG | _     | _      | _     | _      | LVP    | _      | STVREN | 11-1                              |

| 300008h | CONFIG5L | _     | _     | _      | _     | CP3    | CP2    | CP1    | CP0    | 1111                              |

| 300009h | CONFIG5H | CPD   | CPB   | —      | -     | -      | -      | -      | —      | 11                                |

| 30000Ah | CONFIG6L | _     | _     | _      | _     | WRT3   | WRT2   | WRT1   | WRT0   | 1111                              |

| 30000Bh | CONFIG6H | WRTD  | WRTB  | WRTC   | _     | _      | _      | _      | _      | 111                               |

| 30000Ch | CONFIG7L | _     | _     | _      | _     | EBTR3  | EBTR2  | EBTR1  | EBTR0  | 1111                              |

| 30000Dh | CONFIG7H | _     | EBTRB | —      | _     | _      | _      | _      | —      | -1                                |

| 3FFFFEh | DEVID1   | DEV2  | DEV1  | DEV0   | REV4  | REV3   | REV2   | REV1   | REV0   | (1)                               |

| 3FFFFFh | DEVID2   | DEV10 | DEV9  | DEV8   | DEV7  | DEV6   | DEV5   | DEV4   | DEV3   | 0000 0100                         |

$\label{eq:Legend: x = unknown, u = unchanged, - = unimplemented, q = value depends on condition. \\ Shaded cells are unimplemented, read as '0'.$

Note 1: See Register 19-12 for DEVID1 values.

#### REGISTER 19-1: CONFIGURATION REGISTER 1 HIGH (CONFIG1H: BYTE ADDRESS 300001h)

| U-0   | U-0 | R/P-1  | U-0 | U-0 | R/P-1 | R/P-1 | R/P-1 |

|-------|-----|--------|-----|-----|-------|-------|-------|

| _     | —   | OSCSEN | _   | —   | FOSC2 | FOSC1 | FOSC0 |

| bit 7 |     |        |     |     |       |       | bit 0 |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| bit 5   | OSCSEN: Oscillator System Clock Switch Enable bit                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|         | <ul> <li>1 = Oscillator system clock switch option is disabled (main oscillator is source)</li> <li>0 = Oscillator system clock switch option is enabled (oscillator switching is enabled)</li> </ul>                                                                                                            |  |  |  |  |  |  |  |

| bit 4-3 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| bit 2-0 | FOSC2:FOSC0: Oscillator Selection bits                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

|         | 111 = RC oscillator w/ OSC2 configured as RA6 110 = HS oscillator with PLL enabled/Clock frequency = (4 x Fosc) 101 = EC oscillator w/ OSC2 configured as RA6 100 = EC oscillator w/ OSC2 configured as divide-by-4 clock output 011 = RC oscillator 010 = HS oscillator 001 = XT oscillator 000 = LP oscillator |  |  |  |  |  |  |  |

|         | Legend:                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

|         | R = Readable bit $P$ = Programmable bit $U$ = Unimplemented bit, read as '0'                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| MULLW                                | Multiply I                                                                                                         | Literal with                                                          | N                                                                         | М         | JLWF                                                                                                                                                                                                                                                                                                                                                                | Multiply \           | N with f                      |                                                                                                                   |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Syntax:                              | [ label ]                                                                                                          | MULLW k                                                               |                                                                           | Sy        | ntax:                                                                                                                                                                                                                                                                                                                                                               | [ label ]            | MULWF f                       | [,a]                                                                                                              |

| Operands:                            | $0 \le k \le 25$                                                                                                   | 5                                                                     |                                                                           | Op        | erands:                                                                                                                                                                                                                                                                                                                                                             | $0 \le f \le 258$    | 5                             |                                                                                                                   |

| Operation:                           | (W) x k $\rightarrow$                                                                                              | PRODH:PF                                                              | ODL                                                                       |           |                                                                                                                                                                                                                                                                                                                                                                     | a ∈ [0,1]            |                               |                                                                                                                   |

| Status Affected:                     | None                                                                                                               |                                                                       |                                                                           | Op        | eration:                                                                                                                                                                                                                                                                                                                                                            | (W) x (f) –          | → PRODH:P                     | RODL                                                                                                              |

| Encoding:                            | 0000                                                                                                               | 1101 kk                                                               | kk kkkk                                                                   | Sta       | tus Affected:                                                                                                                                                                                                                                                                                                                                                       | None                 |                               |                                                                                                                   |

| Description:                         | An unsign                                                                                                          | ed multiplica                                                         | tion is car-                                                              | En        | coding:                                                                                                                                                                                                                                                                                                                                                             | 0000                 | 001a fff                      | ff ffff                                                                                                           |

|                                      | W and the<br>16-bit rest<br>PRODH:F<br>PRODH c<br>W is unch<br>None of th<br>affected.<br>Note that<br>carry is po | ne status flag<br>neither overf<br>ossible in this<br>ro result is po | k'. The<br>in<br>ter pair.<br>high byte.<br>Is are<br>low nor<br>s opera- | De        | escription: An unsigned multiplication<br>ried out between the conte<br>W and the register file loca<br>The 16-bit result is stored<br>PRODH:PRODL register p<br>PRODH contains the high<br>Both W and 'f' are unchany<br>None of the status flags ar<br>affected.<br>Note that neither overflow<br>carry is possible in this op<br>tion. A zero result is possible |                      |                               | ontents of<br>location 'f'.<br>red in the<br>ter pair.<br>high byte.<br>hanged.<br>gs are<br>flow nor<br>s opera- |

| Words:                               | 1                                                                                                                  |                                                                       |                                                                           |           |                                                                                                                                                                                                                                                                                                                                                                     |                      | ed. If 'a' is 0               | <i>,</i>                                                                                                          |

| Cycles:                              | 1                                                                                                                  |                                                                       |                                                                           |           |                                                                                                                                                                                                                                                                                                                                                                     |                      | ank will be se<br>the BSR val | ,                                                                                                                 |

| Q Cycle Activity:                    |                                                                                                                    |                                                                       |                                                                           |           |                                                                                                                                                                                                                                                                                                                                                                     |                      | en the bank v                 |                                                                                                                   |

| Q1                                   | Q2                                                                                                                 | Q3                                                                    | Q4                                                                        |           |                                                                                                                                                                                                                                                                                                                                                                     |                      | as per the BS                 | SR value                                                                                                          |

| Decode                               | Read                                                                                                               | Process                                                               | Write                                                                     |           |                                                                                                                                                                                                                                                                                                                                                                     | (default).           |                               |                                                                                                                   |

|                                      | literal 'k'                                                                                                        | Data                                                                  | registers<br>PRODH:                                                       |           | ords:                                                                                                                                                                                                                                                                                                                                                               | 1                    |                               |                                                                                                                   |

|                                      |                                                                                                                    |                                                                       | PRODL                                                                     | -         | cles:                                                                                                                                                                                                                                                                                                                                                               | 1                    |                               |                                                                                                                   |

|                                      |                                                                                                                    |                                                                       |                                                                           | Q         | Cycle Activity                                                                                                                                                                                                                                                                                                                                                      |                      | 0.0                           | <b>.</b>                                                                                                          |

| Example:                             | MULLW                                                                                                              | 0xC4                                                                  |                                                                           |           | Q1                                                                                                                                                                                                                                                                                                                                                                  | Q2                   | Q3                            | Q4                                                                                                                |

| Before Instru<br>W<br>PRODH<br>PRODL |                                                                                                                    | E2                                                                    |                                                                           |           | Decode                                                                                                                                                                                                                                                                                                                                                              | Read<br>register 'f' | Process<br>Data               | Write<br>registers<br>PRODH:<br>PRODL                                                                             |

| After Instruct                       | =                                                                                                                  |                                                                       |                                                                           |           |                                                                                                                                                                                                                                                                                                                                                                     |                      |                               |                                                                                                                   |

| W                                    | = 0x                                                                                                               | E2                                                                    |                                                                           | <u>Ex</u> | ample:                                                                                                                                                                                                                                                                                                                                                              | MULWF                | REG, 1                        |                                                                                                                   |

| PRODH<br>PRODL                       |                                                                                                                    | AD<br>08                                                              |                                                                           |           | Before Instr<br>W<br>REG<br>PRODH<br>PRODL                                                                                                                                                                                                                                                                                                                          | = 0x<br>= 0x         | C4<br>B5                      |                                                                                                                   |

|                                      |                                                                                                                    |                                                                       |                                                                           |           | After Instruc                                                                                                                                                                                                                                                                                                                                                       | •                    |                               |                                                                                                                   |

|                                      |                                                                                                                    |                                                                       |                                                                           |           |                                                                                                                                                                                                                                                                                                                                                                     |                      | <b>.</b>                      |                                                                                                                   |

| ner instruction |   |      |

|-----------------|---|------|

| W               | = | 0xC4 |

| REG             | = | 0xB5 |

| PRODH           | = | 0x8A |

| PRODL           | = | 0x94 |

| XORWF Exclusive OR W with f                                                                                                                                                                                                                                                                                                                        |                                                     |                        |      |                       |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------------|------|-----------------------|--|--|--|

| Syntax: [label] XORWF f[,d[,a]                                                                                                                                                                                                                                                                                                                     |                                                     |                        |      |                       |  |  |  |

| Operands:                                                                                                                                                                                                                                                                                                                                          | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$ | 5                      |      |                       |  |  |  |

| Operation:                                                                                                                                                                                                                                                                                                                                         | (W) .XOR                                            | . (f) $\rightarrow$ de | st   |                       |  |  |  |

| Status Affected                                                                                                                                                                                                                                                                                                                                    | l: N, Z                                             |                        |      |                       |  |  |  |

| Encoding:                                                                                                                                                                                                                                                                                                                                          | 0001                                                | 10da                   | ffff | ffff                  |  |  |  |

| Description: Exclusive OR the contents of W<br>with register 'f'. If 'd' is 0, the resu<br>is stored in W. If 'd' is 1, the resu<br>stored back in the register 'f'<br>(default). If 'a' is 0, the Access<br>Bank will be selected, overriding<br>the BSR value. If 'a' is 1, then the<br>bank will be selected as per the<br>BSR value (default). |                                                     |                        |      |                       |  |  |  |

| Words:                                                                                                                                                                                                                                                                                                                                             | 1                                                   |                        |      |                       |  |  |  |

| Cycles:                                                                                                                                                                                                                                                                                                                                            | 1                                                   |                        |      |                       |  |  |  |

| Q Cycle Activi                                                                                                                                                                                                                                                                                                                                     | ty:                                                 |                        |      |                       |  |  |  |

| Q1                                                                                                                                                                                                                                                                                                                                                 | Q2                                                  | Q3                     |      | Q4                    |  |  |  |

| Decode                                                                                                                                                                                                                                                                                                                                             | Read<br>register 'f'                                | Proces<br>Data         |      | /rite to<br>stination |  |  |  |

| Example: XORWF REG, 1, 0                                                                                                                                                                                                                                                                                                                           |                                                     |                        |      |                       |  |  |  |

| Before Ins<br>REG<br>W                                                                                                                                                                                                                                                                                                                             | truction<br>= 0xAF<br>= 0xB5                        |                        |      |                       |  |  |  |

| After Instru<br>REG<br>W                                                                                                                                                                                                                                                                                                                           | uction<br>= 0x1A<br>= 0xB5                          |                        |      |                       |  |  |  |

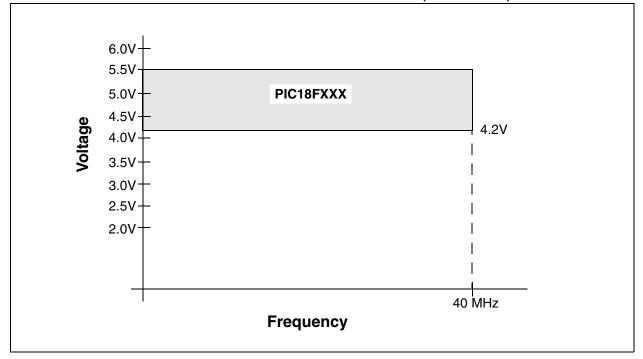

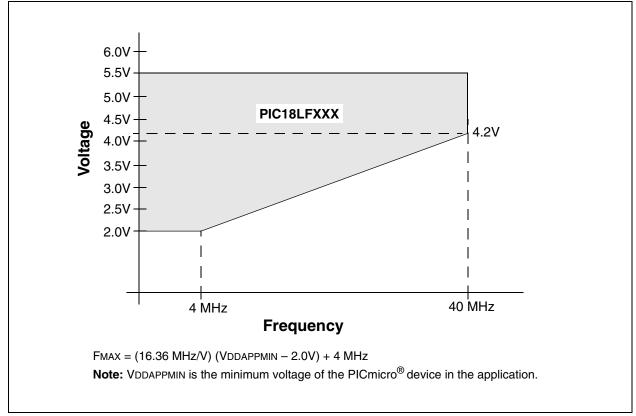

FIGURE 22-2: PIC18LFXX2 VOLTAGE-FREQUENCY GRAPH (INDUSTRIAL)

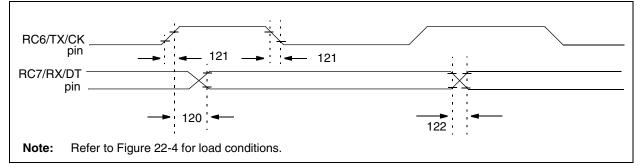

#### FIGURE 22-20: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

### TABLE 22-19: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param.<br>No. | Symbol        | Characteristic                                                        | Min                 | Max | Units | Conditions |          |

|---------------|---------------|-----------------------------------------------------------------------|---------------------|-----|-------|------------|----------|

| 120           | TckH2dtV      | <u>SYNC XMIT (MASTER &amp; SLAVE)</u><br>Clock high to data out valid | PIC18 <b>F</b> XXX  | _   | 50    | ns         |          |

|               |               |                                                                       | PIC18LFXXX          |     | 150   | ns         | VDD = 2V |

| 121           | Tckr          | Clock out rise time and fall time                                     | PIC18FXXX           | _   | 25    | ns         |          |

|               | (Master mode) |                                                                       | PIC18LFXXX          | —   | 60    | ns         | VDD = 2V |

| 122           | Tdtr          | Data out rise time and fall time                                      | PIC18FXXX           |     | 25    | ns         |          |

|               |               |                                                                       | PIC18 <b>LF</b> XXX |     | 60    | ns         | VDD = 2V |

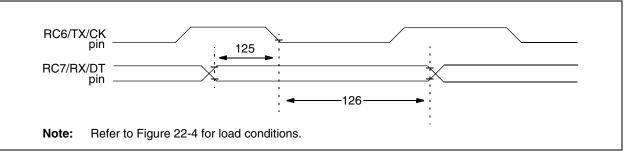

#### FIGURE 22-21: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

## TABLE 22-20: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Param.<br>No. | Symbol   | Characteristic                                                                          | Min        | Max | Units | Conditions |          |

|---------------|----------|-----------------------------------------------------------------------------------------|------------|-----|-------|------------|----------|

| 125           | TdtV2ckl | <u>SYNC RCV (MASTER &amp; SLAVE)</u><br>Data hold before CK $\downarrow$ (DT hold time) | 10         |     | ns    |            |          |

| 126           | TckL2dtl | Data hold after CK $\downarrow$ (DT hold time)                                          | PIC18FXXX  | 15  |       | ns         |          |

|               |          |                                                                                         | PIC18LFXXX | 20  |       | ns         | VDD = 2V |

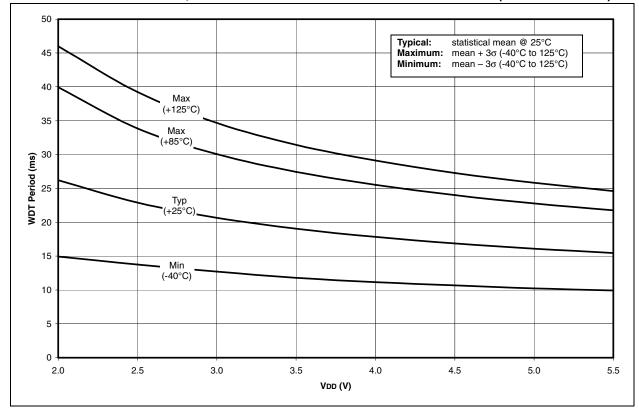

#### FIGURE 23-19: TYPICAL, MINIMUM AND MAXIMUM WDT PERIOD vs. VDD (-40°C TO +125°C)

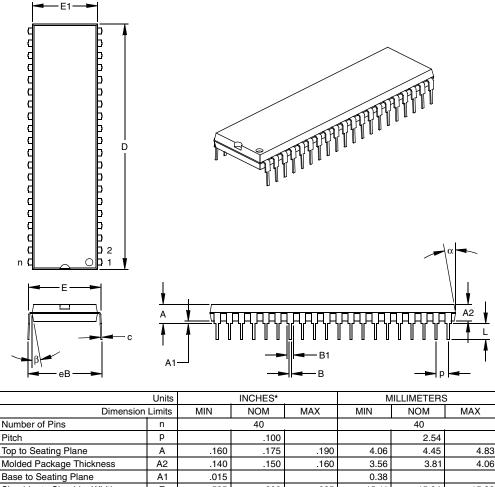

# 40-Lead Plastic Dual In-line (P) – 600 mil Body (PDIP)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Molded Package Thickness   | A2 | .140  | .150  | .160  | 3.56  | 3.81  | 4.06  |

|----------------------------|----|-------|-------|-------|-------|-------|-------|

| Base to Seating Plane      | A1 | .015  |       |       | 0.38  |       |       |

| Shoulder to Shoulder Width | E  | .595  | .600  | .625  | 15.11 | 15.24 | 15.88 |

| Molded Package Width       | E1 | .530  | .545  | .560  | 13.46 | 13.84 | 14.22 |

| Overall Length             | D  | 2.045 | 2.058 | 2.065 | 51.94 | 52.26 | 52.45 |

| Tip to Seating Plane       | L  | .120  | .130  | .135  | 3.05  | 3.30  | 3.43  |

| Lead Thickness             | С  | .008  | .012  | .015  | 0.20  | 0.29  | 0.38  |

| Upper Lead Width           | B1 | .030  | .050  | .070  | 0.76  | 1.27  | 1.78  |

| Lower Lead Width           | В  | .014  | .018  | .022  | 0.36  | 0.46  | 0.56  |

| Overall Row Spacing §      | eB | .620  | .650  | .680  | 15.75 | 16.51 | 17.27 |