Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 34                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1.5K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf452t-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name          | Pin Number |          | Pin  | Buffer    | Description                                                                                                    |

|-------------------|------------|----------|------|-----------|----------------------------------------------------------------------------------------------------------------|

| Pin Name          | DIP        | SOIC     | Туре | Туре      | Description                                                                                                    |

|                   |            |          |      |           | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-ups on all inputs. |

| RB0/INT0          | 21         | 21       |      |           |                                                                                                                |

| RB0               |            |          | I/O  | TTL       | Digital I/O.                                                                                                   |

| INT0              |            |          | I    | ST        | External Interrupt 0.                                                                                          |

| RB1/INT1          | 22         | 22       |      |           |                                                                                                                |

| RB1               |            |          | I/O  | TTL       | <b>_</b>                                                                                                       |

| INT1              |            |          | I    | ST        | External Interrupt 1.                                                                                          |

| RB2/INT2          | 23         | 23       |      |           |                                                                                                                |

| RB2<br>INT2       |            |          | I/O  | TTL<br>ST | Digital I/O.                                                                                                   |

|                   |            |          | I    | 51        | External Interrupt 2.                                                                                          |

| RB3/CCP2<br>RB3   | 24         | 24       | I/O  | TTL       | Digital I/O.                                                                                                   |

| CCP2              |            |          | 1/O  | ST        | Capture2 input, Compare2 output, PWM2 output.                                                                  |

| RB4               | 25         | 25       | 1/O  | TTL       | Digital I/O.                                                                                                   |

| ND4               | 25         | 25       | 1/0  | 116       | Interrupt-on-change pin.                                                                                       |

| RB5/PGM           | 26         | 26       |      |           |                                                                                                                |

| RB5               | 20         | 20       | I/O  | TTL       | Digital I/O. Interrupt-on-change pin.                                                                          |

| PGM               |            |          | I/O  | ST        | Low Voltage ICSP programming enable pin.                                                                       |

| RB6/PGC           | 27         | 27       |      |           |                                                                                                                |

| RB6               |            |          | I/O  | TTL       | Digital I/O. Interrupt-on-change pin.                                                                          |

| PGC               |            |          | I/O  | ST        | In-Circuit Debugger and ICSP programming clock pin.                                                            |

| RB7/PGD           | 28         | 28       |      |           |                                                                                                                |

| RB7               |            |          | I/O  | TTL       | Digital I/O. Interrupt-on-change pin.                                                                          |

| PGD               |            |          | I/O  | ST        | In-Circuit Debugger and ICSP programming data pin.                                                             |

| Legend: TTL = TTL | compati    | ble inpu | t    |           | CMOS = CMOS compatible input or output                                                                         |

| TABLE 1-2:PIC18F2X2 PINOUT | O DESCRIPTIONS (CONTINUED) |

|----------------------------|----------------------------|

|----------------------------|----------------------------|

ST = Schmitt Trigger input with CMOS levels O = Output

OD = Open Drain (no P diode to VDD)

I = Input P = Power

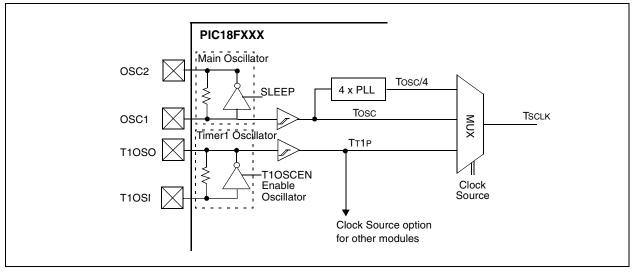

# 2.6 Oscillator Switching Feature

The PIC18FXX2 devices include a feature that allows the system clock source to be switched from the main oscillator to an alternate low frequency clock source. For the PIC18FXX2 devices, this alternate clock source is the Timer1 oscillator. If a low frequency crystal (32 kHz, for example) has been attached to the Timer1 oscillator pins and the Timer1 oscillator has been enabled, the device can switch to a Low Power Execution mode. Figure 2-7 shows a block diagram of the system clock sources. The clock switching feature is enabled <u>by programming the Oscillator Switching</u> Enable (OSCSEN) bit in Configuration Register1H to a '0'. Clock switching is disabled in an erased device. See Section 11.0 for further details of the Timer1 oscillator. See Section 19.0 for Configuration Register details.

### FIGURE 2-7: DEVICE CLOCK SOURCES

# PIC18FXX2

|          |                           |     |        |                   |                                    | MCLR Resets                                    |                                 |  |

|----------|---------------------------|-----|--------|-------------------|------------------------------------|------------------------------------------------|---------------------------------|--|

| Register | Applicable Devices        |     |        |                   | Power-on Reset,<br>Brown-out Reset | WDT Reset<br>RESET Instruction<br>Stack Resets | Wake-up via WDT<br>or Interrupt |  |

| TOSU     | OSU 242 442 252 4520 0000 |     | 0 0000 | 0 uuuu <b>(3)</b> |                                    |                                                |                                 |  |

| TOSH     | 242                       | 442 | 252    | 452               | 0000 0000                          | 0000 0000                                      | uuuu uuuu <sup>(3)</sup>        |  |

| TOSL     | 242                       | 442 | 252    | 452               | 0000 0000                          | 0000 0000                                      | uuuu uuuu <b>(3)</b>            |  |

| STKPTR   | 242                       | 442 | 252    | 452               | 00-0 0000                          | uu-0 0000                                      | uu-u uuuu <b>(3)</b>            |  |

| PCLATU   | 242                       | 442 | 252    | 452               | 0 0000                             | 0 0000                                         | u uuuu                          |  |

| PCLATH   | 242                       | 442 | 252    | 452               | 0000 0000                          | 0000 0000                                      | uuuu uuuu                       |  |

| PCL      | 242                       | 442 | 252    | 452               | 0000 0000                          | 0000 0000                                      | PC + 2 <sup>(2)</sup>           |  |

| TBLPTRU  | 242                       | 442 | 252    | 452               | 00 0000                            | 00 0000                                        | uu uuuu                         |  |

| TBLPTRH  | 242                       | 442 | 252    | 452               | 0000 0000                          | 0000 0000                                      | uuuu uuuu                       |  |

| TBLPTRL  | 242                       | 442 | 252    | 452               | 0000 0000                          | 0000 0000                                      | uuuu uuuu                       |  |

| TABLAT   | 242                       | 442 | 252    | 452               | 0000 0000                          | 0000 0000                                      | uuuu uuuu                       |  |

| PRODH    | 242                       | 442 | 252    | 452               | xxxx xxxx                          | սսսս սսսս                                      | uuuu uuuu                       |  |

| PRODL    | 242                       | 442 | 252    | 452               | xxxx xxxx                          | սսսս սսսս                                      | սսսս սսսս                       |  |

| INTCON   | 242                       | 442 | 252    | 452               | 0000 000x                          | 0000 000u                                      | uuuu uuuu <b>(1)</b>            |  |

| INTCON2  | 242                       | 442 | 252    | 452               | 1111 -1-1                          | 1111 -1-1                                      | uuuu -u-u <b>(1)</b>            |  |

| INTCON3  | 242                       | 442 | 252    | 452               | 11-0 0-00                          | 11-0 0-00                                      | uu-u u-uu <b>(1)</b>            |  |

| INDF0    | 242                       | 442 | 252    | 452               | N/A                                | N/A                                            | N/A                             |  |

| POSTINC0 | 242                       | 442 | 252    | 452               | N/A                                | N/A                                            | N/A                             |  |

| POSTDEC0 | 242                       | 442 | 252    | 452               | N/A                                | N/A                                            | N/A                             |  |

| PREINC0  | 242                       | 442 | 252    | 452               | N/A                                | N/A                                            | N/A                             |  |

| PLUSW0   | 242                       | 442 | 252    | 452               | N/A                                | N/A                                            | N/A                             |  |

| FSR0H    | 242                       | 442 | 252    | 452               | xxxx                               | uuuu                                           | uuuu                            |  |

| FSR0L    | 242                       | 442 | 252    | 452               | xxxx xxxx                          | uuuu uuuu                                      | սսսս սսսս                       |  |

| WREG     | 242                       | 442 | 252    | 452               | xxxx xxxx                          | uuuu uuuu                                      | սսսս սսսս                       |  |

| INDF1    | 242                       | 442 | 252    | 452               | N/A                                | N/A                                            | N/A                             |  |

| POSTINC1 | 242                       | 442 | 252    | 452               | N/A                                | N/A                                            | N/A                             |  |

| POSTDEC1 | 242                       | 442 | 252    | 452               | N/A                                | N/A                                            | N/A                             |  |

| PREINC1  | 242                       | 442 | 252    | 452               | N/A                                | N/A                                            | N/A                             |  |

| PLUSW1   | 242                       | 442 | 252    | 452               | N/A                                | N/A                                            | N/A                             |  |

### TABLE 3-3: INITIALIZATION CONDITIONS FOR ALL REGISTERS

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 4: See Table 3-2 for RESET value for specific condition.

- 5: Bit 6 of PORTA, LATA, and TRISA are enabled in ECIO and RCIO Oscillator modes only. In all other Oscillator modes, they are disabled and read '0'.

- 6: Bit 6 of PORTA, LATA and TRISA are not available on all devices. When unimplemented, they are read '0'.

# 4.3 Fast Register Stack

A "fast interrupt return" option is available for interrupts. A Fast Register Stack is provided for the STATUS, WREG and BSR registers and are only one in depth. The stack is not readable or writable and is loaded with the current value of the corresponding register when the processor vectors for an interrupt. The values in the registers are then loaded back into the working registers, if the FAST RETURN instruction is used to return from the interrupt.

A low or high priority interrupt source will push values into the stack registers. If both low and high priority interrupts are enabled, the stack registers cannot be used reliably for low priority interrupts. If a high priority interrupt occurs while servicing a low priority interrupt, the stack register values stored by the low priority interrupt will be overwritten.

If high priority interrupts are not disabled during low priority interrupts, users must save the key registers in software during a low priority interrupt.

If no interrupts are used, the fast register stack can be used to restore the STATUS, WREG and BSR registers at the end of a subroutine call. To use the fast register stack for a subroutine call, a FAST CALL instruction must be executed.

Example 4-1 shows a source code example that uses the fast register stack.

### EXAMPLE 4-1: FAST REGISTER STACK CODE EXAMPLE

| CALL SUB1, FAST | ;STATUS, WREG, BSR<br>;SAVED IN FAST REGISTER<br>;STACK |

|-----------------|---------------------------------------------------------|

| •<br>SUB1       |                                                         |

| RETURN FAST     | ;RESTORE VALUES SAVED<br>;IN FAST REGISTER STACK        |

# 4.4 PCL, PCLATH and PCLATU

The program counter (PC) specifies the address of the instruction to fetch for execution. The PC is 21-bits wide. The low byte is called the PCL register. This register is readable and writable. The high byte is called the PCH register. This register contains the PC<15:8> bits and is not directly readable or writable. Updates to the PCH register. The upper byte is called PCU. This register contains the PC<20:16> bits and is not directly readable or writable. Updates to the PCH register. The Upper byte is called PCU. This register contains the PC<20:16> bits and is not directly readable or writable. Updates to the PCU register may be performed through the PCLATU register.

The PC addresses bytes in the program memory. To prevent the PC from becoming misaligned with word instructions, the LSB of PCL is fixed to a value of '0'. The PC increments by 2 to address sequential instructions in the program memory.

The CALL, RCALL, GOTO and program branch instructions write to the program counter directly. For these instructions, the contents of PCLATH and PCLATU are not transferred to the program counter.

The contents of PCLATH and PCLATU will be transferred to the program counter by an operation that writes PCL. Similarly, the upper two bytes of the program counter will be transferred to PCLATH and PCLATU by an operation that reads PCL. This is useful for computed offsets to the PC (see Section 4.8.1).

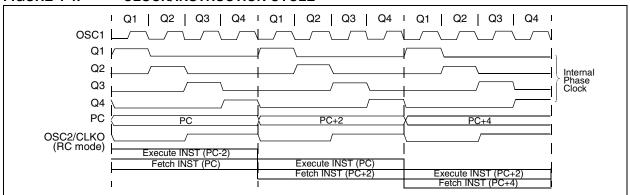

## 4.5 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 4-4.

### FIGURE 4-4:

### **CLOCK/INSTRUCTION CYCLE**

### 5.2.2 TABLAT - TABLE LATCH REGISTER

The Table Latch (TABLAT) is an 8-bit register mapped into the SFR space. The Table Latch is used to hold 8-bit data during data transfers between program memory and data RAM.

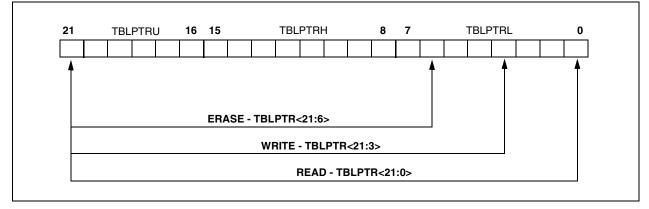

### 5.2.3 TBLPTR - TABLE POINTER REGISTER

The Table Pointer (TBLPTR) addresses a byte within the program memory. The TBLPTR is comprised of three SFR registers: Table Pointer Upper Byte, Table Pointer High Byte and Table Pointer Low Byte (TBLPTRU:TBLPTRH:TBLPTRL). These three registers join to form a 22-bit wide pointer. The low order 21 bits allow the device to address up to 2 Mbytes of program memory space. The 22nd bit allows access to the Device ID, the User ID and the Configuration bits.

The table pointer, TBLPTR, is used by the TBLRD and TBLWT instructions. These instructions can update the TBLPTR in one of four ways based on the table operation. These operations are shown in Table 5-1. These operations on the TBLPTR only affect the low order 21 bits.

### 5.2.4 TABLE POINTER BOUNDARIES

TBLPTR is used in reads, writes, and erases of the FLASH program memory.

When a TBLRD is executed, all 22 bits of the Table Pointer determine which byte is read from program memory into TABLAT.

When a TBLWT is executed, the three LSbs of the Table Pointer (TBLPTR<2:0>) determine which of the eight program memory holding registers is written to. When the timed write to program memory (long write) begins, the 19 MSbs of the Table Pointer, TBLPTR (TBLPTR<21:3>), will determine which program memory block of 8 bytes is written to. For more detail, see Section 5.5 ("Writing to FLASH Program Memory").

When an erase of program memory is executed, the 16 MSbs of the Table Pointer (TBLPTR<21:6>) point to the 64-byte block that will be erased. The Least Significant bits (TBLPTR<5:0>) are ignored.

Figure 5-3 describes the relevant boundaries of TBLPTR based on FLASH program memory operations.

### TABLE 5-1: TABLE POINTER OPERATIONS WITH TBLRD AND TBLWT INSTRUCTIONS

| Example            | Operation on Table Pointer                  |

|--------------------|---------------------------------------------|

| TBLRD*<br>TBLWT*   | TBLPTR is not modified                      |

| TBLRD*+<br>TBLWT*+ | TBLPTR is incremented after the read/write  |

| TBLRD*-<br>TBLWT*- | TBLPTR is decremented after the read/write  |

| TBLRD+*<br>TBLWT+* | TBLPTR is incremented before the read/write |

### FIGURE 5-3: TABLE POINTER BOUNDARIES BASED ON OPERATION

| Name                    | Bit# | Buffer                | Function                                                                                                                                                |

|-------------------------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/INT0                | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input0.<br>Internal software programmable weak pull-up.                                                          |

| RB1/INT1                | bit1 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input1.<br>Internal software programmable weak pull-up.                                                          |

| RB2/INT2                | bit2 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input2.<br>Internal software programmable weak pull-up.                                                          |

| RB3/CCP2 <sup>(3)</sup> | bit3 | TTL/ST <sup>(4)</sup> | Input/output pin or Capture2 input/Compare2 output/PWM output when CCP2MX configuration bit is enabled.<br>Internal software programmable weak pull-up. |

| RB4                     | bit4 | TTL                   | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.                                                            |

| RB5/PGM <sup>(5)</sup>  | bit5 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.<br>Low voltage ICSP enable pin.                            |

| RB6/PGC                 | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.<br>Serial programming clock.                               |

| RB7/PGD                 | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.<br>Serial programming data.                                |

### TABLE 9-3:PORTB FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

**Note 1:** This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: A device configuration bit selects which I/O pin the CCP2 pin is multiplexed on.

4: This buffer is a Schmitt Trigger input when configured as the CCP2 input.

5: Low Voltage ICSP Programming (LVP) is enabled by default, which disables the RB5 I/O function. LVP must be disabled to enable RB5 as an I/O pin and allow maximum compatibility to the other 28-pin and 40-pin mid-range devices.

| TABLE 9-4: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTB |

|------------|--------------------------------------------|

|------------|--------------------------------------------|

| Name    | Bit 7        | Bit 6         | Bit 5       | Bit 4     | Bit 3     | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |

|---------|--------------|---------------|-------------|-----------|-----------|--------|--------|--------|----------------------|---------------------------------|

| PORTB   | RB7          | RB6           | RB5         | RB4       | RB3       | RB2    | RB1    | RB0    | xxxx xxxx            | uuuu uuuu                       |

| LATB    | LATB Da      | ata Output Re |             | xxxx xxxx | uuuu uuuu |        |        |        |                      |                                 |

| TRISB   | PORTB        | Data Directio | on Register |           |           |        |        |        | 1111 1111            | 1111 1111                       |

| INTCON  | GIE/<br>GIEH | PEIE/<br>GIEL | TMR0IE      | INTOIE    | RBIE      | TMR0IF | INTOIF | RBIF   | 0000 000x            | 0000 000u                       |

| INTCON2 | RBPU         | INTEDG0       | INTEDG1     | INTEDG2   | —         | TMR0IP | _      | RBIP   | 1111 -1-1            | 1111 -1-1                       |

| INTCON3 | INT2IP       | INT1IP        | —           | INT2IE    | INT1IE    | —      | INT2IF | INT1IF | 11-0 0-00            | 11-0 0-00                       |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

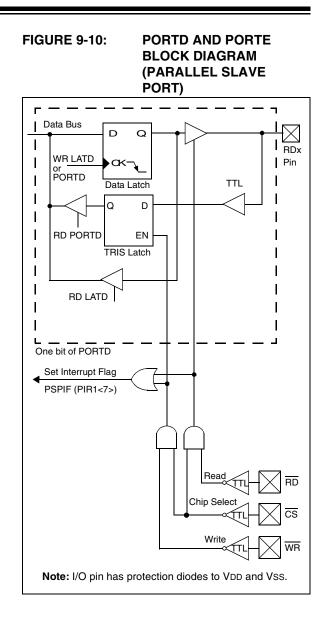

# 9.6 Parallel Slave Port

The Parallel Slave Port is implemented on the 40-pin devices only (PIC18F4X2).

PORTD operates as an 8-bit wide Parallel Slave Port, or microprocessor port when control bit, PSPMODE (TRISE<4>) is set. It is asynchronously readable and writable by the external world through RD control input pin, RE0/RD and WR control input pin, RE1/WR.

It can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting bit PSPMODE enables port pin RE0/RD to be the RD input, <u>RE1/WR</u> to be the WR input and RE2/CS to be the CS (chip select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set). The A/D port configuration bits PCFG2:PCFG0 (ADCON1<2:0>) must be set, which will configure pins RE2:RE0 as digital I/O.

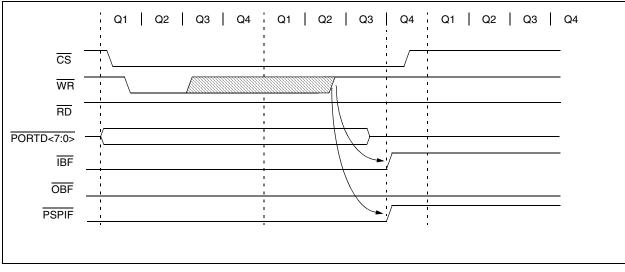

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$  lines are first detected low. A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low.

The PORTE I/O pins become control inputs for the microprocessor port when bit PSPMODE (TRISE<4>) is set. In this mode, the user must make sure that the TRISE<2:0> bits are set (pins are configured as digital inputs), and the ADCON1 is configured for digital I/O. In this mode, the input buffers are TTL.

# FIGURE 9-11: PARALLEL SLAVE PORT WRITE WAVEFORMS

# PIC18FXX2

NOTES:

# 15.3.2 OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON1<5:0>) and SSPSTAT<7:6>. These control bits allow the following to be specified:

- · Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (IDLE state of SCK)

- Data input sample phase (middle or end of data output time)

- Clock edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

The MSSP consists of a transmit/receive Shift Register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR, until the received data is ready. Once the 8 bits of data have been received, that byte is moved to the SSPBUF register. Then the buffer full detect bit, BF (SSPSTAT<0>), and the interrupt flag bit, SSPIF, are set. This double buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the

SSPBUF register during transmission/reception of data will be ignored, and the write collision detect bit, WCOL (SSPCON1<7>), will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully.

When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. Buffer full bit, BF (SSPSTAT<0>), indicates when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP Interrupt is used to determine when the transmission/reception has completed. The SSPBUF must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 15-1 shows the loading of the SSPBUF (SSPSR) for data transmission.

The SSPSR is not directly readable or writable, and can only be accessed by addressing the SSPBUF register. Additionally, the MSSP status register (SSPSTAT) indicates the various status conditions.

# EXAMPLE 15-1: LOADING THE SSPBUF (SSPSR) REGISTER

| LOOP | BRA | SSPSTAT, BF<br>LOOP<br>SSPBUF, W | ;Has data been received(transmit complete)?<br>;No<br>;WREG req = contents of SSPBUF |

|------|-----|----------------------------------|--------------------------------------------------------------------------------------|

|      |     | RXDATA                           | ;Save in user RAM, if data is meaningful                                             |

|      |     | TXDATA, W<br>SSPBUF              | ;W reg = contents of TXDATA<br>;New data to xmit                                     |

# REGISTER 15-3: SSPSTAT: MSSP STATUS REGISTER (I<sup>2</sup>C MODE)

|       | R/W-0                                      | R/W-0                           | R-0                                             | R-0                          | R-0                              | R-0                        | R-0                        | R-0             |  |  |  |  |  |

|-------|--------------------------------------------|---------------------------------|-------------------------------------------------|------------------------------|----------------------------------|----------------------------|----------------------------|-----------------|--|--|--|--|--|

|       | SMP                                        | CKE                             |                                                 | P                            | s                                | R/W                        | UA                         | BF              |  |  |  |  |  |

|       | bit 7                                      | ONE                             | Birt                                            | •                            | Ű                                | 1011                       | 0/1                        | bit 0           |  |  |  |  |  |

|       |                                            |                                 |                                                 |                              |                                  |                            |                            |                 |  |  |  |  |  |

| oit 7 | In Master of                               | Rate Control                    |                                                 | Standard Cn                  | and made (                       |                            | 1 MU-)                     |                 |  |  |  |  |  |

|       |                                            |                                 | enabled for H                                   |                              |                                  |                            | i iviriz)                  |                 |  |  |  |  |  |

| oit 6 | In Master of                               | us Select bi<br>or Slave moo    | de:                                             |                              |                                  |                            |                            |                 |  |  |  |  |  |

|       |                                            | SMBus spe<br>SMBus spe          |                                                 |                              |                                  |                            |                            |                 |  |  |  |  |  |

| oit 5 | D/A: Data/Address bit                      |                                 |                                                 |                              |                                  |                            |                            |                 |  |  |  |  |  |

|       | <u>In Master r</u><br>Reserved             | <u>node:</u>                    |                                                 |                              |                                  |                            |                            |                 |  |  |  |  |  |

|       | In Slave m                                 | ode:                            |                                                 |                              |                                  |                            |                            |                 |  |  |  |  |  |

|       |                                            |                                 | ast byte rece<br>ast byte rece                  |                              |                                  |                            |                            |                 |  |  |  |  |  |

| bit 4 | <b>P:</b> STOP b                           |                                 | OP bit has b                                    | oon dotocto                  | d last                           |                            |                            |                 |  |  |  |  |  |

|       |                                            |                                 | letected last                                   |                              | u last                           |                            |                            |                 |  |  |  |  |  |

|       | Note:                                      | This bit is c                   | leared on RE                                    | SET and w                    | hen SSPEN                        | is cleared.                |                            |                 |  |  |  |  |  |

| oit 3 |                                            | es that a sta                   | rt bit has bee<br>detected las                  |                              | last                             |                            |                            |                 |  |  |  |  |  |

|       | Note:                                      | This bit is c                   | leared on RE                                    | SET and w                    | hen SSPEN                        | is cleared.                |                            |                 |  |  |  |  |  |

| oit 2 | R/W: Read                                  | I/Write bit Int                 | formation (I <sup>2</sup>                       | C mode only                  | /)                               |                            |                            |                 |  |  |  |  |  |

|       | <u>In Slave m</u><br>1 = Read<br>0 = Write | ode:                            |                                                 |                              |                                  |                            |                            |                 |  |  |  |  |  |

|       | Note:                                      |                                 | ls the R/W bi<br>ne address m                   |                              |                                  |                            |                            |                 |  |  |  |  |  |

|       | <u>In Master r</u><br>1 = Transm           | <u>node:</u><br>nit is in progi | ress                                            |                              |                                  |                            |                            |                 |  |  |  |  |  |

|       | 0 = Transm                                 | nit is not in p                 |                                                 |                              |                                  |                            |                            |                 |  |  |  |  |  |

|       | Note:                                      | ORing this I                    | bit with SEN,<br>de.                            | RSEN, PE                     | N, RCEN, o                       | r ACKEN wil                | l indicate if t            | he MSSP is      |  |  |  |  |  |

| bit 1 | 1 = Indicate                               | es that the u                   | 10-bit Slave r<br>ser needs to<br>need to be up | update the                   | address in t                     | he SSPADD                  | register                   |                 |  |  |  |  |  |

| bit 0 | BF: Buffer                                 | Full Status b                   | oit                                             |                              |                                  |                            |                            |                 |  |  |  |  |  |

|       |                                            | e complete,                     | SSPBUF is t<br>ete, SSPBUF                      |                              |                                  |                            |                            |                 |  |  |  |  |  |

|       | In Receive                                 | -                               | ,                                               | ie empty                     |                                  |                            |                            |                 |  |  |  |  |  |

|       | 1 = Data training 0 = Data training 1      | ansmit in pro<br>ansmit comp    | ogress (does<br>blete (does n                   | not include<br>ot include th | th <u>e ACK</u> ar<br>ne ACK and | d STOP bits<br>STOP bits), | ), SSPBUF i<br>SSPBUF is ( | s full<br>empty |  |  |  |  |  |

|       | Legend:                                    |                                 |                                                 |                              |                                  |                            |                            |                 |  |  |  |  |  |

|       | R = Reada                                  | ble bit                         | W = Writab                                      | le bit                       | U = Unimp                        | lemented bit               | , read as '0'              |                 |  |  |  |  |  |

|       | - n = Value                                | at POR                          | '1' = Bit is s                                  | et                           | '0' = Bit is                     | cleared                    | x = Bit is ur              | nknown          |  |  |  |  |  |

| BAUD           | Fosc = 40 MHz |            | SPBRG              | 33 MHz |            | SPBRG              | 25 MHz |            | SPBRG              | 20 MHz |            | SPBRG              |

|----------------|---------------|------------|--------------------|--------|------------|--------------------|--------|------------|--------------------|--------|------------|--------------------|

| RATE<br>(Kbps) | KBAUD         | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) |

| 0.3            | NA            | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA     | -          | -                  |

| 1.2            | NA            | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA     | -          | -                  |

| 2.4            | NA            | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA     | -          | -                  |

| 9.6            | NA            | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA     | -          | -                  |

| 19.2           | NA            | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA     | -          | -                  |

| 76.8           | 76.92         | +0.16      | 129                | 77.10  | +0.39      | 106                | 77.16  | +0.47      | 80                 | 76.92  | +0.16      | 64                 |

| 96             | 96.15         | +0.16      | 103                | 95.93  | -0.07      | 85                 | 96.15  | +0.16      | 64                 | 96.15  | +0.16      | 51                 |

| 300            | 303.03        | +1.01      | 32                 | 294.64 | -1.79      | 27                 | 297.62 | -0.79      | 20                 | 294.12 | -1.96      | 16                 |

| 500            | 500           | 0          | 19                 | 485.30 | -2.94      | 16                 | 480.77 | -3.85      | 12                 | 500    | 0          | 9                  |

| HIGH           | 10000         | -          | 0                  | 8250   | -          | 0                  | 6250   | -          | 0                  | 5000   | -          | 0                  |

| LOW            | 39.06         | -          | 255                | 32.23  | -          | 255                | 24.41  | -          | 255                | 19.53  | -          | 255                |

|  | TABLE 16-3: | BAUD RATES FOR SYNCHRONOUS MODE |

|--|-------------|---------------------------------|

|--|-------------|---------------------------------|

| BAUD           | Fosc = | 16 MHz SPBRG 10 |                    | MHz SPBRG |            | 7.1590             | 9 MHz   | SPBRG      | 5.0688 MHz         |         | SPBRG      |                    |  |

|----------------|--------|-----------------|--------------------|-----------|------------|--------------------|---------|------------|--------------------|---------|------------|--------------------|--|

| RATE<br>(Kbps) | KBAUD  | %<br>ERROR      | value<br>(decimal) | KBAUD     | %<br>ERROR | value<br>(decimal) | KBAUD   | %<br>ERROR | value<br>(decimal) | KBAUD   | %<br>ERROR | value<br>(decimal) |  |

| 0.3            | NA     | -               | -                  | NA        | -          | -                  | NA      | -          | -                  | NA      | -          | -                  |  |

| 1.2            | NA     | -               | -                  | NA        | -          | -                  | NA      | -          | -                  | NA      | -          | -                  |  |

| 2.4            | NA     | -               | -                  | NA        | -          | -                  | NA      | -          | -                  | NA      | -          | -                  |  |

| 9.6            | NA     | -               | -                  | NA        | -          | -                  | 9.62    | +0.23      | 185                | 9.60    | 0          | 131                |  |

| 19.2           | 19.23  | +0.16           | 207                | 19.23     | +0.16      | 129                | 19.24   | +0.23      | 92                 | 19.20   | 0          | 65                 |  |

| 76.8           | 76.92  | +0.16           | 51                 | 75.76     | -1.36      | 32                 | 77.82   | +1.32      | 22                 | 74.54   | -2.94      | 16                 |  |

| 96             | 95.24  | -0.79           | 41                 | 96.15     | +0.16      | 25                 | 94.20   | -1.88      | 18                 | 97.48   | +1.54      | 12                 |  |

| 300            | 307.70 | +2.56           | 12                 | 312.50    | +4.17      | 7                  | 298.35  | -0.57      | 5                  | 316.80  | +5.60      | 3                  |  |

| 500            | 500    | 0               | 7                  | 500       | 0          | 4                  | 447.44  | -10.51     | 3                  | 422.40  | -15.52     | 2                  |  |

| HIGH           | 4000   | -               | 0                  | 2500      | -          | 0                  | 1789.80 | -          | 0                  | 1267.20 | -          | 0                  |  |

| LOW            | 15.63  | -               | 255                | 9.77      | -          | 255                | 6.99    | -          | 255                | 4.95    | -          | 255                |  |

| BAUD           | Fosc = | 4 MHz      | SPBRG              | 3.5795 | 45 MHz     | SPBRG              | 1 MHz |            | SPBRG              | 32.768 kHz |            | SPBRG              |

|----------------|--------|------------|--------------------|--------|------------|--------------------|-------|------------|--------------------|------------|------------|--------------------|

| RATE<br>(Kbps) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD | %<br>ERROR | value<br>(decimal) | KBAUD      | %<br>ERROR | value<br>(decimal) |

| 0.3            | NA     | -          | -                  | NA     | -          | -                  | NA    | -          | -                  | 0.30       | +1.14      | 26                 |

| 1.2            | NA     | -          | -                  | NA     | -          | -                  | 1.20  | +0.16      | 207                | 1.17       | -2.48      | 6                  |

| 2.4            | NA     | -          | -                  | NA     | -          | -                  | 2.40  | +0.16      | 103                | 2.73       | +13.78     | 2                  |

| 9.6            | 9.62   | +0.16      | 103                | 9.62   | +0.23      | 92                 | 9.62  | +0.16      | 25                 | 8.20       | -14.67     | 0                  |

| 19.2           | 19.23  | +0.16      | 51                 | 19.04  | -0.83      | 46                 | 19.23 | +0.16      | 12                 | NA         | -          | -                  |

| 76.8           | 76.92  | +0.16      | 12                 | 74.57  | -2.90      | 11                 | 83.33 | +8.51      | 2                  | NA         | -          | -                  |

| 96             | 1000   | +4.17      | 9                  | 99.43  | +3.57      | 8                  | 83.33 | -13.19     | 2                  | NA         | -          | -                  |

| 300            | 333.33 | +11.11     | 2                  | 298.30 | -0.57      | 2                  | 250   | -16.67     | 0                  | NA         | -          | -                  |

| 500            | 500    | 0          | 1                  | 447.44 | -10.51     | 1                  | NA    | -          | -                  | NA         | -          | -                  |

| HIGH           | 1000   | -          | 0                  | 894.89 | -          | 0                  | 250   | -          | 0                  | 8.20       | -          | 0                  |

| LOW            | 3.91   | -          | 255                | 3.50   | -          | 255                | 0.98  | -          | 255                | 0.03       | -          | 255                |

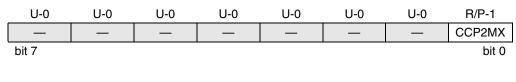

### REGISTER 19-4: CONFIGURATION REGISTER 3 HIGH (CONFIG3H: BYTE ADDRESS 300005h)

bit 7-1 Unimplemented: Read as '0'

bit 0

CCP2MX: CCP2 Mux bit

1 = CCP2 input/output is multiplexed with RC1

0 = CCP2 input/output is multiplexed with RB3

| Legend:             |                      |                                     |

|---------------------|----------------------|-------------------------------------|

| R = Readable bit    | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| - n = Value when de | vice is unprogrammed | u = Unchanged from programmed state |

### REGISTER 19-5: CONFIGURATION REGISTER 4 LOW (CONFIG4L: BYTE ADDRESS 300006h)

|         | R/P-1                                                         | U-0                                        | U-0           | U-0          | U-0      | R/P-1       | U-0            | R/P-1    |  |  |

|---------|---------------------------------------------------------------|--------------------------------------------|---------------|--------------|----------|-------------|----------------|----------|--|--|

|         | BKBUG                                                         | —                                          | —             | —            | —        | LVP         | —              | STVREN   |  |  |

|         | bit 7                                                         |                                            |               |              |          |             |                | bit 0    |  |  |

| bit 7   | 1 = Backg                                                     | Background D<br>round Debug<br>round Debug | ger disabled  | d. RB6 and I | 0        | 0           |                | •        |  |  |

| bit 6-3 | Unimplemented: Read as '0'                                    |                                            |               |              |          |             |                |          |  |  |

| bit 2   | LVP: Low Voltage ICSP Enable bit                              |                                            |               |              |          |             |                |          |  |  |

|         | 1 = Low Voltage ICSP enabled<br>0 = Low Voltage ICSP disabled |                                            |               |              |          |             |                |          |  |  |

| bit 1   | Unimplem                                                      | ented: Read                                | as '0'        |              |          |             |                |          |  |  |

| bit 0   | STVREN:                                                       | Stack Full/Ur                              | derflow Re    | set Enable b | pit      |             |                |          |  |  |

|         |                                                               | Full/Underflow                             |               |              |          |             |                |          |  |  |

|         | 0 = Stack I                                                   | Full/Underflow                             | v will not ca | use RESET    | •        |             |                |          |  |  |

|         |                                                               |                                            |               |              |          |             |                |          |  |  |

|         | Legend:                                                       |                                            |               |              |          |             |                |          |  |  |

|         | R = Reada                                                     | ble bit                                    | C = Cleara    | able bit     | U = Unin | nplemented  | d bit, read as | '0'      |  |  |

|         | - n = Value                                                   | when device                                | is unprogra   | ammed        | u = Unch | nanged fror | n programme    | ed state |  |  |

# 19.4 Program Verification and Code Protection

The overall structure of the code protection on the PIC18 FLASH devices differs significantly from other PICmicro devices.

The user program memory is divided into five blocks. One of these is a boot block of 512 bytes. The remainder of the memory is divided into four blocks on binary boundaries. Each of the five blocks has three code protection bits associated with them. They are:

- Code Protect bit (CPn)

- Write Protect bit (WRTn)

- External Block Table Read bit (EBTRn)

Figure 19-3 shows the program memory organization for 16- and 32-Kbyte devices, and the specific code protection bit associated with each block. The actual locations of the bits are summarized in Table 19-3.

### FIGURE 19-3: CODE PROTECTED PROGRAM MEMORY FOR PIC18F2XX/4XX

|   | MEMORY SI                 | ZE/DEVICE                 |                    | Block Code Protection        |

|---|---------------------------|---------------------------|--------------------|------------------------------|

|   | 16 Kbytes<br>(PIC18FX42)  | 32 Kbytes<br>(PIC18FX52)  | Address<br>Range   | Controlled By:               |

|   | Boot Block                | Boot Block                | 000000h<br>0001FFh | CPB, WRTB, EBTRB             |

| - | Block 0                   | Block 0                   | 000200h<br>001FFFh | CP0, WRT0, EBTR0             |

|   | Block 1                   | Block 1                   | 002000h<br>003FFFh | CP1, WRT1, EBTR1             |

|   | Unimplemented<br>Read 0's | Block 2                   | 004000h<br>005FFFh | CP2, WRT2, EBTR2             |

|   | Unimplemented<br>Read 0's | Block 3                   | 006000h<br>007FFFh | CP3, WRT3, EBTR3             |

|   | Unimplemented<br>Read 0's | Unimplemented<br>Read 0's | 008000h            | (Unimplemented Memory Space) |

|   |                           |                           | 1FFFFFh            |                              |

# TABLE 19-3: SUMMARY OF CODE PROTECTION REGISTERS

| File Name |          | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----------|----------|-------|-------|-------|-------|-------|-------|-------|-------|

| 300008h   | CONFIG5L | —     | —     |       |       | CP3   | CP2   | CP1   | CP0   |

| 300009h   | CONFIG5H | CPD   | CPB   | _     | _     | —     | —     | —     | _     |

| 30000Ah   | CONFIG6L | —     | —     | _     | _     | WRT3  | WRT2  | WRT1  | WRT0  |

| 30000Bh   | CONFIG6H | WRTD  | WRTB  | WRTC  | _     | —     | —     | —     |       |

| 30000Ch   | CONFIG7L | _     | —     | _     | _     | EBTR3 | EBTR2 | EBTR1 | EBTR0 |

| 30000Dh   | CONFIG7H |       | EBTRB | _     | _     | —     | _     | —     |       |

Legend: Shaded cells are unimplemented.

| INCFSZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Incremen                                | t f, skip if 0                   |                 |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------|-----------------|--|--|--|--|

| Syntax:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | [label]                                 | NCFSZ f[                         | ,d [,a]         |  |  |  |  |

| Operands:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]   | 5                                |                 |  |  |  |  |

| Operation:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | (f) + 1 $\rightarrow$ c<br>skip if resu |                                  |                 |  |  |  |  |

| Status Affected:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | None                                    |                                  |                 |  |  |  |  |

| Encoding:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0011                                    | 11da ff:                         | ff ffff         |  |  |  |  |

| Description:<br>The contents of register 'f' are<br>incremented. If 'd' is 0, the result is<br>placed in W. If 'd' is 1, the result is<br>placed back in register 'f'. (default)<br>If the result is 0, the next instruc-<br>tion, which is already fetched, is<br>discarded, and a NOP is executed<br>instead, making it a two-cycle<br>instruction. If 'a' is 0, the Access<br>Bank will be selected, overriding<br>the BSR value. If 'a' = 1, then the<br>bank will be selected as per the<br>BSR value (default). |                                         |                                  |                 |  |  |  |  |

| Words:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                       |                                  |                 |  |  |  |  |

| Cycles: 1(2)<br>Note: 3 cycles if skip and followed<br>by a 2-word instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         |                                  |                 |  |  |  |  |

| Q Cycle Activity:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | - ,                                     |                                  |                 |  |  |  |  |

| Q1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Q2                                      | Q3                               | Q4              |  |  |  |  |

| Decode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Read                                    | Process                          | Write to        |  |  |  |  |

| lf alvia:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | register 'f'                            | Data                             | destination     |  |  |  |  |

| lf skip:<br>Q1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Q2                                      | Q3                               | 04              |  |  |  |  |

| No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | No                                      | No                               | Q4<br>No        |  |  |  |  |

| operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | operation                               | operation                        | operation       |  |  |  |  |

| If skip and follow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ed by 2-wor                             | d instruction:                   |                 |  |  |  |  |

| Q1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Q2                                      | Q3                               | Q4              |  |  |  |  |

| No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | No                                      | No                               | No              |  |  |  |  |

| operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | operation                               | operation                        | operation       |  |  |  |  |

| No<br>operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | No<br>operation                         | No<br>operation                  | No<br>operation |  |  |  |  |

| Example:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | HERE I<br>NZERO ZERO                    | HERE INCFSZ CNT, 1, 0<br>NZERO : |                 |  |  |  |  |

| Before Instru                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                         | (הממקת)                          |                 |  |  |  |  |

| 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | = Address                               | 6 (HERE)                         |                 |  |  |  |  |

| CNT<br>If CNT<br>PC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | If $CNT = 0;$                           |                                  |                 |  |  |  |  |

| If CNT<br>PC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ≠ 0;<br>= Address                       | (NZERO)                          |                 |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         | ,                                |                 |  |  |  |  |

| INFS                                                                                                                                                                                                                                                                                                                                                                                                             | SNZ             | Increment                               | t f, skip i    | if not 0  |               |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------------------------|----------------|-----------|---------------|--|--|--|--|--|

| Synt                                                                                                                                                                                                                                                                                                                                                                                                             | ax:             | [label]                                 | NFSNZ          | f [,d [,a | a]            |  |  |  |  |  |

| Ope                                                                                                                                                                                                                                                                                                                                                                                                              | rands:          | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]   | 5              |           |               |  |  |  |  |  |

| Ope                                                                                                                                                                                                                                                                                                                                                                                                              | ration:         | (f) + 1 $\rightarrow$ c<br>skip if resu |                |           |               |  |  |  |  |  |

| Statu                                                                                                                                                                                                                                                                                                                                                                                                            | us Affected:    | None                                    |                |           |               |  |  |  |  |  |

| Enco                                                                                                                                                                                                                                                                                                                                                                                                             | oding:          | 0100                                    | 10da           | ffff      | ffff          |  |  |  |  |  |

| Description:The contents of register 'f' are<br>incremented. If 'd' is 0, the result is<br>placed in W. If 'd' is 1, the result is<br>placed back in register 'f' (default).<br>If the result is not 0, the next<br>instruction, which is already<br>fetched, is discarded, and a NOP is<br>executed instead, making it a two-<br>cycle instruction. If 'a' is 0, the<br>Access Bank will be selected, over-<br> |                 |                                         |                |           |               |  |  |  |  |  |