Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

### Details

E·XFI

| 2 0 0 0 0 0             |                                                                       |

|-------------------------|-----------------------------------------------------------------------|

| Product Status          | Active                                                                |

| Туре                    | Floating Point                                                        |

| Interface               | Host Interface, Link Port, Serial Port                                |

| Clock Rate              | 80MHz                                                                 |

| Non-Volatile Memory     | External                                                              |

| On-Chip RAM             | 512kB                                                                 |

| Voltage - I/O           | 3.30V                                                                 |

| Voltage - Core          | 2.50V                                                                 |

| Operating Temperature   | 0°C ~ 85°C (TC)                                                       |

| Mounting Type           | Surface Mount                                                         |

| Package / Case          | 400-BBGA                                                              |

| Supplier Device Package | 400-PBGA (27x27)                                                      |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adsp-21160mkbz-80 |

|                         |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE OF CONTENTS

| General Description                    | 4  |

|----------------------------------------|----|

| ADSP-21160x Family Core Architecture   | 4  |

| Memory and I/O Interface Features      | 7  |

| Development Tools                      | 9  |

| Additional Information                 | 10 |

| Related Signal Chains                  | 10 |

| Pin Function Descriptions              | 11 |

| Specifications                         | 15 |

| Operating Conditions—ADSP-21160M       | 15 |

| Electrical Characteristics—ADSP-21160M | 16 |

| Operating Conditions—ADSP-21160N       | 17 |

| Electrical Characteristics—ADSP-21160N | 18 |

| Absolute Maximum Ratings               | 19 |

## **REVISION HISTORY**

| Removed model ADSP-21160NKB-100 (no longer available) |

|-------------------------------------------------------|

| from Ordering Guide                                   |

|    | ESD Sensitivity                   | 19 |

|----|-----------------------------------|----|

|    | Package Information               | 19 |

|    | Timing Specifications             | 20 |

|    | Output Drive Currents—ADSP-21160M | 47 |

|    | Output Drive Currents—ADSP-21160N | 47 |

|    | Power Dissipation                 | 47 |

|    | Test Conditions                   | 48 |

|    | Environmental Conditions          | 51 |

| 4( | 00-Ball PBGA Pin Configurations   | 52 |

| 0  | utline Dimensions                 | 57 |

| Sı | urface-Mount Design               | 57 |

| 0  | rdering Guide                     | 58 |

|    |                                   |    |

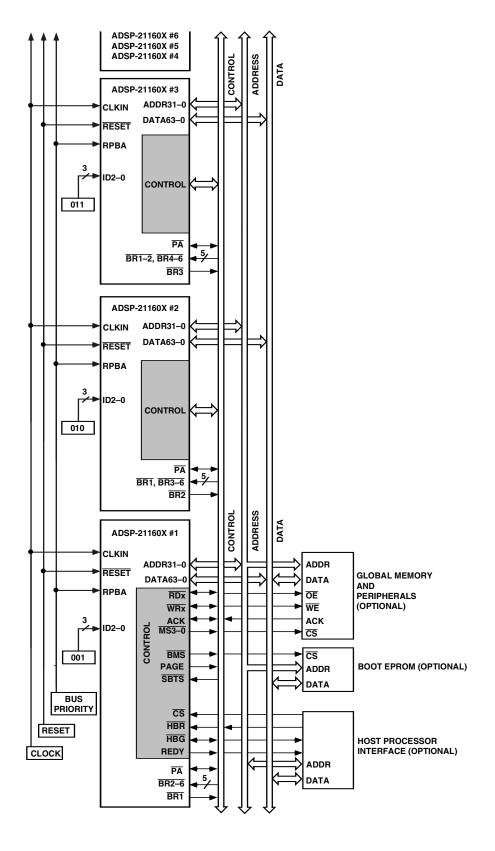

Figure 3. Shared Memory Multiprocessing System

located on the web page for the associated EZ-KIT or EZ-Extender product. The link is found in the *Product Download* area of the product web page.

### **Middleware Packages**

Analog Devices separately offers middleware add-ins such as real time operating systems, file systems, USB stacks, and TCP/IP stacks. For more information, see the following web pages:

- www.analog.com/ucos3

- www.analog.com/ucfs

- www.analog.com/ucusbd

- www.analog.com/lwip

### **Algorithmic Modules**

To speed development, Analog Devices offers add-ins that perform popular audio and video processing algorithms. These are available for use with both CrossCore Embedded Studio and VisualDSP++. For more information visit www.analog.com and search on "Blackfin software modules" or "SHARC software modules".

### Designing an Emulator-Compatible DSP Board (Target)

For embedded system test and debug, Analog Devices provides a family of emulators. On each JTAG DSP, Analog Devices supplies an IEEE 1149.1 JTAG Test Access Port (TAP). In-circuit emulation is facilitated by use of this JTAG interface. The emulator accesses the processor's internal features via the processor's TAP, allowing the developer to load code, set breakpoints, and view variables, memory, and registers. The processor must be halted to send data and commands, but once an operation is completed by the emulator, the DSP system is set to run at full speed with no impact on system timing. The emulators require the target board to include a header that supports connection of the DSP's JTAG port to the emulator.

For details on target board design issues including mechanical layout, single processor connections, signal buffering, signal termination, and emulator pod logic, see the application note (EE-68) "Analog Devices JTAG Emulation Technical Reference" (www.analog.com/ee-68). This document is updated regularly to keep pace with improvements to emulator support.

## **ADDITIONAL INFORMATION**

This data sheet provides a general overview of the ADSP-21160x architecture and functionality. For detailed information on the Blackfin family core architecture and instruction set, refer to the ADSP-21160 SHARC DSP Hardware Reference and the ADSP-21160 SHARC DSP Instruction Set Reference. For detailed information on the development tools for this processor, see the VisualDSP++ User's Guide.

## **RELATED SIGNAL CHAINS**

A signal chain is a series of signal conditioning electronic components that receive input (data acquired from sampling either real-time phenomena or from stored data) in tandem, with the output of one portion of the chain supplying input to the next. Signal chains are often used in signal processing applications to gather and process data or to apply system controls based on analysis of real-time phenomena.

Analog Devices eases signal processing system development by providing signal processing components that are designed to work together well. A tool for viewing relationships between specific applications and related components is available on the www.analog.com website.

The application signal chains page in the Circuits from the Lab<sup>®</sup> site (http://www.analog.com/circuits) provides:

- Graphical circuit block diagram presentation of signal chains for a variety of circuit types and applications

- Drill down links for components in each chain to selection guides and application information

- Reference designs applying best practice design techniques

# **PIN FUNCTION DESCRIPTIONS**

ADSP-21160x pin definitions are listed below. Inputs identified as synchronous (S) must meet timing requirements with respect to CLKIN (or with respect to TCK for TMS, TDI). Inputs identified as asynchronous (A) can be asserted asynchronously to CLKIN (or to TCK for TRST).

Tie or pull unused inputs to  $V_{\text{DD}}$  or GND, except for the following:

- ADDR31-0, DATA63-0, PAGE, BRST, CLKOUT (ID2-0 = 00x) (Note: These pins have a logic-level hold circuit enabled on the ADSP-21160x DSP with ID2-0 = 00x.)

- PA, ACK, MS3-0, RDx, WRx, CIF, DMARx, DMAGx (ID2-0 = 00x) (Note: These pins have a pull-up enabled on the ADSP-21160x with ID2-0 = 00x.)

#### Table 3. Pin Function Descriptions

- LxCLK, LxACK, LxDAT7-0 (LxPDRDE = 0) (Note: See Link Port Buffer Control Register Bit definitions in the ADSP-21160 SHARC DSP Hardware Reference.)

- DTx, DRx, TCLKx, RCLKx, EMU, TMS, TRST, TDI (Note: These pins have a pull-up.)

The following symbols appear in the Type column of Table 3: A = Asynchronous, G = Ground, I = Input, O = Output, P = Power Supply, S = Synchronous, (A/D) = Active Drive, (O/D) = Open Drain, and T = Three-State (when SBTS is asserted, or when the ADSP-21160x is a bus slave).

| Pin      | Туре  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADDR31-0 | I/O/T | External Bus Address. The ADSP-21160x outputs addresses for external memory and peripherals<br>on these pins. In a multiprocessor system, the bus master outputs addresses for read/writes of the<br>internal memory or IOP registers of other ADSP-21160x DSPs. The ADSP-21160x inputs addresses<br>when a host processor or multiprocessing bus master is reading or writing its internal memory or<br>IOP registers. A keeper latch on the DSP's ADDR31–0 pins maintains the input at the level it was<br>last driven (only enabled on the processor with ID2–0 = 00x).                                                                                                                   |

| DATA63-0 | I/O/T | External Bus Data. The ADSP-21160x inputs and outputs data and instructions on these pins. Pull-<br>up resistors on unused DATA pins are not necessary. A keeper latch on the DSP's DATA63-0 pins<br>maintains the input at the level it was last driven (only enabled on the processor with ID2–0 = 00x).                                                                                                                                                                                                                                                                                                                                                                                   |

| MS3-0    | 0/Т   | Memory Select Lines. These outputs are asserted (low) as chip selects for the corresponding banks<br>of external memory. Memory bank size must be defined in the SYSCON control register. The $\overline{MS3-0}$<br>outputs are decoded memory address lines. In asynchronous access mode, the $\overline{MS3-0}$ outputs<br>transition with the other address outputs. In synchronous access modes, the $\overline{MS3-0}$ outputs assert<br>with the other address lines; however, they deassert after the first CLKIN cycle in which ACK is<br>sampled asserted. $\overline{MS3-0}$ has a 20 k $\Omega$ internal pull-up resistor that is enabled on the ADSP-21160x<br>with ID2-0 = 00x. |

| RDL      | I/O/T | Memory Read Low Strobe. RDL is asserted whenever ADSP-21160x reads from the low word of external memory or from the internal memory of other ADSP-21160x DSPs. External devices, including other ADSP-21160x DSPs, must assert RDL for reading from the low word of processor internal memory. In a multiprocessing system, RDL is driven by the bus master. RDL has a 20 k $\Omega$ internal pull-up resistor that is enabled on the processor with ID2–0 = 00x.                                                                                                                                                                                                                            |

| RDH      | I/O/T | Memory Read High Strobe. RDH is asserted whenever ADSP-21160x reads from the high word of external memory or from the internal memory of other ADSP-21160x DSPs. External devices, including other ADSP-21160x DSPs, must assert RDH for reading from the high word of ADSP-21160x internal memory. In a multiprocessing system, RDH is driven by the bus master. RDH has a 20 k $\Omega$ internal pull-up resistor that is enabled on the processor with ID2–0 = 00x.                                                                                                                                                                                                                       |

| WRL      | I/O/T | Memory Write Low Strobe. WRL is asserted when ADSP-21160x writes to the low word of external memory or internal memory of other ADSP-21160x DSPs. External devices must assert WRL for writing to ADSP-21160x DSP's low word of internal memory. In a multiprocessing system, WRL is driven by the bus master. WRL has a 20 k $\Omega$ internal pull-up resistor that is enabled on the processor with ID2–0 = 00x.                                                                                                                                                                                                                                                                          |

| WRH      | I/O/T | Memory Write High Strobe. WRH is asserted when ADSP-21160x writes to the high word of external memory or internal memory of other ADSP-21160x DSPs. External devices must assert WRH for writing to ADSP-21160x DSP's high word of internal memory. In a multiprocessing system, WRH is driven by the bus master. WRH has a 20 k $\Omega$ internal pull-up resistor that is enabled on the processor with ID2–0 = 00x.                                                                                                                                                                                                                                                                       |

### Table 3. Pin Function Descriptions (Continued)

| Pin         | Туре    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PAGE        | 0/Т     | DRAM Page Boundary. The processor asserts this pin to an external DRAM controller, to signal that<br>an external DRAM page boundary has been crossed. DRAM page size must be defined in the<br>processor's memory control register (WAIT). DRAM can only be implemented in external memory<br>Bank 0; the PAGE signal can only be activated for Bank 0 accesses. In a multiprocessing system, PAGE<br>is output by the bus master. A keeper latch on the DSP's PAGE pin maintains the output at the level<br>it was last driven (only enabled on the processor with ID2–0 = 00x).                                                                                                                                                                                                                                        |

| BRST        | I/O/T   | Sequential Burst Access. BRST is asserted by ADSP-21160x or a host to indicate that data associated with consecutive addresses is being read or written. A slave device samples the initial address and increments an internal address counter after each transfer. The incremented address is not pipelined on the bus. If the burst access is a read from the host to the processor, the processor automatically increments the address as long as BRST is asserted. BRST is asserted after the initial access of a burst transfer. It is asserted for every cycle after that, except for the last data request cycle (denoted by RDx or WRx asserted and BRST negated). A keeper latch on the DSP's BRST pin maintains the input at the level it was last driven (only enabled on the processor with $ID2-0 = 00x$ ). |

| АСК         | I/O/S   | Memory Acknowledge. External devices can deassert ACK (low) to add wait states to an external memory access. ACK is used by I/O devices, memory controllers, or other peripherals to hold off completion of an external memory access. The ADSP-21160x deasserts ACK as an output to add wait states to a synchronous access of its internal memory, by a synchronous host or another DSP in a multiprocessor configuration. ACK has a 2 k $\Omega$ internal pull-up resistor that is enabled on the processor with ID2–0 = 00x.                                                                                                                                                                                                                                                                                         |

| <u>SBTS</u> | I/S     | Suspend Bus and Three-State. External devices can assert SBTS (low) to place the external bus address, data, selects, and strobes in a high-impedance state for the following cycle. If the ADSP-21160x attempts to access external memory while SBTS is asserted, the processor will halt and the memory access will not be completed until SBTS is deasserted. SBTS should only be used to recover from host processor and/or ADSP-21160x deadlock or used with a DRAM controller.                                                                                                                                                                                                                                                                                                                                     |

| IRQ2-0      | I/A     | Interrupt Request Lines. These are sampled on the rising edge of CLKIN and may be either edge-<br>triggered or level-sensitive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| FLAG3-0     | I/O/A   | Flag Pins. Each is configured via control bits as either an input or output. As an input, it can be tested as a condition. As an output, it can be used to signal external peripherals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TIMEXP      | 0       | Timer Expired. Asserted for four processor core clock (CCLK) cycles when the timer is enabled and TCOUNT decrements to zero.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| HBR         | I/A     | Host Bus Request. Must be asserted by a host processor to request control of the ADSP-21160x DSP's external bus. When HBR is asserted in a multiprocessing system, the processor that is bus master will relinquish the bus and assert HBG. To relinquish the bus, the processor places the address, data, select, and strobe lines in a high-impedance state. HBR has priority over all processor bus requests (BR6–1) in a multiprocessing system.                                                                                                                                                                                                                                                                                                                                                                     |

| HBG         | I/O     | Host Bus Grant. Acknowledges an HBR bus request, indicating that the host processor may take control of the external bus. HBG is asserted (held low) by the ADSP-21160x until HBR is released. In a multiprocessing system, HBG is output by the processor bus master and is monitored by all others. After HBR is asserted, and before HBG is given, HBG will float for 1 $t_{CLK}$ (1 CLKIN cycle). To avoid erroneous grants, HBG should be pulled up with a 20 k $\Omega$ to 50 k $\Omega$ external resistor.                                                                                                                                                                                                                                                                                                        |

| <u>CS</u>   | I/A     | Chip Select. Asserted by host processor to select the ADSP-21160x, for asynchronous transfer protocol.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| REDY        | O (O/D) | Host Bus Acknowledge. The ADSP-21160x deasserts REDY (low) to add wait states to an asynchronous host access when CS and HBR inputs are asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DMAR1       | I/A     | DMA Request 1 (DMA Channel 11). Asserted by external port devices to request DMA services. DMAR1 has a 20 k $\Omega$ internal pull-up resistor that is enabled on the ADSP-21160x with ID2–0 = 00x.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DMAR2       | I/A     | DMA Request 2 (DMA Channel 12). Asserted by external port devices to request DMA services.<br>DMAR2 has a 20 k $\Omega$ internal pull-up resistor that is enabled on the ADSP-21160x with ID2–0 = 00x.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Pin        | Туре  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ID2-0      | 1     | Multiprocessing ID. Determines which multiprocessing bus request ( $\overline{BR1}$ – $\overline{BR6}$ ) is used by the ADSP-21160x. ID = 001 corresponds to $\overline{BR1}$ , ID = 010 corresponds to $\overline{BR2}$ , and so on. Use ID = 000 or ID = 001 in single-processor systems. These lines are a system configuration selection which should be hardwired or only changed at reset.                                                         |

| DMAG1      | O/T   | DMA Grant 1 (DMA Channel 11). Asserted by ADSP-21160x to indicate that the requested DMA starts on the next cycle. Driven by bus master only. DMAG1 has a 20 k $\Omega$ internal pull-up resistor that is enabled on the ADSP-21160x with ID2–0 = 00x.                                                                                                                                                                                                   |

| DMAG2      | 0/Т   | DMA Grant 2 (DMA Channel 12). Asserted by ADSP-21160x to indicate that the requested DMA starts on the next cycle. Driven by bus master only. DMAG2 has a 20 k $\Omega$ internal pull-up resistor that is enabled on the ADSP-21160x with ID2–0 = 00x.                                                                                                                                                                                                   |

| BR6-1      | I/O/S | Multiprocessing Bus Requests. Used by multiprocessing ADSP-21160x DSPs to arbitrate for bus mastership. An ADSP-21160x only drives its own BRx line (corresponding to the value of its ID2–0 inputs) and monitors all others. In a multiprocessor system with less than six ADSP-21160x DSPs, the unused BRx pins should be pulled high; the processor's own BRx line must not be pulled high or low because it is an output.                            |

| RPBA       | I/S   | Rotating Priority Bus Arbitration Select. When RPBA is high, rotating priority for multiprocessor bus arbitration is selected. When RPBA is low, fixed priority is selected. This signal is a system configuration selection which must be set to the same value on every ADSP-21160x. If the value of RPBA is changed during system operation, it must be changed in the same CLKIN cycle on every processor.                                           |

| PA         | I/O/T | Priority Access. Asserting its $\overline{PA}$ pin allows an ADSP-21160x bus slave to interrupt background DMA transfers and gain access to the external bus. $\overline{PA}$ is connected to all ADSP-21160x DSPs in the system. If access priority is not required in a system, the $\overline{PA}$ pin should be left unconnected. $\overline{PA}$ has a 20 k $\Omega$ internal pull-up resistor that is enabled on the ADSP-21160x with ID2-0 = 00x. |

| DTx        | 0     | Data Transmit (Serial Ports 0, 1). Each DT pin has a 50 k $\Omega$ internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                            |

| DRx        | I     | Data Receive (Serial Ports 0, 1). Each DR pin has a 50 k $\Omega$ internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                             |

| TCLKx      | I/O   | Transmit Clock (Serial Ports 0, 1). Each TCLK pin has a 50 k $\Omega$ internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                         |

| RCLKx      | I/O   | Receive Clock (Serial Ports 0, 1). Each RCLK pin has a 50 k $\Omega$ internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                          |

| TFSx       | I/O   | Transmit Frame Sync (Serial Ports 0, 1).                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RFSx       | I/O   | Receive Frame Sync (Serial Ports 0, 1).                                                                                                                                                                                                                                                                                                                                                                                                                  |

| LxDAT7-0   | I/O   | Link Port Data (Link Ports 0–5). Each LxDAT pin has a 50 k $\Omega$ internal pull-down resistor that is enabled or disabled by the LPDRD bit of the LCTL0–1 register.                                                                                                                                                                                                                                                                                    |

| LxCLK      | I/O   | Link Port Clock (Link Ports 0–5). Each LxCLK pin has a 50 k $\Omega$ internal pull-down resistor that is enabled or disabled by the LPDRD bit of the LCTL0–1 register.                                                                                                                                                                                                                                                                                   |

| LxACK      | I/O   | Link Port Acknowledge (Link Ports 0–5). Each LxACK pin has a 50 k $\Omega$ internal pull-down resistor that is enabled or disabled by the LPDRD bit of the LCOM register.                                                                                                                                                                                                                                                                                |

| EBOOT      | 1     | EPROM Boot Select. For a description of how this pin operates, see Table 4. This signal is a system configuration selection that should be hardwired.                                                                                                                                                                                                                                                                                                    |

| LBOOT      | I     | Link Boot. For a description of how this pin operates, see Table 4. This signal is a system configuration selection that should be hardwired.                                                                                                                                                                                                                                                                                                            |

| BMS        | I/O/T | Boot Memory Select. Serves as an output or input as selected with the EBOOT and LBOOT pins; see Table 4. This input is a system configuration selection that should be hardwired.                                                                                                                                                                                                                                                                        |

| CLKIN      | 1     | Local Clock In. CLKIN is the ADSP-21160x clock input. The ADSP-21160x external port cycles at the frequency of CLKIN. The instruction cycle rate is a multiple of the CLKIN frequency; it is programmable at power-up. CLKIN may not be halted, changed, or operated below the specified frequency.                                                                                                                                                      |

| CLK_CFG3-0 | I     | Core/CLKIN Ratio Control. ADSP-21160x core clock (instruction cycle) rate is equal to n x CLKIN where n is user-selectable to 2, 3, or 4, using the CLK_CFG3–0 inputs. For clock configuration definitions, see the <i>RESET &amp; CLKIN</i> section of the <i>System Design</i> chapter of the <i>ADSP-21160 SHARC DSP</i> Hardware Reference.                                                                                                          |

## Table 3. Pin Function Descriptions (Continued)

| Table 3. | <b>Pin Function I</b> | Descriptions | (Continued) |

|----------|-----------------------|--------------|-------------|

|----------|-----------------------|--------------|-------------|

| Pin                | Туре    | Function                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKOUT             | 0/Т     | Local Clock Out. CLKOUT is driven at the CLKIN frequency by the processor. This output can be three-stated by setting the COD bit in the SYSCON register. A keeper latch on the DSP's CLKOUT pin maintains the output at the level it was last driven (only enabled on the processor with ID2-0 = 00x). Do not use CLKOUT in multiprocessing systems; use CLKIN instead. |

| RESET              | I/A     | Processor Reset. Resets the ADSP-21160x to a known state and begins execution at the program memory location specified by the hardware reset vector address. The RESET input must be asserted (low) at power-up.                                                                                                                                                         |

| ТСК                | I       | Test Clock (JTAG). Provides a clock for JTAG boundary scan.                                                                                                                                                                                                                                                                                                              |

| TMS                | I/S     | Test Mode Select (JTAG). Used to control the test state machine. TMS has a 20 $k\Omega$ internal pull-up resistor.                                                                                                                                                                                                                                                       |

| TDI                | I/S     | Test Data Input (JTAG). Provides serial data for the boundary scan logic. TDI has a 20 k $\Omega$ internal pull-up resistor.                                                                                                                                                                                                                                             |

| TDO                | 0       | Test Data Output (JTAG). Serial scan output of the boundary scan path.                                                                                                                                                                                                                                                                                                   |

| TRST               | I/A     | Test Reset (JTAG). Resets the test state machine. TRST must be asserted (pulsed low) after power-<br>up or held low for proper operation of the ADSP-21160x. TRST has a 20 k $\Omega$ internal pull-up resistor.                                                                                                                                                         |

| EMU                | O (O/D) | Emulation Status. Must be connected to the ADSP-21160x emulator target board connector only. EMU has a 50 k $\Omega$ internal pull-up resistor.                                                                                                                                                                                                                          |

| CIF                | 0/Т     | Core Instruction Fetch. Signal is active low when an external instruction fetch is performed. Driven by bus master only. Three-state when host is bus master. $\overline{\text{CIF}}$ has a 20 k $\Omega$ internal pull-up resistor that is enabled on the ADSP-21160x with ID2–0 = 00x.                                                                                 |

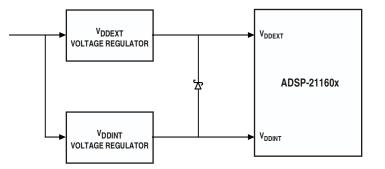

| V <sub>DDINT</sub> | Р       | Core Power Supply. Nominally 2.5 V (ADSP-21160M) or 1.9 V (ADSP-21160N) dc and supplies the DSP's core processor                                                                                                                                                                                                                                                         |

| V <sub>DDEXT</sub> | Р       | I/O Power Supply. Nominally 3.3 V dc.                                                                                                                                                                                                                                                                                                                                    |

| AV <sub>DD</sub>   | Ρ       | Analog Power Supply. Nominally 2.5 V (ADSP-21160M) or 1.9 V (ADSP-21160N) dc and supplies the DSP's internal PLL (clock generator). This pin has the same specifications as V <sub>DDINT</sub> , except that added filtering circuitry is required. For more information, see Power Supplies on page 9.                                                                  |

| AGND               | G       | Analog Power Supply Return.                                                                                                                                                                                                                                                                                                                                              |

| GND                | G       | Power Supply Return.                                                                                                                                                                                                                                                                                                                                                     |

| NC                 |         | Do Not Connect. Reserved pins that must be left open and unconnected.                                                                                                                                                                                                                                                                                                    |

### Table 4. Boot Mode Selection

| EBOOT | LBOOT | BMS       | Booting Mode                                         |

|-------|-------|-----------|------------------------------------------------------|

| 1     | 0     | Output    | EPROM (Connect BMS to EPROM chip select.)            |

| 0     | 0     | 1 (Input) | Host Processor                                       |

| 0     | 1     | 1 (Input) | Link Port                                            |

| 0     | 0     | 0 (Input) | No Booting. Processor executes from external memory. |

| 0     | 1     | 0 (Input) | Reserved                                             |

| 1     | 1     | x (Input) | Reserved                                             |

## **ABSOLUTE MAXIMUM RATINGS**

Stresses at or above those listed in Table 9 (ADSP-21160M) and Table 10 (ADSP-21160N) may cause permanent damage to the product. These are stress ratings only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

| Table 9   | Absolute Maxim   | um Ratings—ADSP-2 | 21160M   |

|-----------|------------------|-------------------|----------|

| I auto J. | Trosofute Manine | um Ratingo ADOLA  | 21100101 |

| Parameter                                            | Rating                               |

|------------------------------------------------------|--------------------------------------|

| Internal (Core) Supply Voltage (V <sub>DDINT</sub> ) | –0.3 V to +3.0 V                     |

| Analog (PLL) Supply Voltage (A <sub>VDD</sub> )      | –0.3 V to +3.0 V                     |

| External (I/O) Supply Voltage (V <sub>DDEXT</sub> )  | –0.3 V to +4.6 V                     |

| Input Voltage                                        | -0.5 V to V <sub>DDEXT</sub> + 0.5 V |

| Output Voltage Swing                                 | -0.5 V to V <sub>DDEXT</sub> + 0.5 V |

| Load Capacitance                                     | 200 pF                               |

| Storage Temperature Range                            | –65°C to +150°C                      |

| Table 10. | Absolute Maximum R | atings—ADSP-21160N |

|-----------|--------------------|--------------------|

| Table IV. | nosolute maximum n | aungo              |

| Parameter                                            | Rating                               |

|------------------------------------------------------|--------------------------------------|

| Internal (Core) Supply Voltage (V <sub>DDINT</sub> ) | –0.3 V to +2.3 V                     |

| Analog (PLL) Supply Voltage (A <sub>VDD</sub> )      | –0.3 V to +2.3 V                     |

| External (I/O) Supply Voltage (V <sub>DDEXT</sub> )  | –0.3 V to +4.6 V                     |

| Input Voltage                                        | -0.5 V to V <sub>DDEXT</sub> + 0.5 V |

| Output Voltage Swing                                 | -0.5 V to V <sub>DDEXT</sub> + 0.5 V |

| Load Capacitance                                     | 200 pF                               |

| Storage Temperature Range                            | –65°C to +150°C                      |

## **ESD SENSITIVITY**

# ESD (electrostatic discharge sensitive device)

Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

## **PACKAGE INFORMATION**

The information presented in Figure 7 provides details about the package branding for the ADSP-21160M/ADSP-21160N processor. For a complete listing of product availability, see Ordering Guide on Page 58.

Figure 7. Typical Package Brand

### Table 11. Package Brand Information

| Brand Key | <b>Field Description</b>          |

|-----------|-----------------------------------|

| a         | ADSP-21160 Model (M or N)         |

| t         | Temperature Range                 |

| рр        | Package Type                      |

| Z         | <b>RoHS</b> Compliant Designation |

| сс        | See Ordering Guide                |

| ννννν.χ   | Assembly Lot Code                 |

| n.n       | Silicon Revision                  |

| #         | <b>RoHS</b> Compliant Designation |

| yyww      | Date Code                         |

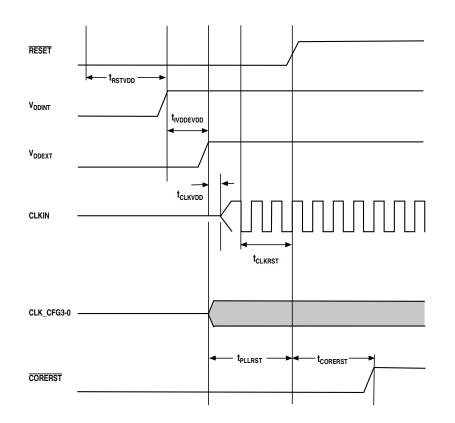

#### Table 12. Power-Up Sequencing

| Parameter             |                                                                               | Min                                 | Max  | Unit |

|-----------------------|-------------------------------------------------------------------------------|-------------------------------------|------|------|

| Timing Requi          | irements                                                                      |                                     |      |      |

| t <sub>RSTVDD</sub>   | RESET Low Before V <sub>DDINT</sub> /V <sub>DDEXT</sub> on                    | 0                                   |      | ns   |

| t <sub>IVDDEVDD</sub> | V <sub>DDINT</sub> on Before V <sub>DDEXT</sub>                               | - 50                                | +200 | ms   |

| t <sub>CLKVDD</sub>   | CLKIN Running After valid V <sub>DDINT</sub> /V <sub>DDEXT</sub> <sup>1</sup> | 0                                   | 200  | ms   |

| t <sub>CLKRST</sub>   | CLKIN Valid Before RESET Deasserted                                           | 10 <sup>2</sup>                     |      | μs   |

| t <sub>PLLRST</sub>   | PLL Control Setup Before RESET Deasserted                                     | 20 <sup>3</sup>                     |      | μs   |

| Switching Ch          | aracteristics                                                                 |                                     |      |      |

| t <sub>CORERST</sub>  | DSP Core Reset Deasserted After RESET Deasserted                              | 4096t <sub>CK</sub> <sup>3, 4</sup> |      |      |

<sup>1</sup> Valid V<sub>DDINT</sub>/V<sub>DDEXT</sub> assumes that the supplies are fully ramped to their V<sub>DDINT</sub> and V<sub>DDEXT</sub> rails. Voltage ramp rates can vary from microseconds to hundreds of milliseconds, depending on the design of the power supply subsystem.

<sup>2</sup> Assumes a stable CLKIN signal after meeting worst-case start-up timing of oscillators. Refer to your oscillator manufacturer's data sheet for start-up time. <sup>3</sup> Based on CLKIN cycles.

<sup>4</sup> CORERST is an internal signal only. The 4096 cycle count is dependent on t<sub>SRST</sub> specification. If setup time is not met, one additional CLKIN cycle may be added to the core reset time, resulting in 4097 cycles maximum.

Figure 8. Power-Up Sequencing

Figure 9. Dual Voltage Schottky Diode

### Clock Input

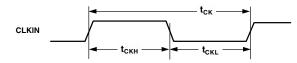

For clock input, see Table 13 and Figure 10.

### Table 13. Clock Input

|                   |                               |      | ADSP-21160M<br>80 MHz |     | ADSP-21160N<br>100 MHz |    |

|-------------------|-------------------------------|------|-----------------------|-----|------------------------|----|

| Parameter         |                               | Min  | Max                   | Min | Мах                    |    |

| Timing Red        | quirements                    |      |                       |     |                        |    |

| t <sub>CK</sub>   | CLKIN Period                  | 25   | 80                    | 20  | 80                     | ns |

| t <sub>CKL</sub>  | CLKIN Width Low               | 10.5 | 40                    | 7.5 | 40                     | ns |

| t <sub>CKH</sub>  | CLKIN Width High              | 10.5 | 40                    | 7.5 | 40                     | ns |

| t <sub>CKRF</sub> | CLKIN Rise/Fall (0.4 V-2.0 V) |      | 3                     |     | 3                      | ns |

| t <sub>CCLK</sub> | Core Clock Period             | 12.5 | 40                    | 10  | 30                     | ns |

Figure 10. Clock Input

#### Reset

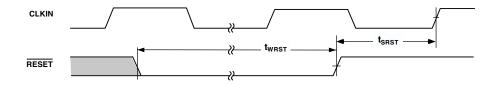

For reset, see Table 14 and Figure 11.

#### Table 14. Reset

| Parameter         |                                            | Min              | Max | Unit |

|-------------------|--------------------------------------------|------------------|-----|------|

| Timing Requ       | uirements                                  |                  |     |      |

| t <sub>WRST</sub> | RESET Pulsewidth Low <sup>1</sup>          | 4t <sub>CK</sub> |     | ns   |

| t <sub>SRST</sub> | RESET Setup Before CLKIN High <sup>2</sup> | 8                |     | ns   |

<sup>1</sup>Applies after the power-up sequence is complete. At power-up, the processor's internal phase-locked loop requires no more than 100 μs while RESET is low, assuming stable V<sub>DD</sub> and CLKIN (not including start-up time of external clock oscillator).

<sup>2</sup>Only required if multiple ADSP-21160x DSPs must come out of reset synchronous to CLKIN with program counters (PC) equal. Not required for multiple

ADSP-21160x DSPs communicating over the shared bus (through the external port), because the bus arbitration logic automatically synchronizes itself after reset.

Figure 11. Reset

### Interrupts

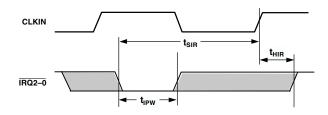

For interrupts, see Table 15 and Figure 12.

### Table 15. Interrupts

| Paramete         | Parameter                                   |                   | Max | Unit |

|------------------|---------------------------------------------|-------------------|-----|------|

| Timing Rec       | quirements                                  |                   |     |      |

| t <sub>SIR</sub> | IRQ2–0 Setup Before CLKIN High <sup>1</sup> | 6                 |     | ns   |

| t <sub>HIR</sub> | IRQ2–0 Hold After CLKIN High <sup>1</sup>   | 0                 |     | ns   |

| t <sub>IPW</sub> | IRQ2-0 Pulsewidth <sup>2</sup>              | 2+t <sub>CK</sub> |     | ns   |

<sup>1</sup>Only required for  $\overline{IRQx}$  recognition in the following cycle.

$^2$  Applies only if  $t_{SIR}$  and  $t_{HIR}$  requirements are not met.

Figure 12. Interrupts

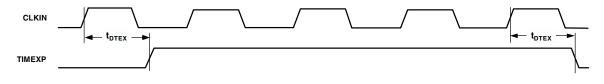

### Timer

For timer, see Table 16 and Figure 13.

#### Table 16. Timer

| Parameter         |                                   | Min | Max | Unit |

|-------------------|-----------------------------------|-----|-----|------|

| Switching Ch      | haracteristic                     |     |     |      |

| t <sub>DTEX</sub> | CLKIN High to TIMEXP <sup>1</sup> | 1   | 9   | ns   |

<sup>1</sup> For ADSP-21160M, specification is 7 ns, maximum.

Figure 13. Timer

### Memory Read—Bus Master

Use these specifications for asynchronous interfacing to memories (and memory-mapped peripherals) without reference to CLKIN except for the ACK pin requirements listed in note 6

### Table 18. Memory Read—Bus Master

of Table 18. These specifications apply when the ADSP-21160x is the bus master accessing external memory space in asynchronous access mode.

| Parameter         |                                                                 | Min                            | Max                               | Unit |

|-------------------|-----------------------------------------------------------------|--------------------------------|-----------------------------------|------|

| Timing Requi      | irements                                                        |                                |                                   |      |

| t <sub>DAD</sub>  | Address, CIF, Selects Delay to Data Valid <sup>1, 2, 3, 4</sup> |                                | $t_{CK} - 0.25t_{CCLK} - 8.5 + W$ | ns   |

| t <sub>DRLD</sub> | RDx Low to Data Valid <sup>1, 4, 5</sup>                        |                                | $t_{CK} - 0.5t_{CCLK} + W$        | ns   |

| HDA               | Data Hold from Address, Selects <sup>6</sup>                    | 0                              |                                   | ns   |

| SDS               | Data Setup to RDx High <sup>1</sup>                             | 8                              |                                   | ns   |

| HDRH              | Data Hold from RDx High <sup>6</sup>                            | 1                              |                                   | ns   |

| DAAK              | ACK Delay from Address, Selects <sup>2, 7</sup>                 |                                | $t_{CK} - 0.5t_{CCLK} - 12 + W$   | ns   |

| DSAK              | ACK Delay from RDx Low <sup>7</sup>                             |                                | $t_{CK} - 0.75t_{CCLK} - 11 + W$  | ns   |

| SAKC              | ACK Setup to CLKIN <sup>7</sup>                                 | 0.5t <sub>CCLK</sub> +3        |                                   | ns   |

| НАКС              | ACK Hold After CLKIN                                            | 1                              |                                   | ns   |

| witching Ch       | aracteristics                                                   |                                |                                   |      |

| DRHA              | Address, CIF, Selects Hold After RDx High                       | $0.25t_{CCLK} - 1 + H$         |                                   | ns   |

| DARL              | Address, CIF, Selects to RDx Low <sup>2</sup>                   | 0.25t <sub>CCLK</sub> – 3      |                                   | ns   |

| RW                | RDx Pulsewidth                                                  | $t_{CK} - 0.5t_{CCLK} - 1 + W$ |                                   | ns   |

| RWR               | RDx High to WRx, RDx, DMAGx Low                                 | 0.5t <sub>CCLK</sub> – 1 + HI  |                                   | ns   |

W = (number of wait states specified in WAIT register)  $\times$  t<sub>CK</sub>.

$HI = t_{CK}$  (if an address hold cycle or bus idle cycle occurs, as specified in WAIT register; otherwise HI = 0).

$H = t_{CK}$  (if an address hold cycle occurs as specified in WAIT register; otherwise H = 0).

$^1$  Data Delay/Setup: User must meet  $t_{\text{DAD}},\,t_{\text{DRLD}},\,\text{or}\,t_{\text{SDS}}.$

<sup>2</sup> The falling edge of  $\overline{MSx}$ ,  $\overline{BMS}$  is referenced.

$^3$  For ADSP-21160M, specification is  $t_{CK}\mbox{--}0.25t_{CCLK}\mbox{--}11\mbox{+}W$  ns, maximum.

<sup>4</sup>The maximum limit of timing requirement values for t<sub>DAD</sub> and t<sub>DRLD</sub> parameters are applicable for the case where AMI\_ACK is always high.

<sup>5</sup> For ADSP-21160M, specification is 0.75t<sub>CK</sub>-11+W ns, maximum.

<sup>6</sup> Data Hold: User must meet t<sub>HDA</sub> or t<sub>HDRH</sub> in asynchronous access mode. See Example System Hold Time Calculation on page 49 for the calculation of hold times given capacitive and dc loads.

<sup>7</sup> For asynchronous access, ACK is sampled only after the programmed wait states for the access have been counted. For the first CLKIN cycle of a new external memory access, ACK must be driven low (deasserted) by t<sub>DAAK</sub>, t<sub>DSAK</sub>, or t<sub>SAKC</sub>. For the second and subsequent cycles of an asynchronous external memory access, the t<sub>SAKC</sub> and t<sub>HAKC</sub> must be met for both assertion and deassertion of ACK signal.

#### Memory Write—Bus Master

Use these specifications for asynchronous interfacing to memories (and memory-mapped peripherals) without reference to CLKIN except for the ACK pin requirements listed in note 1

#### Table 19. Memory Write—Bus Master

of Table 19. These specifications apply when the ADSP-21160x is the bus master accessing external memory space in asynchronous access mode.

| Parameter           |                                                                                               | Min                             | Мах                               | Unit |

|---------------------|-----------------------------------------------------------------------------------------------|---------------------------------|-----------------------------------|------|

| Timing Requ         | irements                                                                                      |                                 |                                   |      |

| t <sub>DAAK</sub>   | ACK Delay from Address, Selects <sup>1, 2</sup>                                               |                                 | $t_{CK} - 0.5t_{CCLK} - 12 + W$   | ns   |

| t <sub>DSAK</sub>   | ACK Delay from WRx Low <sup>1</sup>                                                           |                                 | $t_{CK} - 0.75 t_{CCLK} - 11 + W$ | ns   |

| t <sub>SAKC</sub>   | ACK Setup to CLKIN <sup>1</sup>                                                               | 0.5t <sub>CCLK</sub> +3         |                                   | ns   |

| t <sub>HAKC</sub>   | ACK Hold After CLKIN <sup>1</sup>                                                             | 1                               |                                   | ns   |

| Switching Ch        | paracteristics                                                                                |                                 |                                   |      |

| t <sub>DAWH</sub>   | Address, $\overline{\text{CIF}}$ , Selects to $\overline{\text{WRx}}$ Deasserted <sup>2</sup> | $t_{CK} - 0.25t_{CCLK} - 3 + W$ |                                   | ns   |

| t <sub>DAWL</sub>   | Address, CIF, Selects to WRx Low <sup>2</sup>                                                 | 0.25t <sub>CCLK</sub> -3        |                                   | ns   |

| t <sub>ww</sub>     | WRx Pulsewidth                                                                                | $t_{CK} - 0.5t_{CCLK} - 1 + W$  |                                   | ns   |

| t <sub>DDWH</sub>   | Data Setup before WRx High <sup>3</sup>                                                       | $t_{CK} - 0.5t_{CCLK} - 1 + W$  |                                   | ns   |

| t <sub>DWHA</sub>   | Address Hold after WRx Deasserted                                                             | $0.25t_{CCLK} - 1 + H$          |                                   | ns   |

| t <sub>DWHD</sub>   | Data Hold after WRx Deasserted                                                                | 0.25t <sub>CCLK</sub> -1+H      |                                   | ns   |

| t <sub>DATRWH</sub> | Data Disable after WRx Deasserted <sup>4</sup>                                                | 0.25t <sub>CCLK</sub> -2+H      | $0.25t_{CCLK}+2+H$                | ns   |

| t <sub>WWR</sub>    | WRx High to WRx, RDx, DMAGx Low                                                               | $0.5t_{CCLK} - 1 + HI$          |                                   | ns   |

| t <sub>DDWR</sub>   | Data Disable before WRx or RDx Low                                                            | 0.25t <sub>CCLK</sub> – 1 + I   |                                   | ns   |

| t <sub>WDE</sub>    | WRx Low to Data Enabled                                                                       | -0.25t <sub>CCLK</sub> -1       |                                   | ns   |

W = (number of wait states specified in WAIT register)  $\times$  t<sub>CK</sub>.

$H = t_{CK}$  (if an address hold cycle occurs, as specified in WAIT register; otherwise H = 0).

$HI = t_{CK}$  (if an address hold cycle or bus idle cycle occurs, as specified in WAIT register; otherwise HI = 0).

$I = t_{CK}$  (if a bus idle cycle occurs, as specified in WAIT register; otherwise I = 0).

<sup>1</sup> For asynchronous access, ACK is sampled only after the programmed wait states for the access have been counted. For the first CLKIN cycle of a new external memory access, ACK must be driven low (deasserted) by t<sub>DAAK</sub> or t<sub>DSAK</sub> or t<sub>DSAK</sub>

<sup>2</sup> The falling edge of  $\overline{\text{MSx}}$ ,  $\overline{\text{BMS}}$  is referenced.

$^3$  For ADSP-21160M, specification is  $t_{CK}\text{--}0.25t_{CCLK}\text{--}12.5\text{+}W$  ns, minimum.

<sup>4</sup> See Example System Hold Time Calculation on Page 49 for calculation of hold times given capacitive and dc loads.

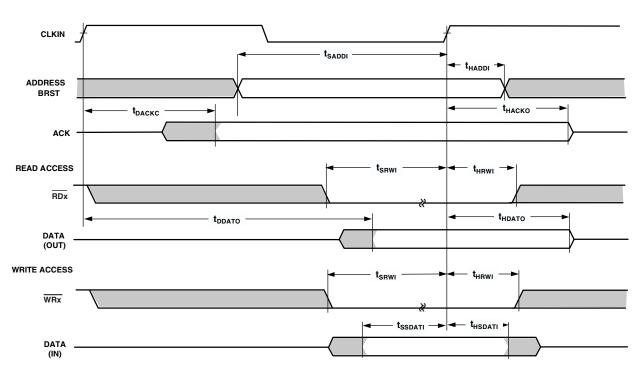

### Synchronous Read/Write—Bus Slave

See Table 21 and Figure 18. Use these specifications for ADSP-21160x bus master accesses of a slave's IOP registers or internal memory (in multiprocessor memory space). The bus master must meet these (bus slave) timing requirements.

### Table 21. Synchronous Read/Write—Bus Slave

| Parameter           |                                     | Min Max               | Unit               |

|---------------------|-------------------------------------|-----------------------|--------------------|

| Timing Requ         | irements                            |                       |                    |

| t <sub>SADDI</sub>  | Address, BRST Setup Before CLKIN    | 5                     | ns                 |

| t <sub>haddi</sub>  | Address, BRST Hold After CLKIN      | 1                     | ns                 |

| t <sub>srwi</sub>   | RDx/WRx Setup Before CLKIN          | 5                     | ns                 |

| t <sub>HRWI</sub>   | RDx/WRx Hold After CLKIN            | 1                     | ns                 |

| t <sub>ssdati</sub> | Data Setup Before CLKIN             | 5.5                   | ns                 |

| t <sub>HSDATI</sub> | Data Hold After CLKIN               | 1                     | ns                 |

| Switching Cł        | naracteristics                      |                       |                    |

| t <sub>DDATO</sub>  | Data Delay After CLKIN <sup>1</sup> | 0.25 t <sub>CCL</sub> | <sub>K</sub> +9 ns |

| t <sub>HDATO</sub>  | Data Hold After CLKIN               | 1.5                   | ns                 |

| t <sub>DACKC</sub>  | ACK Delay After CLKIN               | 10                    | ns                 |

| t <sub>HACKO</sub>  | ACK Hold After CLKIN                | 1.5                   | ns                 |

<sup>1</sup> For ADSP-21160M, specification is 12.5 ns, maximum.

Figure 18. Synchronous Read/Write—Bus Slave

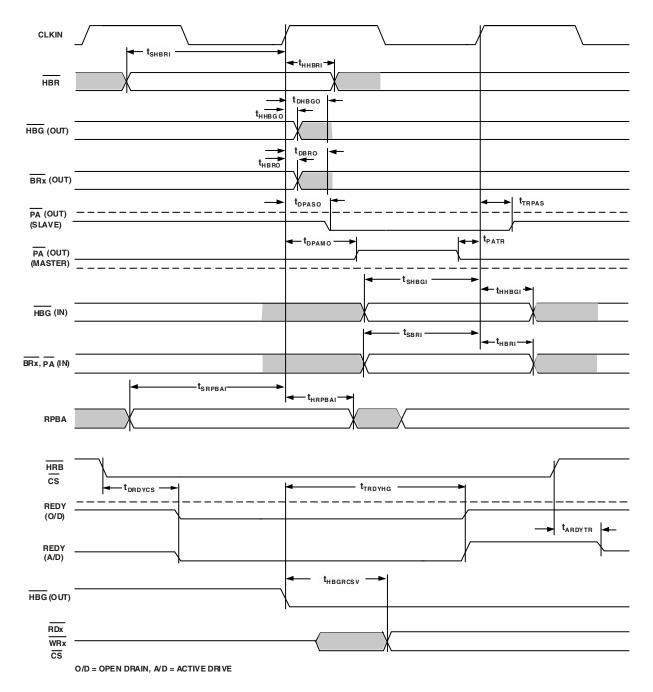

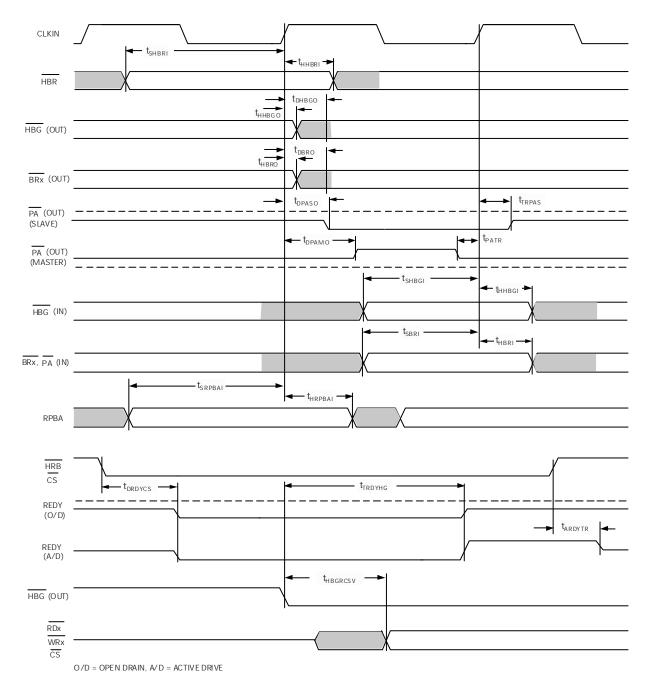

Figure 19. Multiprocessor Bus Request and Host Bus Request

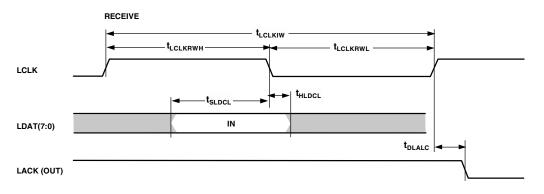

#### Link Ports—Receive, Transmit

For link ports, see Table 27, Table 28, Figure 24, and Figure 25. Calculation of link receiver data setup and hold, relative to link clock, is required to determine the maximum allowable skew that can be introduced in the transmission path, between LDATA and LCLK. Setup skew is the maximum delay that can be introduced in LDATA, relative to LCLK (setup skew =  $t_{LCLKTWH}$  minimum –  $t_{DLDCH}$  –  $t_{SLDCL}$ ). Hold skew is the

Table 27. Link Ports-Receive

maximum delay that can be introduced in LCLK, relative to LDATA (hold skew =  $t_{LCLKTWL}$  minimum +  $t_{HLDCH}$  –  $t_{HLDCL}$ ). Calculations made directly from speed specifications result in unrealistically small skew times, because they include multiple tester guardbands.

Note that there is a two-cycle effect latency between the link port enable instruction and the DSP enabling the link port.

| Parameter            |                                                | Min               | Max | Unit |

|----------------------|------------------------------------------------|-------------------|-----|------|

| Timing Requi         | rements                                        |                   |     |      |

| t <sub>sldcl</sub>   | Data Setup Before LCLK Low                     | 2.5               |     | ns   |

| t <sub>HLDCL</sub>   | Data Hold After LCLK Low <sup>1</sup>          | 3                 |     | ns   |

| t <sub>LCLKIW</sub>  | LCLK Period                                    | t <sub>LCLK</sub> |     | ns   |

| t <sub>LCLKRWL</sub> | LCLK Width Low <sup>2</sup>                    | 4                 |     | ns   |

| t <sub>LCLKRWH</sub> | LCLK Width High <sup>3</sup>                   | 4                 |     | ns   |

| Switching Ch         | aracteristics                                  |                   |     |      |

| t <sub>DLALC</sub>   | LACK Low Delay After LCLK High <sup>4, 5</sup> | 9                 | 17  | ns   |

<sup>1</sup> For ADSP-21160M, specification is 2.5 ns, minimum.

<sup>2</sup> For ADSP-21160M, specification is 6 ns, minimum.

<sup>3</sup> For ADSP-21160M, specification is 6 ns, minimum.

<sup>4</sup> LACK goes low with t<sub>DLALC</sub> relative to rise of LCLK after first nibble, but does not go low if the receiver's link buffer is not about to fill.

<sup>5</sup> For ADSP-21160M, specification is 12 ns, minimum.

Figure 24. Link Ports—Receive

Figure 19. Multiprocessoret and Host Bus Request