Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at90s4414-4ac |

|----------------------------|-------------------------------------------------------------------------|

| Supplier Device Package    | 44-TQFP (10x10)                                                         |

| Package / Case             | 44-TQFP                                                                 |

| Mounting Type              | Surface Mount                                                           |

| Operating Temperature      | 0°C ~ 70°C                                                              |

| Oscillator Type            | Internal                                                                |

| Data Converters            | -                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 6V                                                               |

| RAM Size                   | 256 x 8                                                                 |

| EEPROM Size                | 256 x 8                                                                 |

| Program Memory Type        | FLASH                                                                   |

| Program Memory Size        | 4KB (2K x 16)                                                           |

| Number of I/O              | 32                                                                      |

| Peripherals                | PWM, WDT                                                                |

| Connectivity               | SPI, UART/USART                                                         |

| Speed                      | 4MHz                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Core Processor             | AVR                                                                     |

| Product Status             | Obsolete                                                                |

| Details                    |                                                                         |

The AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The AT90S4414/8515 provides the following features: 4K/8K bytes of In-System Programmable Flash, 256/512 bytes EEPROM, 256/512 bytes SRAM, 32 general purpose I/O lines, 32 general purpose working registers, flexible timer/counters with compare modes, internal and external interrupts, a programmable serial UART, programmable Watchdog Timer with internal oscillator, an SPI serial port and two software selectable power saving modes. The Idle Mode stops the CPU while allowing the SRAM, timer/counters, SPI port and interrupt system to continue functioning. The power down mode saves the register contents but freezes the oscillator, disabling all other chip functions until the next external interrupt or hardware reset.

The device is manufactured using Atmel's high density nonvolatile memory technology. The on-chip in-system programmable Flash allows the program memory to be reprogrammed in-system through an SPI serial interface or by a conventional nonvolatile memory programmer. By combining an enhanced RISC 8-bit CPU with In-System Programmable Flash on a monolithic chip, the Atmel AT90S4414/8515 is a powerful microcontroller that provides a highly flexible and cost effective solution to many embedded control applications.

The AT90S4414/8515 AVR is supported with a full suite of program and system development tools including: C compilers, macro assemblers, program debugger/simulators, in-circuit emulators, and evaluation kits.

# Comparison Between AT90S4414 and AT90S8515

The AT90S4414 has 4K bytes of In-System Programmable Flash, 256 bytes of EEPROM and 256 bytes of internal SRAM. The AT90S8515 has 8K bytes of In-System Programmable Flash, 512 bytes of EEPROM and 512 bytes of internal SRAM. Table 1 summarizes the different memory sizes for the two devices.

Table 1. Memory Size Summary

| Part      | Flash    | EEPROM    | SRAM      |

|-----------|----------|-----------|-----------|

| AT90S4414 | 4K bytes | 256 bytes | 256 bytes |

| AT90S8515 | 8K bytes | 512 bytes | 512 bytes |

# **Pin Descriptions**

VCC

Supply voltage

**GND**

Ground

#### Port A (PA7..PA0)

Port A is an 8-bit bidirectional I/O port. Port pins can provide internal pull-up resistors (selected for each bit). The Port A output buffers can sink 20mA and can drive LED displays directly. When pins PA0 to PA7 are used as inputs and are externally pulled low, they will source current if the internal pull-up resistors are activated. The Port A pins are tri-stated when a reset condition becomes active, even if the clock is not active.

Port A serves as Multiplexed Address/Data input/output when using external SRAM.

A flexible interrupt module has its control registers in the I/O space with an additional global interrupt enable bit in the status register. All the different interrupts have a separate interrupt vector in the interrupt vector table at the beginning of the program memory. The different interrupts have priority in accordance with their interrupt vector position. The lower the interrupt vector address the higher the priority.

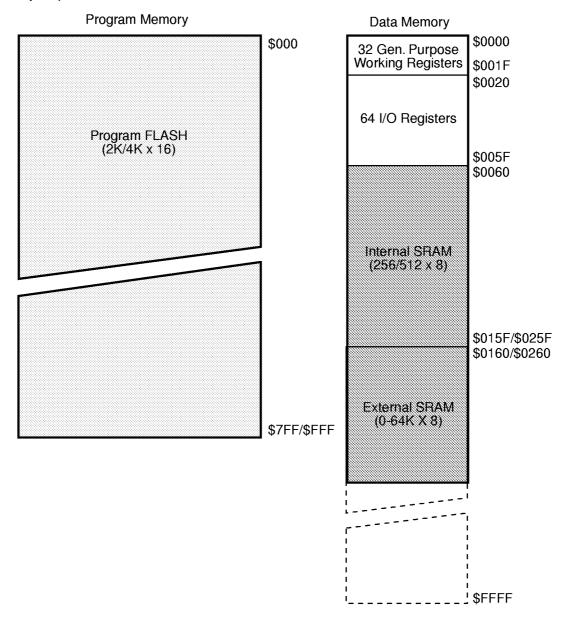

Figure 5. Memory Maps

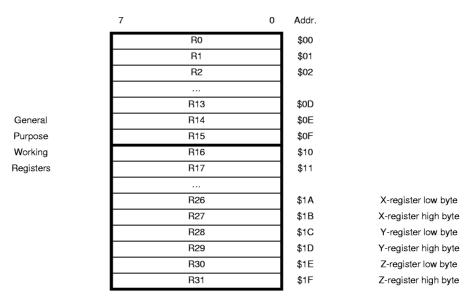

## **General Purpose Register File**

Figure 6 shows the structure of the 32 general purpose working registers in the CPU.

Figure 6. AVR CPU General Purpose Working Registers

All the register operating instructions in the instruction set have direct and single cycle access to all registers. The only exception is the five constant arithmetic and logic instructions SBCI, SUBI, CPI, ANDI and ORI between a constant and a register and the LDI instruction for load immediate constant data. These instructions apply to the second half of the registers in the register file - R16..R31. The general SBC, SUB, CP, AND and OR and all other operations between two registers or on a single register apply to the entire register file.

As shown in Figure 6, each register is also assigned a data memory address, mapping them directly into the first 32 locations of the user Data Space. Although not being physically implemented as SRAM locations, this memory organization provides great flexibility in access of the registers, as the X,Y and Z registers can be set to index any register in the file.

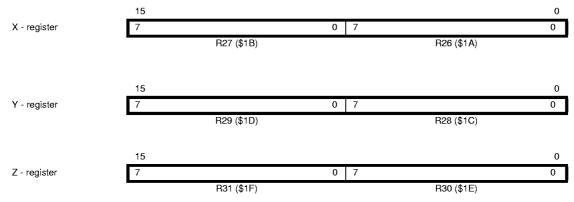

#### X-Register, Y-Register And Z-Register

The registers R26..R31 have some added functions to their general purpose usage. These registers are address pointers for indirect addressing of the Data Space. The three indirect address registers X, Y and Z are defined as:

Figure 7. X, Y and Z Registers

In the different addressing modes these address registers have functions as fixed displacement, automatic increment and decrement (see the descriptions for the different instructions).

# **ALU - Arithmetic Logic Unit**

The high-performance AVR ALU operates in direct connection with all the 32 general purpose working registers. Within a single clock cycle, ALU operations between registers in the register file are executed. The ALU operations are divided into three main categories - arithmetic, logical and bit-functions.

# **In-System Programmable Flash Program Memory**

The AT90S4414/8515 contains 4K/8K bytes on-chip In-System Programmable Flash memory for program storage. Since all instructions are 16-or 32-bit words, the Flash is organized as 2K x 16/4K x 16. The Flash memory has an endurance of at least 1000 write/erase cycles. The AT90S4414/8515 Program Counter (PC) is 11/12 bits wide, thus addressing the 2048/4096 program memory addresses.

See page 77 for a detailed description on Flash data downloading.

See page 10 for the different program memory addressing modes.

# **SRAM Data Memory - Internal and External**

The following figure shows how the AT90S4414/8515 SRAM Memory is organized:

Figure 8. SRAM Organization

| Register File | Data Address Space             |

|---------------|--------------------------------|

| R0            | \$0000                         |

| R1            | \$0001                         |

| R2            | \$0002                         |

|               |                                |

| R29           | \$001D                         |

| R30           | \$001E                         |

| R31           | \$001F                         |

| I/O Registers |                                |

| \$00          | \$0020                         |

| \$01          | \$0021                         |

| \$02          | \$0022                         |

|               |                                |

| \$3D          | \$005D                         |

| \$3E          | \$005E                         |

| \$3F          | \$005F                         |

|               | Internal SRAM                  |

|               | \$0060                         |

|               | \$0061                         |

|               | **                             |

|               | \$015E/\$025E                  |

|               | <b>\$</b> 015F/ <b>\$</b> 025F |

|               | External SRAM                  |

|               | \$0160/\$0260                  |

|               | \$0161/\$0261                  |

|               | ***                            |

|               | \$FFFE                         |

|               | \$FFFF                         |

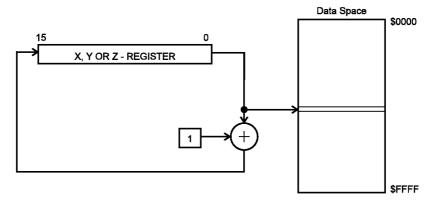

#### **Data Indirect with Post-increment**

Figure 16. Data Indirect Addressing with Post-increment

The X, Y or the Z-register is incremented after the operation. Operand address is the content of the X, Y or the Z-register prior to incrementing.

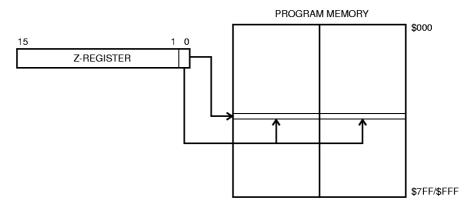

# **Constant Addressing Using the LPM Instruction**

Figure 17. Code Memory Constant Addressing

Constant byte address is specified by the Z-register contents. The 15 MSBs select word address (0 - 2K/4K), the LSB selects low byte if cleared (LSB = 0) or high byte if set (LSB = 1).

# I/O Memory

The I/O space definition of the AT90S4414/8515 is shown in the following table:

**Table 2.** AT90S4414/8515 I/O Space

| Address Hex | Name   | Function                                           |

|-------------|--------|----------------------------------------------------|

| \$3F (\$5F) | SREG   | Status Register                                    |

| \$3E (\$5E) | SPH    | Stack Pointer High                                 |

| \$3D (\$5D) | SPL    | Stack Pointer Low                                  |

| \$3B (\$5B) | GIMSK  | General Interrupt Mask register                    |

| \$3A (\$5A) | GIFR   | General Interrupt Flag Register                    |

| \$39 (\$59) | TIMSK  | Timer/Counter Interrupt Mask register              |

| \$38 (\$58) | TIFR   | Timer/Counter Interrupt Flag register              |

| \$35 (\$55) | MCUCR  | MCU general Control Register                       |

| \$33 (\$53) | TCCR0  | Timer/Counter0 Control Register                    |

| \$32 (\$52) | TCNT0  | Timer/Counter0 (8-bit)                             |

| \$2F (\$4F) | TCCR1A | Timer/Counter1 Control Register A                  |

| \$2E (\$4E) | TCCR1B | Timer/Counter1 Control Register B                  |

| \$2D (\$4D) | TCNT1H | Timer/Counter1 High Byte                           |

| \$2C (\$4C) | TCNT1L | Timer/Counter1 Low Byte                            |

| \$2B (\$4B) | OCR1AH | Timer/Counter1 Output Compare Register A High Byte |

| \$2A (\$4A) | OCR1AL | Timer/Counter1 Output Compare Register A Low Byte  |

| \$29 (\$49) | OCR1BH | Timer/Counter1 Output Compare Register B High Byte |

| \$28 (\$48) | OCR1BL | Timer/Counter1 Output Compare Register B Low Byte  |

| \$25 (\$45) | ICR1H  | T/C 1 Input Capture Register High Byte             |

| \$24 (\$44) | ICR1L  | T/C 1 Input Capture Register Low Byte              |

| \$21 (\$41) | WDTCR  | Watchdog Timer Control Register                    |

| \$1F (\$3E) | EEARH  | EEPROM Address Register High Byte (AT90S8515)      |

| \$1E (\$3E) | EEARL  | EEPROM Address Register Low Byte                   |

| \$1D (\$3D) | EEDR   | EEPROM Data Register                               |

| \$1C (\$3C) | EECR   | EEPROM Control Register                            |

| \$1B (\$3B) | PORTA  | Data Register, Port A                              |

| \$1A (\$3A) | DDRA   | Data Direction Register, Port A                    |

| \$19 (\$39) | PINA   | Input Pins, Port A                                 |

| \$18 (\$38) | PORTB  | Data Register, Port B                              |

| \$17 (\$37) | DDRB   | Data Direction Register, Port B                    |

| \$16 (\$36) | PINB   | Input Pins, Port B                                 |

| \$15 (\$35) | PORTC  | Data Register, Port C                              |

| \$14 (\$34) | DDRC   | Data Direction Register, Port C                    |

| \$13 (\$33) | PINC   | Input Pins, Port C                                 |

Table 3. Reset and Interrupt Vectors

| Vector No. | Program Address | Source       | Interrupt Definition                              |

|------------|-----------------|--------------|---------------------------------------------------|

| 1          | \$000           | RESET        | External Reset, Power-on Reset and Watchdog Reset |

| 2          | \$001           | INT0         | External Interrupt Request 0                      |

| 3          | \$002           | INT1         | External Interrupt Request 1                      |

| 4          | \$003           | TIMER1 CAPT  | Timer/Counter1 Capture Event                      |

| 5          | \$004           | TIMER1 COMPA | Timer/Counter1 Compare Match A                    |

| 6          | \$005           | TIMER1 COMPB | Timer/Counter1 Compare Match B                    |

| 7          | \$006           | TIMER1 OVF   | Timer/Counter1 Overflow                           |

| 8          | \$007           | TIMER0, OVF  | Timer/Counter0 Overflow                           |

| 9          | \$008           | SPI, STC     | Serial Transfer Complete                          |

| 10         | \$009           | UART, RX     | UART, Rx Complete                                 |

| 11         | \$00A           | UART, UDRE   | UART Data Register Empty                          |

| 12         | \$00B           | UART, TX     | UART, Tx Complete                                 |

| 13         | \$00C           | ANA_COMP     | Analog Comparator                                 |

# The most typical and general program setup for the Reset and Interrupt Vector Addresses are:

| Address | Labels | Code            |             | Comments                        |

|---------|--------|-----------------|-------------|---------------------------------|

| \$000   |        | rjmp            | RESET       | ; Reset Handler                 |

| \$001   |        | rjmp            | EXT_INTO    | ; IRQ0 Handler                  |

| \$002   |        | rjmp            | EXT_INT1    | ; IRQ1 Handler                  |

| \$003   |        | rjmp            | TIM1_CAPT   | ; Timerl Capture Handler        |

| \$004   |        | rjmp            | TIM1_COMPA  | ; Timer1 CompareA Handler       |

| \$005   |        | rjmp            | TIM1_COMPB  | ; Timerl CompareB Handler       |

| \$006   |        | rjmp            | TIM1_OVF    | ; Timer1 Overflow Handler       |

| \$007   |        | rjmp            | TIMO_OVF    | ; Timer0 Overflow Handler       |

| \$008   |        | rjmp            | SPI_STC     | ; SPI Transfer Complete Handler |

| \$009   |        | rjmp            | UART_RXC    | ; UART RX Complete Handler      |

| \$00a   |        | rjmp            | UART_DRE    | ; UDR Empty Handler             |

| \$00b   |        | rjmp            | UART_TXC    | ; UART TX Complete Handler      |

| \$00c   |        | rjmp            | ANA_COMP    | ; Analog Comparator Handler     |

| ;       |        |                 |             |                                 |

| \$00d   | MAIN:  | ldi r16         | ,high(RAMEN | D); Main program start          |

| \$00e   |        | out SPH         | ,r16        |                                 |

| \$00f   |        | ldi r16         | ,low(RAMEND | )                               |

| \$010   |        | out SPI         | ,r16        |                                 |

| \$011   |        | <instr></instr> | xxx         |                                 |

|         |        |                 |             |                                 |

|         |        |                 |             |                                 |

... ... ... ...

Table 7. Interrupt 0 Sense Control

| ISC01 | ISC00 | Description                                              |

|-------|-------|----------------------------------------------------------|

| 0     | 0     | The low level of INT0 generates an interrupt request.    |

| 0     | 1     | Reserved                                                 |

| 1     | 0     | The falling edge of INT0 generates an interrupt request. |

| 1     | 1     | The rising edge of INT0 generates an interrupt request.  |

Note: When changing the ISC01/ISC00 bits, INT0 must be disabled by clearing its Interrupt Enable bit in the GIMSK Register.

Otherwise an interrupt can occur when the bits are changed.

The value on the INTn pin is sampled before detecting edges. If edge interrupt is selected, pulses with a duration longer than one CPU clock period will generate an interrupt. Shorter pulses are not guaranteed to generate an interrupt. If low level interrupt is selected, the low level must be held until the completion of the currently executing instruction to generate an interrupt. If enabled, a level triggered interrupt will generate an interrupt request as long as the pin is held low.

### Sleep Modes

To enter the sleep modes, the SE bit in MCUCR must be set (one) and a SLEEP instruction must be executed. If an enabled interrupt occurs while the MCU is in a sleep mode, the MCU awakes, executes the interrupt routine, and resumes execution from the instruction following SLEEP. The contents of the register file, SRAM and I/O memory are unaltered. If a reset occurs during sleep mode, the MCU wakes up and executes from the Reset vector.

#### **Idle Mode**

When the SM bit is cleared (zero), the SLEEP instruction forces the MCU into the Idle Mode stopping the CPU but allowing Timer/Counters, Watchdog and the interrupt system to continue operating. This enables the MCU to wake up from external triggered interrupts as well as internal ones like Timer Overflow interrupt and watchdog reset. If wakeup from the Analog Comparator interrupt is not required, the analog comparator can be powered down by setting the ACD-bit in the Analog Comparator Control and Status register - ACSR. This will reduce power consumption in Idle Mode. When the MCU wakes up from Idle mode, the CPU starts program execution immediately.

#### **Power Down Mode**

When the SM bit is set (one), the SLEEP instruction forces the MCU into the Power Down Mode. In this mode, the external oscillator is stopped, while the external interrupts and the Watchdog (if enabled) continue operating. Only an external reset, a watchdog reset (if enabled), an external level interrupt on INT0 or INT1, can wake up the MCU.

Note that when a level triggered interrupt is used for wake-up from power down, the low level must be held for a time longer than the reset delay time-out period  $t_{TOLIT}$ . Otherwise, the MCU will fail to wake up.

# Timer/Counters

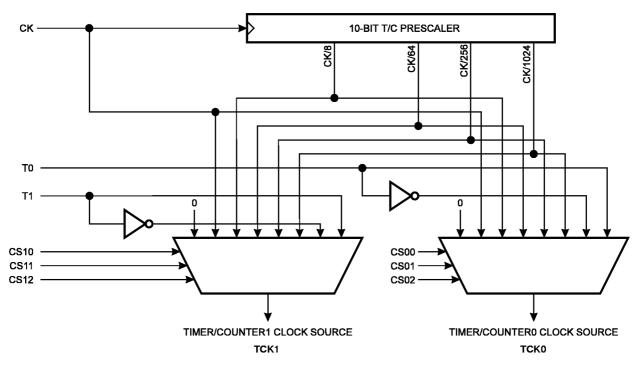

The AT90S4414/8515 provides two general purpose Timer/Counters - one 8-bit T/C and one 16-bit T/C. The Timer/Counters have individual prescaling selection from the same 10-bit prescaling timer. Both Timer/Counters can either be used as a timer with an internal clock timebase or as a counter with an external pin connection which triggers the counting.

#### **Timer/Counter Prescaler**

Figure 28 shows the general Timer/Counter prescaler.

Figure 28. Timer/Counter Prescaler

The four different prescaled selections are: CK/8, CK/64, CK/256 and CK/1024 where CK is the oscillator clock. For the two Timer/Counters, added selections as CK, external source and stop, can be selected as clock sources.

#### 8-bit Timer/Counter0

Figure 29 shows the block diagram for Timer/Counter0.

The 8-bit Timer/Counter0 can select clock source from CK, prescaled CK, or an external pin. In addition it can be stopped as described in the specification for the Timer/Counter0 Control Register - TCCR0. The overflow status flag is found in the Timer/Counter Insterrupt Flag Register - TIFR. Control signals are found in the Timer/Counter0 Control Register - TCCR0. The interrupt enable/disable settings for Timer/Counter0 are found in the Timer/Counter Interrupt Mask Register - TIMSK.

When Timer/Counter0 is externally clocked, the external signal is synchronized with the oscillator frequency of the CPU. To assure proper sampling of the external clock, the minimum time between two external clock transitions must be at least one internal CPU clock period. The external clock signal is sampled on the rising edge of the internal CPU clock.

The 8-bit Timer/Counter0 features both a high resolution and a high accuracy usage with the lower prescaling opportunities. Similarly, the high prescaling opportunities make the Timer/Counter0 useful for lower speed functions or exact timing functions with infrequent actions.

#### • Bit 3 - CTC1: Clear Timer/Counter1 on Compare Match

When the CTC1 control bit is set (one), the Timer/Counter1 is reset to \$0000 in the clock cycle after a compareA match. If the CTC1 control bit is cleared, Timer/Counter1 continues counting and is unaffected by a compare match. Since the compare match is detected in the CPU clock cycle following the match, this function will behave differently when a prescaling higher than 1 is used for the timer. When a prescaling of 1 is used, and the compareA register is set to C, the timer will count as follows if CTC1 is set:

When the prescaler is set to divide by 8, the timer will count like this:

In PWM mode, this bit has no effect.

#### • Bits 2,1,0 - CS12, CS11, CS10: Clock Select1, bit 2,1 and 0

The Clock Select1 bits 2,1 and 0 define the prescaling source of Timer/Counter1.

Table 11. Clock 1 Prescale Select

| CS12 | CS11 | CS10 | Description                          |

|------|------|------|--------------------------------------|

| 0    | 0    | 0    | Stop, the Timer/Counter1 is stopped. |

| 0    | 0    | 1    | СК                                   |

| 0    | 1    | 0    | CK/8                                 |

| 0    | 1    | 1    | CK/64                                |

| 1    | 0    | 0    | CK/256                               |

| 1    | 0    | 1    | CK/1024                              |

| 1    | 1    | 0    | External Pin T1, falling edge        |

| 1    | 1    | 1    | External Pin T1, rising edge         |

The Stop condition provides a Timer Enable/Disable function. The CK down divided modes are scaled directly from the CK oscillator clock. If the external pin modes are used for Timer/Counter1, transitions on PB1/(T1) will clock the counter even if the pin is configured as an output. This feature can give the user SW control of the counting.

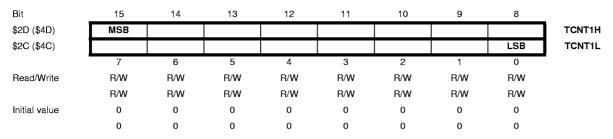

Timer/Counter1 - TCNT1H AND TCNT1L

This 16-bit register contains the prescaled value of the 16-bit Timer/Counter1. To ensure that both the high and low bytes are read and written simultaneously when the CPU accesses these registers, the access is performed using an 8-bit temporary register (TEMP). This temporary register is also used when accessing OCR1A, OCR1B and ICR1. If the main program and also interrupt routines perform access to registers using TEMP, interrupts must be disabled during access from the main program (and from interrupt routines if interrupts are allowed from within interrupt routines).

#### TCNT1 Timer/Counter1 Write:

When the CPU writes to the high byte TCNT1H, the written data is placed in the TEMP register. Next, when the CPU writes the low byte TCNT1L, this byte of data is combined with the byte data in the TEMP register, and all 16 bits are written to the TCNT1 Timer/Counter1 register simultaneously. Consequently, the high byte TCNT1H must be accessed first for a full 16-bit register write operation.

#### TCNT1 Timer/Counter1 Read:

When the CPU reads the low byte TCNT1L, the data of the low byte TCNT1L is sent to the CPU and the data of the high byte TCNT1H is placed in the TEMP register. When the CPU reads the data in the high byte TCNT1H, the CPU receives the data in the TEMP register. Consequently, the low byte TCNT1L must be accessed first for a full 16-bit register read operation.

The Timer/Counter1 is realized as an up or up/down (in PWM mode) counter with read and write access. If Timer/Counter1 is written to and a clock source is selected, the Timer/Counter1 continues counting in the timer clock cycle after it is preset with the written value.

#### Timer/Counter1 Output Compare Register - OCR1AH AND OCR1AL

| Bit           | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | _      |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|--------|

| \$2B (\$4B)   | MSB |     |     |     |     |     |     |     | OCR1AH |

| \$2A (\$4A)   |     |     |     |     |     |     |     | LSB | OCR1AL |

|               | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | •      |

| Read/Write    | R/W |        |

|               | R/W |        |

| Initial value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |        |

|               | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |        |

#### Timer/Counter1 Output Compare Register - OCR1BH AND OCR1BL

| Bit           | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |        |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|--------|

| \$29 (\$49)   | MSB |     |     |     |     |     |     |     | OCR1BH |

| \$28 (\$48)   |     |     |     |     |     |     |     | LSB | OCR1BL |

|               | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |        |

| Read/Write    | R/W |        |

|               | R/W |        |

| Initial value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |        |

|               | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |        |

The output compare registers are 16-bit read/write registers.

The Timer/Counter1 Output Compare Registers contain the data to be continuously compared with Timer/Counter1. Actions on compare matches are specified in the Timer/Counter1 Control and Status register. A compare match does only occur if Timer/Counter1 counts to the OCR value. A software write that sets TCNT1 and OCR1A or OCR1B to the same value does not generate a compare match.

A compare match will set the compare interrupt flag in the CPU clock cycle following the compare event.

Since the Output Compare Registers - OCR1A and OCR1B - are 16-bit registers, a temporary register TEMP is used when OCR1A/B are written to ensure that both bytes are updated simultaneously. When the CPU writes the high byte, OCR1AH or OCR1BH, the data is temporarily stored in the TEMP register. When the CPU writes the low byte, OCR1AL or OCR1BL, the TEMP register is simultaneously written to OCR1AH or OCR1BH. Consequently, the high byte OCR1AH or OCR1BH must be written first for a full 16-bit register write operation.

The TEMP register is also used when accessing TCNT1, and ICR1. If the main program and also interrupt routines perform access to registers using TEMP, interrupts must be disabled during access from the main program (and from interrupt routines if interrupts are allowed from within interrupt routines)..

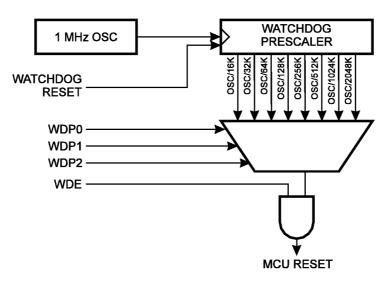

# **Watchdog Timer**

The Watchdog Timer is clocked from a separate on-chip oscillator which runs at 1MHz. This is the typical value at  $V_{CC} = 5V$ . See characterization data for typical values at other  $V_{CC}$  levels. By controlling the Watchdog Timer prescaler, the Watchdog reset interval can be adjusted, see Table 15 for a detailed description. The WDR - Watchdog Reset - instruction resets the Watchdog Timer. Eight different clock cycle periods can be selected to determine the reset period. If the reset period expires without another Watchdog reset, the AT90S4414/8515 resets and executes from the reset vector. For timing details on the Watchdog reset, refer to page 23.

To prevent unintentional disabling of the watchdog, a special turn-off sequence must be followed when the watchdog is disabled. Refer to the description of the Watchdog Timer Control Register for details.

Figure 33. Watchdog Timer

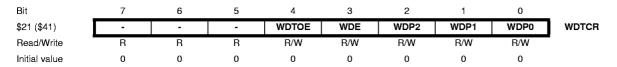

## Watchdog Timer Control Register - WDTCR

#### • Bits 7..5 - Res: Reserved bits

These bits are reserved bits in the AT90S4414/8515 and will always read as zero.

#### Bit 4 - WDTOE: Watch Dog Turn-Off Enable

This bit must be set (one) when the WDE bit is cleared. Otherwise, the watchdog will not be disabled. Once set, hardware will clear this bit to zero after four clock cycles. Refer to the description of the WDE bit for a watchdog disable procedure.

#### • Bit 3 - WDE: Watch Dog Enable

When the WDE is set (one) the Watchdog Timer is enabled, and if the WDE is cleared (zero) the Watchdog Timer function is disabled. WDE can only be cleared if the WDTOE bit is set(one). To disable an enabled watchdog timer, the following procedure must be followed:

- 1. In the same operation, write a logical one to WDTOE and WDE. A logical one must be written to WDE even though it is set to one before the disable operation starts.

- 2. Within the next four clock cycles, write a logical 0 to WDE. This disables the watchdog.

#### • Bits 2..0 - WDP2, WDP1, WDP0: Watch Dog Timer Prescaler 2, 1 and 0

The WDP2, WDP1 and WDP0 bits determine the Watchdog Timer prescaling when the Watchdog Timer is enabled. The different prescaling values and their corresponding Time-out Periods are shown in Table 15.

Table 15. Watch Dog Timer Prescale Select

| WDP2 | WDP1 | WDP0 | Number of WDT<br>Oscillator cycles | Typical Time-out<br>at V <sub>CC</sub> = 3.0V | Typical Time-out<br>at V <sub>CC</sub> = 5.0V |  |

|------|------|------|------------------------------------|-----------------------------------------------|-----------------------------------------------|--|

| 0    | 0    | 0    | 16K cycles                         | 47 ms                                         | 15 ms                                         |  |

| 0    | 0    | 1    | 32K cycles                         | 94 ms                                         | 30 ms                                         |  |

| 0    | 1    | 0    | 64K cycles                         | 0.19 s                                        | 60 ms                                         |  |

| 0    | 1    | 1    | 128K cycles                        | 0.38 s                                        | 0.12 s                                        |  |

| 1    | 0    | 0    | 256K cycles                        | 0.75 s                                        | 0,24 s                                        |  |

| 1    | 0    | 1    | 512K cycles                        | 1.5 s                                         | 0.49 s                                        |  |

| 1    | 1    | 0    | 1,024K cycles                      | 3.0 s                                         | 0.97 s                                        |  |

| 1    | 1    | 1    | 2,048K cycles                      | 6.0 s                                         | 1.9 s                                         |  |

Note: The frequency of the watchdog oscillator is voltage dependent as shown in the Electrical Characteristics section.

The WDR - Watchdog Reset - instruction should always be executed before the Watchdog Timer is enabled. This ensures that the reset period will be in accordance with the Watchdog Timer prescale settings. If the Watchdog Timer is enabled without reset, the watchdog timer may not start to count from zero.

### **EEPROM Read/Write Access**

The EEPROM access registers are accessible in the I/O space.

The write access time is in the range of 2.5 - 4ms, depending on the  $V_{CC}$  voltages. A self-timing function, however, lets the user software detect when the next byte can be written. If the user code contains code that writes the EEPROM, some precaution must be taken. In heavily filtered power supplies,  $V_{CC}$  is likely to rise or fall slowly on power-up/down. This causes the device for some period of time to run at a voltage lower than specified as minimum for the clock frequency used. CPU operation under these conditions is likely cause the program counter to perform unintentional jumps and eventually execute the EEPROM write code. To secure EEPROM integrity, the user is advised to use an external under-voltage reset circuit in this case.

In order to prevent unintentional EEPROM writes, a specific write procedure must be followed. Refer to the description of the EEPROM Control Register for details on this.

When the EEPROM is read or written, the CPU is halted for two clock cycles before the next instruction is executed.

#### **EEPROM Address Register - EEARH and EEARL**

| Bit           | 15    | 14    | 13    | 12    | 11    | 10    | 9     | 8     | _     |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$1F (\$3F)   | -     | -     | -     | -     | -     | -     | -     | EEAR8 | EEARH |

| \$1E (\$3E)   | EEAR7 | EEAR6 | EEAR5 | EEAR4 | EEAR3 | EEAR2 | EEAR1 | EEAR0 | EEARL |

| !             | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     | ı     |

| Read/Write    | R/W   |       |

|               | R/W   |       |

| Initial value | 8     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |       |

|               | 8     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |       |

The EEPROM Address Registers - EEARH and EEARL specify the EEPROM address in the 512 bytes EEPROM space for AT90S8515. For AT90S4414 EEARH is not present, thus EEARL specify the EEPROM address in the 256 bytes EEPROM space. The EEPROM data bytes are addressed linearly between 0 and 256/512.

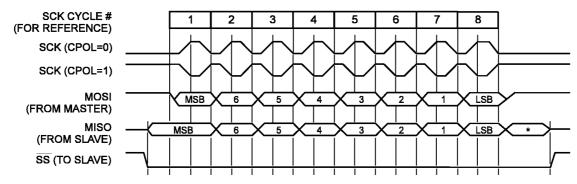

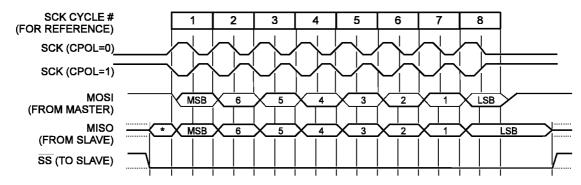

#### **Data Modes**

There are four combinations of SCK phase and polarity with respect to serial data, which are determined by control bits CPHA and CPOL. The SPI data transfer formats are shown in Figure 36 and Figure 37.

Figure 36. SPI Transfer Format with CPHA = 0 and DORD = 0

<sup>\*</sup> Not defined but normally MSB of character just received

Figure 37. SPI Transfer Format with CPHA = 1 and DORD = 0

<sup>\*</sup> Not defined but normally LSB of previously transmitted character

## **SPI Control Register - SPCR**

| Bit           | 7    | 6   | 5    | 4    | 3    | 2    | 1    | 0    | _    |

|---------------|------|-----|------|------|------|------|------|------|------|

| \$0D (\$2D)   | SPIE | SPE | DORD | MSTR | CPOL | CPHA | SPR1 | SPR0 | SPCR |

| Read/Write    | R/W  | R/W | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | •    |

| Initial value | 0    | 0   | 0    | 0    | 0    | 0    | 0    | 0    |      |

### • Bit 7 - SPIE: SPI Interrupt Enable

This bit causes the SPI interrupt to be executed if SPIF bit in the SPSR register is set and the global interrupts are enabled.

• Bit 6 - SPE: SPI Enable

When the SPE bit is set (one), the SPI is enabled. This bit must be set to enable any SPI operations.

· Bit 5 - DORD: Data Order

When the DORD bit is set (one), the LSB of the data word is transmitted first.

When the DORD bit is cleared (zero), the MSB of the data word is transmitted first.

• Bit 4 - MSTR: Master/Slave Select

This bit selects Master SPI mode when set (one), and Slave SPI mode when cleared (zero). If  $\overline{SS}$  is configured as an input and is driven low while MSTR is set, MSTR will be cleared, and SPIF in SPSR will become set. The user will then have to set MSTR to re-enable SPI master mode.

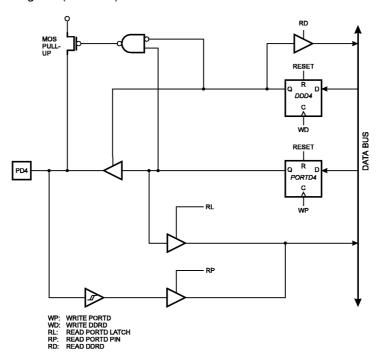

Figure 56. Port D Schematic Diagram (Pin PD4)

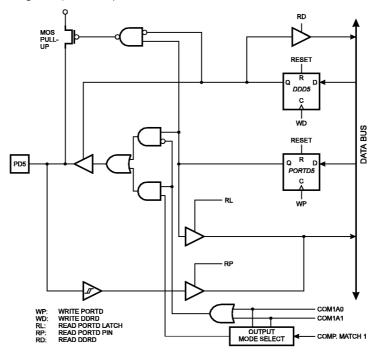

Figure 57. Port D Schematic Diagram (Pin PD5)

# **Parallel Programming Characteristics**

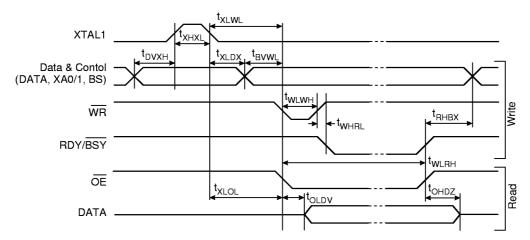

Figure 63. Parallel Programming Timing

**Table 31.** Parallel Programming Characteristics  $T_A = 25^{\circ}C \pm 10\%$ ,  $V_{CC} = 5V \pm 10\%$

| Symbol                | Parameter                                        | Min  | Тур | Max  | Units |

|-----------------------|--------------------------------------------------|------|-----|------|-------|

| V <sub>PP</sub>       | Programming Enable Voltage                       | 11.5 |     | 12.5 | V     |

| I <sub>PP</sub>       | Programming Enable Current                       |      |     | 250  | μА    |

| t <sub>DVXH</sub>     | Data and Control Setup before XTAL1 High         | 67   |     |      | ns    |

| t <sub>XHXL</sub>     | XTAL1 Pulse Width High                           | 67   |     |      | ns    |

| t <sub>XLDX</sub>     | Data and Control Hold after XTAL1 Low            | 67   |     |      | ns    |

| t <sub>XLWL</sub>     | XTAL1 Low to WR Low                              | 67   |     |      | ns    |

| t <sub>BVWL</sub>     | BS Valid to WR Low                               | 67   |     |      | ns    |

| t <sub>RHBX</sub>     | BS Hold after RDY/BSY High                       | 67   |     |      | ns    |

| t <sub>WLWH</sub>     | WR Pulse Width Low <sup>(1)</sup>                | 67   |     |      | ns    |

| t <sub>WHRL</sub>     | WR High to RDY/BSY Low <sup>(2)</sup>            |      | 20  |      | ns    |

| t <sub>WLRH</sub>     | WR Low to RDY/BSY High <sup>(2)</sup>            | 0.5  | 0.7 | 0.9  | ms    |

| t <sub>XLOL</sub>     | XTAL1 Low to OE Low                              | 67   |     |      | ns    |

| t <sub>OLDV</sub>     | OE Low to DATA Valid                             |      | 20  |      | ns    |

| t <sub>OHDZ</sub>     | OE High to DATA Tri-stated                       |      |     | 20   | ns    |

| t <sub>WLWH_CE</sub>  | WR Pulse Width Low for Chip Erase                | 5    | 10  | 15   | ms    |

| t <sub>WLWH_PFB</sub> | WR Pulse Width Low for Programming the Fuse Bits | 1.0  | 1.5 | 1.8  | ms    |

Notes:

1. Use t<sub>WLWH\_CE</sub> for Chip Erase and t<sub>WLWH\_PFB</sub> for Programming the Fuse Bits.

2. If t<sub>WLWH</sub> is held longer than t<sub>WLRH</sub>, no RDY/BSY pulse will be seen.

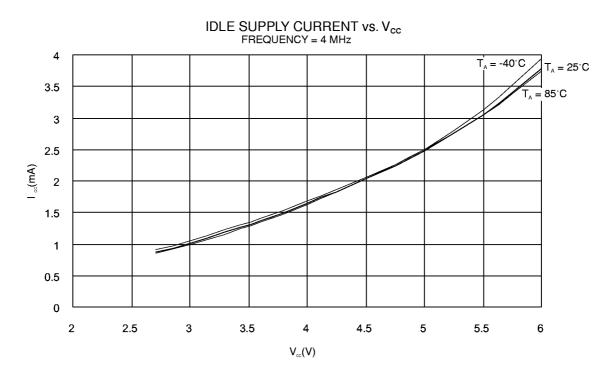

Figure 72. Idle Supply current vs.  $V_{\text{CC}}$

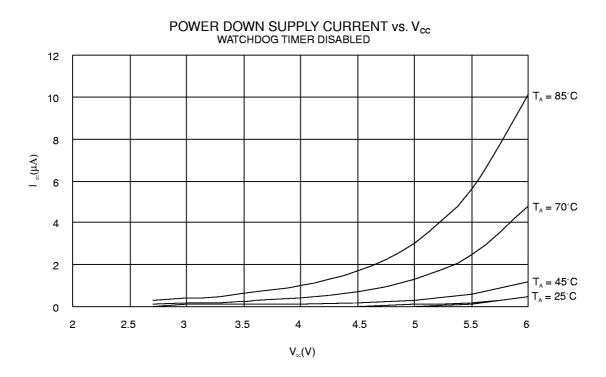

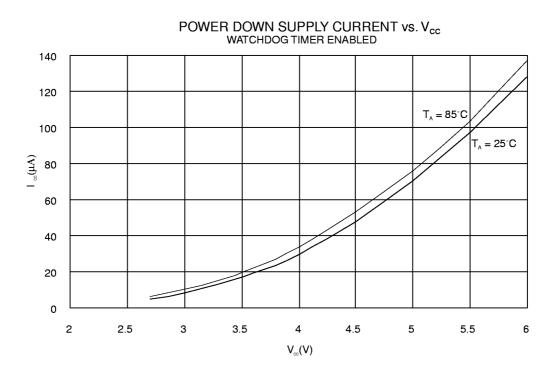

Figure 73. Power Down Supply Current vs.  $V_{\rm CC}$

Figure 74. Power Down Supply Current vs.  $V_{\rm CC}$

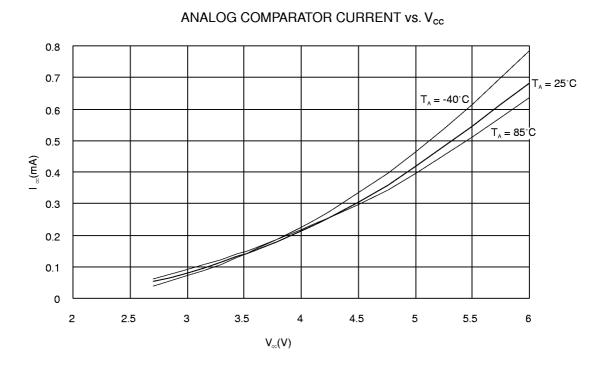

Figure 75. Analog Comparator Current vs.  $V_{\rm CC}$

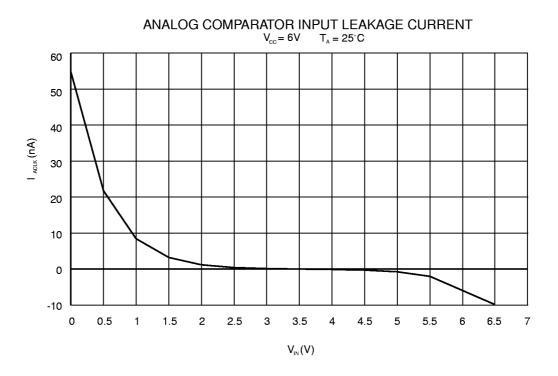

Figure 78. Analog Comparator Input Leakage Current

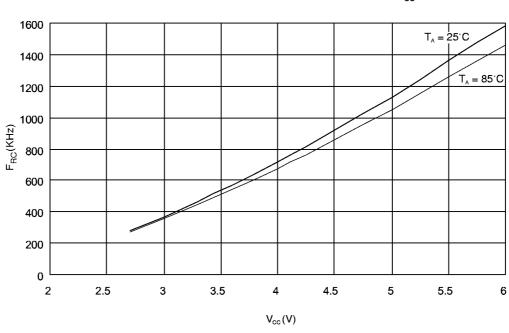

Figure 79. Watchdog Oscillator Frequency vs. V<sub>CC</sub>

# WATCHDOG OSCILLATOR FREQUENCY vs. V<sub>cc</sub>

# **Ordering Information**

| Speed (MHz) | Power Supply | Ordering Code | Package | Operation Range |

|-------------|--------------|---------------|---------|-----------------|

| 4           | 2.7 - 6.0V   | AT90S4414-4AC | 44A     | Commercial      |

|             |              | AT90S4414-4JC | 44J     | (0°C to 70°C)   |

|             |              | AT90S4414-4PC | 40P6    |                 |

|             |              | AT90S4414-4AI | 44A     | Industrial      |

|             |              | AT90S4414-4JI | 44J     | (-40°C to 85°C) |

|             |              | AT90S4414-4PI | 40P6    |                 |

| 8           | 4.0 - 6.0V   | AT90S4414-8AC | 44A     | Commercial      |

|             |              | AT90S4414-8JC | 44J     | (0°C to 70°C)   |

|             |              | AT90S4414-8PC | 40P6    |                 |

|             |              | AT90S4414-8AI | 44A     | Industrial      |

|             |              | AT90S4414-8JI | 44J     | (-40°C to 85°C) |

|             |              | AT90S4414-8PI | 40P6    |                 |

Note: Order AT904414A-XXX for devices with the FSTRT Fuse programmed.

| Speed (MHz) | Power Supply | Ordering Code | Package | Operation Range |

|-------------|--------------|---------------|---------|-----------------|

| 4           | 2.7 - 6.0V   | AT90S8515-4AC | 44A     | Commercial      |

|             |              | AT90S8515-4JC | 44J     | (0°C to 70°C)   |

|             |              | AT90S8515-4PC | 40P6    |                 |

|             |              | AT90S8515-4AI | 44A     | Industrial      |

|             |              | AT90S8515-4JI | 44J     | (-40°C to 85°C) |

|             |              | AT90S8515-4PI | 40P6    |                 |

| 8           | 4.0 - 6.0V   | AT90S8515-8AC | 44A     | Commercial      |

|             |              | AT90S8515-8JC | 44J     | (0°C to 70°C)   |

|             |              | AT90S8515-8PC | 40P6    |                 |

|             |              | AT90S8515-8AI | 44A     | Industrial      |

|             |              | AT90S8515-8JI | 44J     | (-40°C to 85°C) |

|             |              | AT90S8515-8PI | 40P6    |                 |

Note: Order AT90S8515A-XXX for devices with the FSTRT Fuse programmed.

| Package Type  |                                                                   |  |  |  |

|---------------|-------------------------------------------------------------------|--|--|--|

| 44 <b>A</b>   | 44-lead, Thin (1.0 mm) Plastic Gull Wing Quad Flat Package (TQFP) |  |  |  |

| 44J           | 44-lead, Plastic J-leaded Chip Carrier (PLCC)                     |  |  |  |

| 40 <b>P</b> 6 | 40-lead, 0.600" Wide, Plastic Dual Inline Package (PDIP)          |  |  |  |