Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | AVR                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | SPI, UART/USART                                                         |

| Peripherals                | PWM, WDT                                                                |

| Number of I/O              | 32                                                                      |

| Program Memory Size        | 4KB (2K x 16)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 256 x 8                                                                 |

| RAM Size                   | 256 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                 |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | 0°C ~ 70°C                                                              |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-LCC (J-Lead)                                                         |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at90s4414-8jc |

|                            |                                                                         |

## **Data Direct**

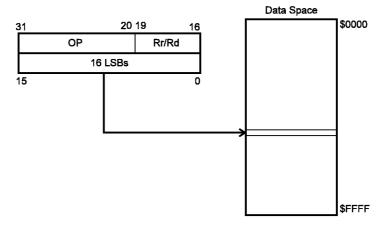

Figure 12. Direct Data Addressing

A 16-bit Data Address is contained in the 16 LSBs of a two-word instruction. Rd/Rr specify the destination or source register.

## **Data Indirect with Displacement**

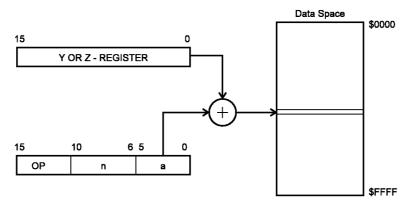

Figure 13. Data Indirect with Displacement

Operand address is the result of the Y or Z-register contents added to the address contained in 6 bits of the instruction word.

## **Data Indirect with Post-increment**

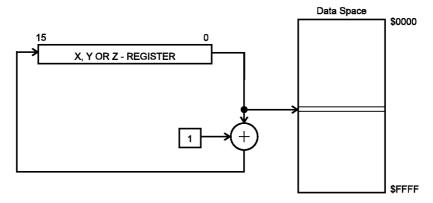

Figure 16. Data Indirect Addressing with Post-increment

The X, Y or the Z-register is incremented after the operation. Operand address is the content of the X, Y or the Z-register prior to incrementing.

## **Constant Addressing Using the LPM Instruction**

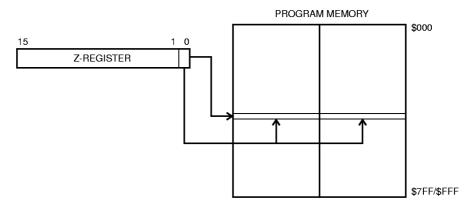

Figure 17. Code Memory Constant Addressing

Constant byte address is specified by the Z-register contents. The 15 MSBs select word address (0 - 2K/4K), the LSB selects low byte if cleared (LSB = 0) or high byte if set (LSB = 1).

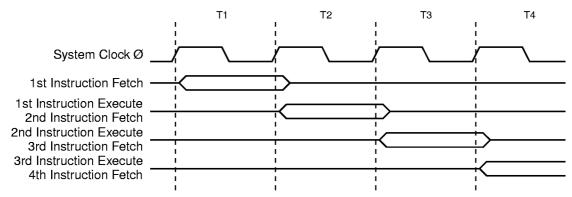

Figure 20. The Parallel Instruction Fetches and Instruction Executions

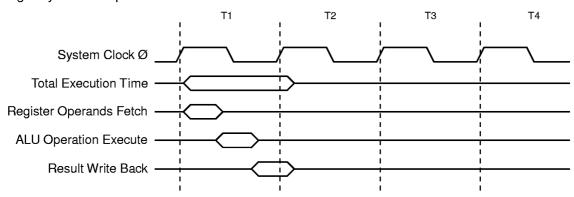

Figure 21 shows the internal timing concept for the register file. In a single clock cycle an ALU operation using two register operands is executed, and the result is stored back to the destination register.

Figure 21. Single Cycle ALU Operation

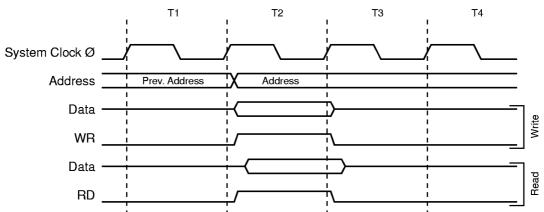

The internal data SRAM access is performed in two System Clock cycles as described in Figure 22.

Figure 22. On-chip Data SRAM Access Cycles

See "Interface to External SRAM" on page 53 for a description of the access to the external SRAM.

## Interrupt Handling

The AT90S4414/8515 has two 8-bit Interrupt Mask control registers; GIMSK - General Interrupt Mask register and TIMSK - Timer/Counter Interrupt Mask register.

When an interrupt occurs, the Global Interrupt Enable I-bit is cleared (zero) and all interrupts are disabled. The user software can set (one) the I-bit to enable nested interrupts. The I-bit is set (one) when a Return from Interrupt instruction - RETI - is executed.

For Interrupts triggered by events that can remain static (e.g. the Output Compare register1 matching the value of Timer/Counter1) the interrupt flag is set when the event occurs. If the interrupt flag is cleared and the interrupt condition persists, the flag will not be set until the event occurs the next time.

When the Program Counter is vectored to the actual interrupt vector in order to execute the interrupt handling routine, hardware clears the corresponding flag that generated the interrupt. Some of the interrupt flags can also be cleared by writing a logic one to the flag bit position(s) to be cleared.

If an interrupt condition occurs when the corresponding interrupt enable bit is cleared (zero), the interrupt flag will be set and remembered until the interrupt is enabled, or the flag is cleared by software.

If one or more interrupt conditions occur when the global interrupt enable bit is cleared (zero), the corresponding interrupt flag(s) will be set and remembered until the global interrupt enable bit is set (one), and will be executed by order of priority.

Note that external level interrupt does not have a flag, and will only be remembered for as long as the interrupt condition is active.

## **General Interrupt Mask Register - GIMSK**

| Bit           | 7    | 6    | 5 | 4 | 3 | 2 | 1 | 0 |       |

|---------------|------|------|---|---|---|---|---|---|-------|

| \$3B (\$5B)   | INT1 | INT0 | - | - | - | - | - | - | GIMSK |

| Read/Write    | R/W  | R/W  | R | R | R | R | R | R |       |

| Initial value | 0    | 0    | 0 | 0 | 0 | 0 | 0 | 0 |       |

#### • Bit 7 - INT1: External Interrupt Request 1 Enable

When the INT1 bit is set (one) and the I-bit in the Status Register (SREG) is set (one), the external pin interrupt is enabled. The Interrupt Sense Control1 bits 1/0 (ISC11 and ISC10) in the MCU general Control Register (MCUCR) defines whether the external interrupt is activated on rising or falling edge of the INT1 pin or level sensed. Activity on the pin will cause an interrupt request even if INT1 is configured as an output. The corresponding interrupt of External Interrupt Request 1 is executed from program memory address \$002. See also "External Interrupts".

## • Bit 6 - INT0: External Interrupt Request 0 Enable

When the INT0 bit is set (one) and the I-bit in the Status Register (SREG) is set (one), the external pin interrupt is enabled. The Interrupt Sense Control0 bits 1/0 (ISC01 and ISC00) in the MCU general Control Register (MCUCR) defines whether the external interrupt is activated on rising or falling edge of the INT0 pin or level sensed. Activity on the pin will cause an interrupt request even if INT0 is configured as an output. The corresponding interrupt of External Interrupt Request 0 is executed from program memory address \$001. See also "External Interrupts."

## • Bits 5..0 - Res: Reserved bits

These bits are reserved bits in the AT90S4414/8515 and always read as zero.

## General Interrupt Flag Register - GIFR

| Bit           | 7     | 6     | 5 | 4 | 3 | 2 | 1 | 0 |      |

|---------------|-------|-------|---|---|---|---|---|---|------|

| \$3A (\$5A)   | INTF1 | INTF0 | - | - | - | - | - | - | GIFR |

| Read/Write    | R/W   | R/W   | R | R | R | R | R | R | _    |

| Initial value | 0     | 0     | 0 | 0 | 0 | 0 | 0 | 0 |      |

## • Bit 7 - INTF1: External Interrupt Flag1

When an event on the INT1 pin triggers an interrupt request, INTF1 becomes set (one). If the I-bit in SREG and the INT1 bit in GIMSK are set (one), the MCU will jump to the interrupt vector at address \$002. The flag is cleared when the interrupt routine is executed. Alternatively, the flag can be cleared by writing a logical one to it.

The Stop condition provides a Timer Enable/Disable function. The CK down divided modes are scaled directly from the CK oscillator clock. If the external pin modes are used for Timer/Counter0, transitions on PB0/(T0) will clock the counter even if the pin is configured as an output. This feature can give the user SW control of the counting.

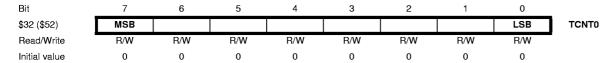

#### **Timer Counter 0 - TCNT0**

The Timer/Counter0 is realized as an up-counter with read and write access. If the Timer/Counter0 is written and a clock source is present, the Timer/Counter0 continues counting in the clock cycle following the write operation.

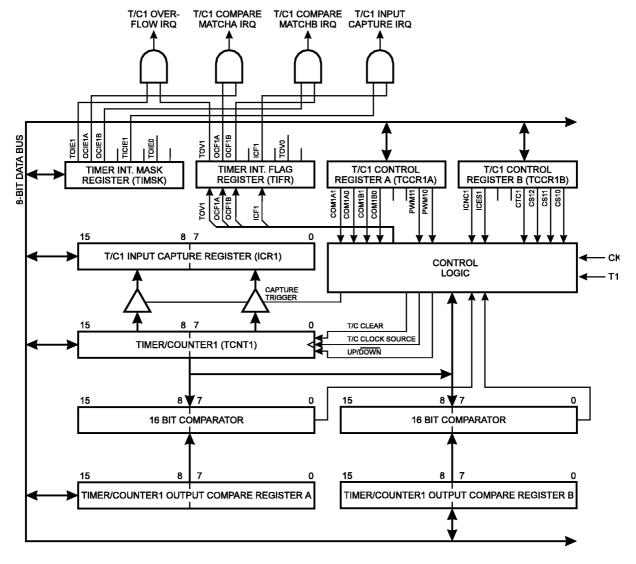

## 16-bit Timer/Counter1

Figure 30 shows the block diagram for Timer/Counter1.

Figure 30. Timer/Counter1 Block Diagram

#### • Bit 3 - CTC1: Clear Timer/Counter1 on Compare Match

When the CTC1 control bit is set (one), the Timer/Counter1 is reset to \$0000 in the clock cycle after a compareA match. If the CTC1 control bit is cleared, Timer/Counter1 continues counting and is unaffected by a compare match. Since the compare match is detected in the CPU clock cycle following the match, this function will behave differently when a prescaling higher than 1 is used for the timer. When a prescaling of 1 is used, and the compareA register is set to C, the timer will count as follows if CTC1 is set:

When the prescaler is set to divide by 8, the timer will count like this:

In PWM mode, this bit has no effect.

## • Bits 2,1,0 - CS12, CS11, CS10: Clock Select1, bit 2,1 and 0

The Clock Select1 bits 2,1 and 0 define the prescaling source of Timer/Counter1.

Table 11. Clock 1 Prescale Select

| CS12 | CS11 | CS10 | Description                          |

|------|------|------|--------------------------------------|

| 0    | 0    | 0    | Stop, the Timer/Counter1 is stopped. |

| 0    | 0    | 1    | СК                                   |

| 0    | 1    | 0    | CK/8                                 |

| 0    | 1    | 1    | CK/64                                |

| 1    | 0    | 0    | CK/256                               |

| 1    | 0    | 1    | CK/1024                              |

| 1    | 1    | 0    | External Pin T1, falling edge        |

| 1    | 1    | 1    | External Pin T1, rising edge         |

The Stop condition provides a Timer Enable/Disable function. The CK down divided modes are scaled directly from the CK oscillator clock. If the external pin modes are used for Timer/Counter1, transitions on PB1/(T1) will clock the counter even if the pin is configured as an output. This feature can give the user SW control of the counting.

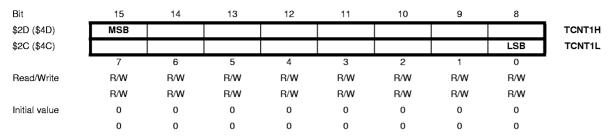

Timer/Counter1 - TCNT1H AND TCNT1L

This 16-bit register contains the prescaled value of the 16-bit Timer/Counter1. To ensure that both the high and low bytes are read and written simultaneously when the CPU accesses these registers, the access is performed using an 8-bit temporary register (TEMP). This temporary register is also used when accessing OCR1A, OCR1B and ICR1. If the main program and also interrupt routines perform access to registers using TEMP, interrupts must be disabled during access from the main program (and from interrupt routines if interrupts are allowed from within interrupt routines).

## TCNT1 Timer/Counter1 Write:

When the CPU writes to the high byte TCNT1H, the written data is placed in the TEMP register. Next, when the CPU writes the low byte TCNT1L, this byte of data is combined with the byte data in the TEMP register, and all 16 bits are written to the TCNT1 Timer/Counter1 register simultaneously. Consequently, the high byte TCNT1H must be accessed first for a full 16-bit register write operation.

## Timer/Counter1 Input Capture Register - ICR1H AND ICR1L

| Bit           | 15  | 14 | 13 | 12 | 11 | 10 | 9 | 8   |       |

|---------------|-----|----|----|----|----|----|---|-----|-------|

| \$25 (\$45)   | MSB |    |    |    |    |    |   |     | ICR1H |

| \$24 (\$44)   |     |    |    |    |    |    |   | LSB | ICR1L |

|               | 7   | 6  | 5  | 4  | 3  | 2  | 1 | 0   | •     |

| Read/Write    | R   | R  | R  | R  | R  | R  | R | R   |       |

|               | R   | R  | R  | R  | R  | R  | R | R   |       |

| Initial value | 0   | 0  | 0  | 0  | 0  | 0  | 0 | 0   |       |

|               | 0   | 0  | 0  | 0  | 0  | 0  | 0 | 0   |       |

The input capture register is a 16-bit read-only register.

When the rising or falling edge (according to the input capture edge setting - ICES1) of the signal at the input capture pin - ICP - is detected, the current value of the Timer/Counter1 is transferred to the Input Capture Register - ICR1. At the same time, the input capture flag - ICF1 - is set (one).

Since the Input Capture Register - ICR1 - is a 16-bit register, a temporary register TEMP is used when ICR1 is read to ensure that both bytes are read simultaneously. When the CPU reads the low byte ICR1L, the data is sent to the CPU and the data of the high byte ICR1H is placed in the TEMP register. When the CPU reads the data in the high byte ICR1H, the CPU receives the data in the TEMP register. Consequently, the low byte ICR1L must be accessed first for a full 16-bit register read operation.

The TEMP register is also used when accessing TCNT1, OCR1A and OCR1B. If the main program and also interrupt routines perform access to registers using TEMP, interrupts must be disabled during access from the main program (and from interrupt routines if interrupts are allowed from within interrupt routines).

#### Timer/Counter1 In PWM Mode

When the PWM mode is selected, Timer/Counter1 and the Output Compare Register1A - OCR1A and the Output Compare Register1B - OCR1B, form a dual 8, 9 or 10-bit, free-running, glitch-free and phase correct PWM with outputs on the PD5(OC1A) and OC1B pins. Timer/Counter1 acts as an up/down counter, counting up from \$0000 to TOP (see Table 12), where it turns and counts down again to zero before the cycle is repeated. When the counter value matches the contents of the 10 least significant bits of OCR1A or OCR1B, the PD5(OC1A)/OC1B pins are set or cleared according to the settings of the COM1A1/COM1A0 or COM1B1/COM1B0 bits in the Timer/Counter1 Control Register TCCR1A. Refer to Table 13 for details.

**Table 12.** Timer TOP Values and PWM Frequency

| PWM Resolution | Timer TOP value | Frequency               |

|----------------|-----------------|-------------------------|

| 8-bit          | \$00FF (255)    | f <sub>TCK1</sub> /510  |

| 9-bit          | \$01FF (511)    | f <sub>TCK1</sub> /1022 |

| 10-bit         | \$03FF(1023)    | f <sub>TCK1</sub> /2046 |

Table 13. Compare1 Mode Select in PWM Mode

| COM1X1 | COM1X0 | Effect on OCX1                                                                                 |

|--------|--------|------------------------------------------------------------------------------------------------|

| 0      | 0      | Not connected                                                                                  |

| 0      | 1      | Not connected                                                                                  |

| 1      | 0      | Cleared on compare match, up-counting. Set on compare match, down-counting (non-inverted PWM). |

| 1      | 1      | Cleared on compare match, down-counting. Set on compare match, up-counting (inverted PWM).     |

Note: X = A or B

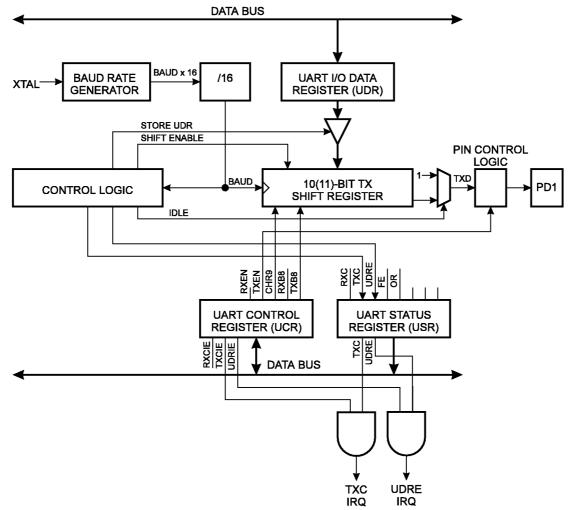

## **UART**

The AT90S4414/8515 features a full duplex (separate receive and transmit registers) Universal Asynchronous Receiver and Transmitter (UART). The main features are:

- Baud rate generator that can generate a large number of baud rates (bps)

- · High baud rates at low XTAL frequencies

- · 8 or 9 bits data

- · Noise filtering

- · Overrun detection

- · Framing Error detection

- · False Start Bit detection

- Three separate interrupts on TX Complete, TX Data Register Empty and RX Complete

## **Data Transmission**

A block schematic of the UART transmitter is shown in Figure 38.

Figure 38. UART Transmitter

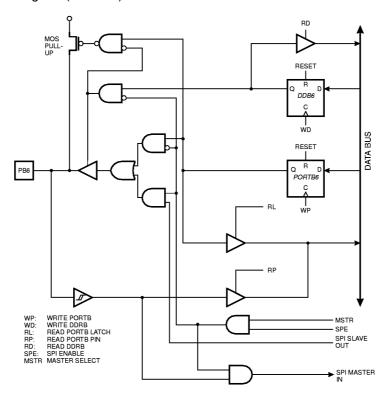

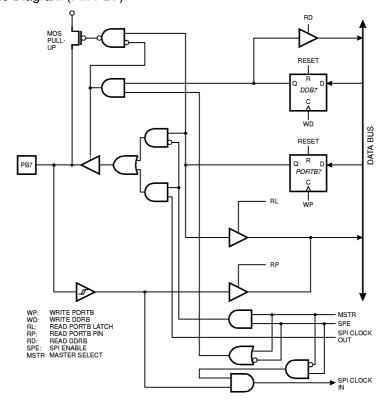

## Port B

Port B is an 8-bit bi-directional I/O port.

Three I/O memory address locations are allocated for the Port B, one each for the Data Register - PORTB, \$18(\$38), Data Direction Register - DDRB, \$17(\$37) and the Port B Input Pins - PINB, \$16(\$36). The Port B Input Pins address is read only, while the Data Register and the Data Direction Register are read/write.

All port pins have individually selectable pull-up resistors. The Port B output buffers can sink 20 mA and thus drive LED displays directly. When pins PB0 to PB7 are used as inputs and are externally pulled low, they will source current if the internal pull-up resistors are activated.

The Port B pins with alternate functions are shown in the following table:

Table 21. Port B Pins Alternate Functions

| Port Pin | Alternate Functions                         |

|----------|---------------------------------------------|

| PB0      | T0 (Timer/Counter 0 external counter input) |

| PB1      | T1 (Timer/Counter 1 external counter input) |

| PB2      | AIN0 (Analog comparator positive input)     |

| PB3      | AIN1 (Analog comparator negative input)     |

| PB4      | SS (SPI Slave Select input)                 |

| PB5      | MOSI (SPI Bus Master Output/Slave Input)    |

| PB6      | MISO (SPI Bus Master Input/Slave Output)    |

| PB7      | SCK (SPI Bus Serial Clock)                  |

When the pins are used for the alternate function the DDRB and PORTB register has to be set according to the alternate function description.

## Port B Data Register - PORTB

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      | _     |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|-------|

| \$18 (\$38)   | PORTB7 | PORTB6 | PORTB5 | PORTB4 | PORTB3 | PORTB2 | PORTB1 | PORTB0 | PORTB |

| Read/Write    | R/W    |       |

| Initial value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

## Port B Data Direction Register - DDRB

| Bit           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |      |

|---------------|------|------|------|------|------|------|------|------|------|

| \$17 (\$37)   | DDB7 | DDB6 | DDB5 | DDB4 | DDB3 | DDB2 | DDB1 | DDB0 | DDRB |

| Read/Write    | R/W  | •    |

| Initial value | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |      |

#### Port B Input Pins Address - PINB

| Bit           | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |      |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| \$16 (\$36)   | PINB7 | PINB6 | PINB5 | PINB4 | PINB3 | PINB2 | PINB1 | PINB0 | PINB |

| Read/Write    | R     | R     | R     | R     | R     | R     | R     | R     |      |

| Initial value | Hi-Z  |      |

The Port B Input Pins address - PINB - is not a register, and this address enables access to the physical value on each Port B pin. When reading PORTB, the Port B Data Latch is read, and when reading PINB, the logical values present on the pins are read.

Figure 50. Port B Schematic Diagram (Pin PB6)

Figure 51. Port B Schematic Diagram (Pin PB7)

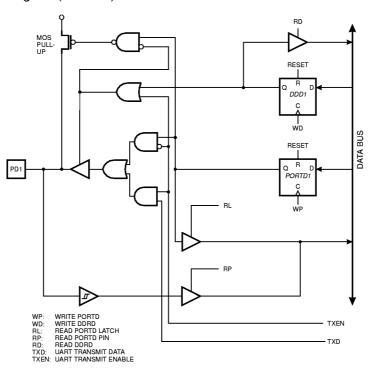

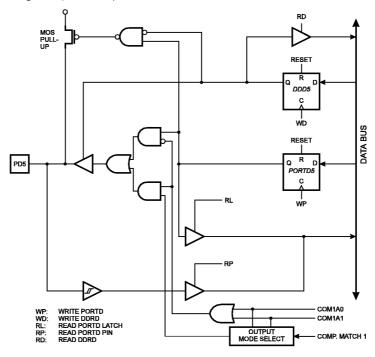

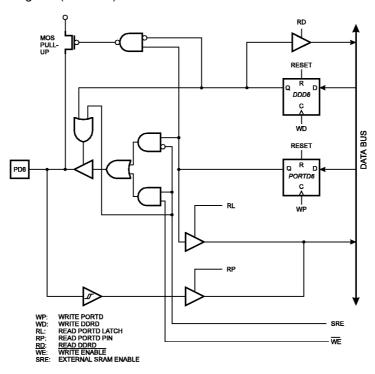

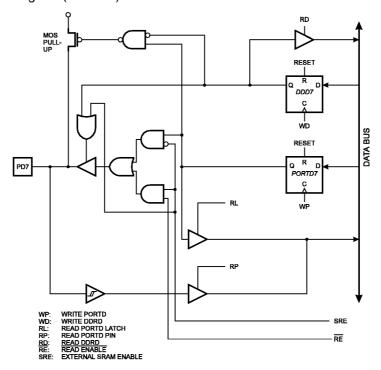

Figure 54. Port D Schematic Diagram (Pin PD1)

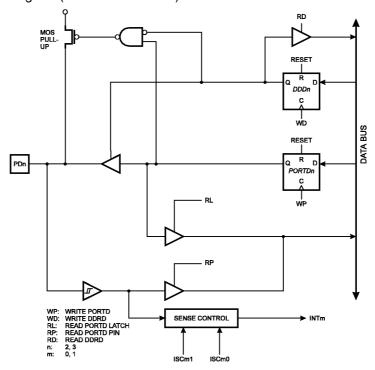

Figure 55. Port D Schematic Diagram (Pins PD2 and PD3)

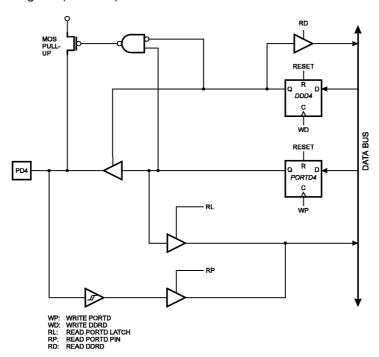

Figure 56. Port D Schematic Diagram (Pin PD4)

Figure 57. Port D Schematic Diagram (Pin PD5)

Figure 58. Port D Schematic Diagram (Pin PD6)

Figure 59. Port D Schematic Diagram (Pin PD7)

# **Memory Programming**

## **Program and Data Memory Lock Bits**

The AT90S4414/8515 MCU provides two Lock bits which can be left unprogrammed ('1') or can be programmed ('0') to obtain the additional features listed in Table 26. The Lock Bits can only be erased with the Chip Erase command.

Table 26. Lock Bit Protection Modes

| Mem  | Memory Lock Bits |         | Protection Type                                              |  |  |  |

|------|------------------|---------|--------------------------------------------------------------|--|--|--|

| Mode | LB1              | LB1 LB2 |                                                              |  |  |  |

| 1    | 1                | 1       | No memory lock features enabled.                             |  |  |  |

| 2    | 0                | 1       | Further programming of the Flash and EEPROM is disabled. (1) |  |  |  |

| 3    | 0                | 0       | Same as mode 2, and verify is also disabled.                 |  |  |  |

Note:

1. In Parallel mode, further programming of the Fuse bits are also disabled. Program the Fuse bits before programming the Lock bits.

## **Fuse Bits**

The AT90S4414/8515 has two Fuse bits, SPIEN and FSTRT.

- When the SPIEN Fuse is programmed ('0'), Serial Program and Data Downloading is enabled. Default value is programmed ("0").

- When the FSTRT Fuse is programmed ('0'), the short start-up time is selected. Default value is unprogrammed ("1"). Parts with this bit pre-programmed ('0') can be delivered on demand.

The Fuse bits are not accessible in Serial Programming Mode. The status of the Fuse bits is not affected by Chip Erase.

## **Signature Bytes**

All Atmel microcontrollers have a three-byte signature code which identifies the device. This code can be read in both serial and parallel mode. The three bytes reside in a separate address space.

For the AT90S8515<sup>(1)</sup> they are:

- \$000: \$1E (indicates manufactured by Atmel)

- 2. \$001: \$93 (indicates 8KB Flash memory)

- \$002: \$01 (indicates AT90S8515 device when signature byte \$001 is \$93)

For the AT90S4414<sup>(1)</sup> they are:

- 1. \$000: \$1E (indicates manufactured by Atmel)

- 2. \$001: \$92 (indicates 4KB Flash memory)

- 3. \$002: \$01 (indicates AT90S4414 device when signature byte \$001 is \$92)

Note: 1. When both Lock bits are programmed (Lock mode 3), the signature bytes can not be read in serial mode. Reading the signature bytes will return: \$00, \$01 and \$02.

# Programming the Flash and EEPROM

Atmel's AT90S4414/8515 offers 4K/8K bytes of In-System Reprogrammable Flash Program memory and 256/512 bytes of EEPROM Data memory.

The AT90S4414/8515 is shipped with the on-chip Flash Program and EEPROM Data memory arrays in the erased state (i.e. contents = \$FF) and ready to be programmed. This device supports a High-voltage (12V) Parallel programming mode and a Low-voltage Serial programming mode. The +12V is used for programming enable only, and no current of significance is drawn by this pin. The serial programming mode provides a convenient way to download program and data into the AT90S4414/8515 inside the user's system.

The Program and Data memory arrays on the AT90S4414/8515 are programmed byte-by-byte in either programming modes. For the EEPROM, an auto-erase cycle is provided within the self-timed write operation in the serial programming mode. During programming, the supply voltage must be in accordance with Table 27.

Table 27. Supply Voltage During Programming

| Part      | Serial Programming | Parallel Programming |

|-----------|--------------------|----------------------|

| AT90S4414 | 2.7 - 6.0V         | 4.5 - 5.5V           |

| AT90S8515 | 2.7 - 6.0V         | 4.5 - 5.5V           |

## **Parallel Programming**

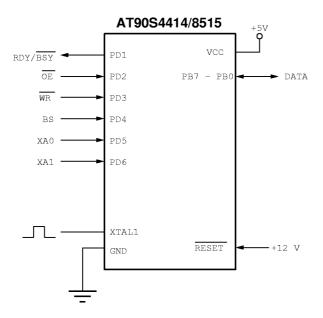

This section describes how to parallel program and verify Flash Program memory, EEPROM Data memory, Lock bits and Fuse bits in the AT90S4414/8515.

## **Signal Names**

In this section, some pins of the AT90S4414/AT908515 are referenced by signal names describing their function during parallel programming. See Figure 60 and Table 28. Pins not described in Table 28 are referenced by pin names.

The XA1/XA0 pins determine the action executed when the XTAL1 pin is given a positive pulse. The bit coding are shown in Table 29.

When pulsing  $\overline{WR}$  or  $\overline{OE}$ , the command loaded determines the action executed. The Command is a byte where the different bits are assigned functions as shown in Table 30.

Figure 60. Parallel Programming

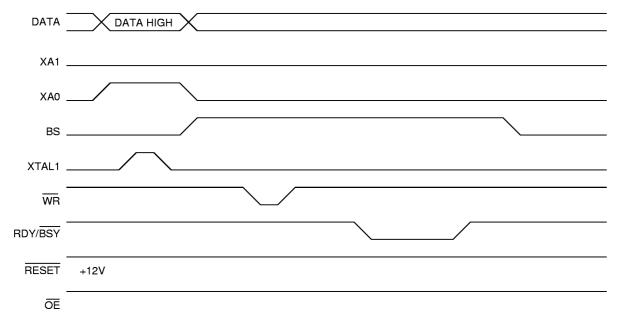

3. Wait until RDY/BSY goes high to program the next byte.

(See Figure 62 for signal waveforms.)

The loaded command and address are retained in the device during programming. For efficient programming, the following should be considered.

- The command needs only be loaded once when writing or reading multiple memory locations.

- Address high byte needs only be loaded before programming a new 256 word page in the Flash.

- Skip writing the data value \$FF, that is the contents of the entire Flash and EEPROM after a Chip Erase.

These considerations also applies to EEPROM programming, and Flash, EEPROM and Signature bytes reading.

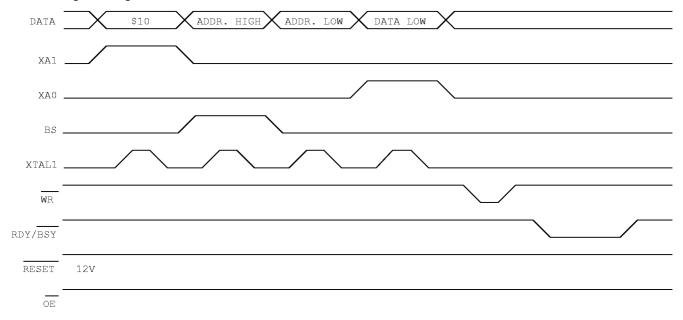

Figure 61. Programming the Flash Waveforms

Figure 62. Programming the Flash Waveforms (continued)

## **Serial Programming Algorithm**

When writing serial data to the AT90S4414/8515, data is clocked on the rising edge of SCK.

When reading data from the AT90S4414/8515, data is clocked on the falling edge of SCK. See Figure 65, Figure 66 and Table 34 for timing details.

To program and verify the AT90S4414/8515 in the serial programming mode, the following sequence is recommended (See four byte instruction formats in Table 33):

- 1. Power-up sequence:

- Apply power between  $V_{CC}$  and GND while  $\overline{RESET}$  and SCK are set to '0'. If a crystal is not connected across pins XTAL1 and XTAL2, apply a clock signal to the XTAL1 pin. In some systems, the programmer can not guarantee that SCK is held low during power-up. In this case,  $\overline{RESET}$  must be given a positive pulse of at least two XTAL1 cycles duration after SCK has been set to '0'.

- 2. Wait for at least 20 ms and enable serial programming by sending the Programming Enable serial instruction to the MOSI (PB5) pin.

- 3. The serial programming instructions will not work if the communication is out of syncronization. When in sync, the second byte (\$53) will echo back when issuing the third byte of the Programming Enable instruction. Whether the echo is correct or not, all 4 bytes of the instruction must be transmitted. If the \$53 did not echo back, give SCK a positive pulse and issue a new Programming Enable instruction. If the \$53 is not seen within 32 attempts, there is no functional device connected.

- 4. If a Chip Erase is performed (must be done to erase the Flash), wait  $t_{WD\_ERASE}$  after the instruction, give  $\overline{RESET}$  a positive pulse, and start over from Step 2. See Table 35 on page 80 for  $t_{WD\_ERASE}$  value.

- 5. The Flash or EEPROM array is programmed one byte at a time by supplying the address and data together with the appropriate Write instruction. An EEPROM memory location is first automatically erased before new data is written. Use Data Polling to detect when the next byte in the Flash or EEPROM can be written. If polling is not used, wait two persons before transmitting the next instruction. See Table 36 on page 80 for two persons value. In an erased device, no \$FFs in the data file(s) needs to be programmed.

- 6. Any memory location can be verified by using the Read instruction which returns the content at the selected address at the serial output MISO (PB6) pin.

- 7. At the end of the programming session, RESET can be set high to commence normal operation.

- 8. Power-off sequence (if needed):

Set XTAL1 to "0" (if a crystal is not used).

Set RESET to "1".

Turn V<sub>CC</sub> power off

## **Data Polling EEPROM**

When a byte is being programmed into the EEPROM, reading the address location being programmed will give the value P1 until the auto-erase is finished, and then the value P2. See Table 32 for P1 and P2 values.

At the time the device is ready for a new EEPROM byte, the programmed value will read correctly. This is used to determine when the next byte can be written. This will not work for the values P1 and P2, so when programming these values, the user will have to wait for at least the prescribed time  $t_{WD\_PROG}$  before programming the next byte. See Table 35 for  $t_{WD\_PROG}$  value. As a chip-erased device contains \$FF in all locations, programming of addresses that are meant to contain \$FF, can be skipped. This does not apply if the EEPROM is reprogrammed without first chip-erasing the device.

**Table 32.** Read Back Value during EEPROM Polling

| Part      | P1   | P2   |

|-----------|------|------|

| AT90S4414 | \$80 | \$7F |

| AT90S8515 | \$80 | \$7F |

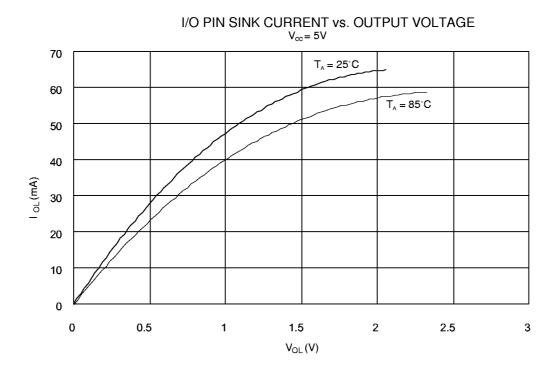

Figure 82. I/O Pin Sink Current vs. Output Voltage

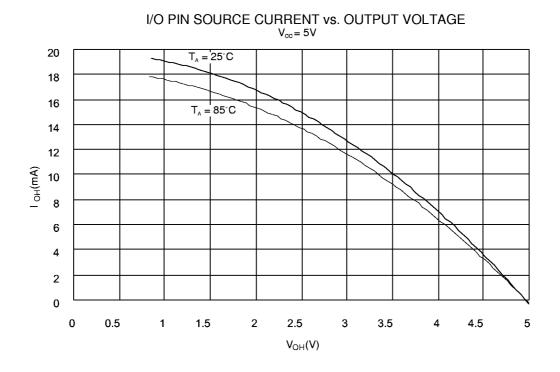

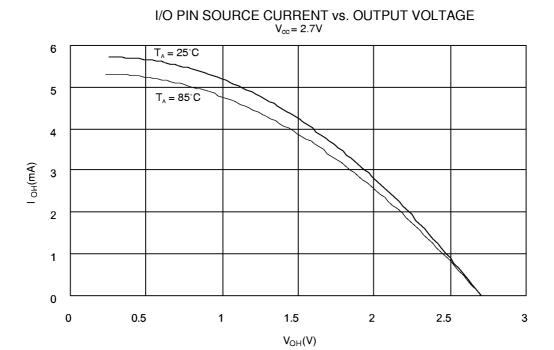

Figure 83. I/O Pin Source Current vs. Output Voltage

Figure 84. I/O Pin Source Curent vs. Output Voltage

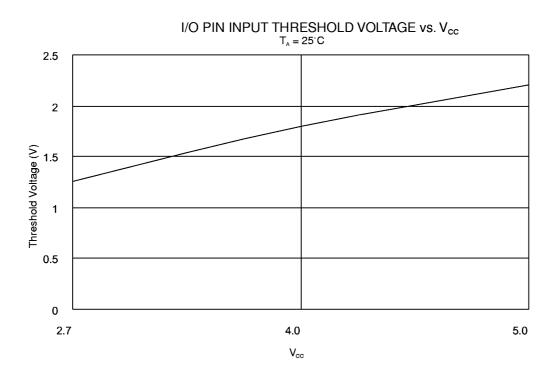

Figure 85. I/O Pin Input Threshold Voltage vs.  $V_{\rm CC}$

# **Instruction Set Summary (Continued)**

|            |                       |                                           |                                                                              | i            | <b>"01 1</b> |

|------------|-----------------------|-------------------------------------------|------------------------------------------------------------------------------|--------------|--------------|

| Mnemonics  | Operands              | Description                               | Operation                                                                    | Flags        | #Clocks      |

|            | RINSTRUCTIONS         |                                           | I                                                                            | T            |              |

| MOV        | Rd, Rr                | Move Between Registers                    | Rd ← Rr                                                                      | None         | 1            |

| LDI        | Rd, K                 | Load Immediate                            | Rd ← K                                                                       | None         | 1            |

| LD         | Rd, X                 | Load Indirect                             | $Rd \leftarrow (X)$                                                          | None         | 2            |

| LD         | Rd, X+<br>Rd, - X     | Load Indirect and Post-Inc.               | $Rd \leftarrow (X), X \leftarrow X + 1$                                      | None         | 2            |

| LD         | Rd, - X               | Load Indirect and Pre-Dec.  Load Indirect | $X \leftarrow X - 1$ , $Rd \leftarrow (X)$<br>$Rd \leftarrow (Y)$            | None<br>None | 2            |

| LD         | Rd, Y+                | Load Indirect Load Indirect and Post-Inc. | $Rd \leftarrow (Y)$ $Rd \leftarrow (Y), Y \leftarrow Y + 1$                  | None         | 2            |

| LD         | Rd, 1+                | Load Indirect and Pre-Dec.                | $Y \leftarrow Y - 1, Rd \leftarrow (Y)$                                      | None         | 2            |

| LDD        | Rd,Y+q                | Load Indirect with Displacement           | $Rd \leftarrow (Y + q)$                                                      | None         | 2            |

| LD         | Rd, Z                 | Load Indirect                             | $Rd \leftarrow (7 + q)$                                                      | None         | 2            |

| LD         | Rd, Z+                | Load Indirect and Post-Inc.               | $Rd \leftarrow (Z), Z \leftarrow Z+1$                                        | None         | 2            |

| LD         | Rd, -Z                | Load Indirect and Pre-Dec.                | $Z \leftarrow Z - 1$ , $Rd \leftarrow (Z)$                                   | None         | 2            |

| LDD        | Rd, Z+q               | Load Indirect with Displacement           | $Rd \leftarrow (Z + q)$                                                      | None         | 2            |

| LDS        | Rd, k                 | Load Direct from SRAM                     | Rd ← (k)                                                                     | None         | 2            |

| ST         | X, Rr                 | Store Indirect                            | (X) ← Rr                                                                     | None         | 2            |

| ST         | X+, Rr                | Store Indirect and Post-Inc.              | $(X) \leftarrow Rr, X \leftarrow X + 1$                                      | None         | 2            |

| ST         | - X, Rr               | Store Indirect and Pre-Dec.               | $X \leftarrow X - 1, (X) \leftarrow Rr$                                      | None         | 2            |

| ST         | Y, Rr                 | Store Indirect                            | (Y) ← Rr                                                                     | None         | 2            |

| ST         | Y+, Rr                | Store Indirect and Post-Inc.              | $(Y) \leftarrow Rr, Y \leftarrow Y + 1$                                      | None         | 2            |

| ST         | - Y, Rr               | Store Indirect and Pre-Dec.               | $Y \leftarrow Y - 1, (Y) \leftarrow Rr$                                      | None         | 2            |

| STD        | Y+q,Rr                | Store Indirect with Displacement          | (Y + q) ← Rr                                                                 | None         | 2            |

| ST         | Z, Rr                 | Store Indirect                            | (Z) ← Rr                                                                     | None         | 2            |

| ST         | Z+, Rr                | Store Indirect and Post-Inc.              | (Z) ← Rr, Z ← Z + 1                                                          | None         | 2            |

| ST         | -Z, Rr                | Store Indirect and Pre-Dec.               | $Z \leftarrow Z - 1$ , $(Z) \leftarrow Rr$                                   | None         | 2            |

| STD        | Z+q,Rr                | Store Indirect with Displacement          | (Z + q) ← Rr                                                                 | None         | 2            |

| STS        | k, Rr                 | Store Direct to SRAM                      | (k) ← Rr                                                                     | None         | 2            |

| LPM        |                       | Load Program Memory                       | R0 ← (Z)                                                                     | None         | 3            |

| IN         | Rd, P                 | In Port                                   | Rd ← P                                                                       | None         | 1            |

| OUT        | P, Rr                 | Out Port                                  | P ← Rr                                                                       | None         | 1            |

| PUSH       | Rr                    | Push Register on Stack                    | STACK ← Rr                                                                   | None         | 2            |

| POP        | Rd<br>ST INSTRUCTIONS | Pop Register from Stack                   | Rd ← STACK                                                                   | None         | 2            |

| SBI        | P,b                   | Set Bit in I/O Register                   | I/O(P,b) ← 1                                                                 | None         | 2            |

| CBI        | P,b                   | Clear Bit in I/O Register                 | $I/O(P,b) \leftarrow 0$                                                      | None         | 2            |

| LSL        | Rd                    | Logical Shift Left                        | $Rd(n+1) \leftarrow Rd(n), Rd(0) \leftarrow 0$                               | Z,C,N,V      | 1            |

| LSR        | Rd                    | Logical Shift Right                       | $Rd(n) \leftarrow Rd(n+1), Rd(7) \leftarrow 0$                               | Z,C,N,V      | 1            |

| ROL        | Rd                    | Rotate Left Through Carry                 | $Rd(0)\leftarrow C,Rd(n+1)\leftarrow Rd(n),C\leftarrow Rd(7)$                | Z,C,N,V      | 1            |

| ROR        | Rd                    | Rotate Right Through Carry                | $Rd(7)\leftarrow C,Rd(n)\leftarrow Rd(n+1),C\leftarrow Rd(0)$                | Z,C,N,V      | 1            |

| ASR        | Rd                    | Arithmetic Shift Right                    | $Rd(n) \leftarrow Rd(n+1), n=06$                                             | Z,C,N,V      | 1            |

| SWAP       | Rd                    | Swap Nibbles                              | Rd(30)←Rd(74),Rd(74)←Rd(30)                                                  | None         | 1            |

| BSET       | s                     | Flag Set                                  | SREG(s) ← 1                                                                  | SREG(s)      | 1            |

| BCLR       | s                     | Flag Clear                                | $SREG(s) \leftarrow 0$                                                       | SREG(s)      | 1            |

| BST        | Rr, b                 | Bit Store from Register to T              | $T \leftarrow Rr(b)$                                                         | Т            | 1            |

| BLD        | Rd, b                 | Bit load from T to Register               | $Rd(b) \leftarrow T$                                                         | None         | 1            |

| SEC        |                       | Set Carry                                 | C ← 1                                                                        | С            | 1            |

| CLC        |                       | Clear Carry                               | C ← 0                                                                        | С            | 1            |

| SEN        |                       | Set Negative Flag                         | N ← 1                                                                        | N            | 1            |

| CLN        |                       | Clear Negative Flag                       | N ← 0                                                                        | N            | 1            |

| SEZ        |                       | Set Zero Flag                             | Z ← 1                                                                        | Z            | 1            |

| CLZ        |                       | Clear Zero Flag                           | Z ← 0                                                                        | Z            | 1            |

| SEI        |                       | Global Interrupt Enable                   | 1←1                                                                          | 1            | 1            |

| CLI        |                       | Global Interrupt Disable                  | 1←0                                                                          | 1            | 1            |

| SES        |                       | Set Signed Test Flag                      | S ← 1                                                                        | S            | 1            |

| CLS        | 1                     | Clear Signed Test Flag                    | S ← 0                                                                        | S            | 1            |

| SEV        |                       | Set Twos Complement Overflow.             | V ← 1                                                                        | V            | 1            |

| CLV        | 1                     | Clear Twos Complement Overflow            | V ← 0                                                                        | V            | 1            |

| SET        | -                     | Set T in SREG                             | T ← 1                                                                        | T            | 1            |

| CLT        |                       | Clear T in SREG                           | T ← 0                                                                        | T            | 1            |

| SEH        |                       | Set Half Carry Flag in SREG               | H ← 1                                                                        | H            | 1            |

| CLH<br>NOP |                       | Clear Half Carry Flag in SREG             | H ← 0                                                                        | H            | 1            |

| SLEEP      |                       | No Operation Sleep                        | (see specific deser for Slean function)                                      | None         | 1            |

| WDR        |                       | Watchdog Reset                            | (see specific descr. for Sleep function) (see specific descr. for WDR/timer) | None         | 3            |

| MDH        | 1                     | vvalundog neset                           | L (see specific descr. for work/timer)                                       | None         |              |