Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | AVR                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | SPI, UART/USART                                                         |

| Peripherals                | PWM, WDT                                                                |

| Number of I/O              | 32                                                                      |

| Program Memory Size        | 4KB (2K x 16)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 256 x 8                                                                 |

| RAM Size                   | 256 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                 |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C                                                            |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-LCC (J-Lead)                                                         |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at90s4414-8ji |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The AT90S4414/8515 provides the following features: 4K/8K bytes of In-System Programmable Flash, 256/512 bytes EEPROM, 256/512 bytes SRAM, 32 general purpose I/O lines, 32 general purpose working registers, flexible timer/counters with compare modes, internal and external interrupts, a programmable serial UART, programmable Watch-dog Timer with internal oscillator, an SPI serial port and two software selectable power saving modes. The Idle Mode stops the CPU while allowing the SRAM, timer/counters, SPI port and interrupt system to continue functioning. The power down mode saves the register contents but freezes the oscillator, disabling all other chip functions until the next external interrupt or hardware reset.

The device is manufactured using Atmel's high density nonvolatile memory technology. The on-chip in-system programmable Flash allows the program memory to be reprogrammed in-system through an SPI serial interface or by a conventional nonvolatile memory programmer. By combining an enhanced RISC 8-bit CPU with In-System Programmable Flash on a monolithic chip, the Atmel AT90S4414/8515 is a powerful microcontroller that provides a highly flexible and cost effective solution to many embedded control applications.

The AT90S4414/8515 AVR is supported with a full suite of program and system development tools including: C compilers, macro assemblers, program debugger/simulators, in-circuit emulators, and evaluation kits.

# Comparison Between AT90S4414 and AT90S8515

The AT90S4414 has 4K bytes of In-System Programmable Flash, 256 bytes of EEPROM and 256 bytes of internal SRAM. The AT90S8515 has 8K bytes of In-System Programmable Flash, 512 bytes of EEPROM and 512 bytes of internal SRAM. Table 1 summarizes the different memory sizes for the two devices.

| Table 1. | Memory S | ize Summary |

|----------|----------|-------------|

|----------|----------|-------------|

| Part      | Flash    | EEPROM    | SRAM      |

|-----------|----------|-----------|-----------|

| AT90S4414 | 4K bytes | 256 bytes | 256 bytes |

| AT90S8515 | 8K bytes | 512 bytes | 512 bytes |

### **Pin Descriptions**

VCC

Supply voltage

GND

Ground

#### Port A (PA7..PA0)

Port A is an 8-bit bidirectional I/O port. Port pins can provide internal pull-up resistors (selected for each bit). The Port A output buffers can sink 20mA and can drive LED displays directly. When pins PA0 to PA7 are used as inputs and are externally pulled low, they will source current if the internal pull-up resistors are activated. The Port A pins are tri-stated when a reset condition becomes active, even if the clock is not active.

Port A serves as Multiplexed Address/Data input/output when using external SRAM.

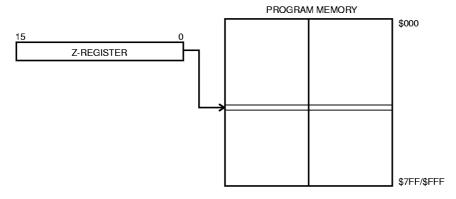

### Indirect Program Addressing, IJMP and ICALL

Figure 18. Indirect Program Memory Addressing

Program execution continues at address contained by the Z-register (i.e. the PC is loaded with the contents of the Z-register).

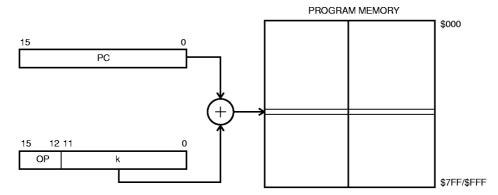

#### Relative Program Addressing, RJMP and RCALL

Figure 19. Relative Program Memory Addressing

Program execution continues at address PC + k + 1. The relative address k is -2048 to 2047.

# **EEPROM Data Memory**

The AT90S4414/8515 contains 256/512 bytes of data EEPROM memory. It is organized as a separate data space, in which single bytes can be read and written. The EEPROM has an endurance of at least 100,000 write/erase cycles. The access between the EEPROM and the CPU is described on page 39 specifying the EEPROM address registers, the EEPROM data register, and the EEPROM control register.

For the SPI data downloading, see page 77 for a detailed description.

# **Memory Access Times and Instruction Execution Timing**

This section describes the general access timing concepts for instruction execution and internal memory access.

The AVR CPU is driven by the System Clock  $\emptyset$ , directly generated from the external clock crystal for the chip. No internal clock division is used.

Figure 20 shows the parallel instruction fetches and instruction executions enabled by the Harvard architecture and the fast-access register file concept. This is the basic pipelining concept to obtain up to 1 MIPS per MHz with the corresponding unique results for functions per cost, functions per clocks, and functions per power-unit.

# I/O Memory

The I/O space definition of the AT90S4414/8515 is shown in the following table:

## Table 2. AT90S4414/8515 I/O Space

| Address Hex | Name   | Function                                           |

|-------------|--------|----------------------------------------------------|

| \$3F (\$5F) | SREG   | Status Register                                    |

| \$3E (\$5E) | SPH    | Stack Pointer High                                 |

| \$3D (\$5D) | SPL    | Stack Pointer Low                                  |

| \$3B (\$5B) | GIMSK  | General Interrupt Mask register                    |

| \$3A (\$5A) | GIFR   | General Interrupt Flag Register                    |

| \$39 (\$59) | TIMSK  | Timer/Counter Interrupt Mask register              |

| \$38 (\$58) | TIFR   | Timer/Counter Interrupt Flag register              |

| \$35 (\$55) | MCUCR  | MCU general Control Register                       |

| \$33 (\$53) | TCCR0  | Timer/Counter0 Control Register                    |

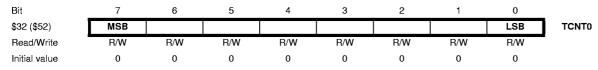

| \$32 (\$52) | TCNT0  | Timer/Counter0 (8-bit)                             |

| \$2F (\$4F) | TCCR1A | Timer/Counter1 Control Register A                  |

| \$2E (\$4E) | TCCR1B | Timer/Counter1 Control Register B                  |

| \$2D (\$4D) | TCNT1H | Timer/Counter1 High Byte                           |

| \$2C (\$4C) | TCNT1L | Timer/Counter1 Low Byte                            |

| \$2B (\$4B) | OCR1AH | Timer/Counter1 Output Compare Register A High Byte |

| \$2A (\$4A) | OCR1AL | Timer/Counter1 Output Compare Register A Low Byte  |

| \$29 (\$49) | OCR1BH | Timer/Counter1 Output Compare Register B High Byte |

| \$28 (\$48) | OCR1BL | Timer/Counter1 Output Compare Register B Low Byte  |

| \$25 (\$45) | ICR1H  | T/C 1 Input Capture Register High Byte             |

| \$24 (\$44) | ICR1L  | T/C 1 Input Capture Register Low Byte              |

| \$21 (\$41) | WDTCR  | Watchdog Timer Control Register                    |

| \$1F (\$3E) | EEARH  | EEPROM Address Register High Byte (AT90S8515)      |

| \$1E (\$3E) | EEARL  | EEPROM Address Register Low Byte                   |

| \$1D (\$3D) | EEDR   | EEPROM Data Register                               |

| \$1C (\$3C) | EECR   | EEPROM Control Register                            |

| \$1B (\$3B) | PORTA  | Data Register, Port A                              |

| \$1A (\$3A) | DDRA   | Data Direction Register, Port A                    |

| \$19 (\$39) | PINA   | Input Pins, Port A                                 |

| \$18 (\$38) | PORTB  | Data Register, Port B                              |

| \$17 (\$37) | DDRB   | Data Direction Register, Port B                    |

| \$16 (\$36) | PINB   | Input Pins, Port B                                 |

| \$15 (\$35) | PORTC  | Data Register, Port C                              |

| \$14 (\$34) | DDRC   | Data Direction Register, Port C                    |

| \$13 (\$33) | PINC   | Input Pins, Port C                                 |

#### Bit 6 - OCF1A: Output Compare Flag 1A

The OCF1A bit is set (one) when compare match occurs between the Timer/Counter1 and the data in OCR1A - Output Compare Register 1A. OCF1A is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCF1A is cleared by writing a logic one to the flag. When the I-bit in SREG, and OCIE1A (Timer/Counter1 Compare match InterruptA Enable), and the OCF1A are set (one), the Timer/Counter1 Compare A match Interrupt is executed.

#### Bit 5 - OCF1B: Output Compare Flag 1B

The OCF1B bit is set (one) when compare match occurs between the Timer/Counter1 and the data in OCR1B - Output Compare Register 1B. OCF1B is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCF1B is cleared by writing a logic one to the flag. When the I-bit in SREG, and OCIE1B (Timer/Counter1 Compare match InterruptB Enable), and the OCF1B are set (one), the Timer/Counter1 Compare B match Interrupt is executed. • Bit 4 - Res: Reserved bit

This bit is a reserved bit in the AT90S4414/8515 and always reads zero.

#### • Bit 3 - ICF1: - Input Capture Flag 1

The ICF1 bit is set (one) to flag an input capture event, indicating that the Timer/Counter1 value has been transferred to the input capture register - ICR1. ICF1 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, ICF1 is cleared by writing a logic one to the flag. When the SREG I-bit, and TICIE1 (Timer/Counter1 Input Capture Interrupt Enable), and ICF1 are set (one), the Timer/Counter1 Capture Interrupt is executed.

#### • Bit 2 - Res: Reserved bit

This bit is a reserved bit in the AT90S4414/8515 and always reads zero.

#### • Bit 1 - TOV: Timer/Counter0 Overflow Flag

The bit TOV0 is set (one) when an overflow occurs in Timer/Counter0. TOV0 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, TOV0 is cleared by writing a logic one to the flag. When the SREG Ibit, and TOIE0 (Timer/Counter0 Overflow Interrupt Enable), and TOV0 are set (one), the Timer/Counter0 Overflow interrupt is executed.

#### • Bit 0 - Res: Reserved bit

This bit is a reserved bit in the AT90S4414/8515 and always reads zero.

#### **External Interrupts**

The external interrupts are triggered by the INT1 and INT0 pins. Observe that, if enabled, the interrupts will trigger even if the INT0/INT1 pins are configured as outputs. This feature provides a way of generating a software interrupt. The external interrupts can be triggered by a falling or rising edge or a low level. This is set up as indicated in the specification for the MCU Control Register - MCUCR. When the external interrupt is enabled and is configured as level triggered, the interrupt will trigger as long as the pin is held low.

The external interrupts are set up as described in the specification for the MCU Control Register - MCUCR.

#### **Interrupt Response Time**

The interrupt execution response for all the enabled AVR interrupts is 4 clock cycles minimum. 4 clock cycles after the interrupt flag has been set, the program vector address for the actual interrupt handling routine is executed. During this 4 clock cycle period, the Program Counter (2 bytes) is pushed onto the Stack, and the Stack Pointer is decremented by 2. The vector is normally a relative jump to the interrupt routine, and this jump takes 2 clock cycles. If an interrupt occurs during execution of a multi-cycle instruction, this instruction is completed before the interrupt is served.

A return from an interrupt handling routine (same as for a subroutine call routine) takes 4 clock cycles. During these 4 clock cycles, the Program Counter (2 bytes) is popped back from the Stack, the Stack Pointer is incremented by 2, and the I flag in SREG is set. When the AVR exits from an interrupt, it will always return to the main program and execute one more instruction before any pending interrupt is served.

Note that the Status Register - SREG - is not handled by the AVR hardware, neither for interrupts nor for subroutines. For the interrupt handling routines requiring a storage of the SREG, this must be performed by user software.

For Interrupts triggered by events that can remain static (E.g. the Output Compare Register1 A matching the value of Timer/Counter1) the interrupt flag is set when the event occurs. If the interrupt flag is cleared and the interrupt condition persists, the flag will not be set until the event occurs the next time. Note that an external level interrupt will only be remembered for as long as the interrupt condition is active.

AT90S4414/8515

#### **MCU Control Register - MCUCR**

The MCU Control Register contains control bits for general MCU functions.

| Bit           | 7   | 6   | 5   | 4   | 3     | 2     | 1     | 0     | _     |

|---------------|-----|-----|-----|-----|-------|-------|-------|-------|-------|

| \$35 (\$55)   | SRE | SRW | SE  | SM  | ISC11 | ISC10 | ISC01 | ISC00 | MCUCR |

| Read/Write    | R/W | R/W | R/W | R/W | R/W   | R/W   | R/W   | R/W   | -     |

| Initial value | 0   | 0   | 0   | 0   | 0     | 0     | 0     | 0     |       |

#### • Bit 7 - SRE: External SRAM Enable

When the SRE bit is set (one), the external data SRAM is enabled, and the pin functions AD0-7 (Port A), A8-15 (Port C),  $\overline{\text{WR}}$  and  $\overline{\text{RD}}$  (Port D) are activated as the alternate pin functions. Then the SRE bit overrides any pin direction settings in the respective data direction registers. See "The SRAM Data Memory - Internal and External" for description of the External SRAM pin functions. When the SRE bit is cleared (zero), the external data SRAM is disabled, and the normal pin and data direction settings are used.

#### • Bit 6 - SRW: External SRAM Wait State

When the SRW bit is set (one), a one cycle wait state is inserted in the external data SRAM access cycle. When the SRW bit is cleared (zero), the external data SRAM access is executed with the normal three-cycle scheme. See Figure 43: External Data SRAM Memory Cycles without Wait State and Figure 44: External Data SRAM Memory Cycles with Wait State. • Bit 5 - SE: Sleep Enable

The SE bit must be set (one) to make the MCU enter the sleep mode when the SLEEP instruction is executed. To avoid the MCU entering the sleep mode unless it is the programmers purpose, it is recommended to set the Sleep Enable SE bit just before the execution of the SLEEP instruction.

#### • Bit 4 - SM: Sleep Mode

This bit selects between the two available sleep modes. When SM is cleared (zero), Idle Mode is selected as Sleep Mode. When SM is set (one), Power Down mode is selected as sleep mode. For details, refer to the paragraph "Sleep Modes" below.

#### • Bit 3, 2 - ISC11, ISC10: Interrupt Sense Control 1 bit 1 and bit 0

The External Interrupt 1 is activated by the external pin INT1 if the SREG I-flag and the corresponding interrupt mask in the GIMSK is set. The level and edges on the external INT1 pin that activate the interrupt are defined in the following table:

| ISC11 | ISC10 | Description                                              |

|-------|-------|----------------------------------------------------------|

| 0     | 0     | The low level of INT1 generates an interrupt request.    |

| 0     | 1     | Reserved                                                 |

| 1     | 0     | The falling edge of INT1 generates an interrupt request. |

| 1     | 1     | The rising edge of INT1 generates an interrupt request.  |

#### Table 6. Interrupt 1 Sense Control

Note: When changing the ISC11/ISC10 bits, INT1 must be disabled by clearing its Interrupt Enable bit in the GIMSK Register. Otherwise an interrupt can occur when the bits are changed.

#### • Bit 1, 0 - ISC01, ISC00: Interrupt Sense Control 0 bit 1 and bit 0

The External Interrupt 0 is activated by the external pin INT0 if the SREG I-flag and the corresponding interrupt mask is set. The level and edges on the external INT0 pin that activate the interrupt are defined in the following table:

#### Table 7. Interrupt 0 Sense Control

| ISC01 | ISC00 | Description                                              |

|-------|-------|----------------------------------------------------------|

| 0     | 0     | The low level of INT0 generates an interrupt request.    |

| 0     | 1     | Reserved                                                 |

| 1     | 0     | The falling edge of INT0 generates an interrupt request. |

| 1     | 1     | The rising edge of INT0 generates an interrupt request.  |

Note: When changing the ISC01/ISC00 bits, INT0 must be disabled by clearing its Interrupt Enable bit in the GIMSK Register. Otherwise an interrupt can occur when the bits are changed.

The value on the INTn pin is sampled before detecting edges. If edge interrupt is selected, pulses with a duration longer than one CPU clock period will generate an interrupt. Shorter pulses are not guaranteed to generate an interrupt. If low level interrupt is selected, the low level must be held until the completion of the currently executing instruction to generate an interrupt. If enabled, a level triggered interrupt will generate an interrupt request as long as the pin is held low.

### **Sleep Modes**

To enter the sleep modes, the SE bit in MCUCR must be set (one) and a SLEEP instruction must be executed. If an enabled interrupt occurs while the MCU is in a sleep mode, the MCU awakes, executes the interrupt routine, and resumes execution from the instruction following SLEEP. The contents of the register file, SRAM and I/O memory are unaltered. If a reset occurs during sleep mode, the MCU wakes up and executes from the Reset vector.

#### Idle Mode

When the SM bit is cleared (zero), the SLEEP instruction forces the MCU into the Idle Mode stopping the CPU but allowing Timer/Counters, Watchdog and the interrupt system to continue operating. This enables the MCU to wake up from external triggered interrupts as well as internal ones like Timer Overflow interrupt and watchdog reset. If wakeup from the Analog Comparator interrupt is not required, the analog comparator can be powered down by setting the ACD-bit in the Analog Comparator Control and Status register - ACSR. This will reduce power consumption in Idle Mode. When the MCU wakes up from Idle mode, the CPU starts program execution immediately.

#### **Power Down Mode**

When the SM bit is set (one), the SLEEP instruction forces the MCU into the Power Down Mode. In this mode, the external oscillator is stopped, while the external interrupts and the Watchdog (if enabled) continue operating. Only an external reset, a watchdog reset (if enabled), an external level interrupt on INT0 or INT1, can wake up the MCU.

Note that when a level triggered interrupt is used for wake-up from power down, the low level must be held for a time longer than the reset delay time-out period  $t_{TOUT}$ . Otherwise, the MCU will fail to wake up.

# **Timer/Counters**

The AT90S4414/8515 provides two general purpose Timer/Counters - one 8-bit T/C and one 16-bit T/C. The Timer/Counters have individual prescaling selection from the same 10-bit prescaling timer. Both Timer/Counters can either be used as a timer with an internal clock timebase or as a counter with an external pin connection which triggers the counting.

The Stop condition provides a Timer Enable/Disable function. The CK down divided modes are scaled directly from the CK oscillator clock. If the external pin modes are used for Timer/Counter0, transitions on PB0/(T0) will clock the counter even if the pin is configured as an output. This feature can give the user SW control of the counting.

#### **Timer Counter 0 - TCNT0**

The Timer/Counter0 is realized as an up-counter with read and write access. If the Timer/Counter0 is written and a clock source is present, the Timer/Counter0 continues counting in the clock cycle following the write operation.

### 16-bit Timer/Counter1

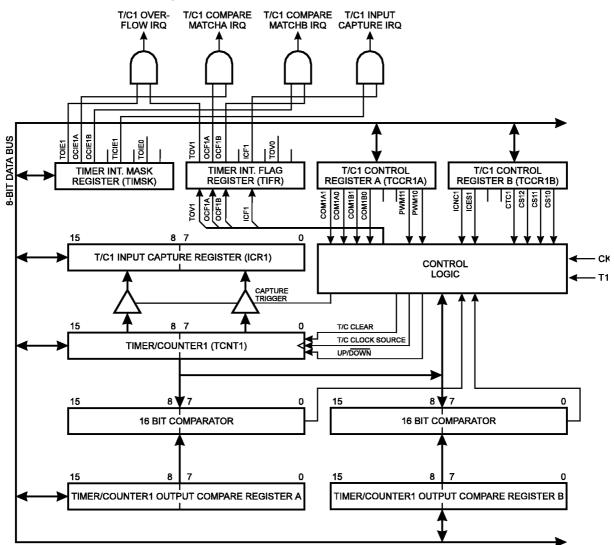

Figure 30 shows the block diagram for Timer/Counter1.

Figure 30. Timer/Counter1 Block Diagram

#### • Bit 3 - CTC1: Clear Timer/Counter1 on Compare Match

When the CTC1 control bit is set (one), the Timer/Counter1 is reset to \$0000 in the clock cycle after a compareA match. If the CTC1 control bit is cleared, Timer/Counter1 continues counting and is unaffected by a compare match. Since the compare match is detected in the CPU clock cycle following the match, this function will behave differently when a prescaling higher than 1 is used for the timer. When a prescaling of 1 is used, and the compareA register is set to C, the timer will count as follows if CTC1 is set:

#### $... \mid C\text{-}2 \mid C\text{-}1 \mid C \mid 0 \mid 1 \mid ...$

When the prescaler is set to divide by 8, the timer will count like this:

... | C-2, C-2, C-2, C-2, C-2, C-2, C-2, C-2 | C-1, C-1, C-1, C-1, C-1, C-1, C-1, C-1 | C, 0, 0, 0, 0, 0, 0, 0 | ...

In PWM mode, this bit has no effect.

#### • Bits 2,1,0 - CS12, CS11, CS10: Clock Select1, bit 2,1 and 0

The Clock Select1 bits 2,1 and 0 define the prescaling source of Timer/Counter1.

| CS12 | CS11 | CS10 | Description                          |

|------|------|------|--------------------------------------|

| 0    | 0    | 0    | Stop, the Timer/Counter1 is stopped. |

| 0    | 0    | 1    | СК                                   |

| 0    | 1    | 0    | CK/8                                 |

| 0    | 1    | 1    | CK/64                                |

| 1    | 0    | 0    | CK/256                               |

| 1    | 0    | 1    | CK/1024                              |

| 1    | 1    | 0    | External Pin T1, falling edge        |

| 1    | 1    | 1    | External Pin T1, rising edge         |

#### Table 11. Clock 1 Prescale Select

The Stop condition provides a Timer Enable/Disable function. The CK down divided modes are scaled directly from the CK oscillator clock. If the external pin modes are used for Timer/Counter1, transitions on PB1/(T1) will clock the counter even if the pin is configured as an output. This feature can give the user SW control of the counting.

#### Timer/Counter1 - TCNT1H AND TCNT1L

| Bit           | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | _      |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|--------|

| \$2D (\$4D)   | MSB |     |     |     |     |     |     |     | TCNT1H |

| \$2C (\$4C)   |     |     |     |     |     |     |     | LSB | TCNT1L |

|               | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | -      |

| Read/Write    | R/W |        |

|               | R/W |        |

| Initial value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |        |

|               | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |        |

This 16-bit register contains the prescaled value of the 16-bit Timer/Counter1. To ensure that both the high and low bytes are read and written simultaneously when the CPU accesses these registers, the access is performed using an 8-bit temporary register (TEMP). This temporary register is also used when accessing OCR1A, OCR1B and ICR1. If the main program and also interrupt routines perform access to registers using TEMP, interrupts must be disabled during access from the main program (and from interrupt routines if interrupts are allowed from within interrupt routines).

#### TCNT1 Timer/Counter1 Write:

When the CPU writes to the high byte TCNT1H, the written data is placed in the TEMP register. Next, when the CPU writes the low byte TCNT1L, this byte of data is combined with the byte data in the TEMP register, and all 16 bits are written to the TCNT1 Timer/Counter1 register simultaneously. Consequently, the high byte TCNT1H must be accessed first for a full 16-bit register write operation.

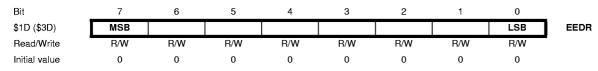

#### **EEPROM Data Register - EEDR**

#### • Bits 7..0 - EEDR7..0: EEPROM Data

For the EEPROM write operation, the EEDR register contains the data to be written to the EEPROM in the address given by the EEAR register. For the EEPROM read operation, the EEDR contains the data read out from the EEPROM at the address given by EEAR.

#### **EEPROM Control Register - EECR**

| Bit           | 7 | 6 | 5 | 4 | 3 | 2     | 1    | 0    | _    |

|---------------|---|---|---|---|---|-------|------|------|------|

| \$1C (\$3C)   | - | - | - | - | - | EEMWE | EEWE | EERE | EECR |

| Read/Write    | R | R | R | R | R | R/W   | R/W  | R/W  | -    |

| Initial value | 0 | 0 | 0 | 0 | 0 | 0     | 0    | 0    |      |

#### • Bit 7..3 - Res: Reserved bits

These bits are reserved bits in the AT90S4414/8515 and will always read as zero.

#### Bit 2 - EEMWE: EEPROM Master Write Enable

The EEMWE bit determines whether setting EEWE to one causes the EEPROM to be written. When EEMWE is set(one) setting EEWE will write data to the EEPROM at the selected address If EEMWE is zero, setting EEWE will have no effect. When EEMWE has been set (one) by software, hardware clears the bit to zero after four clock cycles. See the description of the EEWE bit for a EEPROM write procedure.

#### • Bit 1 - EEWE: EEPROM Write Enable

The EEPROM Write Enable Signal EEWE is the write strobe to the EEPROM. When address and data are correctly set up, the EEWE bit must be set to write the value into the EEPROM. The EEMWE bit must be set when the logical one is written to EEWE, otherwise no EEPROM write takes place. The following procedure should be followed when writing the EEPROM (the order of steps 2 and 3 is unessential):

- 1. Wait until EEWE becomes zero.

- 2. Write new EEPROM address to EEARL and EEARH (optional)

- 3. Write new EEPROM data to EEDR (optional)

- 4. Write a logical one to the EEMWE bit in EECR

- 5. Within four clock cycles after setting EEMWE, write a logical one to EEWE.

When the write access time (typically 2.5 ms at  $V_{CC} = 5V$  or 4 ms at  $V_{CC} = 2.7V$ ) has elapsed, the EEWE bit is cleared (zero) by hardware. The user software can poll this bit and wait for a zero before writing the next byte. When EEWE has been set, the CPU is halted for two cycles before the next instruction is executed.

Caution: An interrupt between step 4 and step 5 will make the write cycle fail, since the EEPROM Master Write Enable will time-out. If an interrupt routine accessing the EEPROM is interrupting another EEPROM access, the EEAR or EEDR register will be modified, causing the interrupted EEPROM access to fail. It is recommended to have the global interrupt flag cleared during the 4 last steps to avoid these problems.

# AT90S4414/8515

#### **UART Status Register - USR**

| Bit           | 7   | 6   | 5    | 4  | 3  | 2 | 1 | 0 | _   |

|---------------|-----|-----|------|----|----|---|---|---|-----|

| \$0B (\$2B)   | RXC | тхс | UDRE | FE | OR | - | - | - | USR |

| Read/Write    | R   | R/W | R    | R  | R  | R | R | R | -   |

| Initial value | 0   | 0   | 1    | 0  | 0  | 0 | 0 | 0 |     |

The USR register is a read-only register providing information on the UART Status.

#### • Bit 7 - RXC: UART Receive Complete

This bit is set (one) when a received character is transferred from the Receiver Shift register to UDR. The bit is set regardless of any detected framing errors. When the RXCIE bit in UCR is set, the UART Receive Complete interrupt will be executed when RXC is set(one). RXC is cleared by reading UDR. When interrupt-driven data reception is used, the UART Receive Complete Interrupt routine must read UDR in order to clear RXC, otherwise a new interrupt will occur once the interrupt routine terminates.

#### • Bit 6 - TXC: UART Transmit Complete

This bit is set (one) when the entire character (including the stop bit) in the Transmit Shift register has been shifted out and no new data has been written to UDR. This flag is especially useful in half-duplex communications interfaces, where a transmitting application must enter receive mode and free the communications bus immediately after completing the transmission.

When the TXCIE bit in UCR is set, setting of TXC causes the UART Transmit Complete interrupt to be executed. TXC is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, the TXC bit is cleared (zero) by writing a logical one to the bit.

#### Bit 5 - UDRE: UART Data Register Empty

This bit is set (one) when a character written to UDR is transferred to the Transmit shift register. Setting of this bit indicates that the transmitter is ready to receive a new character for transmission.

When the UDRIE bit in UCR is set, the UART Transmit Complete interrupt to be executed as long as UDRE is set. UDRE is cleared by writing UDR. When interrupt-driven data transmittal is used, the UART Data Register Empty Interrupt routine must write UDR in order to clear UDRE, otherwise a new interrupt will occur once the interrupt routine terminates.

UDRE is set (one) during reset to indicate that the transmitter is ready.

#### • Bit 4 - FE: Framing Error

This bit is set if a Framing Error condition is detected, i.e. when the stop bit of an incoming character is zero.

The FE bit is cleared when the stop bit of received data is one.

#### • Bit 3 - OR: Overrun

This bit is set if an Overrun condition is detected, i.e. when a character already present in the UDR register is not read before the next character has been shifted into the Receiver Shift register. The OR bit is buffered, which means that it will be set once the valid data still in UDRE is read.

The OR bit is cleared (zero) when data is received and transferred to UDR.

#### • Bits 2..0 - Res: Reserved bits

These bits are reserved bits in the AT90S4414/8515 and will always read as zero.

#### **UART Control Register - UCR**

| Bit           | 7     | 6     | 5     | 4    | 3    | 2    | 1    | 0    |     |

|---------------|-------|-------|-------|------|------|------|------|------|-----|

| \$0A (\$2A)   | RXCIE | TXCIE | UDRIE | RXEN | TXEN | CHR9 | RXB8 | TXB8 | UCR |

| Read/Write    | R/W   | R/W   | R/W   | R/W  | R/W  | R/W  | R    | W    | •   |

| Initial value | 0     | 0     | 0     | 0    | 0    | 0    | 1    | 0    |     |

#### • Bit 7 - RXCIE: RX Complete Interrupt Enable

When this bit is set (one), a setting of the RXC bit in USR will cause the Receive Complete interrupt routine to be executed provided that global interrupts are enabled.

#### Bit 6 - TXCIE: TX Complete Interrupt Enable

When this bit is set (one), a setting of the TXC bit in USR will cause the Transmit Complete interrupt routine to be executed provided that global interrupts are enabled.

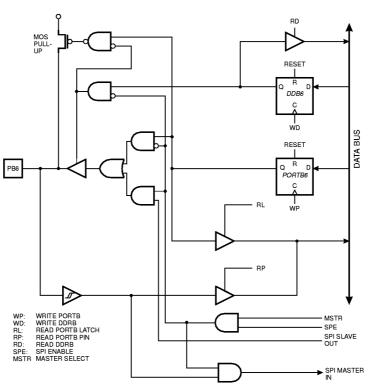

Figure 50. Port B Schematic Diagram (Pin PB6)

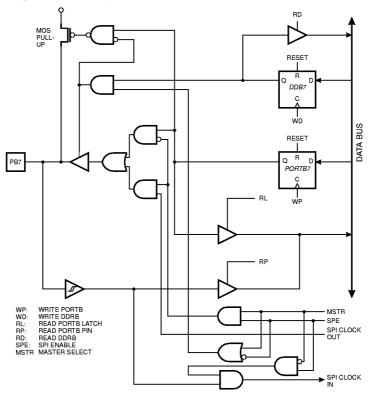

Figure 51. Port B Schematic Diagram (Pin PB7)

### **Port C Schematics**

Note that all port pins are synchronized. The synchronization latch is however, not shown in the figure.

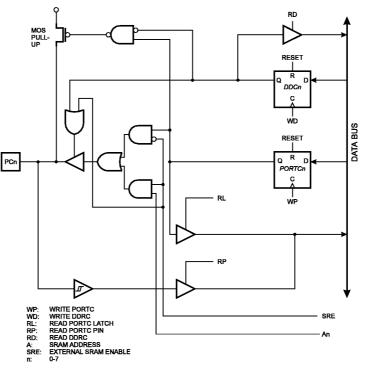

Figure 52. Port C Schematic Diagram (Pins PC0 - PC7)

# Port D

Port D is an 8 bit bi-directional I/O port with internal pull-up resistors.

Three I/O memory address locations are allocated for the Port D, one each for the Data Register - PORTD, \$12(\$32), Data Direction Register - DDRD, \$11(\$31) and the Port D Input Pins - PIND, \$10(\$30). The Port D Input Pins address is read only, while the Data Register and the Data Direction Register are read/write.

The Port D output buffers can sink 20 mA. As inputs, Port D pins that are externally pulled low will source current if the pullup resistors are activated.

Some Port D pins have alternate functions as shown in the following table:

| Port Pin | Alternate Function                                 |  |  |  |  |

|----------|----------------------------------------------------|--|--|--|--|

| PD0      | RXD (UART Input line)                              |  |  |  |  |

| PD1      | TXD (UART Output line)                             |  |  |  |  |

| PD2      | NT0 (External interrupt 0 input)                   |  |  |  |  |

| PD3      | INT1 (External interrupt 1 input)                  |  |  |  |  |

| PD5      | OC1A (Timer/Counter1 Output compareA match output) |  |  |  |  |

| PD6      | WR (Write strobe to external memory)               |  |  |  |  |

| PD7      | RD (Read strobe to external memory)                |  |  |  |  |

#### Table 24. Port D Pins Alternate Functions

When the pins are used for the alternate function the DDRD and PORTD register has to be set according to the alternate function description.

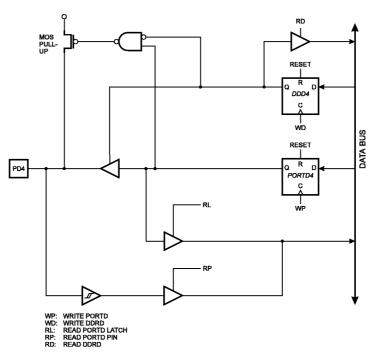

Figure 56. Port D Schematic Diagram (Pin PD4)

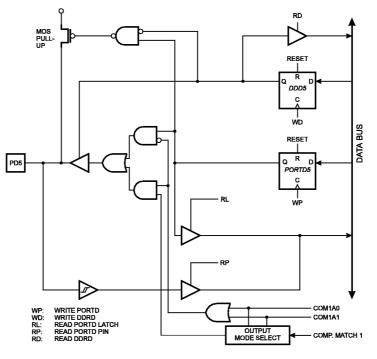

Figure 57. Port D Schematic Diagram (Pin PD5)

# **Memory Programming**

# **Program and Data Memory Lock Bits**

The AT90S4414/8515 MCU provides two Lock bits which can be left unprogrammed ('1') or can be programmed ('0') to obtain the additional features listed in Table 26. The Lock Bits can only be erased with the Chip Erase command.

| Memory Lock Bits |     | Bits | Protection Type                                                         |  |

|------------------|-----|------|-------------------------------------------------------------------------|--|

| Mode             | LB1 | LB2  |                                                                         |  |

| 1                | 1   | 1    | No memory lock features enabled.                                        |  |

| 2                | 0   | 1    | Further programming of the Flash and EEPROM is disabled. <sup>(1)</sup> |  |

| 3                | 0   | 0    | Same as mode 2, and verify is also disabled.                            |  |

#### Table 26. Lock Bit Protection Modes

Note: 1. In Parallel mode, further programming of the Fuse bits are also disabled. Program the Fuse bits before programming the Lock bits.

# **Fuse Bits**

The AT90S4414/8515 has two Fuse bits, SPIEN and FSTRT.

- When the SPIEN Fuse is programmed ('0'), Serial Program and Data Downloading is enabled. Default value is programmed ("0").

- When the FSTRT Fuse is programmed ('0'), the short start-up time is selected. Default value is unprogrammed ("1"). Parts with this bit pre-programmed ('0') can be delivered on demand.

The Fuse bits are not accessible in Serial Programming Mode. The status of the Fuse bits is not affected by Chip Erase.

# **Signature Bytes**

All Atmel microcontrollers have a three-byte signature code which identifies the device. This code can be read in both serial and parallel mode. The three bytes reside in a separate address space.

For the AT90S8515<sup>(1)</sup> they are:

- 1. \$000: \$1E (indicates manufactured by Atmel)

- 2. \$001: \$93 (indicates 8KB Flash memory)

- 3. \$002: \$01 (indicates AT90S8515 device when signature byte \$001 is \$93)

For the AT90S4414<sup>(1)</sup> they are:

- 1. \$000: \$1E (indicates manufactured by Atmel)

- 2. \$001: \$92 (indicates 4KB Flash memory)

- 3. \$002: \$01 (indicates AT90S4414 device when signature byte \$001 is \$92)

- Note: 1. When both Lock bits are programmed (Lock mode 3), the signature bytes can not be read in serial mode. Reading the signature bytes will return: \$00, \$01 and \$02.

# Programming the Flash and EEPROM

Atmel's AT90S4414/8515 offers 4K/8K bytes of In-System Reprogrammable Flash Program memory and 256/512 bytes of EEPROM Data memory.

The AT90S4414/8515 is shipped with the on-chip Flash Program and EEPROM Data memory arrays in the erased state (i.e. contents = FF) and ready to be programmed. This device supports a High-voltage (12V) Parallel programming mode and a Low-voltage Serial programming mode. The +12V is used for programming enable only, and no current of significance is drawn by this pin. The serial programming mode provides a convenient way to download program and data into the AT90S4414/8515 inside the user's system.

### Chip Erase

The Chip Erase command will erase the Flash and EEPROM memories, and the Lock bits. The Lock bits are not reset until the Flash and EEPROM have been completely erased. The Fuse bits are not changed. Chip Erase must be performed before the Flash or EEPROM is reprogrammed.

Load Command "Chip Erase"

- 1. Set XA1, XA0 to "10". This enables command loading.

- 2. Set BS to "0".

- 3. Set DATA to '1000 0000'. This is the command for Chip erase.

- 4. Give XTAL1 a positive pulse. This loads the command.

- 5. Give WR a t<sub>WLWH\_CE</sub> wide negative pulse to execute Chip Erase. See Table 31 for t<sub>WLWH\_CE</sub> value. Chip Erase does not generate any activity on the RDY/BSY pin.

#### **Programming the Flash**

A: Load Command "Write Flash"

- 1. Set XA1, XA0 to '10'. This enables command loading.

- 2. Set BS to '0'

- 3. Set DATA to '0001 0000'. This is the command for Write Flash.

- 4. Give XTAL1 a positive pulse. This loads the command.

- B: Load Address High Byte

- 1. Set XA1, XA0 to "00". This enables address loading.

- 2. Set BS to "1". This selects high byte.

- 3. Set DATA = Address high byte (\$00 \$07/\$0F)

- 4. Give XTAL1 a positive pulse. This loads the address high byte.

- C: Load Address Low Byte

- 1. Set XA1, XA0 to "00". This enables address loading.

- 2. Set BS to "0". This selects low byte.

- 3. Set DATA = Address low byte (\$00 \$FF)

- 4. Give XTAL1 a positive pulse. This loads the address low byte.

- D: Load Data Low Byte

- 1. Set XA1, XA0 to "01". This enables data loading.

- 2. Set DATA = Data low byte (\$00 \$FF)

- 3. Give XTAL1 a positive pulse. This loads the data low byte.

- E: Write Data Low Byte

- 1. Set BS to "0". This selects low data.

- 2. Give  $\overline{WR}$  a negative pulse. This starts programming of the data byte. RDY/ $\overline{BSY}$  goes low.

- 3. Wait until RDY/BSY goes high to program the next byte.

#### (See Figure 61 for signal waveforms.)

F: Load Data High Byte

- 1. Set XA1, XA0 to "01". This enables data loading.

- 2. Set DATA = Data high byte (\$00 \$FF)

- 3. Give XTAL1 a positive pulse. This loads the data high byte.

- G: Write Data High Byte

- 1. Set BS to "1". This selects high data.

- 2. Give  $\overline{WR}$  a negative pulse. This starts programming of the data byte. RDY/ $\overline{BSY}$  goes low.

# **External Clock Drive Waveforms**

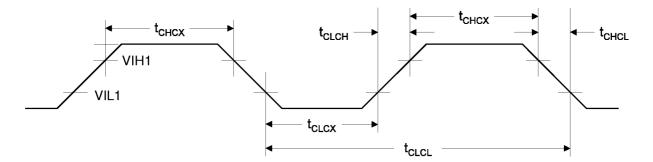

Figure 67. External Clock

#### Table 37. External Clock Drive

|                     |                      | V <sub>CC</sub> = 2.7V to 4.0V |     | V <sub>CC</sub> = 4.0V to 6.0V |     |       |

|---------------------|----------------------|--------------------------------|-----|--------------------------------|-----|-------|

| Symbol              | Parameter            | Min                            | Max | Min                            | Мах | Units |

| 1/t <sub>CLCL</sub> | Oscillator Frequency | 0                              | 4   | 0                              | 8   | MHz   |

| t <sub>CLCL</sub>   | Clock Period         | 250                            |     | 125                            |     | ns    |

| t <sub>CHCX</sub>   | High Time            | 100                            |     | 50                             |     | ns    |

| t <sub>CLCX</sub>   | Low Time             | 100                            |     | 50                             |     | ns    |

| t <sub>CLCH</sub>   | Rise Time            |                                | 1.6 |                                | 0.5 | μs    |

| t <sub>CHCL</sub>   | Fall Time            |                                | 1.6 |                                | 0.5 | μs    |

Note: See "External Data Memory Timing" on page 84. for a description of how the duty cycle influences the timing for the External Data Memory

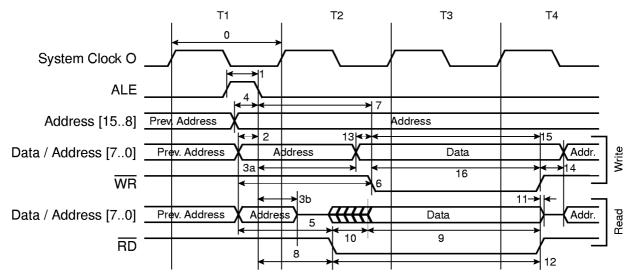

#### Figure 68. External RAM Timing

Note: Clock cycle T3 is only present when external SRAM waitstate is enabled

T3 is only present when wait-state is enabled.

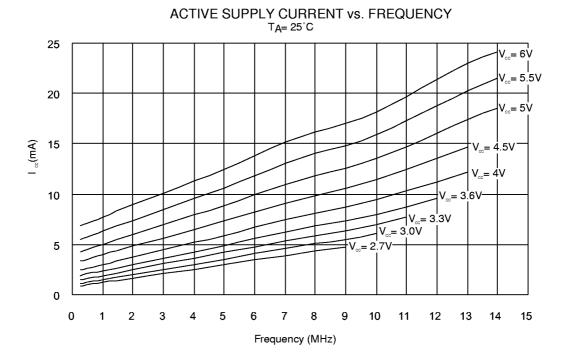

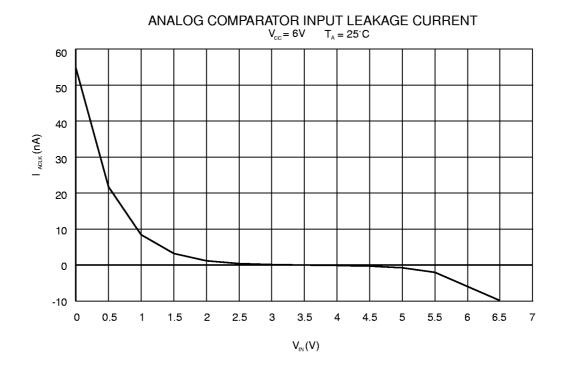

# **Typical Characteristics**

The following charts show typical behavior. These data are characterized, but not tested. All current consumption measurements are performed with all I/O pins configured as inputs and with internal pull-ups enabled. ICP pulled high externally. A sine wave generator with rail to rail output is used as clock source.

The power consumption in power-down mode is independent of clock selection.

The current consumption is a function of several factors such as: operating voltage, operating frequency, loading of I/O pins, switching rate of I/O pins, code executed and ambient temperature. The dominating factors are operating voltage and frequency.

The current drawn from capacitive loaded pins may be estimated (for one pin) as  $C_L^*V_{CC}^*f$  where  $C_L$  = load capacitance,  $V_{CC}$  = operating voltage and f = average switching frequency of I/O pin.

The parts are characterized at frequencies higher than test limits. Parts are not guaranteed to function properly at frequencies higher than the ordering code indicates.

The difference between current consumption in Power Down mode with Watchdog timer enabled and Power Down mode with Watchdog timer disabled represents the differential current drawn by the watchdog timer

Figure 69. Active Supply Current vs. Frequency

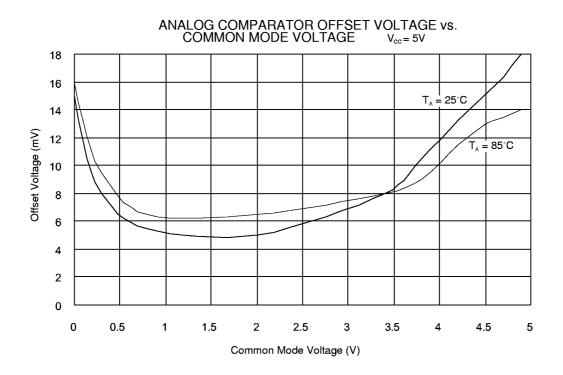

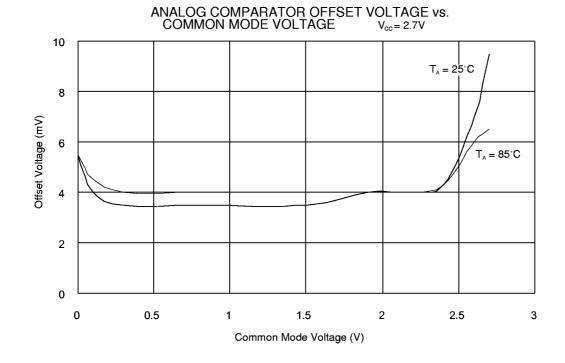

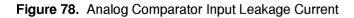

Analog comparator offset voltage is measured as absolute offset

Figure 76. Analog Comparator Offest Voltage vs. Common Mode Voltage

Figure 77. Analog Comparator Offset Voltage vs. Common Mode Voltage

Figure 79. Watchdog Oscillator Frequency vs. V<sub>CC</sub>

# AT90S4414/8515

# Instruction Set Summary

| Mnemonics     | Operands | Description                            | Operation                                             | Flags      | #Clocks |

|---------------|----------|----------------------------------------|-------------------------------------------------------|------------|---------|

| ARITHMETIC AN |          | CTIONS                                 |                                                       |            | _1      |

| ADD           | Rd, Rr   | Add two Registers                      | $Rd \leftarrow Rd + Rr$                               | Z,C,N,V,H  | 1       |

| ADC           | Rd, Rr   | Add with Carry two Registers           | $Rd \leftarrow Rd + Rr + C$                           | Z,C,N,V,H  | 1       |

| ADIW          | Rdl,K    | Add Immediate to Word                  | Rdh:Rdl ← Rdh:Rdl + K                                 | Z,C,N,V,S  | 2       |

| SUB           | Rd, Rr   | Subtract two Registers                 | Rd ← Rd - Rr                                          | Z,C,N,V,H  | 1       |

| SUBI          | Rd, K    | Subtract Constant from Register        | Rd ← Rd - K                                           | Z,C,N,V,H  | 1       |

| SBC           | Rd, Rr   | Subtract with Carry two Registers      | Rd ← Rd - Rr - C                                      | Z,C,N,V,H  | 1       |

| SBCI          | Rd, K    | Subtract with Carry Constant from Reg. | Rd ← Rd - K - C                                       | Z,C,N,V,H  | 1       |

| SBIW          | Rdl,K    | Subtract Immediate from Word           | Rdh:Rdl ← Rdh:Rdl - K                                 | Z,C,N,V,S  | 2       |

| AND           | Rd, Rr   | Logical AND Registers                  | $Rd \leftarrow Rd \bullet Rr$                         | Z,N,V      | 1       |

| ANDI          | Rd, K    | Logical AND Register and Constant      | $Rd \leftarrow Rd \bullet K$                          | Z,N,V      | 1       |

| OR            | Rd, Rr   | Logical OR Registers                   | Rd ← Rd v Rr                                          | Z,N,V      | 1       |

| ORI           | Rd, K    | Logical OR Register and Constant       | $Rd \leftarrow Rd \lor K$                             | Z,N,V      | 1       |

| EOR           | Rd, Rr   | Exclusive OR Registers                 | $Rd \leftarrow Rd \oplus Rr$                          | Z,N,V      | 1       |

| COM           | Rd       | One's Complement                       | Rd ← \$FF – Rd                                        | Z,C,N,V    | 1       |

| NEG           | Rd       | Two's Complement                       | Rd ← \$00 – Rd                                        | Z,C,N,V,H  | 1       |

| SBR           | Rd,K     | Set Bit(s) in Register                 | $Rd \leftarrow Rd \lor K$                             | Z,N,V      | 1       |

| CBR           | Rd,K     | Clear Bit(s) in Register               | $Rd \leftarrow Rd \bullet (\$FF - K)$                 | Z,N,V      | 1       |

| INC           | Rd       | Increment                              | $Rd \leftarrow Rd + 1$                                | Z,N,V      | 1       |

| DEC           | Rd       | Decrement                              | $Rd \leftarrow Rd - 1$                                | Z,N,V      | 1       |

| TST           | Rd       | Test for Zero or Minus                 | $Rd \leftarrow Rd \bullet Rd$                         | Z,N,V      | 1       |

| CLR           | Rd       | Clear Register                         | $Rd \leftarrow Rd \oplus Rd$                          | Z,N,V      | 1       |

| SER           | Rd       | Set Register                           | Rd ← \$FF                                             | None       | 1       |

| BRANCH INSTR  | UCTIONS  |                                        |                                                       |            |         |

| RJMP          | k        | Relative Jump                          | $PC \leftarrow PC + k + 1$                            | None       | 2       |

| IJMP          |          | Indirect Jump to (Z)                   | $PC \leftarrow Z$                                     | None       | 2       |

| RCALL         | k        | Relative Subroutine Call               | $PC \leftarrow PC + k + 1$                            | None       | 3       |

| ICALL         |          | Indirect Call to (Z)                   | $PC \leftarrow Z$                                     | None       | 3       |

| RET           |          | Subroutine Return                      | $PC \leftarrow STACK$                                 | None       | 4       |

| RETI          |          | Interrupt Return                       | $PC \leftarrow STACK$                                 | 1          | 4       |

| CPSE          | Rd,Rr    | Compare, Skip if Equal                 | if (Rd = Rr) PC $\leftarrow$ PC + 2 or 3              | None       | 1/2/3   |

| CP            | Rd,Rr    | Compare                                | Rd – Rr                                               | Z, N,V,C,H | 1       |

| CPC           | Rd,Rr    | Compare with Carry                     | Rd – Rr – C                                           | Z, N,V,C,H | 1       |

| CPI           | Rd,K     | Compare Register with Immediate        | Rd – K                                                | Z, N,V,C,H | 1       |

| SBRC          | Rr, b    | Skip if Bit in Register Cleared        | if $(Rr(b)=0) PC \leftarrow PC + 2 \text{ or } 3$     | None       | 1/2/3   |

| SBRS          | Rr, b    | Skip if Bit in Register is Set         | if $(Rr(b)=1) PC \leftarrow PC + 2 \text{ or } 3$     | None       | 1/2/3   |

| SBIC          | P, b     | Skip if Bit in I/O Register Cleared    | if (P(b)=0) PC $\leftarrow$ PC + 2 or 3               | None       | 1/2/3   |

| SBIS          | P, b     | Skip if Bit in I/O Register is Set     | if (P(b)=1) PC $\leftarrow$ PC + 2 or 3               | None       | 1/2/3   |

| BRBS          | s, k     | Branch if Status Flag Set              | if (SREG(s) = 1) then $PC \leftarrow PC + k + 1$      | None       | 1/2     |

| BRBC          | s, k     | Branch if Status Flag Cleared          | if (SREG(s) = 0) then $PC \leftarrow PC + k + 1$      | None       | 1/2     |

| BREQ          | k        | Branch if Equal                        | if (Z = 1) then PC $\leftarrow$ PC + k + 1            | None       | 1/2     |

| BRNE          | k        | Branch if Not Equal                    | if $(Z = 0)$ then PC $\leftarrow$ PC + k + 1          | None       | 1/2     |

| BRCS          | k        | Branch if Carry Set                    | if (C = 1) then PC $\leftarrow$ PC + k + 1            | None       | 1/2     |

| BRCC          | k        | Branch if Carry Cleared                | if (C = 0) then PC $\leftarrow$ PC + k + 1            | None       | 1/2     |

| BRSH          | k        | Branch if Same or Higher               | if (C = 0) then PC $\leftarrow$ PC + k + 1            | None       | 1/2     |

| BRLO          | k        | Branch if Lower                        | if (C = 1) then PC $\leftarrow$ PC + k + 1            | None       | 1/2     |

| BRMI          | k        | Branch if Minus                        | if (N = 1) then PC $\leftarrow$ PC + k + 1            | None       | 1/2     |

| BRPL          | k        | Branch if Plus                         | if $(N = 0)$ then PC $\leftarrow$ PC + k + 1          | None       | 1/2     |

| BRGE          | k        | Branch if Greater or Equal, Signed     | if $(N \oplus V = 0)$ then PC $\leftarrow$ PC + k + 1 | None       | 1/2     |

| BRLT          | k        | Branch if Less Than Zero, Signed       | if (N $\oplus$ V= 1) then PC $\leftarrow$ PC + k + 1  | None       | 1/2     |

| BRHS          | k        | Branch if Half Carry Flag Set          | if (H = 1) then PC $\leftarrow$ PC + k + 1            | None       | 1/2     |

| BRHC          | k        | Branch if Half Carry Flag Cleared      | if (H = 0) then PC $\leftarrow$ PC + k + 1            | None       | 1/2     |

| BRTS          | k        | Branch if T Flag Set                   | if (T = 1) then PC $\leftarrow$ PC + k + 1            | None       | 1/2     |

| BRTC          | k        | Branch if T Flag Cleared               | if (T = 0) then PC $\leftarrow$ PC + k + 1            | None       | 1/2     |

| BRVS          | k        | Branch if Overflow Flag is Set         | if (V = 1) then PC $\leftarrow$ PC + k + 1            | None       | 1/2     |

| BRVC          | k        | Branch if Overflow Flag is Cleared     | if $(V = 0)$ then PC $\leftarrow$ PC + k + 1          | None       | 1/2     |

| BRIE          | k        | Branch if Interrupt Enabled            | if (I = 1) then PC $\leftarrow$ PC + k + 1            | None       | 1/2     |

| BRID          | k        | Branch if Interrupt Disabled           | if (I = 0) then PC $\leftarrow$ PC + k + 1            | None       | 1/2     |