Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | AVR                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | SPI, UART/USART                                                         |

| Peripherals                | PWM, WDT                                                                |

| Number of I/O              | 32                                                                      |

| Program Memory Size        | 4KB (2K x 16)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 256 x 8                                                                 |

| RAM Size                   | 256 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                 |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C                                                            |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                |

| Supplier Device Package    | 40-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at90s4414-8pi |

|                            |                                                                         |

# **Description**

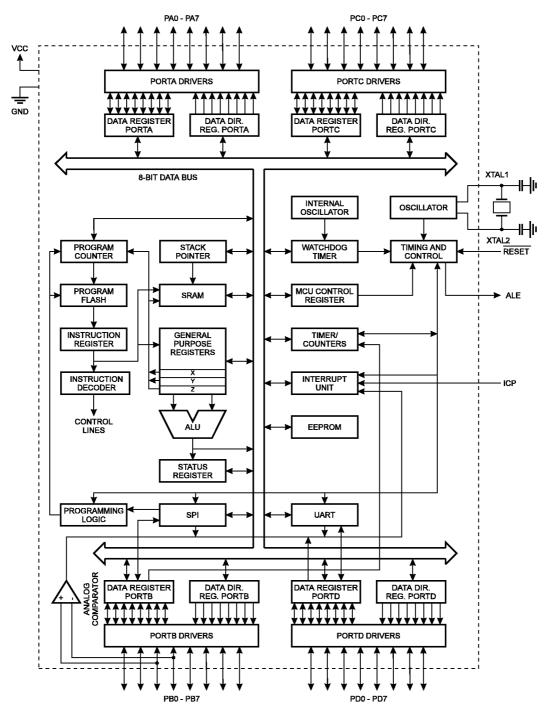

The AT90S4414/AT90S8515 is a low-power CMOS 8-bit microcontroller based on the AVR RISC architecture. By executing powerful instructions in a single clock cycle, the AT90S4414/8515 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

## **Block Diagram**

Figure 1. The AT90S4414/8515 Block Diagram

A flexible interrupt module has its control registers in the I/O space with an additional global interrupt enable bit in the status register. All the different interrupts have a separate interrupt vector in the interrupt vector table at the beginning of the program memory. The different interrupts have priority in accordance with their interrupt vector position. The lower the interrupt vector address the higher the priority.

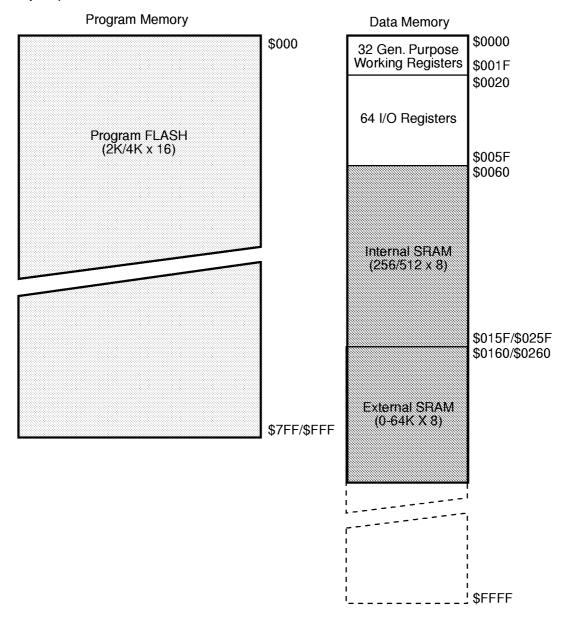

Figure 5. Memory Maps

# **ALU - Arithmetic Logic Unit**

The high-performance AVR ALU operates in direct connection with all the 32 general purpose working registers. Within a single clock cycle, ALU operations between registers in the register file are executed. The ALU operations are divided into three main categories - arithmetic, logical and bit-functions.

# **In-System Programmable Flash Program Memory**

The AT90S4414/8515 contains 4K/8K bytes on-chip In-System Programmable Flash memory for program storage. Since all instructions are 16-or 32-bit words, the Flash is organized as 2K x 16/4K x 16. The Flash memory has an endurance of at least 1000 write/erase cycles. The AT90S4414/8515 Program Counter (PC) is 11/12 bits wide, thus addressing the 2048/4096 program memory addresses.

See page 77 for a detailed description on Flash data downloading.

See page 10 for the different program memory addressing modes.

# **SRAM Data Memory - Internal and External**

The following figure shows how the AT90S4414/8515 SRAM Memory is organized:

Figure 8. SRAM Organization

| Register File | Data Address Space             |

|---------------|--------------------------------|

| R0            | \$0000                         |

| R1            | \$0001                         |

| R2            | \$0002                         |

|               |                                |

| R29           | \$001D                         |

| R30           | \$001E                         |

| R31           | \$001F                         |

| I/O Registers |                                |

| \$00          | \$0020                         |

| \$01          | \$0021                         |

| \$02          | \$0022                         |

|               |                                |

| \$3D          | \$005D                         |

| \$3E          | \$005E                         |

| \$3F          | \$005F                         |

|               | Internal SRAM                  |

|               | \$0060                         |

|               | \$0061                         |

|               | **                             |

|               | \$015E/\$025E                  |

|               | <b>\$</b> 015F/ <b>\$</b> 025F |

|               | External SRAM                  |

|               | \$0160/\$0260                  |

|               | \$0161/\$0261                  |

|               | ***                            |

|               | \$FFFE                         |

|               | \$FFFF                         |

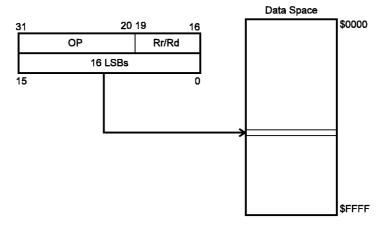

## **Data Direct**

Figure 12. Direct Data Addressing

A 16-bit Data Address is contained in the 16 LSBs of a two-word instruction. Rd/Rr specify the destination or source register.

## **Data Indirect with Displacement**

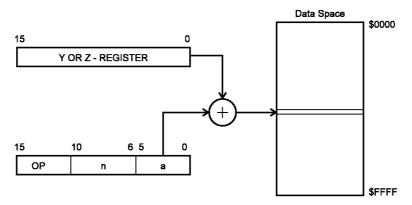

Figure 13. Data Indirect with Displacement

Operand address is the result of the Y or Z-register contents added to the address contained in 6 bits of the instruction word.

## **Data Indirect with Post-increment**

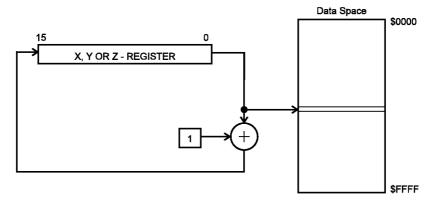

Figure 16. Data Indirect Addressing with Post-increment

The X, Y or the Z-register is incremented after the operation. Operand address is the content of the X, Y or the Z-register prior to incrementing.

## **Constant Addressing Using the LPM Instruction**

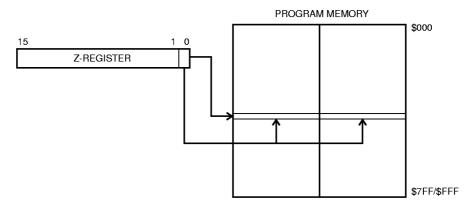

Figure 17. Code Memory Constant Addressing

Constant byte address is specified by the Z-register contents. The 15 MSBs select word address (0 - 2K/4K), the LSB selects low byte if cleared (LSB = 0) or high byte if set (LSB = 1).

#### **Reset Sources**

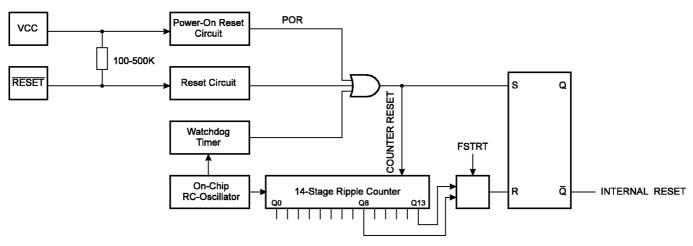

The AT90S4414/8515 has three sources of reset:

- Power-On Reset. The MCU is reset when the supply voltage is below the power-on reset threshold (V<sub>POT</sub>).

- External Reset. The MCU is reset when a low level is present on the RESET pin for more than 50 ns.

- Watchdog Reset. The MCU is reset when the Watchdog timer period expires and the Watchdog is enabled.

During reset, all I/O registers are then set to their initial values, and the program starts execution from address \$000. The instruction placed in address \$000 must be an RJMP - relative jump - instruction to the reset handling routine. If the program never enables an interrupt source, the interrupt vectors are not used, and regular program code can be placed at these locations. The circuit diagram in Figure 23 shows the reset logic. Table 4 defines the timing and electrical parameters of the reset circuitry.

Figure 23. Reset Logic

Table 4. Reset Characteristics

| Symbol                          | Parameter                                      | Min | Тур | Max                 | Units |

|---------------------------------|------------------------------------------------|-----|-----|---------------------|-------|

| V <sub>POT</sub> <sup>(1)</sup> | Power-on Reset Threshold Voltage (rising)      | 0.8 | 1.2 | 1.6                 | ٧     |

|                                 | Power-on Reset Threshold Voltage (falling)     | 0.2 | 0.4 | 0.6                 | ٧     |

| V <sub>RST</sub>                | RESET Pin Threshold Voltage                    | -   | -   | 0.9 V <sub>CC</sub> | V     |

| t <sub>TOUT</sub>               | Reset Delay Time-out Period FSTRT Unprogrammed | 11  | 16  | 21                  | ms    |

| t <sub>TOUT</sub>               | Reset Delay Time-out Period FSTRT Programmed   | 1.0 | 1.1 | 1.2                 | ms    |

Notes: 1. The Power-on Reset will not work unless the supply voltage has been below V<sub>POT</sub> (falling).

The user can select the start-up time according to typical oscillator start-up. The number of WDT oscillator cycles used for each time-out is shown in Table 5. The frequency of the watchdog oscillator is voltage dependent as shown in "Typical Characteristics" on page 86.

Table 5. Number of Watchdog Oscillator Cycles

| FSTRT        | Time-out at V <sub>CC</sub> = 5V | Number of WDT cycles |

|--------------|----------------------------------|----------------------|

| Programmed   | 1.1 ms                           | 1K                   |

| Unprogrammed | 16.0 ms                          | 16K                  |

### • Bit 6 - OCF1A: Output Compare Flag 1A

The OCF1A bit is set (one) when compare match occurs between the Timer/Counter1 and the data in OCR1A - Output Compare Register 1A. OCF1A is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCF1A is cleared by writing a logic one to the flag. When the I-bit in SREG, and OCIE1A (Timer/Counter1 Compare match InterruptA Enable), and the OCF1A are set (one), the Timer/Counter1 Compare A match Interrupt is executed.

## • Bit 5 - OCF1B: Output Compare Flag 1B

The OCF1B bit is set (one) when compare match occurs between the Timer/Counter1 and the data in OCR1B - Output Compare Register 1B. OCF1B is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCF1B is cleared by writing a logic one to the flag. When the I-bit in SREG, and OCIE1B (Timer/Counter1 Compare match InterruptB Enable), and the OCF1B are set (one), the Timer/Counter1 Compare B match Interrupt is executed.

#### · Bit 4 - Res: Reserved bit

This bit is a reserved bit in the AT90S4414/8515 and always reads zero.

### • Bit 3 - ICF1: - Input Capture Flag 1

The ICF1 bit is set (one) to flag an input capture event, indicating that the Timer/Counter1 value has been transferred to the input capture register - ICR1. ICF1 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, ICF1 is cleared by writing a logic one to the flag. When the SREG I-bit, and TICIE1 (Timer/Counter1 Input Capture Interrupt Enable), and ICF1 are set (one), the Timer/Counter1 Capture Interrupt is executed.

## • Bit 2 - Res: Reserved bit

This bit is a reserved bit in the AT90S4414/8515 and always reads zero.

## • Bit 1 - TOV: Timer/Counter0 Overflow Flag

The bit TOV0 is set (one) when an overflow occurs in Timer/Counter0. TOV0 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, TOV0 is cleared by writing a logic one to the flag. When the SREG I-bit, and TOIE0 (Timer/Counter0 Overflow Interrupt Enable), and TOV0 are set (one), the Timer/Counter0 Overflow interrupt is executed.

#### · Bit 0 - Res: Reserved bit

This bit is a reserved bit in the AT90S4414/8515 and always reads zero.

## **External Interrupts**

The external interrupts are triggered by the INT1 and INT0 pins. Observe that, if enabled, the interrupts will trigger even if the INT0/INT1 pins are configured as outputs. This feature provides a way of generating a software interrupt. The external interrupts can be triggered by a falling or rising edge or a low level. This is set up as indicated in the specification for the MCU Control Register - MCUCR. When the external interrupt is enabled and is configured as level triggered, the interrupt will trigger as long as the pin is held low.

The external interrupts are set up as described in the specification for the MCU Control Register - MCUCR.

## **Interrupt Response Time**

The interrupt execution response for all the enabled AVR interrupts is 4 clock cycles minimum. 4 clock cycles after the interrupt flag has been set, the program vector address for the actual interrupt handling routine is executed. During this 4 clock cycle period, the Program Counter (2 bytes) is pushed onto the Stack, and the Stack Pointer is decremented by 2. The vector is normally a relative jump to the interrupt routine, and this jump takes 2 clock cycles. If an interrupt occurs during execution of a multi-cycle instruction, this instruction is completed before the interrupt is served.

A return from an interrupt handling routine (same as for a subroutine call routine) takes 4 clock cycles. During these 4 clock cycles, the Program Counter (2 bytes) is popped back from the Stack, the Stack Pointer is incremented by 2, and the I flag in SREG is set. When the AVR exits from an interrupt, it will always return to the main program and execute one more instruction before any pending interrupt is served.

Note that the Status Register - SREG - is not handled by the AVR hardware, neither for interrupts nor for subroutines. For the interrupt handling routines requiring a storage of the SREG, this must be performed by user software.

For Interrupts triggered by events that can remain static (E.g. the Output Compare Register1 A matching the value of Timer/Counter1) the interrupt flag is set when the event occurs. If the interrupt flag is cleared and the interrupt condition persists, the flag will not be set until the event occurs the next time. Note that an external level interrupt will only be remembered for as long as the interrupt condition is active.

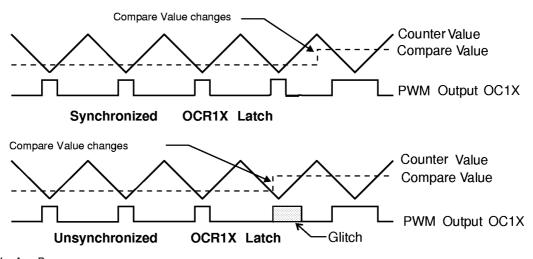

Note that in the PWM mode, the 10 least significant OCR1A/OCR1B bits, when written, are transferred to a temporary location. They are latched when Timer/Counter1 reaches the value TOP. This prevents the occurrence of odd-length PWM pulses (glitches) in the event of an unsynchronized OCR1A/OCR1B write. See Figure 32 for an example.

Figure 32. Effects on Unsynchronized OCR1 Latching

Note: X = A or B

During the time between the write and the latch operation, a read from OCR1A or OCR1B will read the contents of the temporary location. This means that the most recently written value always will read out of OCR1A/B

When the OCR1 contains \$0000 or TOP, the output OC1A/OC1B is updated to low or high on the next compare match according to the settings of COM1A1/COM1A0 or COM1B1/COM1B0. This is shown in Table .

Table 14. PWM Outputs OCR1X = \$0000 or TOP

| COM1X1 | COM1X0 | OCR1X  | Output OC1X |

|--------|--------|--------|-------------|

| 1      | 0      | \$0000 | L           |

| 1      | 0      | TOP    | Н           |

| 1      | 1      | \$0000 | Н           |

| 1      | 1      | TOP    | L           |

Note: X = A or B

In PWM mode, the Timer Overflow Flag1, TOV1, is set when the counter advances from \$0000. Timer Overflow Interrupt1 operates exactly as in normal Timer/Counter mode, i.e. it is executed when TOV1 is set provided that Timer Overflow Interrupt1 and global interrupts are enabled. This does also apply to the Timer Output Compare1 flags and interrupts.

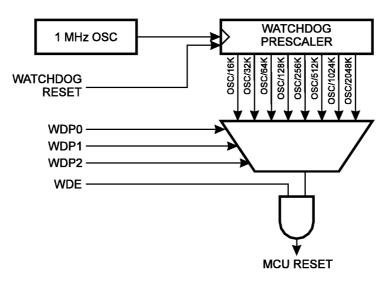

# **Watchdog Timer**

The Watchdog Timer is clocked from a separate on-chip oscillator which runs at 1MHz. This is the typical value at  $V_{CC} = 5V$ . See characterization data for typical values at other  $V_{CC}$  levels. By controlling the Watchdog Timer prescaler, the Watchdog reset interval can be adjusted, see Table 15 for a detailed description. The WDR - Watchdog Reset - instruction resets the Watchdog Timer. Eight different clock cycle periods can be selected to determine the reset period. If the reset period expires without another Watchdog reset, the AT90S4414/8515 resets and executes from the reset vector. For timing details on the Watchdog reset, refer to page 23.

To prevent unintentional disabling of the watchdog, a special turn-off sequence must be followed when the watchdog is disabled. Refer to the description of the Watchdog Timer Control Register for details.

Figure 33. Watchdog Timer

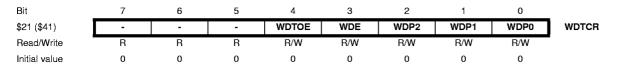

## Watchdog Timer Control Register - WDTCR

## • Bits 7..5 - Res: Reserved bits

These bits are reserved bits in the AT90S4414/8515 and will always read as zero.

#### Bit 4 - WDTOE: Watch Dog Turn-Off Enable

This bit must be set (one) when the WDE bit is cleared. Otherwise, the watchdog will not be disabled. Once set, hardware will clear this bit to zero after four clock cycles. Refer to the description of the WDE bit for a watchdog disable procedure.

### • Bit 3 - WDE: Watch Dog Enable

When the WDE is set (one) the Watchdog Timer is enabled, and if the WDE is cleared (zero) the Watchdog Timer function is disabled. WDE can only be cleared if the WDTOE bit is set(one). To disable an enabled watchdog timer, the following procedure must be followed:

- 1. In the same operation, write a logical one to WDTOE and WDE. A logical one must be written to WDE even though it is set to one before the disable operation starts.

- 2. Within the next four clock cycles, write a logical 0 to WDE. This disables the watchdog.

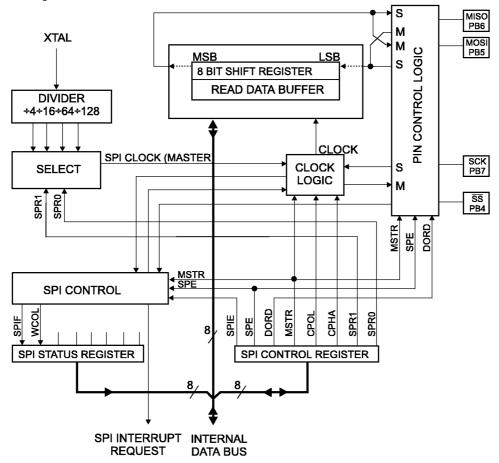

Figure 34. SPI Block Diagram

The interconnection between master and slave CPUs with SPI is shown in Figure 35. The PB7(SCK) pin is the clock output in the master mode and is the clock input in the slave mode. Writing to the SPI data register of the master CPU starts the SPI clock generator, and the data written shifts out of the PB5(MOSI) pin and into the PB5(MOSI) pin of the slave CPU. After shifting one byte, the SPI clock generator stops, setting the end of transmission flag (SPIF). If the SPI interrupt enable bit (SPIE) in the SPCR register is set, an interrupt is requested. The Slave Select input, PB4( $\overline{SS}$ ), is set low to select an individual slave SPI device. The two shift registers in the Master and the Slave can be considered as one distributed 16-bit circular shift register. This is shown in Figure 35. When data is shifted from the master to the slave, data is also shifted in the opposite direction, simultaneously. This means that during one shift cycle, data in the master and the slave are interchanged.

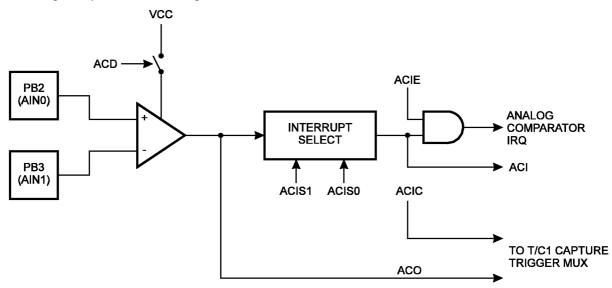

# **Analog Comparator**

The analog comparator compares the input values on the positive input PB2 (AIN0) and negative input PB3 (AIN1). When the voltage on the positive input PB2 (AIN0) is higher than the voltage on the negative input PB3 (AIN1), the Analog Comparator Output, ACO is set (one). The comparator's output can be set to trigger the Timer/Counter1 Input Capture function. In addition, the comparator can trigger a separate interrupt, exclusive to the Analog Comparator. The user can select Interrupt triggering on comparator output rise, fall or toggle. A block diagram of the comparator and its surrounding logic is shown in Figure 41.

Figure 41. Analog Comparator Block Diagram

#### **Analog Comparator Control And Status Register - ACSR**

| Bit           | 7   | 6 | 5   | 4   | 3    | 2    | 1     | 0     |      |

|---------------|-----|---|-----|-----|------|------|-------|-------|------|

| \$08 (\$28)   | ACD | - | ACO | ACI | ACIE | ACIC | ACIS1 | ACIS0 | ACSR |

| Read/Write    | R/W | R | R   | R/W | R/W  | R/W  | R/W   | R/W   |      |

| Initial value | 0   | 0 | 0   | 0   | 0    | 0    | 0     | 0     |      |

#### Bit 7 - ACD: Analog Comparator Disable

When this bit is set(one), the power to the analog comparator is switched off. This bit can be set at any time to turn off the analog comparator. This will reduce power consumption in active and idle mode. When changing the ACD bit, the Analog Comparator Interrupt must be disabled by clearing the ACIE bit in ACSR. Otherwise an interrupt can occur when the bit is changed.

#### · Bit 6 - Res: Reserved bit

This bit is a reserved bit in the AT90S4414/8515 and will always read as zero.

### Bit 5 - ACO: Analog Comparator Output

ACO is directly connected to the comparator output.

## • Bit 4 - ACI: Analog Comparator Interrupt Flag

This bit is set (one) when a comparator output event triggers the interrupt mode defined by ACI1 and ACI0. The Analog Comparator Interrupt routine is executed if the ACIE bit is set (one) and the I-bit in SREG is set (one). ACI is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, ACI is cleared by writing a logic one to the flag. Observe however, that if another bit in this register is modified using the SBI or CBI instruction, ACI will be cleared if it has become set before the operation.

#### • Bit 3 - ACIE: Analog Comparator Interrupt Enable

When the ACIE bit is set (one) and the I-bit in the Status Register is set (one), the analog comparator interrupt is activated. When cleared (zero), the interrupt is disabled.

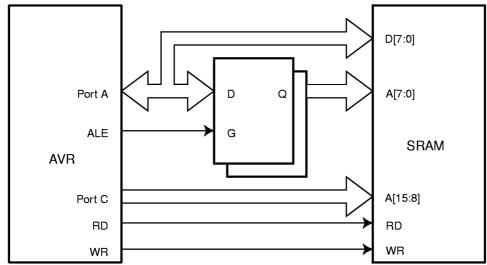

Figure 42. External SRAM Connected to the AVR

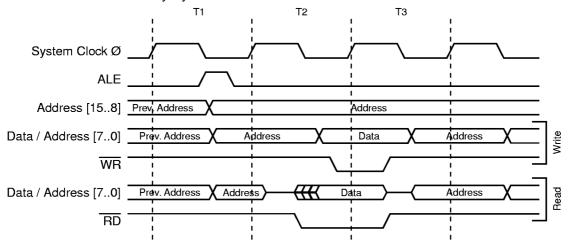

Figure 43. External Data SRAM Memory Cycles without Wait State

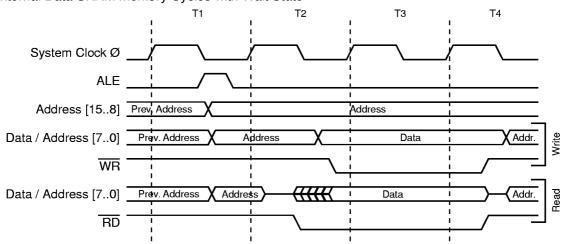

Figure 44. External Data SRAM Memory Cycles with Wait State

## Port B

Port B is an 8-bit bi-directional I/O port.

Three I/O memory address locations are allocated for the Port B, one each for the Data Register - PORTB, \$18(\$38), Data Direction Register - DDRB, \$17(\$37) and the Port B Input Pins - PINB, \$16(\$36). The Port B Input Pins address is read only, while the Data Register and the Data Direction Register are read/write.

All port pins have individually selectable pull-up resistors. The Port B output buffers can sink 20 mA and thus drive LED displays directly. When pins PB0 to PB7 are used as inputs and are externally pulled low, they will source current if the internal pull-up resistors are activated.

The Port B pins with alternate functions are shown in the following table:

Table 21. Port B Pins Alternate Functions

| Port Pin | Alternate Functions                         |  |  |  |

|----------|---------------------------------------------|--|--|--|

| PB0      | T0 (Timer/Counter 0 external counter input) |  |  |  |

| PB1      | 1 (Timer/Counter 1 external counter input)  |  |  |  |

| PB2      | IN0 (Analog comparator positive input)      |  |  |  |

| PB3      | AIN1 (Analog comparator negative input)     |  |  |  |

| PB4      | SS (SPI Slave Select input)                 |  |  |  |

| PB5      | MOSI (SPI Bus Master Output/Slave Input)    |  |  |  |

| PB6      | /ISO (SPI Bus Master Input/Slave Output)    |  |  |  |

| PB7      | SCK (SPI Bus Serial Clock)                  |  |  |  |

When the pins are used for the alternate function the DDRB and PORTB register has to be set according to the alternate function description.

## Port B Data Register - PORTB

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      | _     |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|-------|

| \$18 (\$38)   | PORTB7 | PORTB6 | PORTB5 | PORTB4 | PORTB3 | PORTB2 | PORTB1 | PORTB0 | PORTB |

| Read/Write    | R/W    |       |

| Initial value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

## Port B Data Direction Register - DDRB

| Bit           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |      |

|---------------|------|------|------|------|------|------|------|------|------|

| \$17 (\$37)   | DDB7 | DDB6 | DDB5 | DDB4 | DDB3 | DDB2 | DDB1 | DDB0 | DDRB |

| Read/Write    | R/W  | •    |

| Initial value | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |      |

### Port B Input Pins Address - PINB

| Bit           | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |      |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| \$16 (\$36)   | PINB7 | PINB6 | PINB5 | PINB4 | PINB3 | PINB2 | PINB1 | PINB0 | PINB |

| Read/Write    | R     | R     | R     | R     | R     | R     | R     | R     |      |

| Initial value | Hi-Z  |      |

The Port B Input Pins address - PINB - is not a register, and this address enables access to the physical value on each Port B pin. When reading PORTB, the Port B Data Latch is read, and when reading PINB, the logical values present on the pins are read.

## PortB as General Digital I/O

All 8 pins in port B have equal functionality when used as digital I/O pins.

PBn, General I/O pin: The DDBn bit in the DDRB register selects the direction of this pin, if DDBn is set (one), PBn is configured as an output pin. If DDBn is cleared (zero), PBn is configured as an input pin. If PORTBn is set (one) when the pin configured as an input pin, the MOS pull up resistor is activated. To switch the pull up resistor off, the PORTBn has to be cleared (zero) or the pin has to be configured as an output pin. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not active.

Table 22. DDBn Effects on Port B Pins

| DDBn | PORTBn | I/O    | Pull up | Comment                                     |

|------|--------|--------|---------|---------------------------------------------|

| 0    | 0      | Input  | No      | Tri-state (Hi-Z)                            |

| 0    | 1      | Input  | Yes     | PBn will source current if ext. pulled low. |

| 1    | 0      | Output | No      | Push-pull Zero Output                       |

| 1    | 1      | Output | No      | Push-pull One Output                        |

n: 7,6...0, pin number.

### **Alternate Functions of PortB**

The alternate pin configuration is as follows:

## · SCK - Port B, Bit 7

SCK: Master clock output, slave clock input pin for SPI channel. When the SPI is enabled as a slave, this pin is configured as an input regardless of the setting of DDB7. When the SPI is enabled as a master, the data direction of this pin is controlled by DDB7. When the pin is forced to be an input, the pull-up can still be controlled by the PORTB7 bit. See the description of the SPI port for further details.

### . MISO - Port B, Bit 6

MISO: Master data input, slave data output pin for SPI channel. When the SPI is enabled as a master, this pin is configured as an input regardless of the setting of DDB6. When the SPI is enabled as a slave, the data direction of this pin is controlled by DDB6. When the pin is forced to be an input, the pull-up can still be controlled by the PORTB6 bit. See the description of the SPI port for further details.

#### . MOSI - Port B, Bit 5

MOSI: SPI Master data output, slave data input for SPI channel. When the SPI is enabled as a slave, this pin is configured as an input regardless of the setting of DDB5. When the SPI is enabled as a master, the data direction of this pin is controlled by DDB5. When the pin is forced to be an input, the pull-up can still be controlled by the PORTB5 bit. See the description of the SPI port for further details.

#### · SS - Port B, Bit 4

SS: Slave port select input. When the SPI is enabled as a slave, this pin is configured as an input regardless of the setting of DDB4. As a slave, the SPI is activated when this pin is driven low. When the SPI is enabled as a master, the data direction of this pin is controlled by DDB4. When the pin is forced to be an input, the pull-up can still be controlled by the PORTB4 bit. See the description of the SPI port for further details.

#### • AIN1 - Port B, Bit 3

AIN1, Analog Comparator Negative Input. When configured as an input (DDB3 is cleared (zero)) and with the internal MOS pull up resistor switched off (PB3 is cleared (zero)), this pin also serves as the negative input of the on-chip analog comparator.

#### . AIN0 - Port B, Bit 2

AIN0, Analog Comparator Positive Input. When configured as an input (DDB2 is cleared (zero)) and with the internal MOS pull up resistor switched off (PB2 is cleared (zero)), this pin also serves as the positive input of the on-chip analog comparator.

### • T1 - Port B, Bit 1

T1, Timer/Counter1 counter source. See the timer description for further details

## • T0 - Port B, Bit 0

T0: Timer/Counter0 counter source. See the timer description for further details.

Table 28. Pin Name Mapping

| Signal Name in Programming Mode | Pin Name | I/O | Function                                                          |

|---------------------------------|----------|-----|-------------------------------------------------------------------|

| RDY/BSY                         | PD1      | 0   | 0: Device is busy programming, 1: Device is ready for new command |

| ŌĒ                              | PD2      | I   | Output Enable (Active low)                                        |

| WR                              | PD3      | I   | Write Pulse (Active low)                                          |

| BS                              | PD4      | I   | Byte Select ("0" selects low byte, "1" selects high byte)         |

| XA0                             | PD5      | I   | XTAL Action Bit 0                                                 |

| XA1                             | PD6      | ı   | XTAL Action Bit 1                                                 |

| DATA                            | PB7-0    | I/O | Bidirectional Databus (Output when $\overline{\text{OE}}$ is low) |

## Table 29. XA1 and XA0 Coding

| XA1 | XA0 | Action when XTAL1 is Pulsed                                             |  |

|-----|-----|-------------------------------------------------------------------------|--|

| 0   | 0   | oad Flash or EEPROM Address (High or low address byte determined by BS) |  |

| 0   | 1   | Load Data (High or Low data byte for Flash determined by BS)            |  |

| 1   | 0   | Load Command                                                            |  |

| 1   | 1   | No Action, Idle                                                         |  |

Table 30. Command Byte Bit Coding

| Command Byte | Command Executed        |

|--------------|-------------------------|

| 1000 0000    | Chip Erase              |

| 0100 0000    | Write Fuse Bits         |

| 0010 0000    | Write Lock Bits         |

| 0001 0000    | Write Flash             |

| 0001 0001    | Write EEPROM            |

| 0000 1000    | Read Signature Bytes    |

| 0000 0100    | Read Lock and Fuse Bits |

| 0000 0010    | Read Flash              |

| 0000 0011    | Read EEPROM             |

## **Enter Programming Mode**

The following algorithm puts the device in parallel programming mode:

- 1. Apply supply voltage according to Table 27, between V<sub>CC</sub> and GND.

- 2. Set the RESET and BS pin to "0" and wait at least 100 ns.

- 3. Apply 11.5 12.5V to RESET. Any activity on BS within 100 ns after +12V has been applied to RESET, will cause the device to fail entering programming mode.

# **Electrical Characteristics**

# **Absolute Maximum Ratings\***

| 1 | 9-                                                                                  |

|---|-------------------------------------------------------------------------------------|

|   | Operating Temperature55°C to +125°C                                                 |

|   | Storage Temperature65°C to +150°C                                                   |

|   | Voltage on any Pin except RESET with respect to Ground1.0V to V <sub>CC</sub> +0.5V |

|   | Voltage on RESET with respect to Ground1.0V to +13.0V                               |

|   | Maximum Operating Voltage 6.6V                                                      |

|   | DC Current per I/O Pin 40.0 mA                                                      |

|   | DC Current V <sub>CC</sub> and GND Pins200.0 mA                                     |

|   |                                                                                     |

\*NOTICE:

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **External Data Memory Timing**

Table 38. External Data Memory Characteristics, 4.0 - 6.0 Volts, No Wait State

|    |                      |                                                        | 8 MHz Oscillator |      | Variable Oscillator                       |                                           |      |

|----|----------------------|--------------------------------------------------------|------------------|------|-------------------------------------------|-------------------------------------------|------|

|    | Symbol               | Parameter                                              | Min              | Max  | Min                                       | Max                                       | Unit |

| 0  | 1/t <sub>CLCL</sub>  | Oscillator Frequency                                   |                  |      | 0.0                                       | 8.0                                       | MHz  |

| 1  | t <sub>LHLL</sub>    | ALE Pulse Width                                        | 32.5             |      | 0.5t <sub>CLCL</sub> -30.0 <sup>(1)</sup> |                                           | ns   |

| 2  | t <sub>AVLL</sub>    | Address Valid A to ALE Low                             | 22.5             |      | 0.5t <sub>CLCL</sub> -40.0 <sup>(1)</sup> |                                           | ns   |

| За | t <sub>LLAX_ST</sub> | Address Hold After ALE Low,<br>ST/STD/STS Instructions | 67.5             |      | 0.5t <sub>CLCL</sub> +5.0 <sup>(2)</sup>  |                                           | ns   |

| 3b | t <sub>LLAX_LD</sub> | Address Hold after ALE Low,<br>LD/LDD/LDS Instructions | 15.0             |      | 15.0                                      |                                           | ns   |

| 4  | t <sub>AVLLC</sub>   | Address Valid C to ALE Low                             | 22.5             |      | 0.5t <sub>CLCL</sub> -40.0 <sup>(1)</sup> |                                           | ns   |

| 5  | t <sub>AVRL</sub>    | Address Valid to RD Low                                | 95.0             |      | 1.0t <sub>CLCL</sub> -30.0                |                                           | ns   |

| 6  | t <sub>AVWL</sub>    | Address Valid to WR Low                                | 157.5            |      | 1.5t <sub>CLCL</sub> -30.0 <sup>(1)</sup> |                                           | ns   |

| 7  | t <sub>LLWL</sub>    | ALE Low to WR Low                                      | 105.0            | 145  | 1.0t <sub>CLCL</sub> -20.0                | 1.0t <sub>CLCL</sub> +20.0                | ns   |

| 8  | t <sub>LLRL</sub>    | ALE Low to RD Low                                      | 42.5             | 82.5 | 0.5t <sub>CLCL</sub> -20.0 <sup>(2)</sup> | 0.5t <sub>CLCL</sub> +20.0 <sup>(2)</sup> | ns   |

| 9  | t <sub>DVRH</sub>    | Data Setup to RD High                                  | 60.0             |      | 60.0                                      |                                           | ns   |

| 10 | t <sub>RLDV</sub>    | Read Low to Data Valid                                 |                  | 70.0 |                                           | 1.0t <sub>CLCL</sub> -55.0                | ns   |

| 11 | t <sub>RHDX</sub>    | Data Hold After RD High                                | 0.0              |      | 0.0                                       |                                           | ns   |

| 12 | t <sub>RLRH</sub>    | RD Pulse Width                                         | 105.0            |      | 1.0t <sub>CLCL</sub> -20.0                |                                           | ns   |

| 13 | t <sub>DVWL</sub>    | Data Setup to WR Low                                   | 27.5             |      | 0.5t <sub>CLCL</sub> -35.0 <sup>(2)</sup> |                                           | ns   |

| 14 | t <sub>whdx</sub>    | Data Hold After WR High                                | 0.0              |      | 0.0                                       |                                           | ns   |

| 15 | t <sub>DVWH</sub>    | Data Valid to WR High                                  | 95.0             |      | 1.0t <sub>CLCL</sub> -30.0                |                                           | ns   |

| 16 | t <sub>wLwH</sub>    | WR Pulse Width                                         | 42.5             |      | 0.5t <sub>CLCL</sub> -20.0 <sup>(1)</sup> |                                           | ns   |

Table 39. External Data Memory Characteristics, 4.0 - 6.0 Volts, 1 Cycle Wait State

|    |                     |                        | 8 MHz Oscillator |       | Variable Oscillator                       |                            |      |

|----|---------------------|------------------------|------------------|-------|-------------------------------------------|----------------------------|------|

|    | Symbol              | Parameter              | Min              | Max   | Min                                       | Max                        | Unit |

| 0  | 1/t <sub>CLCL</sub> | Oscillator Frequency   |                  |       | 0.0                                       | 8.0                        | MHz  |

| 10 | t <sub>RLDV</sub>   | Read Low to Data Valid |                  | 195.0 |                                           | 2.0t <sub>CLCL</sub> -55.0 | ns   |

| 12 | t <sub>RLRH</sub>   | RD Pulse Width         | 230.0            |       | 2.0t <sub>CLCL</sub> -20.0                |                            | ns   |

| 15 | t <sub>DVWH</sub>   | Data Valid to WR High  | 220.0            |       | 2.0t <sub>CLCL</sub> -30.0                |                            | ns   |

| 16 | t <sub>wLWH</sub>   | WR Pulse Width         | 167.5            |       | 1.5t <sub>CLCL</sub> -20.0 <sup>(2)</sup> |                            | ns   |

Notes: 1. This assumes 50% clock duty cycle. The half period is actually the high time of the external clock, XTAL1.

<sup>2.</sup> This assumes 50% clock duty cycle. The half period is actually the low time of the external clock, XTAL1.

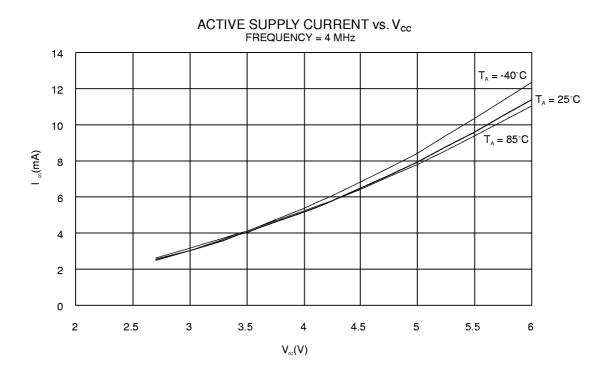

Figure 70. Active Supply Current vs. V<sub>CC</sub>

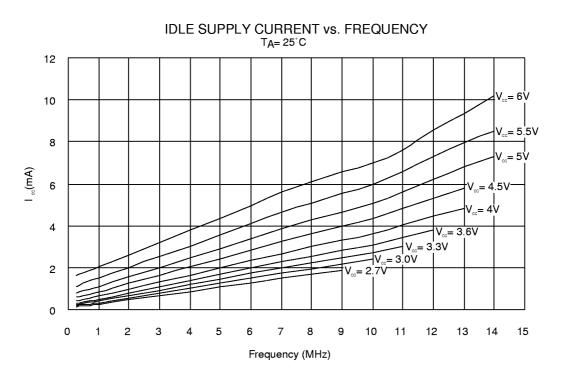

Figure 71. Idle Supply Current vs. Frequency

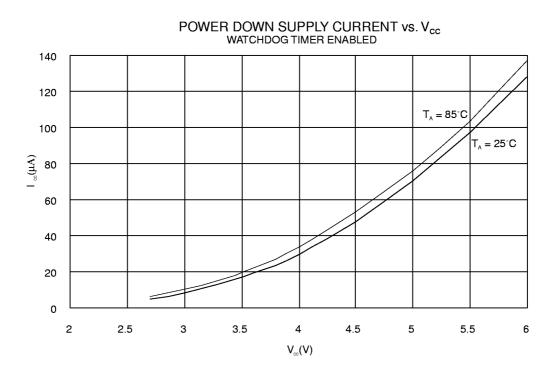

Figure 74. Power Down Supply Current vs.  $V_{\rm CC}$

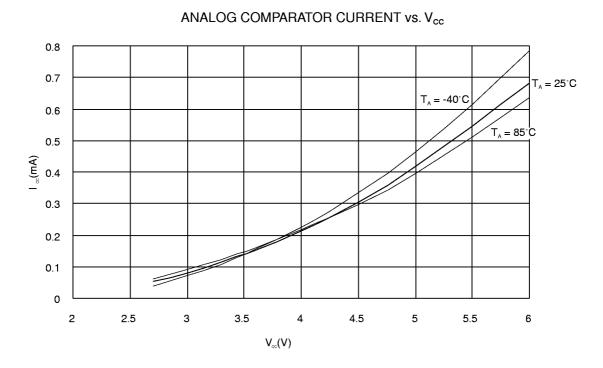

Figure 75. Analog Comparator Current vs.  $V_{\rm CC}$

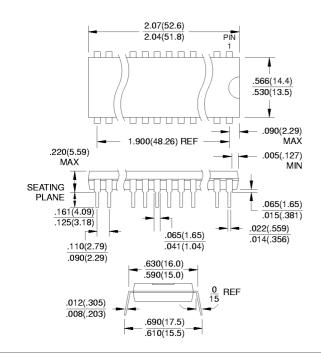

# **Packaging Information**

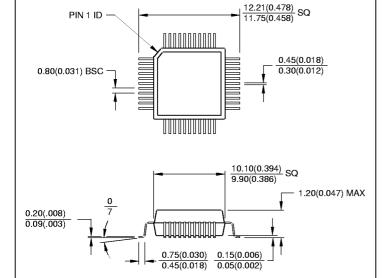

**44A**, 44-lead, Thin (1.0 mm) Plastic Gull Wing Quad Flat Package (TQFP)

Dimensions in Millimeters and (Inches)\*

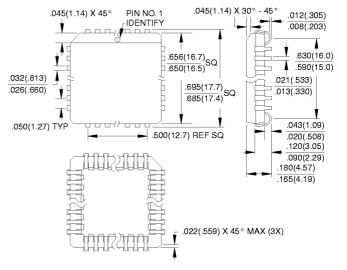

**44J**, 44-lead, Plastic J-leaded Chip Carrier (PLCC) Dimensions in Inches and (Millimeters)

\*Controlling dimension: millimeters

**40P6,** 40-lead, 0.600" Wide, Plastic Dual Inline Package (PDIP) Dimensions in Inches and (Millimeters) JEDEC STANDARD MS-011 AC