Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Obsolete                                                                        |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | SH-2                                                                            |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 50MHz                                                                           |

| Connectivity               | SCI                                                                             |

| Peripherals                | POR, PWM, WDT                                                                   |

| Number of I/O              | 23                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                       |

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | External                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 48-LQFP                                                                         |

| Supplier Device Package    | 48-LQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df71241ad50fpv |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Secti | ion 21 Electrical Characteristics                      | 711 |  |  |  |  |  |  |

|-------|--------------------------------------------------------|-----|--|--|--|--|--|--|

| 21.1  | Absolute Maximum Ratings                               |     |  |  |  |  |  |  |

| 21.2  | DC Characteristics                                     |     |  |  |  |  |  |  |

| 21.3  | AC Characteristics                                     |     |  |  |  |  |  |  |

|       | 21.3.1 Clock Timing                                    |     |  |  |  |  |  |  |

|       | 21.3.2 Control Signal Timing                           | 717 |  |  |  |  |  |  |

|       | 21.3.3 Multi Function Timer Pulse Unit 2 (MTU2) Timing |     |  |  |  |  |  |  |

|       | 21.3.4 I/O Port Timing                                 |     |  |  |  |  |  |  |

|       | 21.3.5 Watchdog Timer (WDT) Timing                     |     |  |  |  |  |  |  |

|       | 21.3.6 Serial Communication Interface (SCI) Timing     |     |  |  |  |  |  |  |

|       | 21.3.7 Port Output Enable (POE) Timing                 |     |  |  |  |  |  |  |

|       | 21.3.8 A/D Converter Timing                            |     |  |  |  |  |  |  |

|       | 21.3.9 Conditions for Testing AC Characteristics       |     |  |  |  |  |  |  |

| 21.4  | A/D Converter Characteristics                          |     |  |  |  |  |  |  |

| 21.5  | Flash Memory Characteristics                           |     |  |  |  |  |  |  |

| 21.6  | Usage Note                                             |     |  |  |  |  |  |  |

|       | 21.6.1 Notes on Connecting V <sub>CL</sub> Capacitor   |     |  |  |  |  |  |  |

| Appe  | endix                                                  | 733 |  |  |  |  |  |  |

| A.    | Pin States                                             |     |  |  |  |  |  |  |

| B.    | Product Code Lineup                                    |     |  |  |  |  |  |  |

| C.    | Package Dimensions                                     |     |  |  |  |  |  |  |

| Main  | n Revisions for This Edition                           | 745 |  |  |  |  |  |  |

| Index | x                                                      |     |  |  |  |  |  |  |

| Classification                     | Symbol                                           | I/O | Name                | Function                                                    |

|------------------------------------|--------------------------------------------------|-----|---------------------|-------------------------------------------------------------|

| A/D converter                      | AVss                                             | I   | Analog ground       | Ground pin for the A/D converter                            |

|                                    |                                                  |     |                     | Connect it to the system ground (0 V).                      |

|                                    |                                                  |     |                     | Connect all AVss pins to the system ground (0 V) correctly. |

| I/O ports                          | PA15 to PA0<br>(SH7125)                          | I/O | General port        | 16-bit input/output port pins                               |

|                                    | PA9 to PA6,<br>PA4, PA3,<br>PA1, PA0<br>(SH7124) |     |                     | 8-bit input/output port pins                                |

|                                    | PB16, PB5,<br>PB3 to PB1<br>(SH7125)             | I/O | General port        | 5-bit input/output port pins                                |

|                                    | PB5, PB3,<br>PB1<br>(SH7124)                     |     |                     | 3-bit input/output port pins                                |

|                                    | PE15 to PE0<br>(SH7125)                          | I/O | General port        | 16-bit input/output port pins                               |

|                                    | PE15 to PE8,<br>PE3 to PE0<br>(SH7124)           |     |                     | 12-bit input/output port pins                               |

|                                    | PF7 to PF0                                       | I   | General port        | 8-bit input port pins                                       |

| User debugging                     | TCK                                              | I   | Test clock          | Test-clock input pin                                        |

| interface<br>(H-UDI)* <sup>1</sup> | TMS                                              |     | Test mode select    | Inputs the test-mode select signal.                         |

|                                    | TDI                                              | I   | Test data input     | Serial input pin for instructions and data                  |

|                                    | TDO                                              | 0   | Test data<br>output | Serial output pin for instructions and data                 |

|                                    | TRST                                             |     | Test reset          | Initialization-signal input pin                             |

Section 1 Overview

| Туре                    | Kinds of<br>Instruction | Op Code | Function                                                 | Number of<br>Instructions |

|-------------------------|-------------------------|---------|----------------------------------------------------------|---------------------------|

| Branch<br>instructions  | 9                       | BF      | Conditional branch, delayed conditional branch $(T = 0)$ | 11                        |

|                         |                         | BT      | Conditional branch, delayed conditional branch $(T = 1)$ | _                         |

|                         |                         | BRA     | Unconditional branch                                     | -                         |

|                         |                         | BRAF    | Unconditional branch                                     | -                         |

|                         |                         | BSR     | Branch to subroutine procedure                           | _                         |

|                         |                         | BSRF    | Branch to subroutine procedure                           | _                         |

|                         |                         | JMP     | Unconditional branch                                     | _                         |

|                         |                         | JSR     | Branch to subroutine procedure                           | -                         |

|                         |                         | RTS     | Return from subroutine procedure                         | -                         |

| System                  | 11                      | CLRT    | T bit clear                                              | 31                        |

| control<br>instructions |                         | CLRMAC  | MAC register clear                                       | -                         |

|                         |                         | LDC     | Load into control register                               | _                         |

|                         |                         | LDS     | Load into system register                                | _                         |

|                         |                         | NOP     | No operation                                             | -                         |

|                         |                         | RTE     | Return from exception handling                           | -                         |

|                         |                         | SETT    | T bit setting                                            | -                         |

|                         |                         | SLEEP   | Transition to power-down mode                            | -                         |

|                         |                         | STC     | Store from control register                              | -                         |

|                         |                         | STS     | Store from system register                               | -                         |

|                         |                         | TRAPA   | Trap exception handling                                  | -                         |

| Total:                  | 62                      |         |                                                          | 142                       |

## 2.5.4 Logic Operation Instructions

## Table 2.13 Logic Operation Instructions

| Instru | ction            | Operation                                                        | Code             | Execution<br>Cycles | T Bit       |

|--------|------------------|------------------------------------------------------------------|------------------|---------------------|-------------|

| AND    | Rm,Rn            | $Rn \& Rm \rightarrow Rn$                                        | 0010nnnnmmm1001  | 1                   | _           |

| AND    | #imm,R0          | R0 & imm $\rightarrow$ R0                                        | 11001001iiiiiii  | 1                   | _           |

| AND.E  | #imm,@(R0,GBR)   | $(R0 + GBR) \& imm \rightarrow$<br>(R0 + GBR)                    | 11001101iiiiiii  | 3                   | _           |

| NOT    | Rm,Rn            | ${\sim}Rm \to Rn$                                                | 0110nnnnmmm0111  | 1                   | _           |

| OR     | Rm,Rn            | $Rn \mid Rm \rightarrow Rn$                                      | 0010nnnnmmm1011  | 1                   | _           |

| OR     | #imm,R0          | $R0 \mid imm \rightarrow R0$                                     | 11001011iiiiiii  | 1                   | _           |

| OR.B   | #imm,@(R0,GBR)   | $(R0 + GBR) \mid imm \rightarrow$<br>(R0 + GBR)                  | 11001111iiiiiii  | 3                   | _           |

| TAS.E  | 8 @Rn            | If (Rn) is 0, $1 \rightarrow T$ ;<br>1 $\rightarrow$ MSB of (Rn) | 0100nnnn00011011 | 4                   | Test result |

| TST    | Rm,Rn            | Rn & Rm; if the result is 0, $1 \rightarrow T$                   | 0010nnnnmmmm1000 | 1                   | Test result |

| TST    | #imm,R0          | R0 & imm; if the result is 0, $1 \rightarrow T$                  | 11001000iiiiiiii | 1                   | Test result |

| TST.E  | 8 #imm,@(R0,GBR) | (R0 + GBR) & imm; if the result is 0, $1 \rightarrow T$          | 11001100iiiiiiii | 3                   | Test result |

| XOR    | Rm,Rn            | $Rn \wedge Rm \rightarrow Rn$                                    | 0010nnnnmmm1010  | 1                   | _           |

| XOR    | #imm,R0          | R0 ^ imm $\rightarrow$ R0                                        | 11001010iiiiiii  | 1                   | _           |

| XOR.E  | 3 #imm,@(R0,GBR) | $(R0 + GBR) \wedge imm \rightarrow$<br>(R0 + GBR)                | 11001110iiiiiii  | 3                   | —           |

|               |               |               |               | Description           |                                                                   |  |  |

|---------------|---------------|---------------|---------------|-----------------------|-------------------------------------------------------------------|--|--|

| Bit 7<br>IOB3 | Bit 6<br>IOB2 | Bit 5<br>IOB1 | Bit 4<br>IOB0 | TGRB_1<br>Function    | TIOC1B Pin Function* <sup>2</sup>                                 |  |  |

| 0             | 0             | 0             | 0             | Output                | Output retained*1                                                 |  |  |

|               |               |               | 1             | compare<br>register   | Initial output is 0                                               |  |  |

|               |               |               |               | register              | 0 output at compare match                                         |  |  |

|               |               | 1             | 0             | -                     | Initial output is 0                                               |  |  |

|               |               |               |               |                       | 1 output at compare match                                         |  |  |

|               |               |               | 1             | -                     | Initial output is 0                                               |  |  |

|               |               |               |               |                       | Toggle output at compare match                                    |  |  |

|               | 1             | 0             | 0             | -                     | Output retained                                                   |  |  |

|               |               |               | 1             | -                     | Initial output is 1                                               |  |  |

|               |               |               |               |                       | 0 output at compare match                                         |  |  |

|               |               | 1             | 0             | _                     | Initial output is 1                                               |  |  |

|               |               |               |               |                       | 1 output at compare match                                         |  |  |

|               |               |               | 1             | -                     | Initial output is 1                                               |  |  |

|               |               |               |               |                       | Toggle output at compare match                                    |  |  |

| 1             | 0             | 0             | 0             |                       | Input capture at rising edge                                      |  |  |

|               |               |               | 1             | <sup>–</sup> register | Input capture at falling edge                                     |  |  |

|               |               | 1             | х             | -                     | Input capture at both edges                                       |  |  |

|               | 1             | x             | х             | _                     | Input capture at generation of TGRC_0 compare match/input capture |  |  |

#### Table 9.14 TIOR\_1 (Channel 1)

[Legend]

x: Don't care

Notes: 1. After power-on reset, 0 is output until TIOR is set.

2. The TIOC1B pin input/output function is supported only by the SH7125.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                     |

|-----|----------|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2   | SYNC2    | 0                | R/W | Timer Synchronous operation 2 to 0                                                                                                                                                                                                              |

| 1   | SYNC1    | 0                | R/W | These bits are used to select whether operation is                                                                                                                                                                                              |

| 0   | SYNC0    | 0                | R/W | independent of or synchronized with other channels.                                                                                                                                                                                             |

|     |          |                  |     | When synchronous operation is selected, the TCNT synchronous presetting of multiple channels, and synchronous clearing by counter clearing on another channel, are possible.                                                                    |

|     |          |                  |     | To set synchronous operation, the SYNC bits for at<br>least two channels must be set to 1. To set<br>synchronous clearing, in addition to the SYNC bit, the<br>TCNT clearing source must also be set by means of<br>bits CCLR0 to CCLR2 in TCR. |

|     |          |                  |     | <ol> <li>TCNT_2 to TCNT_0 operates independently (TCNT<br/>presetting /clearing is unrelated to other channels)</li> </ol>                                                                                                                      |

|     |          |                  |     | 1: TCNT_2 to TCNT_0 performs synchronous operation<br>TCNT synchronous presetting/synchronous clearing<br>is possible                                                                                                                           |

|     |          |                  |     |                                                                                                                                                                                                                                                 |

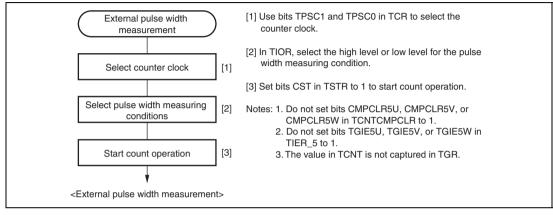

## 9.4.10 External Pulse Width Measurement

The pulse widths of up to three external input lines can be measured in channel 5.

#### **Example of External Pulse Width Measurement Setting Procedure:**

Figure 9.77 Example of External Pulse Width Measurement Setting Procedure

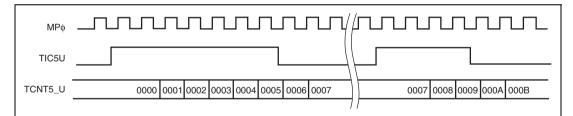

#### **Example of External Pulse Width Measurement:**

Figure 9.78 Example of External Pulse Width Measurement (Measuring High Pulse Width)

## 9.6.2 Interrupt Signal Timing

**TGF Flag Setting Timing in Case of Compare Match:** Figures 9.99 and 9.100 show the timing for setting of the TGF flag in TSR on compare match, and TGI interrupt request signal timing.

| MPø                     |         |

|-------------------------|---------|

| TCNT input clock        |         |

| TCNT                    | N N + 1 |

| TGR                     | Ν       |

| Compare<br>match signal |         |

| TGF flag                |         |

| TGI interrupt           |         |

Figure 9.99 TGI Interrupt Timing (Compare Match) (Channels 0 to 4)

| ΜΡφ                     |         |  |

|-------------------------|---------|--|

| TCNT input<br>clock     |         |  |

| TCNT                    | N - 1 N |  |

| TGR                     | Ν       |  |

| Compare<br>match signal |         |  |

| TGF flag                |         |  |

| TGI interrupt           |         |  |

Figure 9.100 TGI Interrupt Timing (Compare Match) (Channel 5)

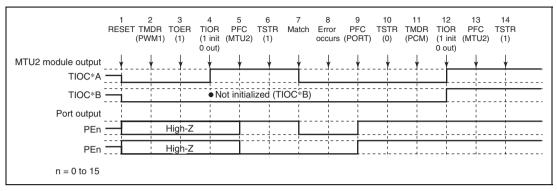

**Operation when Error Occurs during PWM Mode 1 Operation, and Operation is Restarted in Phase Counting Mode:** Figure 9.133 shows an explanatory diagram of the case where an error occurs in PWM mode 1 and operation is restarted in phase counting mode after re-setting.

Figure 9.133 Error Occurrence in PWM Mode 1, Recovery in Phase Counting Mode

1 to 10 are the same as in figure 9.130.

- 11. Set phase counting mode.

- 12. Initialize the pins with TIOR.

- 13. Set MTU2 output with the PFC.

- 14. Operation is restarted by TSTR.

- Note: Phase counting mode can only be set for channels 1 and 2, and therefore TOER setting is not necessary.

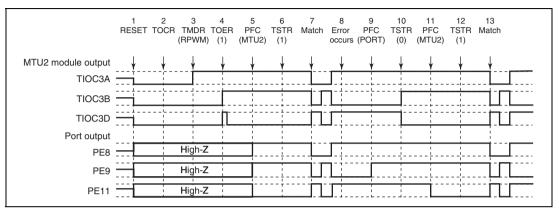

## **Operation when Error Occurs during Reset-Synchronized PWM Mode Operation, and Operation is Restarted in Reset-Synchronized PWM Mode:** Figure 9.152 shows an

explanatory diagram of the case where an error occurs in reset-synchronized PWM mode and operation is restarted in reset-synchronized PWM mode after re-setting.

1 to 10 are the same as in figure 9.149.

- 11. Set MTU2 output with the PFC.

- 12. Operation is restarted by TSTR.

- 13. The reset-synchronized PWM waveform is output on compare-match occurrence.

| Bit      | Bit Name | Initial<br>value | R/W               | Description                                                                                                                                                                                                              |

|----------|----------|------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 to 13 | 3 —      | All 0            | R                 | Reserved                                                                                                                                                                                                                 |

|          |          |                  |                   | These bits are always read as 0. The write value should always be 0.                                                                                                                                                     |

| 12       | POE8F    | 0                | R/(W)*1           | POE8 Flag                                                                                                                                                                                                                |

|          |          |                  |                   | This flag indicates that a high impedance request has been input to the $\overline{\text{POE8}}$ pin.                                                                                                                    |

|          |          |                  |                   | [Clearing conditions]                                                                                                                                                                                                    |

|          |          |                  |                   | <ul> <li>By writing 0 to POE8F after reading POE8F = 1<br/>(when the falling edge is selected by bits 1 and 0 in<br/>ICSR3).</li> </ul>                                                                                  |

|          |          |                  |                   | <ul> <li>By writing 0 to POE8F after reading POE8F = 1 after<br/>a high level input to POE8 is sampled at Pf/8, Pf/16,<br/>or Pf/128 clock (when low-level sampling is selected<br/>by bits 1 and 0 in ICSR3)</li> </ul> |

|          |          |                  |                   | [Setting condition]                                                                                                                                                                                                      |

|          |          |                  |                   | <ul> <li>When the input condition set by bits 1 and 0 in<br/>ICSR3 occurs at the POE8 pin</li> </ul>                                                                                                                     |

| 11, 10   |          | All 0            | R                 | Reserved                                                                                                                                                                                                                 |

|          |          |                  |                   | These bits are always read as 0. The write value should always be 0.                                                                                                                                                     |

| 9        | POE8E    | 0                | R/W* <sup>2</sup> | POE8 High-Impedance Enable                                                                                                                                                                                               |

|          |          |                  |                   | This bit specifies whether to place the pins in high-<br>impedance state when the POE8F bit in ICSR3 is set<br>to 1.                                                                                                     |

|          |          |                  |                   | 0: Does not place the pins in high-impedance state                                                                                                                                                                       |

|          |          |                  |                   | 1: Places the pins in high-impedance state                                                                                                                                                                               |

| 8        | PIE3     | 0                | R/W               | Port Interrupt Enable 3                                                                                                                                                                                                  |

|          |          |                  |                   | (Supported only by the SH7125. Write 0 to this bit in the SH7124.)                                                                                                                                                       |

|          |          |                  |                   | This bit enables or disables interrupt requests when the POE8 bit in ICSR3 is set to 1.                                                                                                                                  |

|          |          |                  |                   | 0: Interrupt requests disabled                                                                                                                                                                                           |

|          |          |                  |                   | 1: Interrupt requests enabled                                                                                                                                                                                            |

## Section 12 Serial Communication Interface (SCI)

This LSI has three independent serial communication interface (SCI) channels. The SCI can handle both asynchronous and clock synchronous serial communication. In asynchronous serial communication mode, serial data communication can be carried out with standard asynchronous communication chips such as a Universal Asynchronous Receiver/Transmitter (UART) or Asynchronous Communication Interface Adapter (ACIA). A function is also provided for serial communication between processors (multiprocessor communication function).

## 12.1 Features

- Choice of asynchronous or clock synchronous serial communication mode

- Asynchronous mode (channels 0 to 2 in the SH7125, channels 0 to 2 in the SH7124):

- Serial data communication is performed by start-stop in character units. The SCIF can communicate with a universal asynchronous receiver/transmitter (UART), an asynchronous communication interface adapter (ACIA), or any other communications chip that employs a standard asynchronous serial system. There are twelve selectable serial data communication formats.

- Data length: 7 or 8 bits

- Stop bit length: 1 or 2 bits

- Parity: Even, odd, or none

- Multiprocessor communications

- Receive error detection: Parity, overrun, and framing errors

- Break detection: Break is detected by reading the RXD pin level directly when a framing error occurs.

- Clock synchronous mode (channels 0 to 2 in the SH7125, channels 0 and 2 in the SH7124):

- Serial data communication is synchronized with a clock signal. The SCIF can communicate with other chips having a clock synchronous communication function.

- Data length: 8 bits

- Receive error detection: Overrun errors

- Full duplex communication: The transmitting and receiving sections are independent, so the SCI can transmit and receive simultaneously. Both sections use double buffering, so high-speed continuous data transfer is possible in both transmit and receive directions.

- On-chip baud rate generator with selectable bit rates

- Internal or external transmit/receive clock source: From either baud rate generator (internal clock) or SCK pin (external clock)

- Choice of LSB-first or MSB-first data transfer (except for 7-bit data in asynchronous mode)

|     |          | Initial |        |                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|----------|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Bit Name | value   | R/W    | Description                                                                                                                                                                                                                                                                                                                                                                        |

| 6   | RDRF     | 0       | R/(W)* | Receive Data Register Full                                                                                                                                                                                                                                                                                                                                                         |

|     |          |         |        | Indicates that the received data is stored in the receive data register (SCRDR).                                                                                                                                                                                                                                                                                                   |

|     |          |         |        | 0: Indicates that valid received data is not stored in SCRDR                                                                                                                                                                                                                                                                                                                       |

|     |          |         |        | [Clearing conditions]                                                                                                                                                                                                                                                                                                                                                              |

|     |          |         |        | By a power-on reset or in standby mode                                                                                                                                                                                                                                                                                                                                             |

|     |          |         |        | <ul> <li>When 0 is written to RDRF after reading RDRF =<br/>1</li> </ul>                                                                                                                                                                                                                                                                                                           |

|     |          |         |        | 1: Indicates that valid received data is stored in<br>SCRDR                                                                                                                                                                                                                                                                                                                        |

|     |          |         |        | [Setting condition]                                                                                                                                                                                                                                                                                                                                                                |

|     |          |         |        | When serial reception ends normally and receive<br>data is transferred from SCRSR to SCRDR                                                                                                                                                                                                                                                                                         |

|     |          |         |        | Note: SCRDR and the RDRF flag are not affected and<br>retain their previous states even if an error is<br>detected during data reception or if the RE bit in<br>the serial control register (SCSCR) is cleared to<br>0. If reception of the next data is completed<br>while the RDRF flag is still set to 1, an overrun<br>error will occur and the received data will be<br>lost. |

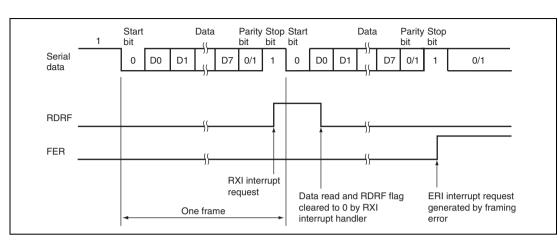

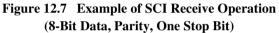

Figure 12.7 shows an example of the operation for reception.

## 12.4.3 Clock Synchronous Mode (Channel 1 in the SH7124 is not Available)

In clock synchronous mode, the SCIF transmits and receives data in synchronization with clock pulses. This mode is suitable for high-speed serial communication.

The SCI transmitter and receiver are independent, so full-duplex communication is possible while sharing the same clock. Both the transmitter and receiver have a double-buffered structure so that data can be read or written during transmission or reception, enabling continuous data transfer.

Figure 12.8 shows the general format in clock synchronous serial communication.

Figure 12.8 Data Format in Clock Synchronous Communication

## 12.5 SCI Interrupt Sources

The SCI has four interrupt sources: transmit end (TEI), receive error (ERI), receive-data-full (RXI), and transmit-data-empty (TXI) interrupt requests.

Table 12.17 shows the interrupt sources. The interrupt sources are enabled or disabled by means of the TIE, RIE, and TEIE bits in SCSCR and the EIO bit in SCSPTR. A separate interrupt request is sent to the interrupt controller for each of these interrupt sources.

When the TDRE flag in the serial status register (SCSSR) is set to 1, a TDR empty interrupt request is generated. When the RDRF flag in SCSSR is set to 1, an RDR full interrupt request is generated. When the ORER, FER, or PER flag in SCSSR is set to 1, an ERI interrupt request is generated. When the TEND flag in SCSSR is set to 1, a TEI interrupt request is generated.

The TXI interrupt indicates that transmit data can be written, and the TEI interrupt indicates that transmission has been completed.

| Interrupt Source | Description                                           |

|------------------|-------------------------------------------------------|

| ERI              | Interrupt caused by receive error (ORER, FER, or PER) |

| RXI              | Interrupt caused by receive data full (RDRF)          |

| ТХІ              | Interrupt caused by transmit data empty (TDRE)        |

| TEI              | Interrupt caused by transmit end (TENT)               |

#### **Table 12.17 SCI Interrupt Sources**

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                      |

|--------|----------|------------------|-----|------------------------------------------------------------------|

| 2 to 0 | CH[2:0]  | 000              | R/W | Channel Select 2 to 0                                            |

|        |          |                  |     | Select analog input channels. See table 13.3.                    |

|        |          |                  |     | When changing the operating mode, first clear the ADST bit to 0. |

Note: \* Writing 0 to this bit after reading it as 1 clears the flag and is the only allowed way.

## 13.3.3 A/D Control Registers\_0 and \_1 (ADCR\_0 and ADCR\_1)

ADCR for each module controls A/D conversion.

| Bit:           | 15 | 14 | 13   | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------|----|----|------|----|----|----|---|---|---|---|---|---|---|---|---|---|

| [              | -  | -  | ADST | -  | -  | -  | - | - | - | - | - | - | - | - | - | - |

| Initial value: | 0  | 0  | 0    | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| R/W:           | R  | R  | R/W  | R  | R  | R  | R | R | R | R | R | R | R | R | R | R |

|         |          | Initial |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------|----------|---------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit     | Bit Name | Value   | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 15, 14  | _        | All 0   | R   | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|         |          |         |     | These bits are always read as 0. The write value should always be 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 13      | ADST     | 0       | R/W | A/D Start                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|         |          |         |     | Starts or stops A/D conversion. When this bit is set to<br>1, A/D conversion is started. When this bit is cleared<br>to 0, A/D conversion is stopped and the A/D converter<br>enters the idle state. In single or single-cycle scan<br>mode, this bit is automatically cleared to 0 when A/D<br>conversion ends on the selected single channel. In<br>continuous scan mode, A/D conversion is continuously<br>performed for the selected channels in sequence until<br>this bit is cleared by a software, reset, or in software<br>standby mode or module standby mode. |

| 12 to 0 | _        | All 0   | R   | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|         |          |         |     | These bits are always read as 0. The write value should always be 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

#### (3.3) Flash pass/fail parameter (FPFR: general register R0 of CPU)

This parameter indicates the return value of the program processing result.

| Bit:                   | 31    | 30       | 29       | 28       | 27       | 26       | 25       | 24       | 23       | 22       | 21       | 20       | 19       | 18       | 17       | 16       |

|------------------------|-------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

|                        | -     | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        |

| Initial value:<br>R/W: |       | -<br>R/W |

| 10.00                  | 10,44 | 10/00    | 11/ 11   | 11/ 00   | 11/ V V  | 11/ 1    | 11/ 1    | 11/ 1    | 11/ 1    | 11/00    | 11/ 11   | 11/ VV   | 11/ VV   | 11/ V V  | 11/ 1    | 11/ VV   |

| Bit:                   | 15    | 14       | 13       | 12       | 11       | 10       | 9        | 8        | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

|                        | -     | -        | -        | -        | -        | -        | -        | -        | -        | MD       | EE       | FK       | -        | WD       | WA       | SF       |

| Initial value:         | -     | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        |

| R/W:                   | R/W   | R/W      | R/W      | R/W      | R/W      | R/W      | R/W      | R/W      | R/W      | R/W      | R/W      | R/W      | R/W      | R/W      | R/W      | R/W      |

| Bit     | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                                                                                           |

|---------|----------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31 to 7 | _        | Undefined        | R/W | Unused                                                                                                                                                                                                                                                                                                                                                                |

|         |          |                  |     | Return 0.                                                                                                                                                                                                                                                                                                                                                             |

| 6       | MD       | Undefined        | R/W | Programming Mode Related Setting Error Detect                                                                                                                                                                                                                                                                                                                         |

|         |          |                  |     | Returns the check result of whether the signal input to the FWE pin is high and whether the error protection state is not entered.                                                                                                                                                                                                                                    |

|         |          |                  |     | When a low-level signal is input to the FWE pin or the error protection state is entered, 1 is written to this bit. The input level to the FWE pin and the error protection state can be confirmed with the FWE bit (bit 7) and the FLER bit (bit 4) in FCCS, respectively. For conditions to enter the error protection state, see section 17.6.3, Error Protection. |

|         |          |                  |     | 0: FWE and FLER settings are normal (FWE = 1, FLER<br>= 0)                                                                                                                                                                                                                                                                                                            |

|         |          |                  |     | 1: FWE = 0 or FLER = 1, and programming cannot be<br>performed                                                                                                                                                                                                                                                                                                        |

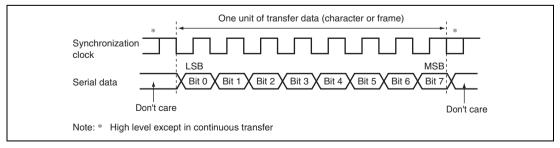

Figure 17.15 Flow of Processing by the Boot Program

• Bit-rate matching state

In bit-rate matching, the boot program measures the low-level intervals in a signal carrying H'00 data that is transmitted by the host, and calculates the bit rate from this. The bit rate can be changed by the new-bit-rate selection command. On completion of bit-rate matching, the boot program goes to the inquiry and selection state. The sequence of processing in bit-rate matching is shown in figure 17.16.

| Register<br>Abbreviation | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 | Module          |

|--------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|-----------------|

| TIORV_5                  |                   |                   | 23/21/10/3        | 20/20/12/4        | 21/13/11/3        | IOC[4:0]          | 23/11/3/1        | MTU2             |                 |

| TCNTW_5                  |                   |                   |                   |                   |                   | 100[4.0]          |                  |                  | 11102           |

| TONTW_5                  |                   |                   |                   |                   |                   |                   |                  |                  |                 |

| TGRW_5                   |                   |                   |                   |                   |                   |                   |                  |                  |                 |

|                          |                   |                   |                   |                   |                   |                   |                  |                  |                 |

| TCRW_5                   |                   |                   |                   |                   |                   |                   | TPS              | C[1:0]           |                 |

| TIORW_5                  | _                 | _                 | _                 |                   | I                 | IOC[4:0]          |                  |                  |                 |

| TSR_5                    | _                 |                   |                   | _                 |                   | CMFU5             | CMFV5            | CMFW5            |                 |

| TIER_5                   | _                 |                   |                   | _                 |                   | TGIE5U            | TGIE5V           | TGIE5W           |                 |

| TSTR_5                   | _                 | _                 | _                 | _                 | _                 | CSTU5             | CSTV5            | CSTW5            |                 |

| TCNTCMPCLR               | _                 | _                 | _                 | _                 | _                 | CMPCLR5U          | CMPCLR5V         | CMPCLR5W         |                 |

| ADDR0                    | AD9               | AD8               | AD7               | AD6               | AD5               | AD4               | AD3              | AD2              | A/D (Channel 0) |

|                          | AD1               | AD0               |                   | _                 | _                 | _                 | _                | _                |                 |

| ADDR1                    | AD9               | AD8               | AD7               | AD6               | AD5               | AD4               | AD3              | AD2              |                 |

|                          | AD1               | AD0               | _                 | —                 | _                 | _                 |                  | _                |                 |

| ADDR2                    | AD9               | AD8               | AD7               | AD6               | AD5               | AD4               | AD3              | AD2              |                 |

|                          | AD1               | AD0               |                   | —                 | _                 | —                 | _                | —                |                 |

| ADDR3                    | AD9               | AD8               | AD7               | AD6               | AD5               | AD4               | AD3              | AD2              |                 |

|                          | AD1               | AD0               |                   | —                 |                   | —                 | _                | —                |                 |

| ADCSR_0                  | ADF               | ADIE              | —                 | —                 | TRGE              | —                 | CONADF           | STC              |                 |

|                          | CKS               | L[1:0]            | ADN               | 1[1:0]            | ADCS              |                   | CH[2:0]          |                  |                 |

| ADCR_0                   | —                 | —                 | ADST              | —                 | —                 | —                 | —                | —                |                 |

|                          | —                 | —                 | —                 | —                 | —                 | —                 | _                | —                |                 |

| ADDR4                    | AD9               | AD8               | AD7               | AD6               | AD5               | AD4               | AD3              | AD2              | A/D (Channel 1) |

|                          | AD1               | AD0               | —                 | —                 | —                 | —                 | _                | —                |                 |

| ADDR5                    | AD9               | AD8               | AD7               | AD6               | AD5               | AD4               | AD3              | AD2              |                 |

|                          | AD1               | AD0               | —                 | —                 | —                 | —                 | _                | —                |                 |

| ADDR6                    | AD9               | AD8               | AD7               | AD6               | AD5               | AD4               | AD3              | AD2              |                 |

|                          | AD1               | AD0               | _                 | _                 | _                 | —                 | _                | —                |                 |

| ADDR7                    | AD9               | AD8               | AD7               | AD6               | AD5               | AD4               | AD3              | AD2              |                 |

|                          | AD1               | AD0               | —                 | —                 | —                 | —                 | _                | —                |                 |

# SH7125 Group, SH7124 Group Hardware Manual

Renesas Electronics Corporation 1753, Shimonumabe, Nakahara-ku, Kawasaki-shi, Kanagawa 211-8668 Japan

REJ09B0243-0500