# Welcome to <u>E-XFL.COM</u>

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | SH-2                                                                              |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 50MHz                                                                             |

| Connectivity               | SCI                                                                               |

| Peripherals                | POR, PWM, WDT                                                                     |

| Number of I/O              | 23                                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                         |

| Data Converters            | A/D 8x10b                                                                         |

| Oscillator Type            | External                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 52-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 52-VQFN (7x7)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df71242d50npv-z1 |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The instruction code, operation, and execution cycles of the instructions are listed in the following tables, classified by type.

| Instruction                                                                                                                                                                                            | Instruction Code                                                                                                                              | Summary of<br>Operation                                                                                                                                                                                                                                                                                                                                              | Execution<br>Cycles | T Bit                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------------------------------------------------------------|

| Indicated by mnemonic.                                                                                                                                                                                 | Indicated in MSB $\leftrightarrow$ LSB order.                                                                                                 | Indicates summary of operation.                                                                                                                                                                                                                                                                                                                                      |                     | Value of T bit after<br>instruction is executed<br>Explanation of Symbols |

| Explanation of Symbols                                                                                                                                                                                 | Explanation of Symbols                                                                                                                        | Explanation of Symbols                                                                                                                                                                                                                                                                                                                                               |                     | —: No change                                                              |

| OP.Sz SRC, DEST<br>OP: Operation code<br>Sz: Size<br>SRC: Source<br>DEST: Destination<br>Rm: Source register<br>Rn: Destination<br>register<br>imm: Immediate data<br>disp: Displacement* <sup>2</sup> | mmmm: Source register<br>nnnn: Destination<br>register<br>0000: R0<br>0001: R1<br><br>1111: R15<br>iiii: Immediate data<br>dddd: Displacement | <ul> <li>→, ←: Transfer direction</li> <li>(xx): Memory operand</li> <li>M/Q/T: Flag bits in SR</li> <li>&amp;: Logical AND of each bit</li> <li> : Logical OR of each bit</li> <li>A: Exclusive logical OR of each bit</li> <li>→: Logical NOT of each bit</li> <li>&lt;<n: left="" li="" n-bit="" shift<=""> <li>&gt;&gt;n: n-bit right shift</li> </n:></li></ul> |                     |                                                                           |

Notes: 1. The table shows the minimum number of execution states. In practice, the number of instruction execution states will be increased in cases such as the following:

- When there is contention between an instruction fetch and a data access

- When the destination register of a load instruction (memory  $\rightarrow$  register) is also used by the following instruction

- Scaled (×1, ×2, or ×4) according to the instruction operand size, etc. For details, see SH-1/SH-2/SH-DSP Software Manual.

# 3.2 Input/Output Pins

Table 3.2 describes the configuration of operating mode related pin.

# Table 3.2Pin Configuration

| Pin Name | Input/Output | Function                                                              |

|----------|--------------|-----------------------------------------------------------------------|

| MD1      | Input        | Designates operating mode through the level applied to this pin       |

| FWE      | Input        | Enables, by hardware, programming/erasing of the on-chip flash memory |

# 3.3 Operating Modes

# 3.3.1 Mode 3 (Single Chip Mode)

All ports can be used in this mode, however the external address cannot be used.

# 6.2 Input/Output Pins

Table 6.1 shows the INTC pin configuration.

# Table 6.1Pin Configuration

| Name                             | Abbr.           | I/O    | Function                                                        |

|----------------------------------|-----------------|--------|-----------------------------------------------------------------|

| Non-maskable interrupt input pin | NMI             | Input  | Input of non-maskable interrupt request signal                  |

| Interrupt request input pins     | IRQ0 to<br>IRQ3 | Input  | Input of maskable interrupt request signals                     |

| Interrupt request output pin     | IRQOUT          | Output | Output of notification signal when an<br>interrupt has occurred |

| Bit      | Bit Name   | Initial<br>Value | R/W | Description                                                 |

|----------|------------|------------------|-----|-------------------------------------------------------------|

| 15 to 12 | IPR[15:12] | 0000             | R/W | Set priority levels for the corresponding interrupt source. |

|          |            |                  |     | 0000: Priority level 0 (lowest)                             |

|          |            |                  |     | 0001: Priority level 1                                      |

|          |            |                  |     | 0010: Priority level 2                                      |

|          |            |                  |     | 0011: Priority level 3                                      |

|          |            |                  |     | 0100: Priority level 4                                      |

|          |            |                  |     | 0101: Priority level 5                                      |

|          |            |                  |     | 0110: Priority level 6                                      |

|          |            |                  |     | 0111: Priority level 7                                      |

|          |            |                  |     | 1000: Priority level 8                                      |

|          |            |                  |     | 1001: Priority level 9                                      |

|          |            |                  |     | 1010: Priority level 10                                     |

|          |            |                  |     | 1011: Priority level 11                                     |

|          |            |                  |     | 1100: Priority level 12                                     |

|          |            |                  |     | 1101: Priority level 13                                     |

|          |            |                  |     | 1110: Priority level 14                                     |

|          |            |                  |     | 1111: Priority level 15 (highest)                           |

| 11 to 8  | IPR[11:8]  | 0000             | R/W | Set priority levels for the corresponding interrupt source. |

|          |            |                  |     | 0000: Priority level 0 (lowest)                             |

|          |            |                  |     | 0001: Priority level 1                                      |

|          |            |                  |     | 0010: Priority level 2                                      |

|          |            |                  |     | 0011: Priority level 3                                      |

|          |            |                  |     | 0100: Priority level 4                                      |

|          |            |                  |     | 0101: Priority level 5                                      |

|          |            |                  |     | 0110: Priority level 6                                      |

|          |            |                  |     | 0111: Priority level 7                                      |

|          |            |                  |     | 1000: Priority level 8                                      |

|          |            |                  |     | 1001: Priority level 9                                      |

|          |            |                  |     | 1010: Priority level 10                                     |

|          |            |                  |     | 1011: Priority level 11                                     |

|          |            |                  |     | 1100: Priority level 12                                     |

|          |            |                  |     | 1101: Priority level 13                                     |

|          |            |                  |     | 1110: Priority level 14                                     |

|          |            |                  |     | 1111: Priority level 15 (highest)                           |

### 7.2.12 Execution Times Break Register (BETR)

BETR is a 16-bit readable/writable register. When the execution-times break condition of channel B is enabled, this register specifies the number of execution times to make the break. The maximum number is  $2^{12} - 1$  times. When a break condition is satisfied, it decreases BETR. A userbreak interrupt is requested when the break condition is satisfied after BETR becomes H'0001.

| Bit:           | 15  | 14     | 13   | 12     | 11  | 10  | 9                                                                    | 8      | 7   | 6        | 5   | 4   | 3   | 2   | 1   | 0   |

|----------------|-----|--------|------|--------|-----|-----|----------------------------------------------------------------------|--------|-----|----------|-----|-----|-----|-----|-----|-----|

|                | -   | -      | -    | -      |     |     |                                                                      |        | E   | BET[11:0 | ]   |     |     |     |     |     |

| Initial value: | 0   | 0      | 0    | 0      | 0   | 0   | 0                                                                    | 0      | 0   | 0        | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W:           | R   | R      | R    | R      | R/W | R/W | R/W                                                                  | R/W    | R/W | R/W      | R/W | R/W | R/W | R/W | R/W | R/W |

|                |     |        |      |        |     |     |                                                                      |        |     |          |     |     |     |     |     |     |

|                |     |        | h    | nitial |     |     |                                                                      |        |     |          |     |     |     |     |     |     |

| Bit            | Bit | t Name | e V  | alue   | R/  | W   | Des                                                                  | cripti | on  |          |     |     |     |     |     |     |

| 15 to 12       |     |        | Α    | VII 0  | R   |     | Res                                                                  | erved  |     |          |     |     |     |     |     |     |

|                |     |        |      |        |     |     | These bits are always read as 0. The write value should always be 0. |        |     |          |     |     |     |     |     |     |

| 11 to 0        | BE  | T[11:C | )] A | 0 11   | R/  | W   | Number of Execution Times                                            |        |     |          |     |     |     |     |     |     |

### Table 9.17 TIORL\_3 (Channel 3)

|               |               |               |               | Description                                        |                                |  |  |  |  |  |

|---------------|---------------|---------------|---------------|----------------------------------------------------|--------------------------------|--|--|--|--|--|

| Bit 7<br>IOD3 | Bit 6<br>IOD2 | Bit 5<br>IOD1 | Bit 4<br>IOD0 | TGRD_3<br>Function                                 | TIOC3D Pin Function            |  |  |  |  |  |

| 0             | 0             | 0             | 0             | Output                                             | Output retained*1              |  |  |  |  |  |

|               |               |               | 1             | compare Initial output is 0 register* <sup>2</sup> |                                |  |  |  |  |  |

|               |               |               |               | register                                           | 0 output at compare match      |  |  |  |  |  |

|               |               | 1             | 0             | _                                                  | Initial output is 0            |  |  |  |  |  |

|               |               |               |               |                                                    | 1 output at compare match      |  |  |  |  |  |

|               |               |               | 1             | _                                                  | Initial output is 0            |  |  |  |  |  |

|               |               |               |               |                                                    | Toggle output at compare match |  |  |  |  |  |

|               | 1             | 0             | 0             | _                                                  | Output retained                |  |  |  |  |  |

|               |               |               | 1             | _                                                  | Initial output is 1            |  |  |  |  |  |

|               |               |               |               |                                                    | 0 output at compare match      |  |  |  |  |  |

|               |               | 1             | 0             |                                                    | Initial output is 1            |  |  |  |  |  |

|               |               |               |               |                                                    | 1 output at compare match      |  |  |  |  |  |

|               |               |               | 1             | _                                                  | Initial output is 1            |  |  |  |  |  |

|               |               |               |               |                                                    | Toggle output at compare match |  |  |  |  |  |

| 1             | х             | 0             | 0             |                                                    | Input capture at rising edge   |  |  |  |  |  |

|               |               |               | 1             | register* <sup>2</sup>                             | Input capture at falling edge  |  |  |  |  |  |

|               |               | 1             | х             | _                                                  | Input capture at both edges    |  |  |  |  |  |

| [] egen       | dl            |               |               |                                                    |                                |  |  |  |  |  |

Description

[Legend]

Don't care x:

Notes: 1. After power-on reset, 0 is output until TIOR is set.

2. When the BFB bit in TMDR\_3 is set to 1 and TGRD\_3 is used as a buffer register, this setting is invalid and input capture/output compare is not generated.

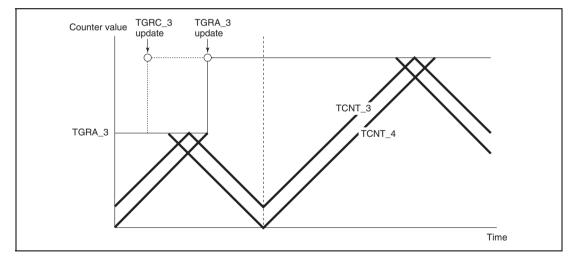

7. PWM Cycle Setting

In complementary PWM mode, the PWM pulse cycle is set in two registers—TGRA\_3, in which the TCNT\_3 upper limit value is set, and TCDR, in which the TCNT\_4 upper limit value is set. The settings should be made so as to achieve the following relationship between these two registers:

With dead time: TGRA\_3 set value = TCDR set value + TDDR set value Without dead time: TGRA\_3 set value = TCDR set value + 1

The TGRA\_3 and TCDR settings are made by setting the values in buffer registers TGRC\_3 and TCBR. The values set in TGRC\_3 and TCBR are transferred simultaneously to TGRA\_3 and TCDR in accordance with the transfer timing selected with bits MD3 to MD0 in the timer mode register (TMDR).

The updated PWM cycle is reflected from the next cycle when the data update is performed at the crest, and from the current cycle when performed in the trough. Figure 9.42 illustrates the operation when the PWM cycle is updated at the crest.

See the following section, Register Data Updating, for the method of updating the data in each buffer register.

Figure 9.42 Example of PWM Cycle Updating

3. Buffer Transfer Control Linked with Interrupt Skipping

In complementary PWM mode, whether to transfer data from a buffer register to a temporary register and whether to link the transfer with interrupt skipping can be specified with the BTE1 and BTE0 bits in the timer buffer transfer set register (TBTER).

Figure 9.70 shows an example of operation when buffer transfer is suppressed (BTE1 = 0 and BTE0 = 1). While this setting is valid, data is not transferred from the buffer register to the temporary register.

Figure 9.71 shows an example of operation when buffer transfer is linked with interrupt skipping (BTE1 = 1 and BET0 = 0). While this setting is valid, data is not transferred from the buffer register outside the buffer transfer-enabled period.

The data transfer timing is two types. That is, from the buffer register to the temporary register and from the temporary register to the buffer register. These timings depend on a programming timing to the buffer register after an interrupt is generated.

Note that the buffer transfer-enabled period depends on the T3AEN and T4VEN bit settings in the timer interrupt skipping set register (TITCR). Figure 9.72 shows the relationship between the T3AEN and T4VEN bit settings in TITCR and buffer transfer-enabled period.

Note: This function must always be used in combination with interrupt skipping. When interrupt skipping is disabled (the T3AEN and T4VEN bits in the timer interrupt skipping set register (TITCR) are cleared to 0 or the skipping count set bits (3ACOR and 4VCOR) in TITCR are cleared to 0), make sure that buffer transfer is not linked with interrupt skipping (clear the BTE1 bit in the timer buffer transfer set register (TBTER) to 0). If buffer transfer is linked with interrupt skipping while interrupt skipping is disabled, buffer transfer is never performed.

### **Complementary PWM Mode Output Protection Function:**

Complementary PWM mode output has the following protection functions.

1. Register and counter miswrite prevention function

With the exception of the buffer registers, which can be rewritten at any time, access by the CPU can be enabled or disabled for the mode registers, control registers, compare registers, and counters used in complementary PWM mode by means of the RWE bit in the timer read/write enable register (TRWER). The applicable registers are some (21 in total) of the registers in channels 3 and 4 shown in the following:

— TCR\_3 and TCR\_4, TMDR\_3 and TMDR\_4, TIORH\_3 and TIORH\_4, TIORL\_3 and TIORL\_4, TIER\_3 and TIER\_4, TCNT\_3 and TCNT\_4, TGRA\_3 and TGRA\_4, TGRB\_3 and TGRB\_4, TOER, TOCR, TGCR, TCDR, and TDDR.

This function enables miswriting due to CPU runaway to be prevented by disabling CPU access to the mode registers, control registers, and counters. When the applicable registers are read in the access-disabled state, undefined values are returned. Writing to these registers is ignored.

2. Halting of PWM output by external signal

The 6-phase PWM output pins can be set automatically to the high-impedance state by inputting specified external signals. There are four external signal input pins.

See section 10, Port Output Enable (POE), for details.

3. Halting of PWM output when oscillator is stopped

If it is detected that the clock input to this LSI has stopped, the 6-phase PWM output pins automatically go to the high-impedance state. The pin states are not guaranteed when the clock is restarted.

See section 4.7, Function for Detecting Oscillator Stop.

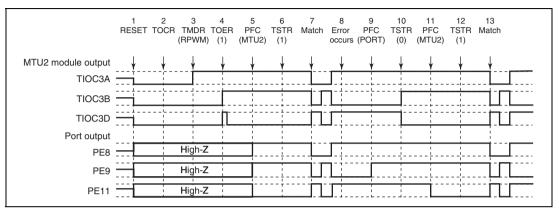

# **Operation when Error Occurs during Reset-Synchronized PWM Mode Operation, and Operation is Restarted in Reset-Synchronized PWM Mode:** Figure 9.152 shows an

explanatory diagram of the case where an error occurs in reset-synchronized PWM mode and operation is restarted in reset-synchronized PWM mode after re-setting.

1 to 10 are the same as in figure 9.149.

- 11. Set MTU2 output with the PFC.

- 12. Operation is restarted by TSTR.

- 13. The reset-synchronized PWM waveform is output on compare-match occurrence.

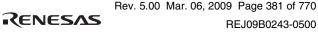

- Four types of interrupts: There are four interrupt sources, transmit-data-empty, transmit end, receive-data-full, and receive error interrupts, and each interrupt can be requested independently.

- Module standby mode can be set

Figure 12.1 shows a block diagram of the SCI.

Figure 12.1 Block Diagram of SCI

RENESAS

## (2) Clock

An internal clock generated by the on-chip baud rate generator or an external clock input from the SCK pin can be selected as the SCI transmit/receive clock. The clock source is selected by the  $C/\overline{A}$  bit in the serial mode register (SCSMR) and bits CKE1 and CKE0 in the serial control register (SCSCR) (table 12.14).

When an external clock is input at the SCK pin, it must have a frequency equal to 16 times the desired bit rate.

When the SCI operates on an internal clock, it can output a clock signal at the SCK pin. The frequency of this output clock is equal to 16 times the desired bit rate.

### (3) Transmitting and Receiving Data

### SCI Initialization (Asynchronous Mode):

Before transmitting or receiving, clear the TE and RE bits to 0 in the serial control register (SCSCR), then initialize the SCI as follows.

When changing the operation mode or the communication format, always clear the TE and RE bits to 0 before following the procedure given below. Clearing the TE bit to 0 sets the TDRE flag to 1 and initializes the transmit shift register (SCTSR). Clearing the RE bit to 0, however, does not initialize the RDRF, PER, FER, and ORER flags or receives data register (SCRDR), which retains their previous contents.

When an external clock is used, the clock should not be stopped during initialization or subsequent operation. SCI operation becomes unreliable if the clock is stopped.

## 14.2.3 Compare Match Counter (CMCNT)

CMCNT is a 16-bit register used as an up-counter. When the counter input clock is selected with bits CKS1 and CKS0 in CMCSR and the STR bit in CMSTR is set to 1, CMCNT starts counting using the selected clock.

When the value in CMCNT and the value in compare match constant register (CMCOR) match, CMCNT is cleared to H'0000 and the CMF flag in CMCSR is set to 1.

| Bit: 15          | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|                  |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Initial value: 0 | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W: R/W         | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

The initial value of CMCNT is H'0000.

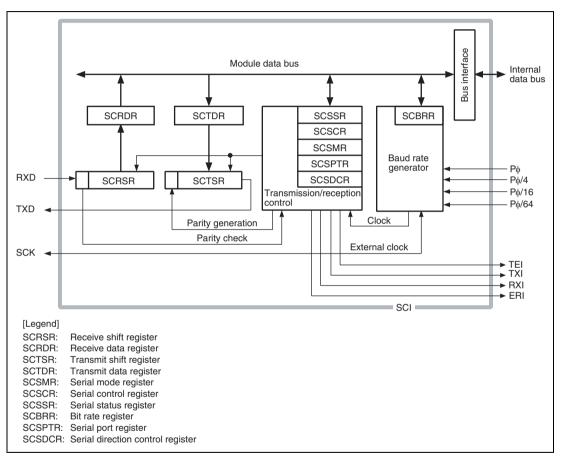

## 14.2.4 Compare Match Constant Register (CMCOR)

CMCOR is a 16-bit register that sets the interval up to a compare match with CMCNT.

The initial value of CMCOR is H'FFFF.

### • PEDRL (SH7124)

| Bit: 15          | 14         | 13         | 12         | 11         | 10         | 9         | 8         | 7 | 6 | 5 | 4 | 3         | 2         | 1         | 0         |

|------------------|------------|------------|------------|------------|------------|-----------|-----------|---|---|---|---|-----------|-----------|-----------|-----------|

| PE15<br>DR       | PE14<br>DR | PE13<br>DR | PE12<br>DR | PE11<br>DR | PE10<br>DR | PE9<br>DR | PE8<br>DR | - | - | - | - | PE3<br>DR | PE2<br>DR | PE1<br>DR | PE0<br>DR |

| Initial value: 0 | 0          | 0          | 0          | 0          | 0          | 0         | 0         | 0 | 0 | 0 | 0 | 0         | 0         | 0         | 0         |

| R/W: R/W         | R/W        | R/W        | R/W        | R/W        | R/W        | R/W       | R/W       | R | R | R | R | R/W       | R/W       | R/W       | R/W       |

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                          |

|--------|----------|------------------|-----|----------------------------------------------------------------------|

| 15     | PE15DR   | 0                | R/W | See table 16.6.                                                      |

| 14     | PE14DR   | 0                | R/W | _                                                                    |

| 13     | PE13DR   | 0                | R/W | —                                                                    |

| 12     | PE12DR   | 0                | R/W | _                                                                    |

| 11     | PE11DR   | 0                | R/W | _                                                                    |

| 10     | PE10DR   | 0                | R/W | _                                                                    |

| 9      | PE9DR    | 0                | R/W | _                                                                    |

| 8      | PE8DR    | 0                | R/W | _                                                                    |

| 7 to 4 | _        | All 0            | R   | Reserved                                                             |

|        |          |                  |     | These bits are always read as 0. The write value should always be 0. |

| 3      | PE3DR    | 0                | R/W | See table 16.6.                                                      |

| 2      | PE2DR    | 0                | R/W | _                                                                    |

| 1      | PE1DR    | 0                | R/W | _                                                                    |

| 0      | PE0DR    | 0                | R/W |                                                                      |

### Table 16.6 Port E Data Register L (PEDRL) Read/Write Operations

• PEDRL Bits 15 to 0

| PEIOR | Pin Function              | Read        | Write                                                 |  |  |  |  |

|-------|---------------------------|-------------|-------------------------------------------------------|--|--|--|--|

| 0     | General input             | Pin state   | Can write to PEDRL, but it has no effect on pin state |  |  |  |  |

|       | Other than general input  | Pin state   | Can write to PEDRL, but it has no effect on pin state |  |  |  |  |

| 1     | General output            | PEDRL value | Value written is output from pin                      |  |  |  |  |

| _     | Other than general output | PEDRL value | Can write to PEDRL, but it has no effect on pin state |  |  |  |  |

128-byte programming is performed in one program processing. When more than 128-byte programming is performed, programming destination address/program data parameter is updated in 128-byte units and programming is repeated.

When less than 128-byte programming is performed, data must total 128 bytes by adding the invalid data. If the invalid data to be added is H'FF, the program processing period can be shortened.

(2.1) Select the on-chip program to be downloaded

When the PPVS bit of FPCS is set to 1, the programming program is selected. Several programming/erasing programs cannot be selected at one time. If several programs are set, download is not performed and a download error is returned to the source select error detect (SS) bit in the DPFR parameter.

Specify the start address of the download destination by FTDAR.

(2.2) Write H'A5 in FKEY

If H'A5 is not written to FKEY for protection, 1 cannot be written to the SCO bit for a download request.

(2.3) VBR is set to 0 and 1 is written to the SCO bit of FCCS, and then download is executed.

VBR must always be set to H'84000000 before setting the SCO bit to 1.

To write 1 to the SCO bit, the following conditions must be satisfied.

- H'A5 is written to FKEY.

- The SCO bit writing is executed in the on-chip RAM.

When the SCO bit is set to 1, download is started automatically. When execution returns to the user procedure program, the SCO bit is cleared to 0. Therefore, the SCO bit cannot be confirmed to be 1 in the user procedure program.

The download result can be confirmed only by the return value of the DPFR parameter. Before the SCO bit is set to 1, incorrect decision must be prevented by setting the DPFR parameter, that is one byte of the start address of the on-chip RAM area specified by FTDAR, to a value other than the return value (H'FF).

When download is executed, particular interrupt processing, which is accompanied by the bank switch as described below, is performed as an internal microcomputer processing, so VBR need to be set to H'84000000. Four NOP instructions are executed immediately after the instructions that set the SCO bit to 1.

- The user MAT space is switched to the on-chip program storage area.

- After the selection condition of the download program and the address set in FTDAR are checked, the transfer processing is executed starting to the on-chip RAM address specified by FTDAR.

- The SCO bits in FCCS, FPCS, and FECS are cleared to 0.

- The return value is set to the DPFR parameter.

| Error    |      |       |

|----------|------|-------|

| response | H'D8 | ERROR |

- Error response H'D8 (1 byte): Error response to the block erasure command

- ERROR (1 byte): Error code

- H'11: Sum-check error

- H'29: Block number error (the specified block number is incorrect.)

- H'51: Erasure error (an error occurred during erasure.)

On receiving the command with H'FF as the block number, the boot program stops erasure processing and waits for the next programming/erasure selection command.

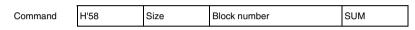

- Command H'58 (1 byte): Erasure of a block

- Size (1 byte): The number of characters in the block number field (fixed at 1)

- Block number (1 byte): H'FF (erasure terminating code)

- SUM (1 byte): Checksum

H'06

Response

Response H'06 (1 byte): ACK code to indicate response to the request for termination of erasure

To perform erasure again after having issued the command with the block number specified as H'FF, execute the process from the selection of erasure.

Memory read

In response to the memory read command, the boot program returns the data from the specified address.

| Command | H'52           | Size | Area | First address for reading |     |  |

|---------|----------------|------|------|---------------------------|-----|--|

|         | Amount to read |      |      |                           | SUM |  |

- Command H'52 (1 byte): Memory read

- Size (1 byte): The total length of the area, address for reading, and amount to read fields (fixed value of 9)

RENESAS

| Register<br>Abbreviation | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 | Module          |

|--------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|-----------------|

| TIORV_5                  |                   |                   |                   |                   |                   | MTU2              |                  |                  |                 |

| TCNTW_5                  |                   |                   |                   |                   |                   | 100[4.0]          |                  |                  | 11102           |

| TONTW_5                  |                   |                   |                   |                   |                   |                   |                  |                  |                 |

| TGRW_5                   |                   |                   |                   |                   |                   |                   |                  |                  |                 |

|                          |                   |                   |                   |                   |                   |                   |                  |                  |                 |

| TCRW_5                   |                   |                   |                   |                   |                   |                   | TPS              |                  |                 |

| TIORW_5                  | _                 | _                 | _                 |                   | I                 | IOC[4:0]          |                  |                  |                 |

| TSR_5                    | _                 |                   |                   | _                 |                   | CMFU5             | CMFV5            | CMFW5            |                 |

| TIER_5                   | _                 |                   |                   | _                 |                   | TGIE5U            | TGIE5V           | TGIE5W           |                 |

| TSTR_5                   | _                 | _                 | _                 | _                 | _                 | CSTU5             | CSTV5            | CSTW5            |                 |

| TCNTCMPCLR               | _                 | _                 | _                 | _                 | _                 | CMPCLR5U          | CMPCLR5V         | CMPCLR5W         |                 |

| ADDR0                    | AD9               | AD8               | AD7               | AD6               | AD5               | AD4               | AD3              | AD2              | A/D (Channel 0) |

|                          | AD1               | AD0               |                   | _                 | _                 | _                 | _                | _                |                 |

| ADDR1                    | AD9               | AD8               | AD7               | AD6               | AD5               | AD4               | AD3              | AD2              |                 |

|                          | AD1               | AD0               | _                 | —                 | _                 | _                 |                  | _                |                 |

| ADDR2                    | AD9               | AD8               | AD7               | AD6               | AD5               | AD4               | AD3              | AD2              |                 |

|                          | AD1               | AD0               |                   | —                 | _                 | —                 | _                | —                |                 |

| ADDR3                    | AD9               | AD8               | AD7               | AD6               | AD5               | AD4               | AD3              | AD2              |                 |

|                          | AD1               | AD0               |                   | —                 |                   | —                 | _                | —                |                 |

| ADCSR_0                  | ADF               | ADIE              | —                 | —                 | TRGE              | —                 | CONADF           | STC              |                 |

|                          | CKS               | L[1:0]            | ADN               | 1[1:0]            | ADCS              | CH[2:0]           |                  |                  |                 |

| ADCR_0                   | —                 | —                 | ADST              | —                 | —                 | —                 | —                | —                |                 |

|                          | —                 | —                 | —                 | —                 | —                 | —                 | _                | —                |                 |

| ADDR4                    | AD9               | AD8               | AD7               | AD6               | AD5               | AD4               | AD3              | AD2              | A/D (Channel 1) |

|                          | AD1               | AD0               | —                 | —                 | —                 | —                 | _                | —                |                 |

| ADDR5                    | AD9               | AD8               | AD7               | AD6               | AD5               | AD4               | AD3              | AD2              |                 |

|                          | AD1               | AD0               | —                 | —                 | —                 | —                 | _                | —                |                 |

| ADDR6                    | AD9               | AD8               | AD7               | AD6               | AD5               | AD4               | AD3              | AD2              |                 |

|                          | AD1               | AD0               | _                 | _                 | _                 | —                 | _                | —                |                 |

| ADDR7                    | AD9               | AD8               | AD7               | AD6               | AD5               | AD4               | AD3              | AD2              |                 |

|                          | AD1               | AD0               | —                 | —                 | —                 | —                 | _                | —                |                 |

| Register     | Bit         |                 |  |

|--------------|------------|------------|------------|------------|------------|------------|------------|-------------|-----------------|--|

| Abbreviation | 31/23/15/7 | 30/22/14/6 | 29/21/13/5 | 28/20/12/4 | 27/19/11/3 | 26/18/10/2 | 25/17/9/1  | 24/16/8/0   | Module          |  |

| ADCSR_1      | ADF        | ADIE       | _          | _          | TRGE       | _          | CONADF     | STC         | A/D (Channel 1) |  |

|              | CKSL[1:0]  |            | ADM[1:0]   |            | ADCS       | CH[2:0]    |            |             |                 |  |

| ADCR_1       | —          | _          | ADST       | _          | _          | _          | _          | —           |                 |  |

|              | —          | _          | _          | _          | _          | _          | _          | —           |                 |  |

| FCCS         | FWE        | —          | —          | FLER       | —          | _          | —          | SCO         | FLASH           |  |

| FPCS         | —          | _          | _          | _          | _          | _          | _          | PPVS        |                 |  |

| FECS         | —          | _          | _          | _          | _          | _          | —          | EPVB        |                 |  |

| FKEY         |            |            |            | K          | 7:0]       |            |            |             |                 |  |

| FTDAR        | TDER       |            |            |            | TDA[6:0]   |            |            |             |                 |  |

| CMSTR        | —          | —          | —          | —          | —          | —          | —          | —           | СМТ             |  |

|              | —          | _          | _          | _          | _          | _          | STR1       | STR0        |                 |  |

| CMCSR_0      | —          | _          | _          | _          | _          | _          | _          | —           |                 |  |

|              | CMF        | CMIE       | _          | _          | _          | _          | CKS[1:0]   |             | 1               |  |

| CMCNT_0      |            |            |            |            |            |            |            |             |                 |  |

|              |            |            |            |            |            |            |            |             |                 |  |

| CMCOR_0      |            |            |            |            |            |            |            |             |                 |  |

|              |            |            |            |            |            |            |            |             |                 |  |

| CMCSR_1      | —          | _          | _          | _          | _          | _          | _          | —           |                 |  |

|              | CMF        | CMIE       | _          | _          | _          | _          | CKS[1:0]   |             |                 |  |

| CMCNT_1      |            |            |            |            |            |            |            |             |                 |  |

|              |            |            |            |            |            |            |            |             |                 |  |

| CMCOR_1      |            |            |            |            |            |            |            |             |                 |  |

|              |            |            |            |            |            |            |            |             |                 |  |

| ICSR1        | POE3F      | _          | POE1F      | POE0F      | _          | _          | _          | PIE1        | POE             |  |

|              | POE3M[1:0] |            | _          | _          | POE1       | POE1M[1:0] |            | POE0M[1:0]  |                 |  |

| OCSR1        | OSF1       | _          | _          | _          | _          | _          | OCE1       | OIE1        |                 |  |

|              | _          | _          | _          | _          | _          | _          | _          | _           |                 |  |

| ICSR3        | _          | _          | _          | POE8F      | _          | _          | POE8E      | PIE3        |                 |  |

|              | _          | _          | _          | _          | _          | _          | POE        | 3M[1:0]     | 1               |  |

| SPOER        | —          | _          | _          | _          | —          | _          | MTU2CH0HIZ | MTU2CH34HIZ |                 |  |

Appendix