Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | SH-2                                                                              |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 50MHz                                                                             |

| Connectivity               | SCI                                                                               |

| Peripherals                | POR, PWM, WDT                                                                     |

| Number of I/O              | 23                                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                         |

| Data Converters            | A/D 8x10b                                                                         |

| Oscillator Type            | External                                                                          |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 48-LQFP                                                                           |

| Supplier Device Package    | 48-LQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df71242n50fpv-z1 |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The clock pulse generator blocks function as follows:

**PLL Circuit:** The PLL circuit multiples the clock frequency input from the crystal oscillator or the EXTAL pin by 8. The multiplication ratio is fixed at  $\times$ 8.

**Crystal Oscillator:** The crystal oscillator is an oscillator circuit when a crystal resonator is connected to the XTAL and EXTAL pins.

**Divider:** The divider generates clocks with the frequencies to be used by the internal clock  $(I\phi)$ , bus clock  $(B\phi)$ , peripheral clock  $(P\phi)$ , and MTU2 clock  $(MP\phi)$ .

The frequencies can be selected from 1/2, 1/4 (initial value), and 1/8 times the frequency output from the PLL circuit. The division ratio should be specified in the frequency control register (FRQCR).

**Oscillation Stop Detection Circuit:** This circuit detects an abnormal condition in the crystal oscillator.

**Clock Frequency Control Circuit:** The clock frequency control circuit controls the clock frequency according to the setting in the frequency control register (FRQCR).

**Standby Control Circuit:** The standby control circuit controls the state of the on-chip oscillator circuit and other modules in sleep or standby mode.

**Frequency Control Register (FRQCR):** The frequency control register (FRQCR) has control bits for the frequency division ratios of the internal clock ( $I\phi$ ), bus clock ( $B\phi$ ), peripheral clock ( $P\phi$ ), and MTU2 clock ( $MP\phi$ ).

**Oscillation Stop Detection Control Register (OSCCR):** The oscillation stop detection control register (OSCCR) has an oscillation stop detection flag and a bit for selecting flag status output through an external pin.

**Standby Control Registers 1 to 6 (STBCR1 to STBCR6):** The standby control register (STBCR) has bits for controlling the power-down modes. For details, see section 19, Power-Down Modes.

# 4.7 Function for Detecting Oscillator Stop

This CPG detects a stop in the clock input if any system abnormality halts the clock supply.

When no change has been detected in the EXTAL input for a certain period, the OSCSTOP bit in OSCCR is set to 1 and this state is retained until a power-on reset is input through the  $\overline{\text{RES}}$  pin or software standby mode is canceled. If the OSCERS bit is set to 1 at this time, an oscillation stop detection flag signal is output through the  $\overline{\text{WDTOVF}}$  pin. In addition, the high-current ports (pins to which the TIOC3B, TIOC3D, and TIOC4A to TIOC4D signals in the MTU2 are assigned) are always placed in high-impedance state regardless of the PFC setting. For details, refer to appendix A, Pin States.

Even in software standby mode, these pins are always placed in high-impedance state. For details, refer to appendix A, Pin States. These pins enter the normal state after software standby mode is canceled. Under an abnormal condition where oscillation stops while the LSI is not in software standby mode, LSI operations other than the oscillation stop detection function become unpredictable. In this case, even after oscillation is restarted, LSI operations including the above high-current pins become unpredictable.

Even while no change is detected in the EXTAL input, the PLL circuit in this LSI continues oscillating at a frequency range from 100 kHz to 10 MHz (depending on the temperature and operating voltage).

| Exception   | Handling Source  | Vector Number | Vector Table Address Offset |  |  |  |  |  |

|-------------|------------------|---------------|-----------------------------|--|--|--|--|--|

| Interrupt   | IRQ0 (SH7125)    | 64            | H'00000100 to H'00000103    |  |  |  |  |  |

|             | IRQ1             | 65            | H'00000104 to H'00000107    |  |  |  |  |  |

|             | IRQ2             | 66            | H'00000108 to H'0000010B    |  |  |  |  |  |

|             | IRQ3             | 67            | H'0000010C to H'0000010F    |  |  |  |  |  |

| (Reserved f | or system use)   | 68            | H'00000110 to H'00000113    |  |  |  |  |  |

|             |                  | :             | :                           |  |  |  |  |  |

|             |                  | 71            | H'0000011C to H'0000011F    |  |  |  |  |  |

| On-chip per | ipheral module*2 | 72            | H'00000120 to H'00000123    |  |  |  |  |  |

|             |                  | :             | :                           |  |  |  |  |  |

|             |                  | 255           | H'000003FC to H'000003FF    |  |  |  |  |  |

Notes: 1. Reserved on the 32 Kbyte (SH71251A and SH71241A) and 16 Kbyte (SH71250A and SH71240A) versions.

2. For details on the vector numbers and vector table address offsets of on-chip peripheral module interrupts, see table 6.3 in section 6, Interrupt Controller (INTC).

#### Table 5.4 Calculating Exception Handling Vector Table Addresses

| Vector Table Address Calculation                           |  |  |  |  |  |  |  |

|------------------------------------------------------------|--|--|--|--|--|--|--|

| Vector table address = (vector table address offset)       |  |  |  |  |  |  |  |

| = (vector number) × 4                                      |  |  |  |  |  |  |  |

| Vector table address = VBR + (vector table address offset) |  |  |  |  |  |  |  |

| = VBR + (vector number) $\times$ 4                         |  |  |  |  |  |  |  |

|                                                            |  |  |  |  |  |  |  |

Notes: 1. VBR: Vector base register

2. Vector table address offset: See table 5.3.

3. Vector number: See table 5.3.

## 6.3.1 Interrupt Control Register 0 (ICR0)

ICR0 is a 16-bit register that sets the input signal detection mode of the external interrupt input pin NMI and indicates the input signal level on the NMI pin.

| Bit: 15          | 14 | 13 | 12 | 11 | 10 | 9 | 8    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------------|----|----|----|----|----|---|------|---|---|---|---|---|---|---|---|

| NMI              |    | -  | -  | -  | -  | - | NMIE | - | - | - | - | - | - | - | - |

| Initial value: * | 0  | 0  | 0  | 0  | 0  | 0 | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| R/W: R           | R  | R  | R  | R  | R  | R | R/W  | R | R | R | R | R | R | R | R |

Note: \* The initial value is 1 when the level on the NMI pin is high, and 0 when the level on the pin is low.

|         |          | Initial |     |                                                                                                                                                 |

|---------|----------|---------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit     | Bit Name | Value   | R/W | Description                                                                                                                                     |

| 15      | NMIL     | *       | R   | NMI Input Level                                                                                                                                 |

|         |          |         |     | Indicates the state of the signal input to the NMI pin.<br>This bit can be read to determine the NMI pin level. This<br>bit cannot be modified. |

|         |          |         |     | 0: State of the NMI input is low                                                                                                                |

|         |          |         |     | 1: State of the NMI input is high                                                                                                               |

| 14 to 9 | _        | All 0   | R   | Reserved                                                                                                                                        |

|         |          |         |     | These bits are always read as 0. The write value should always be 0.                                                                            |

| 8       | NMIE     | 0       | R/W | NMI Edge Select                                                                                                                                 |

|         |          |         |     | 0: Interrupt request is detected on the falling edge of the<br>NMI input                                                                        |

|         |          |         |     | 1: Interrupt request is detected on the rising edge of the<br>NMI input                                                                         |

| 7 to 0  | _        | All 0   | R   | Reserved                                                                                                                                        |

|         |          |         |     | These bits are always read as 0. The write value should always be 0.                                                                            |

|         |          |         |     |                                                                                                                                                 |

- Notes: The interrupt source flag should be cleared in the interrupt handler. To ensure that an interrupt source that should have been cleared is not inadvertently accepted again, read the interrupt source flag after it has been cleared, confirm that it has been cleared, and then execute an RTE instruction.

- \* Interrupt requests that are designated as edge-detect type are held pending until the interrupt requests are accepted. IRQ interrupts, however, can be cancelled by accessing the IRQ status register (IRQSR). Interrupts held pending due to edge detection are cleared by a power-on reset or a manual reset.

|               |               |               |               | Description           |                                |  |  |  |  |  |  |  |  |

|---------------|---------------|---------------|---------------|-----------------------|--------------------------------|--|--|--|--|--|--|--|--|

| Bit 3<br>IOA3 | Bit 2<br>IOA2 | Bit 1<br>IOA1 | Bit 0<br>IOA0 | TGRA_3<br>Function    | TIOC3A Pin Function            |  |  |  |  |  |  |  |  |

| 0             | 0             | 0             | 0             | Output                | Output retained*               |  |  |  |  |  |  |  |  |

|               |               |               | 1             | compare<br>register   | Initial output is 0            |  |  |  |  |  |  |  |  |

|               |               |               |               | Tegister              | 0 output at compare match      |  |  |  |  |  |  |  |  |

|               |               | 1             | 0             | _                     | Initial output is 0            |  |  |  |  |  |  |  |  |

|               |               |               |               |                       | 1 output at compare match      |  |  |  |  |  |  |  |  |

|               |               |               | 1             | _                     | Initial output is 0            |  |  |  |  |  |  |  |  |

|               |               |               |               |                       | Toggle output at compare match |  |  |  |  |  |  |  |  |

|               | 1             | 0             | 0             | _                     | Output retained                |  |  |  |  |  |  |  |  |

|               |               |               | 1             | _                     | Initial output is 1            |  |  |  |  |  |  |  |  |

|               |               |               |               |                       | 0 output at compare match      |  |  |  |  |  |  |  |  |

|               |               | 1             | 0             | _                     | Initial output is 1            |  |  |  |  |  |  |  |  |

|               |               |               |               |                       | 1 output at compare match      |  |  |  |  |  |  |  |  |

|               |               |               | 1             | _                     | Initial output is 1            |  |  |  |  |  |  |  |  |

|               |               |               |               |                       | Toggle output at compare match |  |  |  |  |  |  |  |  |

| 1             | х             | 0             | 0             |                       | Input capture at rising edge   |  |  |  |  |  |  |  |  |

|               |               |               | 1             | <sup>–</sup> register | Input capture at falling edge  |  |  |  |  |  |  |  |  |

|               |               | 1             | х             | _                     | Input capture at both edges    |  |  |  |  |  |  |  |  |

| [Legend       | 4]            |               |               |                       |                                |  |  |  |  |  |  |  |  |

## Table 9.24 TIORH\_3 (Channel 3)

[Legend]

x: Don't care

Note: \* After power-on reset, 0 is output until TIOR is set.

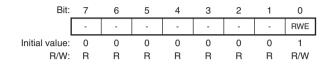

# 9.3.16 Timer Read/Write Enable Register (TRWER)

TRWER is an 8-bit readable/writable register that enables or disables access to the registers and counters which have write-protection capability against accidental modification in channels 3 and 4.

|        |          | Initial |     |                                                                                                                     |

|--------|----------|---------|-----|---------------------------------------------------------------------------------------------------------------------|

| Bit    | Bit Name | Value   | R/W | Description                                                                                                         |

| 7 to 1 | _        | All 0   | R   | Reserved                                                                                                            |

|        |          |         |     | These bits are always read as 0. The write value should always be 0.                                                |

| 0      | RWE      | 1       | R/W | Read/Write Enable                                                                                                   |

|        |          |         |     | Enables or disables access to the registers which have write-protection capability against accidental modification. |

|        |          |         |     | 0: Disables read/write access to the registers                                                                      |

|        |          |         |     | 1: Enables read/write access to the registers                                                                       |

|        |          |         |     | [Clearing condition]                                                                                                |

| _      |          |         |     | <ul> <li>When 0 is written to the RWE bit after reading<br/>RWE = 1</li> </ul>                                      |

• Registers and counters having write-protection capability against accidental modification 22 registers: TCR\_3, TCR\_4, TMDR\_3, TMDR\_4, TIORH\_3, TIORH\_4, TIORL\_3, TIORL\_4, TIER\_3, TIER\_4, TGRA\_3, TGRA\_4, TGRB\_3, TGRB\_4, TOER, TOCR1, TOCR2, TGCR, TCDR, TDDR, TCNT\_3, and TCNT\_4.

| Bit | Bit Name | Initial<br>Value | R/W   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|----------|------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | WRE      | 0                | R/(W) | Waveform Retain Enable                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |          |                  |       | Selects the waveform output when synchronous counter clearing occurs in complementary PWM mode.                                                                                                                                                                                                                                                                                                                                                                |

|     |          |                  |       | The output waveform is retained only when<br>synchronous clearing occurs within the Tb interval at<br>the trough in complementary PWM mode. When<br>synchronous clearing occurs outside this interval, the<br>initial value specified in TOCR is output regardless of<br>the WRE bit setting. The initial value is also output<br>when synchronous clearing occurs in the Tb interval at<br>the trough immediately after TCNT_3 and TCNT_4 start<br>operation. |

|     |          |                  |       | For the Tb interval at the trough in complementary PWM mode, see figure 9.40.                                                                                                                                                                                                                                                                                                                                                                                  |

|     |          |                  |       | 0: Outputs the initial value specified in TOCR                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |          |                  |       | 1: Retains the waveform output immediately before<br>synchronous clearing                                                                                                                                                                                                                                                                                                                                                                                      |

|     |          |                  |       | [Setting condition]                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |          |                  |       | • When 1 is written to WRE after reading WRE = 0                                                                                                                                                                                                                                                                                                                                                                                                               |

Note: \* Do not set to 1 when complementary PWM mode is not selected.

## 9.3.31 Bus Master Interface

The timer counters (TCNT), general registers (TGR), timer subcounter (TCNTS), timer cycle buffer register (TCBR), timer dead time data register (TDDR), timer cycle data register (TCDR), timer A/D converter start request control register (TADCR), timer A/D converter start request cycle set registers (TADCOR), and timer A/D converter start request cycle set buffer registers (TADCOR) are 16-bit registers. A 16-bit data bus to the bus master enables 16-bit read/writes. 8-bit read/write is not possible. Always access in 16-bit units.

All registers other than the above registers are 8-bit registers. These are connected to the CPU by a 16-bit data bus, so 16-bit read/writes and 8-bit read/writes are both possible.

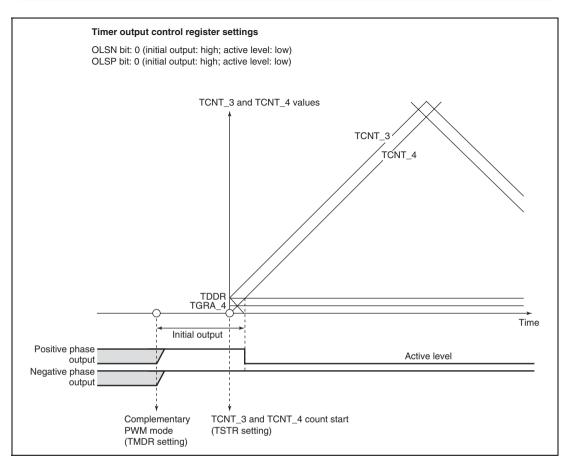

Figure 9.45 Example of Initial Output in Complementary PWM Mode (2)

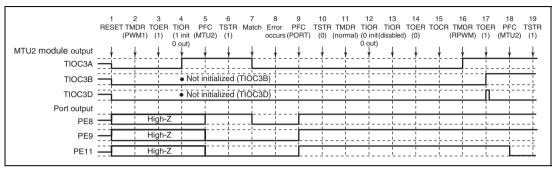

**Operation when Error Occurs during PWM Mode 1 Operation, and Operation is Restarted in Reset-Synchronized PWM Mode:** Figure 9.135 shows an explanatory diagram of the case where an error occurs in PWM mode 1 and operation is restarted in reset-synchronized PWM mode after re-setting.

# Figure 9.135 Error Occurrence in PWM Mode 1, Recovery in Reset-Synchronized PWM Mode

- 1 to 14 are the same as in figure 9.134.

- 15. Select the reset-synchronized PWM output level and cyclic output enabling/disabling with TOCR.

- 16. Set reset-synchronized PWM.

- 17. Enable channel 3 and 4 output with TOER.

- 18. Set MTU2 output with the PFC.

- 19. Operation is restarted by TSTR.

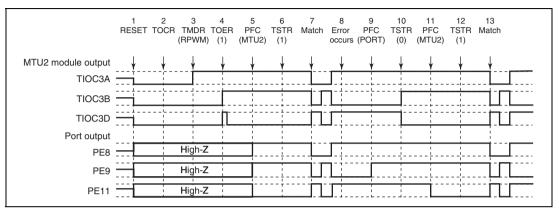

# **Operation when Error Occurs during Reset-Synchronized PWM Mode Operation, and Operation is Restarted in Reset-Synchronized PWM Mode:** Figure 9.152 shows an

explanatory diagram of the case where an error occurs in reset-synchronized PWM mode and operation is restarted in reset-synchronized PWM mode after re-setting.

1 to 10 are the same as in figure 9.149.

- 11. Set MTU2 output with the PFC.

- 12. Operation is restarted by TSTR.

- 13. The reset-synchronized PWM waveform is output on compare-match occurrence.

| Bit      | Bit Name | Initial<br>value | R/W               | Description                                                                                                      |

|----------|----------|------------------|-------------------|------------------------------------------------------------------------------------------------------------------|

| 14 to 10 | )        | All 0            | R                 | Reserved                                                                                                         |

|          |          |                  |                   | These bits are always read as 0. The write value should always be 0.                                             |

| 9        | OCE1     | 0                | R/W* <sup>2</sup> | Output Short High-Impedance Enable 1                                                                             |

|          |          |                  |                   | This bit specifies whether to place the pins in high-<br>impedance state when the OSF1 bit in OCSR1 is set to 1. |

|          |          |                  |                   | 0: Does not place the pins in high-impedance state                                                               |

|          |          |                  |                   | 1: Places the pins in high-impedance state                                                                       |

| 8        | OIE1     | 0                | R/W               | Output Short Interrupt Enable 1                                                                                  |

|          |          |                  |                   | This bit enables or disables interrupt requests when the OSF1 bit in OCSR is set to 1.                           |

|          |          |                  |                   | 0: Interrupt requests disabled                                                                                   |

|          |          |                  |                   | 1: Interrupt requests enabled                                                                                    |

| 7 to 0   |          | All 0            | R                 | Reserved                                                                                                         |

|          |          |                  |                   | These bits are always read as 0. The write value should always be 0.                                             |

Notes: 1. Writing 0 to this bit after reading it as 1 clears the flag and is the only allowed way.2. Can be modified only once after a power-on reset.

### 10.3.3 Input Level Control/Status Register 3 (ICSR3)

ICSR3 is a 16-bit readable/writable register that selects the  $\overline{POE8}$  pin input mode, controls the enable/disable of interrupts, and indicates status.

| Bit:           | 15 | 14 | 13 | 12      | 11 | 10 | 9     | 8    | 7 | 6 | 5 | 4 | 3 | 2 | 1          | 0     |

|----------------|----|----|----|---------|----|----|-------|------|---|---|---|---|---|---|------------|-------|

|                | -  | -  | -  | POE8F   | -  | -  | POE8E | PIE3 | - | - | - | - | - | - | POE8M[1:0] |       |

| Initial value: | 0  | 0  | 0  | 0       | 0  | 0  | 0     | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0          | 0     |

| R/W:           | R  | R  | R  | R/(W)*1 | R  | R  | R/W*2 | R/W  | R | R | R | R | R | R | R/W*2      | R/W*2 |

RENESAS

Notes: 1. Writing 0 to this bit after reading it as 1 clears the flag and is the only allowed way.

2. Can be modified only once after a power-on reset.

|        |          | Initial |     |                                                                      |

|--------|----------|---------|-----|----------------------------------------------------------------------|

| Bit    | Bit Name | Value   | R/W | Description                                                          |

| 10     | PB2MD2   | 0       | R/W | PB2 Mode                                                             |

| 9      | PB2MD1   | 0       | R/W | Select the function of the PB2/IRQ0/POE0 pin.                        |

| 8      | PB2MD0   | 0       | R/W | 000: PB2 I/O (port)                                                  |

|        |          |         |     | 001: IRQ0 input (INTC)                                               |

|        |          |         |     | 010: POE0 input (POE)                                                |

|        |          |         |     | Other than above: Setting prohibited                                 |

| 7      |          | 0       | R   | Reserved                                                             |

|        |          |         |     | This bit is always read as 0. The write value should always be 0.    |

| 6      | PB1MD2   | 0       | R/W | PB1 Mode                                                             |

| 5      | PB1MD1   | 0       | R/W | Select the function of the PB1/TIC5W pin.                            |

| 4      | PB1MD0   | 0       | R/W | 000: PB1 I/O (port)                                                  |

|        |          |         |     | 011: TIC5W input (MTU2)                                              |

|        |          |         |     | Other than above: Setting prohibited                                 |

| 3 to 0 |          | All 0   | R   | Reserved                                                             |

|        |          |         |     | These bits are always read as 0. The write value should always be 0. |

## SH7124:

## • Port B Control Register H1 (PBCRH1)

| Bit:           | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|                | -  | -  | -  | -  | -  | -  | - | - | - | - | - | - | - | - | - | - |

| Initial value: | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| R/W:           | R  | R  | R  | R  | R  | R  | R | R | R | R | R | R | R | R | R | R |

| Bit     | Bit Name | Initial<br>Value | R/W | Description                                                          |

|---------|----------|------------------|-----|----------------------------------------------------------------------|

| 15 to 0 | _        | All 0            | R   | Reserved                                                             |

|         |          |                  |     | These bits are always read as 0. The write value should always be 0. |

## • Port E Control Register L1 (PECRL1)

| Bit:           | 15 | 14         | 13         | 12         | 11 | 10         | 9          | 8          | 7 | 6          | 5          | 4          | 3 | 2 | 1          | 0          |

|----------------|----|------------|------------|------------|----|------------|------------|------------|---|------------|------------|------------|---|---|------------|------------|

|                | -  | PE3<br>MD2 | PE3<br>MD1 | PE3<br>MD0 | -  | PE2<br>MD2 | PE2<br>MD1 | PE2<br>MD0 | - | PE1<br>MD2 | PE1<br>MD1 | PE1<br>MD0 | - | - | PE0<br>MD1 | PE0<br>MD0 |

| Initial value: | 0  | 0          | 0          | 0          | 0  | 0          | 0          | 0          | 0 | 0          | 0          | 0          | 0 | 0 | 0          | 0          |

| R/W:           | R  | R/W        | R/W        | R/W        | R  | R/W        | R/W        | R/W        | R | R/W        | R/W        | R/W        | R | R | R/W        | R/W        |

| <b>D</b> |          | Initial | <b>B</b> 444 |                                                                   |

|----------|----------|---------|--------------|-------------------------------------------------------------------|

| Bit      | Bit Name | Value   | R/W          | Description                                                       |

| 15       | —        | 0       | R            | Reserved                                                          |

|          |          |         |              | This bit is always read as 0. The write value should always be 0. |

| 14       | PE3MD2   | 0       | R/W          | PE3 Mode                                                          |

| 13       | PE3MD1   | 0       | R/W          | Select the function of the PE3/TIOC0D/SCK0 pin.                   |

| 12       | PE3MD0   | 0       | R/W          | 000: PE3 I/O (port)                                               |

|          |          |         |              | 001: TIOC0D I/O (MTU2)                                            |

|          |          |         |              | 110: SCK0 I/O (SCI)                                               |

|          |          |         |              | Other than above: Setting prohibited                              |

| 11       | —        | 0       | R            | Reserved                                                          |

|          |          |         |              | This bit is always read as 0. The write value should always be 0. |

| 10       | PE2MD2   | 0       | R/W          | PE2 Mode                                                          |

| 9        | PE2MD1   | 0       | R/W          | Select the function of the PE2/TIOC0C/TXD0 pin.                   |

| 8        | PE2MD0   | 0       | R/W          | 000: PE2 I/O (port)                                               |

|          |          |         |              | 001: TIOC0C I/O (MTU2)                                            |

|          |          |         |              | 110: TXD0 output (SCI)                                            |

|          |          |         |              | Other than above: Setting prohibited                              |

| 7        | _        | 0       | R            | Reserved                                                          |

|          |          |         |              | This bit is always read as 0. The write value should always be 0. |

| 6        | PE1MD2   | 0       | R/W          | PE1 Mode                                                          |

| 5        | PE1MD1   | 0       | R/W          | Select the function of the PE1/TIOC0B/RXD0 pin.                   |

| 4        | PE1MD0   | 0       | R/W          | 000: PE1 I/O (port)                                               |

|          |          |         |              | 001: TIOC0B I/O (MTU2)                                            |

|          |          |         |              | 110: RXD0 input (SCI)                                             |

|          |          |         |              | Other than above: Setting prohibited                              |

| • PAPRL (SH7124) |

|------------------|

|------------------|

| Bit:           | 15 | 14 | 13 | 12 | 11 | 10 | 9         | 8         | 7         | 6         | 5 | 4         | 3         | 2 | 1         | 0         |

|----------------|----|----|----|----|----|----|-----------|-----------|-----------|-----------|---|-----------|-----------|---|-----------|-----------|

| [              | -  | -  | -  | -  | -  | -  | PA9<br>PR | PA8<br>PR | PA7<br>PR | PA6<br>PR | - | PA4<br>PR | PA3<br>PR | - | PA1<br>PR | PA0<br>PR |

| Initial value: | 0  | 0  | 0  | 0  | 0  | 0  | *         | *         | *         | *         | 0 | *         | *         | 0 | *         | *         |

| R/W:           | R  | R  | R  | R  | R  | R  | R         | R         | R         | R         | R | R         | R         | R | R         | R         |

|          |          | Initial   |     |                                                                                            |

|----------|----------|-----------|-----|--------------------------------------------------------------------------------------------|

| Bit      | Bit Name | Value     | R/W | Description                                                                                |

| 15 to 10 | _        | All 0     | R   | Reserved                                                                                   |

|          |          |           |     | These bits are always read as 0. The write value should always be 0.                       |

| 9        | PA9PR    | Pin state | R   | The pin state is returned regardless of the PFC setting.                                   |

| 8        | PA8PR    | Pin state | R   | These bits cannot be modified.                                                             |

| 7        | PA7PR    | Pin state | R   | -                                                                                          |

| 6        | PA6PR    | Pin state | R   | -                                                                                          |

| 5        | _        | 0         | R   | Reserved                                                                                   |

|          |          |           |     | This bit is always read as 0. The write value should always be 0.                          |

| 4        | PA4PR    | Pin state | R   | The pin state is returned regardless of the PFC setting.                                   |

| 3        | PA3PR    | Pin state | R   | These bits cannot be modified.                                                             |

| 2        | _        | 0         | R   | Reserved                                                                                   |

|          |          |           |     | This bit is always read as 0. The write value should always be 0.                          |

| 1        | PA1PR    | Pin state | R   | The pin state is returned regardless of the PFC setting.<br>These bits cannot be modified. |

| 0        | PA0PR    | Pin state | R   | -                                                                                          |

(5) Flash Transfer Destination Address Register (FTDAR)

FTDAR specifies the on-chip RAM address to which the on-chip program is downloaded. Make settings for FTDAR before writing 1 to the SCO bit in FCCS. The initial value is H'00.

| Bit:           | 7    | 6   | 5   | 4   | 3        | 2   | 1   | 0   |

|----------------|------|-----|-----|-----|----------|-----|-----|-----|

|                | TDER |     |     |     | TDA[6:0] |     |     |     |

| Initial value: | 0    | 0   | 0   | 0   | 0        | 0   | 0   | 0   |

| R/W:           | R/W  | R/W | R/W | R/W | R/W      | R/W | R/W | R/W |

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|----------|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TDER     | 0                | R/W | Transfer Destination Address Setting Error                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |          |                  |     | This bit is set to 1 when there is an error in the<br>download start address set by bits 6 to 0 (TDA6 to<br>TDA0). Whether the address setting is erroneous or not<br>is tested by checking whether the setting of TDA6 to<br>TDA0 is between the range of H'02 to H'04 after setting<br>the SCO bit in FCCS to 1 and performing download.<br>Before setting the SCO bit to 1 be sure to set the<br>FTDAR value between H'02 to H'04 as well as clearing<br>this bit to 0. |

|     |          |                  |     | 0: Setting of TDA6 to TDA0 is normal                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |          |                  |     | 1: Setting of TDER and TDA6 to TDA0 is H'00 to H'01<br>and H'05 to H'FF and download has been aborted                                                                                                                                                                                                                                                                                                                                                                      |

All commands in the above table, except for the boot program state inquiry command (H'4F), are valid until the boot program accepts the transition-to-programming/erasure state command (H'40). That is, until the transition command is accepted, the host can continue to send commands listed in the above table until it has made the necessary inquiries and selections. The host can send the boot program state inquiry command (H'4F) even after acceptance of the transition-to-programming/erasure state command (H'40) by the boot program.

## (1) Inquiry on supported devices

In response to the inquiry on supported devices, the boot program returns the device codes of the devices it supports and the product names of their respective boot programs.

Command

H'20

- Command H'20 (1 byte): Inquiry on supported devices

Response

| H'30                    | Size        | No. of devices |              |

|-------------------------|-------------|----------------|--------------|

| Number of<br>characters | Device code |                | Product name |

|                         |             |                |              |

| SUM                     |             |                |              |

- Response H'30 (1 byte): Response to the inquiry on supported devices

- Size (1 byte): The length of data for transfer excluding the command code, this field (size), and the checksum. Here, it is the total number of bytes taken up by the number of devices, number of characters, device code, and product name fields.

- Number of devices (1 byte): The number of device models supported by the boot program embedded in the microcomputer.

- Number of characters (1 byte): The number of characters in the device code and product name fields.

- Device code (4 bytes): Device code of a supported device (ASCII encoded)

- Product name (n bytes): Product code of the boot program (ASCII encoded)

- SUM (1 byte): Checksum

This is set so that the total sum of all bytes from the command code to the checksum is H'00.

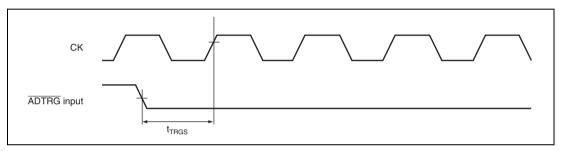

## 21.3.8 A/D Converter Timing

## Table 21.12 A/D Converter Timing

Conditions:  $V_{cc} = AV_{cc} = 4.0 \text{ V to } 5.5 \text{ V}, V_{ss} = PLLV_{ss} = AV_{ss} = 0 \text{ V},$   $T_a = -20 \text{ to } +85^{\circ}\text{C} \text{ (consumer specifications)},$  $T_a = -40 \text{ to } +85^{\circ}\text{C} \text{ (industrial specifications)}$

| Item                                                       | Symbol            | Min. | Тур. | Max. | Unit | Reference<br>Figure |

|------------------------------------------------------------|-------------------|------|------|------|------|---------------------|

| External trigger input start delay time (reference values) | t <sub>rrgs</sub> | 25   | —    | —    | ns   | Figure 21.15        |

Figure 21.15 External Trigger Input Timing

| Item                             | Page | Revision (See Manual for Details)                                                                                                                               |

|----------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.4.1 Interrupt Sources          | 81   | Note added                                                                                                                                                      |

| Table 5.7 Interrupt Sources      |      | Note: * The user break interrupt is not generated on<br>the 32 Kbyte (SH71251A and SH71241A)<br>and 16 Kbyte (SH71250A and SH71240A)<br>versions.               |

| 5.4.2 Interrupt Priority         | 82   | Table amended                                                                                                                                                   |

| Table 5.8 Interrupt Priority     |      | Type         Priority Level         Comment           User break*         15         Fixed priority level. Can be masked.                                       |

|                                  |      | Note added                                                                                                                                                      |

|                                  |      | Note: * The user break interrupt is not generated on<br>the 32 Kbyte (SH71251A and SH71241A)<br>and 16 Kbyte (SH71250A and SH71240A)<br>versions.               |

| 6.1 Features                     | 92   | Figure amended                                                                                                                                                  |

| Figure 6.1 Block Diagram of INTC |      | <complex-block></complex-block>                                                                                                                                 |

| 6.4.3 User Break Interrupt*      | 105  | Note added<br>Note: * The user break interrupt is not generated on<br>the 32 Kbyte (SH71251A and SH71241A)<br>and 16 Kbyte (SH71250A and SH71240A)<br>versions. |

RENESAS