Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | SH-2                                                                              |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 50MHz                                                                             |

| Connectivity               | SCI                                                                               |

| Peripherals                | POR, PWM, WDT                                                                     |

| Number of I/O              | 23                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                         |

| Data Converters            | A/D 8x10b                                                                         |

| Oscillator Type            | External                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 48-LQFP                                                                           |

| Supplier Device Package    | 48-LQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df71243d50fpv-z1 |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|       | 16.1.3  | Port A Port Register L (PAPRL)                       | 559 |

|-------|---------|------------------------------------------------------|-----|

| 16.2  | Port B. |                                                      | 561 |

|       | 16.2.1  | Register Descriptions                                |     |

|       | 16.2.2  | Port B Data Registers H and L (PBDRH and PBDRL)      | 562 |

|       | 16.2.3  | Port B Port Registers H and L (PBPRH and PBPRL)      | 565 |

| 16.3  | Port E. | -                                                    | 568 |

|       | 16.3.1  | Register Descriptions                                |     |

|       | 16.3.2  | Port E Data Register L (PEDRL)                       | 570 |

|       | 16.3.3  | Port E Port Register L (PEPRL)                       | 573 |

| 16.4  | Port F. |                                                      | 575 |

|       | 16.4.1  | Register Descriptions                                | 575 |

|       | 16.4.2  | Port F Data Register L (PFDRL)                       | 576 |

| 16.5  | Usage I | Notes                                                |     |

|       | 16.5.1  | Handling of Unused Pins                              |     |

|       |         |                                                      |     |

| Secti | on 17 ] | Flash Memory (ROM)                                   | 579 |

| 17.1  | Feature | 28                                                   | 579 |

| 17.2  | Overvi  | ew                                                   |     |

|       | 17.2.1  | Block Diagram                                        | 581 |

|       | 17.2.2  | Operating Mode                                       |     |

|       | 17.2.3  | Mode Comparison                                      | 583 |

|       | 17.2.4  | Flash Memory Configuration                           | 584 |

|       | 17.2.5  | Block Division                                       | 584 |

|       | 17.2.6  | Programming/Erasing Interface                        | 585 |

| 17.3  | Input/C | Dutput Pins                                          | 587 |

| 17.4  | Registe | r Descriptions                                       | 587 |

|       | 17.4.1  | Registers                                            | 587 |

|       | 17.4.2  | Programming/Erasing Interface Registers              | 590 |

|       | 17.4.3  | Programming/Erasing Interface Parameters             | 596 |

| 17.5  | On-Boa  | ard Programming Mode                                 | 611 |

|       | 17.5.1  | Boot Mode                                            | 611 |

|       | 17.5.2  | User Program Mode                                    |     |

|       |         | (Only in On-Chip 128-Kbyte and 64-Kbyte ROM Version) | 615 |

| 17.6  | Protect | ion                                                  |     |

|       | 17.6.1  | Hardware Protection                                  |     |

|       | 17.6.2  | Software Protection                                  |     |

|       | 17.6.3  | Error Protection                                     |     |

| 17.7  | Usage 1 | Notes                                                |     |

|       | 17.7.1  | Interrupts during Programming/Erasing                |     |

|       | 17.7.2  | Other Notes                                          | 629 |

| Secti | ion 21 Electrical Characteristics                      | 711 |

|-------|--------------------------------------------------------|-----|

| 21.1  | Absolute Maximum Ratings                               | 711 |

| 21.2  | DC Characteristics                                     |     |

| 21.3  | AC Characteristics                                     |     |

|       | 21.3.1 Clock Timing                                    |     |

|       | 21.3.2 Control Signal Timing                           | 717 |

|       | 21.3.3 Multi Function Timer Pulse Unit 2 (MTU2) Timing |     |

|       | 21.3.4 I/O Port Timing                                 |     |

|       | 21.3.5 Watchdog Timer (WDT) Timing                     |     |

|       | 21.3.6 Serial Communication Interface (SCI) Timing     |     |

|       | 21.3.7 Port Output Enable (POE) Timing                 |     |

|       | 21.3.8 A/D Converter Timing                            |     |

|       | 21.3.9 Conditions for Testing AC Characteristics       |     |

| 21.4  | A/D Converter Characteristics                          |     |

| 21.5  | Flash Memory Characteristics                           |     |

| 21.6  | Usage Note                                             |     |

|       | 21.6.1 Notes on Connecting V <sub>CL</sub> Capacitor   |     |

| Appe  | endix                                                  | 733 |

| A.    | Pin States                                             |     |

| B.    | Product Code Lineup                                    |     |

| C.    | Package Dimensions                                     |     |

| Main  | n Revisions for This Edition                           | 745 |

| Index | x                                                      |     |

# 1.4 Pin Functions

Table 1.2 summarizes the pin functions.

# Table 1.2Pin Functions

| Classification         | Symbol | I/O | Name                                | Function                                                                                                     |

|------------------------|--------|-----|-------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Power supply           | Vcc    | Ι   | Power supply                        | Power supply pin                                                                                             |

|                        |        |     |                                     | Connect all Vcc pins to the system.<br>There will be no operation if any pins<br>are open.                   |

|                        | Vss    | Ι   | Ground                              | Ground pin                                                                                                   |

|                        |        |     |                                     | Connect all Vss pins to the system<br>power supply (0V). There will be no<br>operation if any pins are open. |

|                        | VCL    | 0   | Power supply for<br>internal power- | External capacitance pins for internal power-down power supply                                               |

|                        |        |     | down                                | Connect these pins to Vss via a 0.1 to 0.47 $\mu$ F capacitor (placed close to the pins).                    |

| Clock                  | PLLVss | I   | PLL ground                          | Ground pin for the on-chip PLL oscillator                                                                    |

|                        | EXTAL  | I   | External clock                      | Connected to a crystal resonator.<br>An external clock signal may also be<br>input to the EXTAL pin.         |

|                        | XTAL   | 0   | Crystal                             | Connected to a crystal resonator.                                                                            |

| Operating mode control | MD1    | I   | Mode set                            | Sets the operating mode. Do not change values on this pin during operation.                                  |

|                        | FWE    | Ι   | Flash memory                        | Pin for flash memory                                                                                         |

|                        |        |     | write enable                        | Flash memory can be protected against programming or erasure through this pin.                               |

| Instru | iction      | Operation                                                           | Code             | Execution<br>Cycles | T Bit |

|--------|-------------|---------------------------------------------------------------------|------------------|---------------------|-------|

| STS    | MACH,Rn     | $MACH \to Rn$                                                       | 0000nnnn00001010 | 1                   | _     |

| STS    | MACL,Rn     | $MACL \to Rn$                                                       | 0000nnnn00011010 | 1                   | _     |

| STS    | PR,Rn       | $PR\toRn$                                                           | 0000nnnn00101010 | 1                   | _     |

| STS.I  | L MACH,@—Rn | Rn–4 $\rightarrow$ Rn, MACH $\rightarrow$ (Rn)                      | 0100nnnn00000010 | 1                   | _     |

| STS.I  | L MACL,@—Rn | Rn–4 $\rightarrow$ Rn, MACL $\rightarrow$ (Rn)                      | 0100nnnn00010010 | 1                   | _     |

| STS.I  | LPR,@-Rn    | Rn–4 $\rightarrow$ Rn, PR $\rightarrow$ (Rn)                        | 0100nnnn00100010 | 1                   | _     |

| TRAP   | A #imm      | $PC/SR \rightarrow Stack area,$<br>(imm × 4 + VBR) $\rightarrow PC$ | 11000011iiiiiiii | 8                   |       |

Note: \* Number of execution cycles until this LSI enters sleep mode.

About the number of execution cycles:

The table lists the minimum number of execution cycles. In practice, the number of execution cycles will be increased depending on the conditions such as:

- When there is a conflict between instruction fetch and data access

- When the destination register of a load instruction (memory → register) is also used by the instruction immediately after the load instruction.

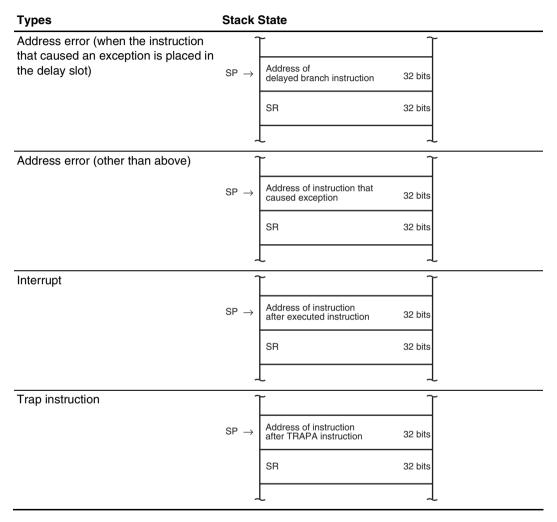

# 5.7 Stack States after Exception Handling Ends

The stack states after exception handling ends are shown in table 5.11.

#### Table 5.11 Stack Status after Exception Handling Ends

# 6.8 Usage Note

### 6.8.1 Clearing Interrupt Source Flags

The interrupt source flag should be cleared in the interrupt handler. To ensure that an interrupt source that should have been cleared is not inadvertently accepted again, read the interrupt source flag after it has been cleared, confirm that it has been cleared, and then execute an RTE instruction.

### 6.8.2 NMI Not Used

If NMI is not used, connect it to  $V_{cc}$  via a resistor and fix it high.

#### 7.2.9 Break Data Mask Register B (BDMRB)

BDMRB is a 32-bit readable/writable register. BDMRB specifies bits masked in the break data specified by BDRB.

| Bi            | : 31   | 30     | 29          | 28     | 27     | 26     | 25     | 24     | 23     | 22     | 21     | 20     | 19     | 18     | 17     | 16         |

|---------------|--------|--------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

|               | BDMB31 | BDMB30 | BDMB29      | BDMB28 | BDMB27 | BDMB26 | BDMB25 | BDMB24 | BDMB23 | BDMB22 | BDMB21 | BDMB20 | BDMB19 | BDMB18 | BDMB17 | BDMB16     |

| Initial value | : 0    | 0      | 0           | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0          |

| R/W           | : R/W  | R/W    | R/W         | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W        |

|               |        |        |             |        |        |        |        |        |        |        |        |        |        |        |        |            |

| Bi            | : 15   | 14     | 13          | 12     | 11     | 10     | 9      | 8      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0          |

|               |        |        |             |        |        |        |        |        |        |        |        |        |        |        |        |            |

|               | BDMB15 | BDMB14 | BDMB13      | BDMB12 | BDMB11 | BDMB10 | BDMB9  | BDMB8  | BDMB7  | BDMB6  | BDMB5  | BDMB4  | BDMB3  | BDMB2  | BDMB1  | BDMB0      |

| Initial value |        | BDMB14 | BDMB13<br>0 | BDMB12 | BDMB11 | BDMB10 | BDMB9  | BDMB8  | BDMB7  | BDMB6  | BDMB5  | BDMB4  | BDMB3  | BDMB2  | BDMB1  | BDMB0<br>0 |

| Bit     | Bit Name     | Initial<br>Value | R/W       | Description                                                                             |

|---------|--------------|------------------|-----------|-----------------------------------------------------------------------------------------|

| 31 to 0 | BDMB31 to    | All 0            | R/W       | Break Data Mask B                                                                       |

|         | BDMB 0       |                  |           | Specifies bits masked in the break data of channel B specified by BDRB (BDB31 to BDB0). |

|         |              |                  |           | 0: Break data BDBn of channel B is included in the<br>break condition                   |

|         |              |                  |           | 1: Break data BDBn of channel B is masked and is not<br>included in the break condition |

|         |              |                  |           | Note: n = 31 to 0                                                                       |

| Notes   | 1 Specify an | operand          | sizo whor | including the value of the data bus in the break condition                              |

Notes: 1. Specify an operand size when including the value of the data bus in the break condition.

2. When the byte size is selected as a break condition, the same byte data must be set in bits 15 to 8 and 7 to 0 in BDMRB as the break mask data in BDRB.

#### 7.2.10 Break Bus Cycle Register B (BBRB)

BBRB is a 16-bit readable/writable register, which specifies (1) bus master for I bus cycle, (2) L bus cycle or I bus cycle, (3) instruction fetch or data access, (4) read or write, and (5) operand size in the break conditions of channel B.

| Bit           | : 15 | 14 | 13 | 12 | 11 | 10  | 9        | 8   | 7   | 6     | 5   | 4     | 3   | 2      | 1   | 0     |

|---------------|------|----|----|----|----|-----|----------|-----|-----|-------|-----|-------|-----|--------|-----|-------|

|               | -    | -  | -  | -  | -  | (   | CPB[2:0] |     | CDB | [1:0] | IDB | [1:0] | RWE | 8[1:0] | SZB | [1:0] |

| Initial value | : 0  | 0  | 0  | 0  | 0  | 0   | 0        | 0   | 0   | 0     | 0   | 0     | 0   | 0      | 0   | 0     |

| R/W           | R    | R  | R  | R  | R  | R/W | R/W      | R/W | R/W | R/W   | R/W | R/W   | R/W | R/W    | R/W | R/W   |

| Bit      | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                          |

|----------|----------|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 to 11 | _        | All 0            | R   | Reserved                                                                                                                                                                                                             |

|          |          |                  |     | These bits are always read as 0. The write value should always be 0.                                                                                                                                                 |

| 10 to 8  | CPB[2:0] | 000              | R/W | Bus Master Select B for I Bus                                                                                                                                                                                        |

|          |          |                  |     | Select the bus master when the I bus is selected as<br>the bus cycle of the channel B break condition.<br>However, when the L bus is selected as the bus cycle,<br>the setting of the CPB2 to CPB0 bits is disabled. |

|          |          |                  |     | 000: Condition comparison is not performed                                                                                                                                                                           |

|          |          |                  |     | xx1: The CPU cycle is included in the break condition                                                                                                                                                                |

|          |          |                  |     | x1x: Setting prohibited                                                                                                                                                                                              |

|          |          |                  |     | 1xx: Setting prohibited                                                                                                                                                                                              |

| 7, 6     | CDB[1:0] | 00               | R/W | L Bus Cycle/I Bus Cycle Select B                                                                                                                                                                                     |

|          |          |                  |     | Select the L bus cycle or I bus cycle as the bus cycle of the channel B break condition.                                                                                                                             |

|          |          |                  |     | 00: Condition comparison is not performed                                                                                                                                                                            |

|          |          |                  |     | 01: The break condition is the L bus cycle                                                                                                                                                                           |

|          |          |                  |     | 10: The break condition is the I bus cycle                                                                                                                                                                           |

|          |          |                  |     | 11: The break condition is the L bus cycle                                                                                                                                                                           |

| Access Size | Address Compared                                                         |

|-------------|--------------------------------------------------------------------------|

| Longword    | Compares break address register bits 31 to 2 to address bus bits 31 to 2 |

| Word        | Compares break address register bits 31 to 1 to address bus bits 31 to 1 |

| Byte        | Compares break address register bits 31 to 0 to address bus bits 31 to 0 |

Table 7.2

Data Access Cycle Addresses and Operand Size Comparison Conditions

This means that when address H'00001003 is set in the break address register (BARA or BARB), for example, the bus cycle in which the break condition is satisfied is as follows (where other conditions are met).

Longword access at H'00001000

Word access at H'00001002

Byte access at H'00001003

3. When the data value is included in the break conditions:

When the data value is included in the break conditions, either longword, word, or byte is specified as the operand size of the break bus cycle register (BBRA or BBRB). When data values are included in break conditions, a break is generated when the address conditions and data conditions both match. To specify byte data for this case, set the same data in two bytes at bits 15 to 8 and bits 7 to 0 of the break data register (BDRA or BDRB) and break data mask register (BDMRA or BDMRB). When word or byte is set, bits 31 to 16 of BDRA or BDRB and BDMRA or BDMRB are ignored.

4. If the L bus is selected, a break occurs on ending execution of the instruction that matches the break condition, and immediately before the next instruction is executed. However, when data is also specified as the break condition, the break may occur on ending execution of the instruction following the instruction that matches the break condition. If the I bus is selected, the instruction at which the break will occur cannot be determined. When this kind of break occurs at a delayed branch instruction or its delay slot, the break may not actually take place until the first instruction at the branch destination.

|               |               |               |               |                           | Description                                                                 |  |  |  |  |  |

|---------------|---------------|---------------|---------------|---------------------------|-----------------------------------------------------------------------------|--|--|--|--|--|

| Bit 3<br>IOA3 | Bit 2<br>IOA2 | Bit 1<br>IOA1 | Bit 0<br>IOA0 | TGRA_1<br>Function        | TIOC1A Pin Function* <sup>2</sup>                                           |  |  |  |  |  |

| 0             | 0             | 0             | 0             | Output                    | Output retained*1                                                           |  |  |  |  |  |

|               |               |               | 1             | compare<br>register       | Initial output is 0                                                         |  |  |  |  |  |

|               |               |               |               | register                  | 0 output at compare match                                                   |  |  |  |  |  |

|               |               | 1             | 0             | -                         | Initial output is 0                                                         |  |  |  |  |  |

|               |               |               |               | 1 output at compare match |                                                                             |  |  |  |  |  |

|               |               |               | 1             | -                         | Initial output is 0                                                         |  |  |  |  |  |

|               |               |               |               |                           | Toggle output at compare match                                              |  |  |  |  |  |

|               | 1             | 0             | 0             | -                         | Output retained                                                             |  |  |  |  |  |

|               |               |               | 1             | -                         | Initial output is 1                                                         |  |  |  |  |  |

|               |               |               |               |                           | 0 output at compare match                                                   |  |  |  |  |  |

|               |               | 1             | 0             | _                         | Initial output is 1                                                         |  |  |  |  |  |

|               |               |               |               |                           | 1 output at compare match                                                   |  |  |  |  |  |

|               |               |               | 1             | _                         | Initial output is 1                                                         |  |  |  |  |  |

|               |               |               |               |                           | Toggle output at compare match                                              |  |  |  |  |  |

| 1             | 0             | 0             | 0             |                           | Input capture at rising edge                                                |  |  |  |  |  |

|               |               |               | 1             | register                  | Input capture at falling edge                                               |  |  |  |  |  |

|               |               | 1             | х             | _                         | Input capture at both edges                                                 |  |  |  |  |  |

| <u>[]</u>     | 1             | x             | x             | _                         | Input capture at generation of channel 0/TGRA_0 compare match/input capture |  |  |  |  |  |

#### Table 9.22 TIOR\_1 (Channel 1)

[Legend]

x: Don't care

Notes: 1. After power-on reset, 0 is output until TIOR is set.

2. The TIOC1A pin input/output function is supported only by the SH7125.

| <b>Table 9.38</b> | <b>TIOC3B Output Level Select Function</b> |

|-------------------|--------------------------------------------|

|-------------------|--------------------------------------------|

| Bit 0 | Function       |              |                      |            |  |  |

|-------|----------------|--------------|----------------------|------------|--|--|

|       |                |              | Compare Match Output |            |  |  |

| OLS1P | Initial Output | Active Level | Up Count             | Down Count |  |  |

| 0     | High level     | Low level    | Low level            | High level |  |  |

| 1     | Low level      | High level   | High level           | Low level  |  |  |

#### 9.3.20 Timer Output Level Buffer Register (TOLBR)

TOLBR is an 8-bit readable/writable register that functions as a buffer for TOCR2 and specifies the PWM output level in complementary PWM mode and reset-synchronized PWM mode.

| Bit:           | 7 | 6 | 5     | 4     | 3     | 2     | 1     | 0     |

|----------------|---|---|-------|-------|-------|-------|-------|-------|

|                | - | - | OLS3N | OLS3P | OLS2N | OLS2P | OLS1N | OLS1P |

| Initial value: | 0 | 0 | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W:           | R | R | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Bit  | Bit Name | Initial<br>value | R/W | Description                                                             |

|------|----------|------------------|-----|-------------------------------------------------------------------------|

| 7, 6 | _        | All 0            | R   | Reserved                                                                |

|      |          |                  |     | These bits are always read as 0. The write value should always be 0.    |

| 5    | OLS3N    | 0                | R/W | Specifies the buffer value to be transferred to the OLS3N bit in TOCR2. |

| 4    | OLS3P    | 0                | R/W | Specifies the buffer value to be transferred to the OLS3P bit in TOCR2. |

| 3    | OLS2N    | 0                | R/W | Specifies the buffer value to be transferred to the OLS2N bit in TOCR2. |

| 2    | OLS2P    | 0                | R/W | Specifies the buffer value to be transferred to the OLS2P bit in TOCR2. |

| 1    | OLS1N    | 0                | R/W | Specifies the buffer value to be transferred to the OLS1N bit in TOCR2. |

| 0    | OLS1P    | 0                | R/W | Specifies the buffer value to be transferred to the OLS1P bit in TOCR2. |

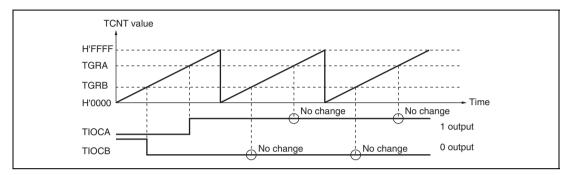

2. Examples of Waveform Output Operation:

Figure 9.8 shows an example of 0 output/1 output.

In this example, TCNT has been designated as a free-running counter, and settings have been made such that 1 is output by compare match A, and 0 is output by compare match B. When the set level and the pin level coincide, the pin level does not change.

Figure 9.8 Example of 0 Output/1 Output Operation

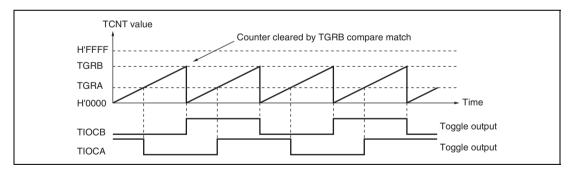

Figure 9.9 shows an example of toggle output.

In this example, TCNT has been designated as a periodic counter (with counter clearing on compare match B), and settings have been made such that the output is toggled by both compare match A and compare match B.

Figure 9.9 Example of Toggle Output Operation

Figure 9.52 Example of Complementary PWM Mode 0% and 100% Waveform Output (4)

Figure 9.53 Example of Complementary PWM Mode 0% and 100% Waveform Output (5)

RENESAS

## 17. A/D Converter Start Request Setting

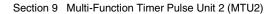

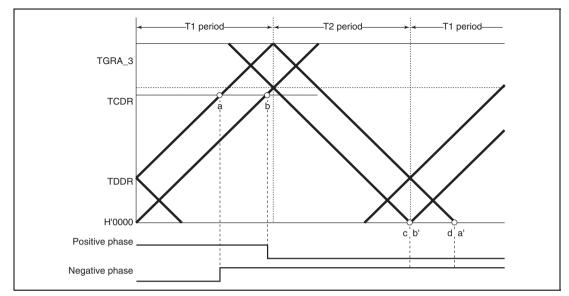

In complementary PWM mode, an A/D converter start request can be issued using a TGRA\_3 compare-match, TCNT\_4 underflow (trough), or compare-match on a channel other than channels 3 and 4.

When start requests using a TGRA\_3 compare-match are specified, A/D conversion can be started at the crest of the TCNT\_3 count.

A/D converter start requests can be set by setting the TTGE bit to 1 in the timer interrupt enable register (TIER). To issue an A/D converter start request at a TCNT\_4 underflow (trough), set the TTGE2 bit in TIER\_4 to 1.

## Interrupt Skipping in Complementary PWM Mode:

Interrupts TGIA\_3 (at the crest) and TCIV\_4 (at the trough) in channels 3 and 4 can be skipped up to seven times by making settings in the timer interrupt skipping set register (TITCR).

Transfers from a buffer register to a temporary register or a compare register can be skipped in coordination with interrupt skipping by making settings in the timer buffer transfer register (TBTER). For the linkage with buffer registers, refer to description 3, Buffer Transfer Control Linked with Interrupt Skipping, below.

A/D converter start requests generated by the A/D converter start request delaying function can also be skipped in coordination with interrupt skipping by making settings in the timer A/D converter request control register (TADCR). For the linkage with the A/D converter start request delaying function, refer to section 9.4.9, A/D Converter Start Request Delaying Function.

The setting of the timer interrupt skipping setting register (TITCR) must be done while the TGIA\_3 and TCIV\_4 interrupt requests are disabled by the settings of registers TIER\_3 and TIER\_4 along with under the conditions in which TGFA\_3 and TCFV\_4 flag settings by compare match never occur. Before changing the skipping count, be sure to clear the T3AEN and T4VEN bits to 0 to clear the skipping counter.

## 1. Example of Interrupt Skipping Operation Setting Procedure

Figure 9.67 shows an example of the interrupt skipping operation setting procedure. Figure 9.68 shows the periods during which interrupt skipping count can be changed.

#### 9.7.20 Output Level in Complementary PWM Mode and Reset-Synchronized PWM Mode

When channels 3 and 4 are in complementary PWM mode or reset-synchronized PWM mode, the PWM waveform output level is set with the OLSP and OLSN bits in the timer output control register (TOCR). In the case of complementary PWM mode or reset-synchronized PWM mode, TIOR should be set to H'00.

#### 9.7.21 Interrupts in Module Standby Mode

If module standby mode is entered when an interrupt has been requested, it will not be possible to clear the CPU interrupt source. Interrupts should therefore be disabled before entering module standby mode.

#### 9.7.22 Simultaneous Capture of TCNT\_1 and TCNT\_2 in Cascade Connection

When timer counters 1 and 2 (TCNT\_1 and TCNT\_2) are operated as a 32-bit counter in cascade connection, the cascade counter value cannot be captured successfully even if input-capture input is simultaneously done to TIOC1A and TIOC2A or to TIOC1B and TIOC2B. This is because the input timing of TIOC1A and TIOC2A or of TIOC1B and TIOC2B may not be the same when external input-capture signals to be input into TCNT\_1 and TCNT\_2 are taken in synchronization with the internal clock. For example, TCNT\_1 (the counter for upper 16 bits) does not capture the count-up value by overflow from TCNT\_2 (the counter for lower 16 bits) but captures the count value before the count-up. In this case, the values of TCNT\_1 = H'FFF1 and TCNT\_2 = H'0000 should be transferred to TGRA\_1 and TGRA\_2 or to TGRB\_1 and TGRB\_2, but the values of TCNT\_1 = H'FFF0 and TCNT\_2 = H'0000 are erroneously transferred.

The MTU2 has a new function that allows simultaneous capture of TCNT\_1 and TCNT\_2 with a single input-capture input as the trigger. This function allows reading of the 32-bit counter such that TCNT\_1 and TCNT\_2 are captured at the same time.

See section 9.3.8, Timer Input Capture Control Register (TICCR), for details.

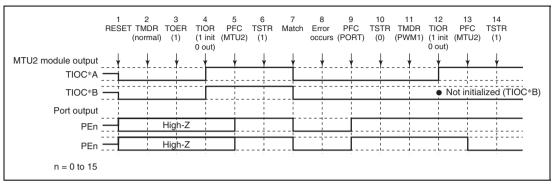

**Operation when Error Occurs during Normal Mode Operation, and Operation is Restarted in PWM Mode 1:** Figure 9.125 shows an explanatory diagram of the case where an error occurs in normal mode and operation is restarted in PWM mode 1 after re-setting.

Figure 9.125 Error Occurrence in Normal Mode, Recovery in PWM Mode 1

1 to 10 are the same as in figure 9.124.

- 11. Set PWM mode 1.

- 12. Initialize the pins with TIOR. (In PWM mode 1, the TIOC\*B side is not initialized. If initialization is required, initialize in normal mode, then switch to PWM mode 1.)

- 13. Set MTU2 output with the PFC.

- 14. Operation is restarted by TSTR.

• The start address in the user branch destination is set to the FUBRA parameter (general register R5).

When the user branch processing is not required, 0 must be set to FUBRA.

When the user branch is executed, the branch destination is executed in flash memory other than the one that is to be programmed. The area of the on-chip program that is downloaded cannot be set.

The program processing must be returned from the user branch processing by the RTS instruction.

See the description in section 17.4.3 (2.2), Flash user branch address setting parameter (FUBRA: general register R5 of CPU).

(2.7) Initialization

When a programming program is downloaded, the initialization program is also downloaded to on-chip RAM. There is an entry point of the initialization program in the area from (download start address set by FTDAR) + 32 bytes. The subroutine is called and initialization is executed by using the following steps.

```

MOV.L #DLTOP+32,R1 ; Set entry address to R1

JSR @R1 ; Call initialization routine

NOP

```

- The general registers other than R0 are saved in the initialization program.

- R0 is a return value of the FPFR parameter.

- Since the stack area is used in the initialization program, a stack area of maximum 128 bytes must be reserved in RAM.

- Interrupts can be accepted during the execution of the initialization program. However, the program storage area and stack area in on-chip RAM and register values must not be destroyed.

- (2.8) The return value of the initialization program, FPFR (general register R0) is checked.

- (2.9) FKEY must be set to H'5A and the user MAT must be prepared for programming.

- (2.10) The parameter which is required for programming is set.

The start address of the programming destination of the user MAT (FMPAR) is set to general register R5. The start address of the program data storage area (FMPDR) is set to general register R4.

• FMPAR setting

FMPAR specifies the programming destination start address. When an address other than one in the user MAT area is specified, even if the programming program is executed, programming is not executed and an error is returned to the return value

RENESAS

All commands in the above table, except for the boot program state inquiry command (H'4F), are valid until the boot program accepts the transition-to-programming/erasure state command (H'40). That is, until the transition command is accepted, the host can continue to send commands listed in the above table until it has made the necessary inquiries and selections. The host can send the boot program state inquiry command (H'4F) even after acceptance of the transition-to-programming/erasure state command (H'40) by the boot program.

### (1) Inquiry on supported devices

In response to the inquiry on supported devices, the boot program returns the device codes of the devices it supports and the product names of their respective boot programs.

Command

H'20

- Command H'20 (1 byte): Inquiry on supported devices

Response

| H'30                             | Size | No. of devices |              |

|----------------------------------|------|----------------|--------------|

| Number of Device code characters |      |                | Product name |

|                                  |      |                |              |

| SUM                              |      |                |              |

- Response H'30 (1 byte): Response to the inquiry on supported devices

- Size (1 byte): The length of data for transfer excluding the command code, this field (size), and the checksum. Here, it is the total number of bytes taken up by the number of devices, number of characters, device code, and product name fields.

- Number of devices (1 byte): The number of device models supported by the boot program embedded in the microcomputer.

- Number of characters (1 byte): The number of characters in the device code and product name fields.

- Device code (4 bytes): Device code of a supported device (ASCII encoded)

- Product name (n bytes): Product code of the boot program (ASCII encoded)

- SUM (1 byte): Checksum

This is set so that the total sum of all bytes from the command code to the checksum is H'00.

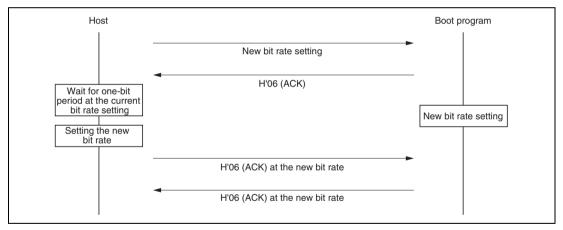

When the new bit rate is selectable, the boot program returns an ACK code to the host and then makes the register setting to select the new bit rate. The host then sends an ACK code at the new bit rate, and the boot program responds to this with another ACK code, this time at the new bit rate.

Acknowledge H'06

Acknowledge H'06 (1 byte): The ACK code sent by the host to acknowledge the new bit rate.

Response H'06

Response H'06 (1 byte): The ACK code transferred in response to acknowledgement of the new bit rate

The sequence of new bit rate selection is shown in figure 17.18.

Figure 17.18 Sequence of New Bit Rate Selection

RENESAS

• Sum checking of the user MAT

In response to the command for sum checking of the user MAT, the boot program adds all bytes of data in the user MAT and returns the result.

Command H'4B

- Command H'4B (1 byte): Sum checking of the user MAT

| Response | H'5B | Size | Checksum for the MAT | SUM |

|----------|------|------|----------------------|-----|

|----------|------|------|----------------------|-----|

- Response H'5B (1 byte): Response to sum checking of the user MAT

- Size (1 byte): The number of characters in the checksum for the MAT (fixed to 4)

- Checksum for the MAT (4 bytes): Result of checksum calculation for the user MAT: the total of all data in the MAT, in byte units.

- SUM (1 byte): Checksum (for the transmitted data)

- Blank checking of the user MAT

In response to the command for blank checking of the user MAT, the boot program checks to see if the whole of the user MAT is blank; the value returned indicates the result.

Command

- Command H'4D (1 byte): Blank checking of the user MAT

Response

H'06

H'4D

Response H'06 (1 byte): Response to blank checking of the user MAT The ACK code is returned when the whole area is blank (all bytes are H'FF).

| Error    |      |      |  |  |  |  |

|----------|------|------|--|--|--|--|

| response | H'CD | H'52 |  |  |  |  |

- Error response H'CD (1 byte): Error response to blank checking of the user MAT

- Error code H'52 (1 byte): Non-erased error