#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | SH-2                                                                            |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 50MHz                                                                           |

| Connectivity               | SCI                                                                             |

| Peripherals                | POR, PWM, WDT                                                                   |

| Number of I/O              | 37                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                       |

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | External                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-LQFP                                                                         |

| Supplier Device Package    | 64-LFQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df71251ad50fpv |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The clock pulse generator blocks function as follows:

**PLL Circuit:** The PLL circuit multiples the clock frequency input from the crystal oscillator or the EXTAL pin by 8. The multiplication ratio is fixed at  $\times$ 8.

**Crystal Oscillator:** The crystal oscillator is an oscillator circuit when a crystal resonator is connected to the XTAL and EXTAL pins.

**Divider:** The divider generates clocks with the frequencies to be used by the internal clock  $(I\phi)$ , bus clock  $(B\phi)$ , peripheral clock  $(P\phi)$ , and MTU2 clock  $(MP\phi)$ .

The frequencies can be selected from 1/2, 1/4 (initial value), and 1/8 times the frequency output from the PLL circuit. The division ratio should be specified in the frequency control register (FRQCR).

**Oscillation Stop Detection Circuit:** This circuit detects an abnormal condition in the crystal oscillator.

**Clock Frequency Control Circuit:** The clock frequency control circuit controls the clock frequency according to the setting in the frequency control register (FRQCR).

**Standby Control Circuit:** The standby control circuit controls the state of the on-chip oscillator circuit and other modules in sleep or standby mode.

**Frequency Control Register (FRQCR):** The frequency control register (FRQCR) has control bits for the frequency division ratios of the internal clock ( $I\phi$ ), bus clock ( $B\phi$ ), peripheral clock ( $P\phi$ ), and MTU2 clock ( $MP\phi$ ).

**Oscillation Stop Detection Control Register (OSCCR):** The oscillation stop detection control register (OSCCR) has an oscillation stop detection flag and a bit for selecting flag status output through an external pin.

**Standby Control Registers 1 to 6 (STBCR1 to STBCR6):** The standby control register (STBCR) has bits for controlling the power-down modes. For details, see section 19, Power-Down Modes.

# 6.5 Interrupt Exception Handling Vector Table

Table 6.3 lists interrupt sources, their vector numbers, vector table address offsets, and interrupt priorities.

Individual interrupt sources are allocated to different vector numbers and vector table address offsets. Vector table addresses are calculated from the vector numbers and vector table address offsets. For interrupt exception handling, the start address of the exception handling routine is fetched from the vector table address in the vector table. For the details on calculation of vector table addresses, see table 5.4 in section 5, Exception Handling.

IRQ interrupts and on-chip peripheral module interrupt priorities can be set freely between 0 and 15 for each pin or module by setting interrupt priority registers A to F and H to M (IPRA to IPRF and IPRH to IPRM). However, when interrupt sources whose priority levels are allocated with the same IPR are requested, the interrupt of the smaller vector number has priority. This priority cannot be changed. Priority levels of IRQ interrupts and on-chip peripheral module interrupts are initialized to level 0 at a power-on reset. If the same priority level is allocated to two or more interrupt sources and interrupts from those sources occur simultaneously, they are processed by the default priority order shown in table 6.3.

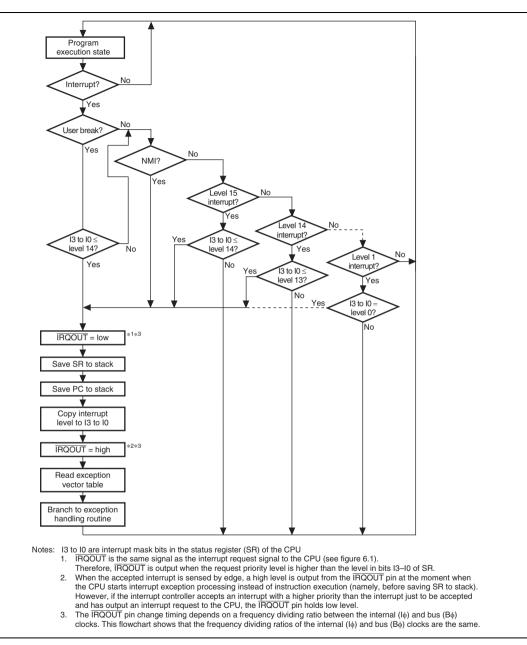

#### Figure 6.3 Interrupt Sequence Flowchart

RENESAS

Rev. 5.00 Mar. 06, 2009 Page 111 of 770 REJ09B0243-0500

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                             |

|-----|----------|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18  |          | 0                | R   | Reserved                                                                                                                                                                |

|     |          |                  |     | This bit is always read as 0. The write value should always be 0.                                                                                                       |

| 17  | UBIDA    | 0                | R/W | User Break Disable A                                                                                                                                                    |

|     |          |                  |     | Enables or disables the user break interrupt request when the channel A break conditions are satisfied.                                                                 |

|     |          |                  |     | 0: User break interrupt request is enabled when break<br>conditions are satisfied                                                                                       |

|     |          |                  |     | 1: User break interrupt request is disabled when break<br>conditions are satisfied                                                                                      |

| 16  | _        | 0                | R   | Reserved                                                                                                                                                                |

|     |          |                  |     | This bit is always read as 0. The write value should always be 0.                                                                                                       |

| 15  | SCMFCA   | 0                | R/W | L Bus Cycle Condition Match Flag A                                                                                                                                      |

|     |          |                  |     | When the L bus cycle condition in the break conditions<br>set for channel A is satisfied, this flag is set to 1. In<br>order to clear this flag, write 0 into this bit. |

|     |          |                  |     | 0: The L bus cycle condition for channel A does not<br>match                                                                                                            |

|     |          |                  |     | 1: The L bus cycle condition for channel A matches                                                                                                                      |

| 14  | SCMFCB   | 0                | R/W | L Bus Cycle Condition Match Flag B                                                                                                                                      |

|     |          |                  |     | When the L bus cycle condition in the break conditions<br>set for channel B is satisfied, this flag is set to 1. In<br>order to clear this flag, write 0 into this bit. |

|     |          |                  |     | 0: The L bus cycle condition for channel B does not<br>match                                                                                                            |

|     |          |                  |     | 1: The L bus cycle condition for channel B matches                                                                                                                      |

| 13  | SCMFDA   | 0                | R/W | I Bus Cycle Condition Match Flag A                                                                                                                                      |

|     |          |                  |     | When the I bus cycle condition in the break conditions<br>set for channel A is satisfied, this flag is set to 1. In<br>order to clear this flag, write 0 into this bit. |

|     |          |                  |     | 0: The I bus cycle condition for channel A does not<br>match                                                                                                            |

|     |          |                  |     | 1: The I bus cycle condition for channel A matches                                                                                                                      |

| Item                      |                  | Channel 0                                                                          | Channel 1                                                       | Channel 2                                                                 | Channel 3                                                                   | Channel 4                                                                   | Channel 5                                   |

|---------------------------|------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------|

| Count clos                | :k               | MP\phi/1<br>MP\phi/4<br>MP\phi/16<br>MP\phi/64<br>TCLKA<br>TCLKB<br>TCLKC<br>TCLKD | MPφ/1<br>MPφ/4<br>MPφ/16<br>MPφ/64<br>MPφ/256<br>TCLKA<br>TCLKB | MPφ/1<br>MPφ/4<br>MPφ/16<br>MPφ/64<br>MPφ/1024<br>TCLKA<br>TCLKB<br>TCLKC | MPφ/1<br>MPφ/4<br>MPφ/16<br>MPφ/64<br>MPφ/256<br>MPφ/1024<br>TCLKA<br>TCLKB | MPφ/1<br>MPφ/4<br>MPφ/16<br>MPφ/64<br>MPφ/256<br>MPφ/1024<br>TCLKA<br>TCLKB | MΡφ/1<br>MΡφ/4<br>MΡφ/16<br>MΡφ/64          |

| General re                | egisters         | TGRA_0<br>TGRB_0<br>TGRE_0                                                         | TGRA_1<br>TGRB_1                                                | TGRA_2<br>TGRB_2                                                          | TGRA_3<br>TGRB_3                                                            | TGRA_4<br>TGRB_4                                                            | TGRU_5<br>TGRV_5<br>TGRW_5                  |

| General re<br>buffer regi | 0                | TGRC_0<br>TGRD_0<br>TGRF_0                                                         | —                                                               | _                                                                         | TGRC_3<br>TGRD_3                                                            | TGRC_4<br>TGRD_4                                                            | _                                           |

| I/O pins                  |                  | TIOC0A<br>TIOC0B<br>TIOC0C<br>TIOC0D                                               | TIOC1A <sup>*1</sup><br>TIOC1B <sup>*1</sup>                    | TIOC2A* <sup>1</sup><br>TIOC2B* <sup>1</sup>                              | TIOC3A<br>TIOC3B<br>TIOC3C<br>TIOC3D                                        | TIOC4A<br>TIOC4B<br>TIOC4C<br>TIOC4D                                        | Input pins<br>TIC5U<br>TIC5V<br>TIC5W       |

| Counter cl<br>function    | ear              | TGR<br>compare<br>match or<br>input capture                                        | TGR<br>compare<br>match or<br>input capture                     | TGR<br>compare<br>match or<br>input capture                               | TGR<br>compare<br>match or<br>input capture                                 | TGR<br>compare<br>match or<br>input capture                                 | TGR<br>compare<br>match or<br>input capture |

| Compare                   | 0 output         | $\checkmark$                                                                       |                                                                 |                                                                           |                                                                             |                                                                             | _                                           |

| match<br>output           | 1 output         |                                                                                    |                                                                 |                                                                           |                                                                             |                                                                             | _                                           |

| ouput                     | Toggle<br>output |                                                                                    |                                                                 | $\checkmark$                                                              | $\checkmark$                                                                | $\checkmark$                                                                | _                                           |

| Input capt<br>function    | ure              |                                                                                    |                                                                 |                                                                           | $\checkmark$                                                                | $\checkmark$                                                                |                                             |

| Synchrono<br>operation    | DUS              |                                                                                    | $\checkmark$                                                    | $\checkmark$                                                              | $\checkmark$                                                                | $\checkmark$                                                                | _                                           |

| PWM mode 1                |                  |                                                                                    |                                                                 |                                                                           |                                                                             |                                                                             | _                                           |

| PWM mode 2                |                  | $\checkmark$                                                                       |                                                                 |                                                                           | _                                                                           | _                                                                           | _                                           |

| Compleme<br>PWM mod       | -                | _                                                                                  |                                                                 |                                                                           | $\checkmark$                                                                | $\checkmark$                                                                | _                                           |

| Reset PW                  | M mode           | _                                                                                  | _                                                               | _                                                                         |                                                                             |                                                                             | _                                           |

| AC synchr<br>motor driv   |                  |                                                                                    | _                                                               | _                                                                         | $\checkmark$                                                                | $\checkmark$                                                                | _                                           |

## Table 9.1MTU2 Functions

## 9.3.1 Timer Control Register (TCR)

The TCR registers are 8-bit readable/writable registers that control the TCNT operation for each channel. The MTU2 has a total of eight TCR registers, one each for channels 0 to 4 and three (TCRU\_5, TCRV\_5, and TCRW\_5) for channel 5. TCR register settings should be conducted only when TCNT operation is stopped.

| Bit:           | 7 6 |         | 5   | 4   | 4 3    |           | 2 1 |     |  |

|----------------|-----|---------|-----|-----|--------|-----------|-----|-----|--|

|                | C   | CLR[2:0 | ]   | CKE | G[1:0] | TPSC[2:0] |     |     |  |

| Initial value: | 0   | 0       | 0   | 0   | 0      | 0         | 0   | 0   |  |

| R/W:           | R/W | R/W     | R/W | R/W | R/W    | R/W       | R/W | R/W |  |

| Bit    | Bit Name  | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------|-----------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 to 5 | CCLR[2:0] | 000              | R/W | Counter Clear 0 to 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        |           |                  |     | These bits select the TCNT counter clearing source.<br>See tables 9.4 and 9.5 for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4, 3   | CKEG[1:0] | 00               | R/W | Clock Edge 0 and 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|        |           |                  |     | These bits select the input clock edge. When the input clock is counted using both edges, the input clock period is halved (e.g. $MP\phi/4$ both edges = $MP\phi/2$ rising edge). If phase counting mode is used on channels 1 and 2, this setting is ignored and the phase counting mode setting has priority. Internal clock edge selection is valid when the input clock is $MP\phi/4$ or slower. When $MP\phi/1$ , or the overflow/underflow of another channel is selected for the input clock, although values can be written, counter operation compiles with the initial value. |

|        |           |                  |     | 00: Count at rising edge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|        |           |                  |     | 01: Count at falling edge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| _      |           |                  |     | 1x: Count at both edges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2 to 0 | TPSC[2:0] | 000              | R/W | Time Prescaler 0 to 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        |           |                  |     | These bits select the TCNT counter clock. The clock source can be selected independently for each channel. See tables 9.6 to 9.10 for details.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

[Legend]

x: Don't care

#### Table 9.10 TPSC1 and TPSC0 (Channel 5)

| Channel | Bit 1<br>TPSC1 | Bit 0<br>TPSC0 | Description                      |

|---------|----------------|----------------|----------------------------------|

| 5       | 0              | 0              | Internal clock: counts on MP/1   |

|         |                | 1              | Internal clock: counts on MP     |

|         | 1              | 0              | Internal clock: counts on MP/16  |

|         |                | 1              | Internal clock: counts on MP6/64 |

Note: Bits 7 to 2 are reserved in channel 5. These bits are always read as 0. The write value should always be 0.

#### 9.3.2 Timer Mode Register (TMDR)

The TMDR registers are 8-bit readable/writable registers that are used to set the operating mode of each channel. The MTU2 has five TMDR registers, one each for channels 0 to 4. TMDR register settings should be changed only when TCNT operation is stopped.

| Bit:           | 7 | 6   | 5   | 4   | 3       | 2   | 1   | 0   |  |

|----------------|---|-----|-----|-----|---------|-----|-----|-----|--|

|                | - | BFE | BFB | BFA | MD[3:0] |     |     |     |  |

| Initial value: | 0 | 0   | 0   | 0   | 0       | 0   | 0   | 0   |  |

| R/W:           | - | R/W | R/W | R/W | R/W     | R/W | R/W | R/W |  |

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                             |

|-----|----------|------------------|-----|-------------------------------------------------------------------------------------------------------------------------|

| 7   |          | 0                | _   | Reserved                                                                                                                |

|     |          |                  |     | This bit is always read as 0. The write value should always be 0.                                                       |

| 6   | BFE      | 0                | R/W | Buffer Operation E                                                                                                      |

|     |          |                  |     | Specifies whether TGRE_0 and TGRF_0 are to operate<br>in the normal way or to be used together for buffer<br>operation. |

|     |          |                  |     | When TGRF is used as a buffer register, TGRF compare match is generated.                                                |

|     |          |                  |     | In channels 1 to 4, this bit is reserved. It is always read as 0 and the write value should always be 0.                |

|     |          |                  |     | 0: TGRE_0 and TGRF_0 operate normally                                                                                   |

|     |          |                  |     | 1: TGRE_0 and TGRF_0 used together for buffer<br>operation                                                              |

| Bit   | Bit Name      | Initial<br>Value | R/W       | Description                                                                                    |

|-------|---------------|------------------|-----------|------------------------------------------------------------------------------------------------|

| 2     | I2AE          | 0                | R/W       | Input Capture Enable                                                                           |

|       |               |                  |           | Specifies whether to include the TIOC2A pin in the TGRA_1 input capture conditions.            |

|       |               |                  |           | <ol> <li>Does not include the TIOC2A pin in the TGRA_1<br/>input capture conditions</li> </ol> |

|       |               |                  |           | 1: Includes the TIOC2A pin in the TGRA_1 input<br>capture conditions                           |

| 1     | I1BE          | 0                | R/W       | Input Capture Enable                                                                           |

|       |               |                  |           | Specifies whether to include the TIOC1B pin in the TGRB_2 input capture conditions.            |

|       |               |                  |           | 0: Does not include the TIOC1B pin in the TGRB_2<br>input capture conditions                   |

|       |               |                  |           | 1: Includes the TIOC1B pin in the TGRB_2 input<br>capture conditions                           |

| 0     | I1AE          | 0                | R/W       | Input Capture Enable                                                                           |

|       |               |                  |           | Specifies whether to include the TIOC1A pin in the TGRA_2 input capture conditions.            |

|       |               |                  |           | 0: Does not include the TIOC1A pin in the TGRA_2<br>input capture conditions                   |

|       |               |                  |           | 1: Includes the TIOC1A pin in the TGRA_2 input<br>capture conditions                           |

| Noto: | This function | ie euronarte     | d only by | the SH7125. In the SH7124, write value should always be                                        |

Note: This function is supported only by the SH7125. In the SH7124, write value should always be H'00.

Table 9.45 shows the TICCR setting and input capture input pins.

| Target Input Capture         | TICCR Setting                | Input Capture Input Pins |  |  |  |

|------------------------------|------------------------------|--------------------------|--|--|--|

| Input capture from TCNT_1 to | I2AE bit = 0 (initial value) | TIOC1A                   |  |  |  |

| TGRA_1                       | I2AE bit = 1                 | TIOC1A, TIOC2A           |  |  |  |

| Input capture from TCNT_1 to | I2BE bit = 0 (initial value) | TIOC1B                   |  |  |  |

| TGRB_1                       | I2BE bit = 1                 | TIOC1B, TIOC2B           |  |  |  |

| Input capture from TCNT_2 to | I1AE bit = 0 (initial value) | TIOC2A                   |  |  |  |

| TGRA_2                       | I1AE bit = 1                 | TIOC2A, TIOC1A           |  |  |  |

| Input capture from TCNT_2 to | I1BE bit = 0 (initial value) | TIOC2B                   |  |  |  |

| TGRB_2                       | I1BE bit = 1                 | TIOC2B, TIOC1B           |  |  |  |

## Table 9.45TICCR Setting and Input Capture Input Pins

**Example of Cascaded Operation Setting Procedure:** Figure 9.20 shows an example of the setting procedure for page ded operation

setting procedure for cascaded operation.

Figure 9.20 Cascaded Operation Setting Procedure

**Cascaded Operation Example (a):** Figure 9.21 illustrates the operation when TCNT\_2 overflow/underflow counting has been set for TCNT\_1 and phase counting mode has been designated for channel 2.

TCNT\_1 is incremented by TCNT\_2 overflow and decremented by TCNT\_2 underflow.

**Phase Counting Mode Application Example:** Figure 9.34 shows an example in which channel 1 is in phase counting mode, and channel 1 is coupled with channel 0 to input servo motor 2-phase encoder pulses in order to detect position or speed.

Channel 1 is set to phase counting mode 1, and the encoder pulse A-phase and B-phase are input to TCLKA and TCLKB.

Channel 0 operates with TCNT counter clearing by TGRC\_0 compare match; TGRA\_0 and TGRC\_0 are used for the compare match function and are set with the speed control period and position control period. TGRB\_0 is used for input capture, with TGRB\_0 and TGRD\_0 operating in buffer mode. The channel 1 counter input clock is designated as the TGRB\_0 input capture source, and the pulse widths of 2-phase encoder 4-multiplication pulses are detected.

TGRA\_1 and TGRB\_1 for channel 1 are designated for input capture, and channel 0 TGRA\_0 and TGRC\_0 compare matches are selected as the input capture source and store the up/down-counter values for the control periods.

This procedure enables the accurate detection of position and speed.

# 9.6 Operation Timing

## 9.6.1 Input/Output Timing

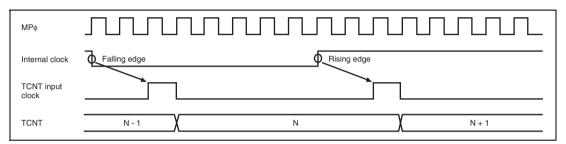

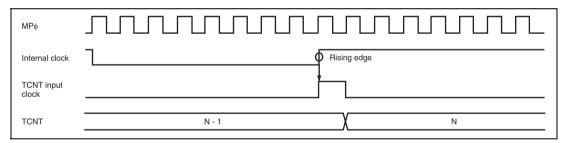

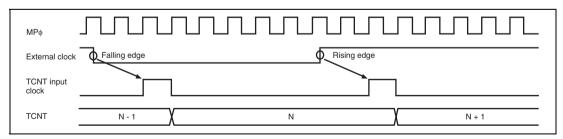

**TCNT Count Timing:** Figures 9.83 and 9.84 show TCNT count timing in internal clock operation, and figure 9.85 shows TCNT count timing in external clock operation (normal mode), and figure 9.86 shows TCNT count timing in external clock operation (phase counting mode).

Figure 9.83 Count Timing in Internal Clock Operation (Channels 0 to 4)

Figure 9.84 Count Timing in Internal Clock Operation (Channel 5)

Figure 9.85 Count Timing in External Clock Operation (Channels 0 to 4)

| Bit     | Bit Name | Initial<br>value | R/W     | Description                                                                                                                                                                                                              |

|---------|----------|------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13      | POE1F    | 0                | R/(W)*1 | POE1 Flag                                                                                                                                                                                                                |

|         |          |                  |         | This flag indicates that a high impedance request has been input to the $\overline{\text{POE1}}$ pin.                                                                                                                    |

|         |          |                  |         | [Clearing conditions]                                                                                                                                                                                                    |

|         |          |                  |         | <ul> <li>By writing 0 to POE1F after reading POE1F = 1<br/>(when the falling edge is selected by bits 3 and 2 in<br/>ICSR1)</li> </ul>                                                                                   |

|         |          |                  |         | <ul> <li>By writing 0 to POE1F after reading POE1F = 1 after<br/>a high level input to POE1 is sampled at Pφ/8, Pφ/16,<br/>or Pφ/128 clock (when low-level sampling is selected<br/>by bits 3 and 2 in ICSR1)</li> </ul> |

|         |          |                  |         | [Setting condition]                                                                                                                                                                                                      |

|         |          |                  |         | <ul> <li>When the input set by ICSR1 bits 3 and 2 occurs at<br/>the POE1 pin</li> </ul>                                                                                                                                  |

| 12      | POE0F    | 0                | R/(W)*1 | POE0 Flag                                                                                                                                                                                                                |

|         |          |                  |         | This flag indicates that a high impedance request has been input to the $\overline{\text{POE0}}$ pin.                                                                                                                    |

|         |          |                  |         | [Clearing conditions]                                                                                                                                                                                                    |

|         |          |                  |         | <ul> <li>By writing 0 to POE0F after reading POE0F = 1<br/>(when the falling edge is selected by bits 1 and 0 in<br/>ICSR1)</li> </ul>                                                                                   |

|         |          |                  |         | <ul> <li>By writing 0 to POE0F after reading POE0F = 1 after<br/>a high level input to POE0 is sampled at Pφ/8, Pφ/16,<br/>or Pφ/128 clock (when low-level sampling is selected<br/>by bits 1 and 0 in ICSR1)</li> </ul> |

|         |          |                  |         | [Setting condition]                                                                                                                                                                                                      |

|         |          |                  |         | <ul> <li>When the input set by ICSR1 bits 1 and 0 occurs at<br/>the POE0 pin</li> </ul>                                                                                                                                  |

| 11 to 9 | _        | All 0            | R       | Reserved                                                                                                                                                                                                                 |

|         |          |                  |         | These bits are always read as 0. The write value should always be 0.                                                                                                                                                     |

RENESAS

|          |   |     |   |       |   | Ρφ  | (MHz) | )   |   |     |   |     |  |

|----------|---|-----|---|-------|---|-----|-------|-----|---|-----|---|-----|--|

| Bit Rate |   | 10  |   | 12 14 |   |     | 16    |     |   | 18  |   | 20  |  |

| (bits/s) | n | Ν   | n | Ν     | n | Ν   | n     | Ν   | n | Ν   | n | Ν   |  |

| 250      | 3 | 155 | 3 | 187   | 3 | 218 | 3     | 249 |   |     |   |     |  |

| 500      | 3 | 77  | 3 | 93    | 3 | 108 | 3     | 124 | 3 | 140 | 3 | 155 |  |

| 1000     | 2 | 155 | 2 | 187   | 2 | 218 | 2     | 249 | 3 | 69  | 3 | 77  |  |

| 2500     | 1 | 249 | 2 | 74    | 2 | 87  | 2     | 99  | 2 | 112 | 2 | 124 |  |

| 5000     | 1 | 124 | 1 | 149   | 1 | 174 | 1     | 199 | 1 | 224 | 1 | 249 |  |

| 10000    | 0 | 249 | 1 | 74    | 1 | 87  | 1     | 99  | 1 | 112 | 1 | 124 |  |

| 25000    | 0 | 99  | 0 | 119   | 0 | 139 | 0     | 159 | 0 | 179 | 0 | 199 |  |

| 50000    | 0 | 49  | 0 | 59    | 0 | 69  | 0     | 79  | 0 | 89  | 0 | 99  |  |

| 100000   | 0 | 24  | 0 | 29    | 0 | 34  | 0     | 39  | 0 | 44  | 0 | 49  |  |

| 250000   | 0 | 9   | 0 | 11    | 0 | 13  | 0     | 15  | 0 | 17  | 0 | 19  |  |

| 500000   | 0 | 4   | 0 | 5     | 0 | 6   | 0     | 7   | 0 | 8   | 0 | 9   |  |

| 1000000  | — | _   | 0 | 2     | _ | _   | 0     | 3   |   | _   | 0 | 4   |  |

| 2500000  | 0 | 0*  |   | _     | _ | _   | _     | _   |   | _   | 0 | 1   |  |

| 5000000  |   |     |   | _     |   | _   | —     |     |   | _   | 0 | 0*  |  |

Table 12.7

Bit Rates and SCBRR Settings in Clock Synchronous Mode (1)

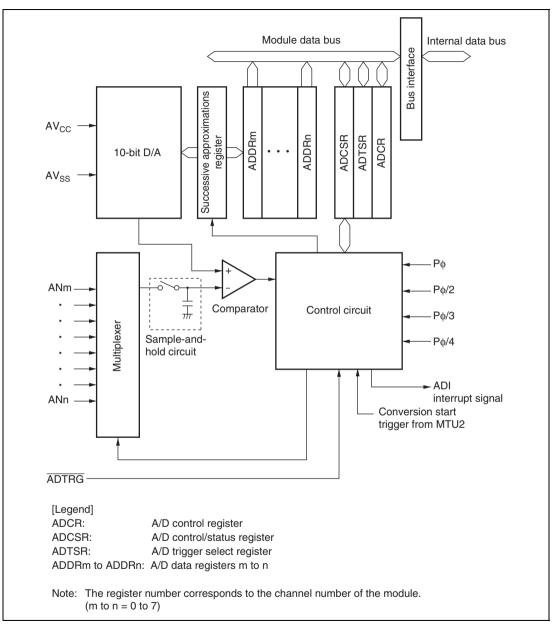

Figure 13.1 shows a block diagram of the A/D converter.

RENESAS

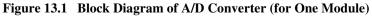

## 14.5.3 Conflict between Word-Write and Count-Up Processes of CMCNT

Even when the count-up occurs in the T2 cycle while writing to CMCNT in words, the writing has priority over the count-up. In this case, the count-up is not performed. Figure 14.6 shows the timing to write to CMCNT in words.

Figure 14.6 Conflict between Word-Write and Count-Up Processes of CMCNT

## 15.1.1 Port A I/O Register L (PAIORL)

PAIORL is a 16-bit readable/writable register that is used to set the pins on port A as inputs or outputs. Bits PA15IOR to PA0IOR correspond to pins PA15 to PA0 (names of multiplexed pins are here given as port names and pin numbers alone). PAIORL is enabled when the port A pins are functioning as general-purpose inputs/outputs (PA15 to PA0). In other states, PAIORL is disabled.

A given pin on port A will be an output pin if the corresponding bit in PAIORL is set to 1, and an input pin if the bit is cleared to 0.

However, bits 15 to 10, 5, and 2 of PAIORL are disabled in SH7124.

The initial value of PAIORL is H'0000.

| Bit: 15          | 14          | 13          | 12          | 11          | 10          | 9          | 8          | 7          | 6          | 5          | 4          | 3          | 2          | 1          | 0          |

|------------------|-------------|-------------|-------------|-------------|-------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|

| PA15<br>IOR      | PA14<br>IOR | PA13<br>IOR | PA12<br>IOR | PA11<br>IOR | PA10<br>IOR | PA9<br>IOR | PA8<br>IOR | PA7<br>IOR | PA6<br>IOR | PA5<br>IOR | PA4<br>IOR | PA3<br>IOR | PA2<br>IOR | PA1<br>IOR | PA0<br>IOR |

| Initial value: 0 | 0           | 0           | 0           | 0           | 0           | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          |

| R/W: R/W         | R/W         | R/W         | R/W         | R/W         | R/W         | R/W        | R/W        | R/W        | R/W        | R/W        | R/W        | R/W        | R/W        | R/W        | R/W        |

## 15.1.2 Port A Control Registers L1 to L4 (PACRL1 to PACRL4)

PACRL1 to PACRL4 are 16-bit readable/writable registers that are used to select the functions of the multiplexed pins on port A.

### SH7125:

• Port A Control Register L4 (PACRL4)

| Bit:           | 15 | 14          | 13          | 12          | 11 | 10          | 9           | 8           | 7 | 6           | 5           | 4           | 3 | 2           | 1           | 0           |

|----------------|----|-------------|-------------|-------------|----|-------------|-------------|-------------|---|-------------|-------------|-------------|---|-------------|-------------|-------------|

|                | -  | PA15<br>MD2 | PA15<br>MD1 | PA15<br>MD0 | -  | PA14<br>MD2 | PA14<br>MD1 | PA14<br>MD0 | - | PA13<br>MD2 | PA13<br>MD1 | PA13<br>MD0 | - | PA12<br>MD2 | PA12<br>MD1 | PA12<br>MD0 |

| Initial value: | 0  | 0           | 0           | 0           | 0  | 0           | 0           | 0           | 0 | 0           | 0           | 0           | 0 | 0           | 0           | 0           |

| R/W:           | R  | R/W         | R/W         | R/W         | R  | R/W         | R/W         | R/W         | R | R/W         | R/W         | R/W         | R | R/W         | R/W         | R/W         |

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                       |

|-----|----------|------------------|-----|-------------------------------------------------------------------|

| 15  |          | 0                | R   | Reserved                                                          |

|     |          |                  |     | This bit is always read as 0. The write value should always be 0. |

## 15.2 Usage Notes

- 1. In this LSI, the same function is available as a multiplexed function on multiple pins. This approach is intended to increase the number of selectable pin functions and to allow the easier design of boards. If two or more pins are specified for one function, however, there are two cautions shown below.

- When the pin function is input

Signals input to several pins are formed as one signal through OR or AND logic and the signal is transmitted into the LSI. Therefore, a signal that differs from the input signals may be transmitted to the LSI depending on the input signals in other pins that have the same functions. Table 15.6 shows the transmit forms of input functions allocated to several pins. When using one of the functions shown below in multiple pins, use it with care of signal polarity considering the transmit forms.

#### Table 15.6 Transmit Forms of Input Functions Allocated to Multiple Pins

| ОК Туре                                             | AND Type      |

|-----------------------------------------------------|---------------|

| SCK0 to SCK2, RXD0 to RXD2, POE0, POE1, POE3*, POE8 | IRQ0* to IRQ3 |

| Note: * This pin is supported only by the SH7       | /125.         |

- OR type: Signals input to several pins are formed as one signal through OR logic and the signal is transmitted into the LSI.

- AND type: Signals input to several pins are formed as one signal through AND logic and the signal is transmitted into the LSI.

- When the pin function is output

Each selected pin can output the same function.

- 2. When the port input is switched from a low level to the IRQ edge for the pins that are multiplexed with input/output and IRQ, the corresponding edge is detected.

- 3. Do not set functions other than those specified in tables 15.3 and 15.4. Otherwise, correct operation cannot be guaranteed.

### Table 17.4 (1) Register Configuration

| Register Name                               | Abbreviation* <sup>3</sup> | R/W                | Initial<br>Value                         | Address    | Access<br>Size |

|---------------------------------------------|----------------------------|--------------------|------------------------------------------|------------|----------------|

| Flash code control and status register      | FCCS                       | R, W* <sup>1</sup> | H'00* <sup>2</sup><br>H'80* <sup>2</sup> | H'FFFFCC00 | 8              |

| Flash program code select register          | FPCS                       | R/W                | H'00                                     | H'FFFFCC01 | 8              |

| Flash erase code select register            | FECS                       | R/W                | H'00                                     | H'FFFFCC02 | 8              |

| Flash key code register                     | FKEY                       | R/W                | H'00                                     | H'FFFFCC04 | 8              |

| Flash transfer destination address register | FTDAR                      | R/W                | H'00                                     | H'FFFFCC06 | 8              |

Notes: 1. The bits except the SCO bit are read-only bits. The SCO bit is a programming-only bit. (The value, which can be read is always 0.)

2. The initial value of the FWE bit is 0 when the FWE pin goes low. The initial value of the FWE bit is 1 when the FWE pin goes high.

3. All registers can be accessed only in bytes.

#### Table 17.4 (2) Parameter Configuration

| Name                                      | Abbreviation | R/W | Initial<br>Value | Address      | Access<br>Size |

|-------------------------------------------|--------------|-----|------------------|--------------|----------------|

| Download pass/fail result                 | DPFR         | R/W | Undefined        | On-chip RAM* | 8, 16, 32      |

| Flash pass/fail result                    | FPFR         | R/W | Undefined        | R0 of CPU    | 8, 16, 32      |

| Flash multipurpose address area           | FMPAR        | R/W | Undefined        | R5 of CPU    | 8, 16, 32      |

| Flash multipurpose data destination area  | FMPDR        | R/W | Undefined        | R4 of CPU    | 8, 16, 32      |

| Flash erase block select                  | FEBS         | R/W | Undefined        | R4 of CPU    | 8, 16, 32      |

| Flash program and erase frequency control | FPEFEQ       | R/W | Undefined        | R4 of CPU    | 8, 16, 32      |

| Flash user branch address set parameter   | FUBRA        | R/W | Undefined        | R5 of CPU    | 8, 16, 32      |

Note: \* One byte of the start address in the on-chip RAM area specified by FTDAR is valid.

## 21.2 DC Characteristics

Tables 21.2 and 21.3 list DC characteristics.

#### Table 21.2 DC Characteristics

Conditions:  $V_{cc} = AV_{cc} = 4.0 \text{ V to } 5.5 \text{ V}, V_{ss} = PLLV_{ss} = AV_{ss} = 0 \text{ V},$

$T_a = -20$  to +85°C (consumer specifications),

$T_a = -40$  to +85°C (industrial specifications)

| Item                                               |                                                                                                                                                                                   | Symbol                           | Min.                  | Тур. | Max.                  | Unit | Test<br>Conditions                  |

|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------|------|-----------------------|------|-------------------------------------|

| Input high-level<br>voltage (other<br>than Schmitt | RES, MRES, NMI,<br>FWE, MD1, ASEMDO,<br>EXTAL                                                                                                                                     | V <sub>IH</sub>                  | $V_{\text{cc}} - 0.7$ | —    | V <sub>cc</sub> + 0.3 | V    |                                     |

| trigger input<br>voltage)                          | Analog ports                                                                                                                                                                      | _                                | 2.2                   | _    | $AV_{cc} + 0.3$       | V    |                                     |

| voltago)                                           | Other input pins                                                                                                                                                                  | -                                | 2.2                   | _    | $V_{cc}$ + 0.3        | V    |                                     |

| Input low-level voltage (other than Schmitt        | RES, MRES, NMI,<br>FWE, MD1, ASEMDO,<br>EXTAL                                                                                                                                     | V <sub>IL</sub>                  | -0.3                  | _    | 0.5                   | V    |                                     |

| trigger input<br>voltage)                          | Other input pins                                                                                                                                                                  | -                                | -0.3                  | _    | 0.8                   | V    |                                     |

| Schmitt trigger                                    | IRQ3 to IRQ0,                                                                                                                                                                     | $V_{_{T+}}$                      | $V_{\text{cc}}-0.5$   | _    | —                     | V    |                                     |

| input voltage                                      | POE8, POE3, POE1,<br>POE0,                                                                                                                                                        | $V_{T-}$                         | _                     | _    | 1.0                   | V    |                                     |

|                                                    | TCLKA to TCLKD,<br>TIOC0A to TIOC0D,<br>TIOC1A, TIOC1B,<br>TIOC2A, TIOC2B,<br>TIOC3A to TIOC3D,<br>TIOC4A to TIOC4D,<br>TIC5U, TIC5V,<br>TIC5WS,<br>SCK0 to SCK3,<br>RXD0 to RXD3 | V <sub>T+</sub> -V <sub>T-</sub> | 0.4                   | _    | _                     | V    | V <sub>cc</sub> = 4.5 V to<br>5.5 V |

| Input leak<br>current                              | All input pins (except ASEMD0)                                                                                                                                                    | I <sub>in</sub>                  | _                     | —    | 1.0                   | μΑ   |                                     |

| Input pull-up<br>MOS current                       | ASEMDO, POE3                                                                                                                                                                      | -I <sub>pu</sub>                 | _                     | _    | 800                   | μΑ   | $V_{in} = 0 V$                      |

| Tri-state<br>leakage current<br>(OFF state)        | Ports A, B, E                                                                                                                                                                     | <sub>tsi</sub>                   | _                     | _    | 1.0                   | μΑ   |                                     |

#### Appendix

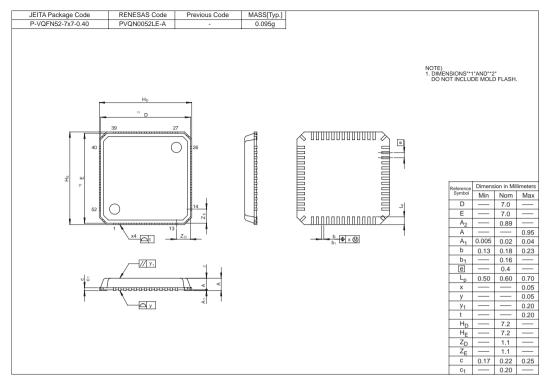

Figure C.5 VQFN-52