#### Details

E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | SH-2                                                                            |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 50MHz                                                                           |

| Connectivity               | SCI                                                                             |

| Peripherals                | POR, PWM, WDT                                                                   |

| Number of I/O              | 37                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                       |

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | External                                                                        |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN                                                                        |

| Supplier Device Package    | 64-VQFN (8.2x8.2)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df71251an50npv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The instruction code, operation, and execution cycles of the instructions are listed in the following tables, classified by type.

| Instruction                                                                                                                                                                                            | Instruction Code                                                                                                                              | Summary of<br>Operation                                                                                                                                                                                                                                                                                                                                              | Execution<br>Cycles | T Bit                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------------------------------------------------------------|

| Indicated by mnemonic.                                                                                                                                                                                 | Indicated in MSB $\leftrightarrow$ LSB order.                                                                                                 | Indicates summary of operation.                                                                                                                                                                                                                                                                                                                                      |                     | Value of T bit after<br>instruction is executed<br>Explanation of Symbols |

| Explanation of Symbols                                                                                                                                                                                 | Explanation of Symbols                                                                                                                        | Explanation of Symbols                                                                                                                                                                                                                                                                                                                                               |                     | —: No change                                                              |

| OP.Sz SRC, DEST<br>OP: Operation code<br>Sz: Size<br>SRC: Source<br>DEST: Destination<br>Rm: Source register<br>Rn: Destination<br>register<br>imm: Immediate data<br>disp: Displacement* <sup>2</sup> | mmmm: Source register<br>nnnn: Destination<br>register<br>0000: R0<br>0001: R1<br><br>1111: R15<br>iiii: Immediate data<br>dddd: Displacement | <ul> <li>→, ←: Transfer direction</li> <li>(xx): Memory operand</li> <li>M/Q/T: Flag bits in SR</li> <li>&amp;: Logical AND of each bit</li> <li> : Logical OR of each bit</li> <li>A: Exclusive logical OR of each bit</li> <li>→: Logical NOT of each bit</li> <li>&lt;<n: left="" li="" n-bit="" shift<=""> <li>&gt;&gt;n: n-bit right shift</li> </n:></li></ul> |                     |                                                                           |

Notes: 1. The table shows the minimum number of execution states. In practice, the number of instruction execution states will be increased in cases such as the following:

- When there is contention between an instruction fetch and a data access

- When the destination register of a load instruction (memory  $\rightarrow$  register) is also used by the following instruction

- Scaled (×1, ×2, or ×4) according to the instruction operand size, etc. For details, see SH-1/SH-2/SH-DSP Software Manual.

|               |               |               |               |                       | Description                    |

|---------------|---------------|---------------|---------------|-----------------------|--------------------------------|

| Bit 3<br>IOA3 | Bit 2<br>IOA2 | Bit 1<br>IOA1 | Bit 0<br>IOA0 | TGRA_3<br>Function    | TIOC3A Pin Function            |

| 0             | 0             | 0             | 0             | Output                | Output retained*               |

|               |               |               | 1             | compare<br>register   | Initial output is 0            |

|               |               |               |               | Tegister              | 0 output at compare match      |

|               |               | 1             | 0             | _                     | Initial output is 0            |

|               |               |               |               |                       | 1 output at compare match      |

|               |               |               | 1             | _                     | Initial output is 0            |

|               |               |               |               |                       | Toggle output at compare match |

|               | 1             | 0             | 0             | _                     | Output retained                |

|               |               |               | 1             | _                     | Initial output is 1            |

|               |               |               |               |                       | 0 output at compare match      |

|               |               | 1             | 0             | _                     | Initial output is 1            |

|               |               |               |               |                       | 1 output at compare match      |

|               |               |               | 1             | _                     | Initial output is 1            |

|               |               |               |               |                       | Toggle output at compare match |

| 1             | х             | 0             | 0             |                       | Input capture at rising edge   |

|               |               |               | 1             | <sup>–</sup> register | Input capture at falling edge  |

|               |               | 1             | х             | _                     | Input capture at both edges    |

| [Legend       | 4]            |               |               |                       |                                |

### Table 9.24 TIORH\_3 (Channel 3)

[Legend]

x: Don't care

Note: \* After power-on reset, 0 is output until TIOR is set.

| Bit | Bit Name | Initial<br>Value | R/W     | Description                                                                                                                                                                                                                                                |

|-----|----------|------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | TCFV     | 0                | R/(W)*1 | Overflow Flag                                                                                                                                                                                                                                              |

|     |          |                  |         | Status flag that indicates that TCNT overflow has occurred. Only 0 can be written, for flag clearing.                                                                                                                                                      |

|     |          |                  |         | [Setting condition]                                                                                                                                                                                                                                        |

|     |          |                  |         | <ul> <li>When the TCNT value overflows (changes from<br/>H'FFFF to H'0000)</li> </ul>                                                                                                                                                                      |

|     |          |                  |         | In channel 4, when the TCNT_4 value underflows<br>(changes from H'0001 to H'0000) in complementary<br>PWM mode, this flag is also set.                                                                                                                     |

|     |          |                  |         | [Clearing condition]                                                                                                                                                                                                                                       |

|     |          |                  |         | <ul> <li>When 0 is written to TCFV after reading TCFV =<br/>1*<sup>2</sup></li> </ul>                                                                                                                                                                      |

| 3   | TGFD     | 0                | R/(W)*1 | Input Capture/Output Compare Flag D                                                                                                                                                                                                                        |

|     |          |                  |         | Status flag that indicates the occurrence of TGRD input capture or compare match in channels 0, 3, and 4. Only 0 can be written, for flag clearing. In channels 1 and 2, bit 3 is reserved. It is always read as 0 and the write value should always be 0. |

|     |          |                  |         | [Setting conditions]                                                                                                                                                                                                                                       |

|     |          |                  |         | <ul> <li>When TCNT = TGRD and TGRD is functioning as<br/>output compare register</li> </ul>                                                                                                                                                                |

|     |          |                  |         | <ul> <li>When TCNT value is transferred to TGRD by input<br/>capture signal and TGRD is functioning as input<br/>capture register</li> </ul>                                                                                                               |

|     |          |                  |         | [Clearing condition]                                                                                                                                                                                                                                       |

|     |          |                  |         | <ul> <li>When 0 is written to TGFD after reading TGFD =<br/>1*<sup>2</sup></li> </ul>                                                                                                                                                                      |

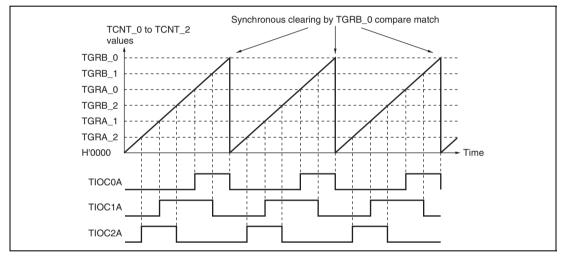

## Example of Synchronous Operation in SH7125:

Figure 9.13 shows an example of synchronous operation.

In this example, synchronous operation and PWM mode 1 have been designated for channels 0 to 2, TGRB\_0 compare match has been set as the channel 0 counter clearing source, and synchronous clearing has been set for the channel 1 and 2 counter clearing source.

Three-phase PWM waveforms are output from pins TIOC0A, TIOC1A, and TIOC2A. At this time, synchronous presetting, and synchronous clearing by TGRB\_0 compare match, are performed for channel 0 to 2 TCNT counters, and the data set in TGRB\_0 is used as the PWM cycle.

For details of PWM modes, see section 9.4.5, PWM Modes.

Figure 9.13 Example of Synchronous Operation

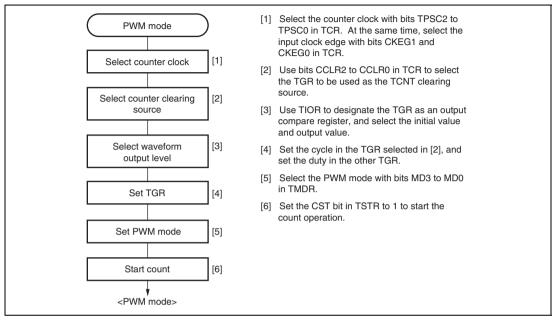

**Example of PWM Mode Setting Procedure:** Figure 9.25 shows an example of the PWM mode setting procedure.

Figure 9.25 Example of PWM Mode Setting Procedure

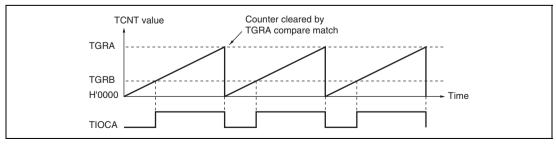

Examples of PWM Mode Operation: Figure 9.26 shows an example of PWM mode 1 operation.

In this example, TGRA compare match is set as the TCNT clearing source, 0 is set for the TGRA initial output value and output value, and 1 is set as the TGRB output value.

In this case, the value set in TGRA is used as the period, and the values set in the TGRB registers are used as the duty levels.

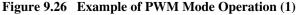

Figure 9.41 Example of Operation without Dead Time

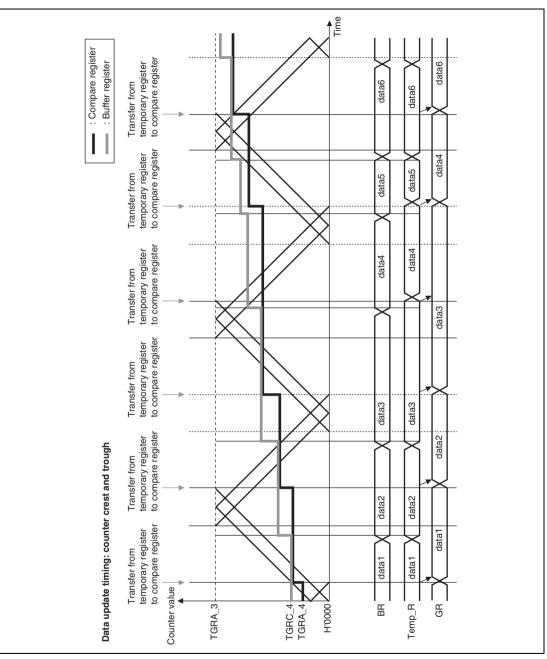

Figure 9.43 Example of Data Update in Complementary PWM Mode

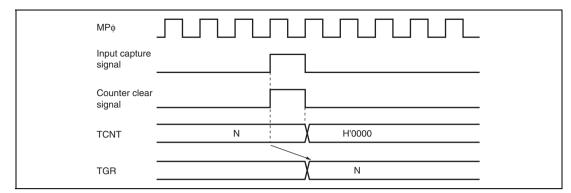

Figure 9.92 Counter Clear Timing (Input Capture)

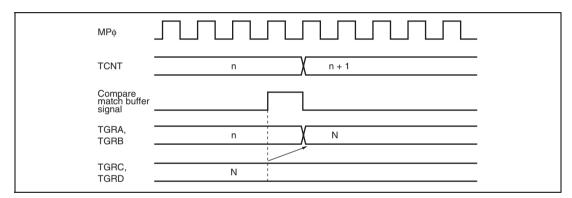

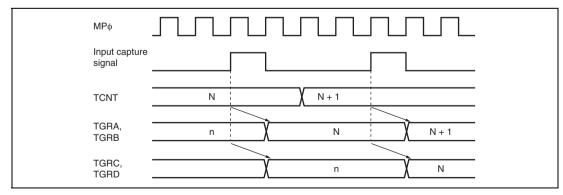

**Buffer Operation Timing:** Figures 9.93 to 9.95 show the timing in buffer operation.

Figure 9.93 Buffer Operation Timing (Compare Match)

Figure 9.94 Buffer Operation Timing (Input Capture)

# **10.3** Register Descriptions

The POE has the following registers. For details on register addresses and register states during each processing, refer to section 20, List of Registers.

### Table 10.3 Register Configuration

| Register Name                            | Abbrevia-<br>tion | R/W  | Initial Value | Address    | Access Size |

|------------------------------------------|-------------------|------|---------------|------------|-------------|

| negister Name                            | lion              | n/ W | Initial value | Audress    | ALLESS SIZE |

| Input level control/status<br>register 1 | ICSR1             | R/W  | H'0000        | H'FFFFD000 | 8, 16, 32   |

| Output level control/status register 1   | OCSR1             | R/W  | H'0000        | H'FFFFD002 | 8, 16       |

| Input level control/status register 3    | ICSR3             | R/W  | H'0000        | H'FFFFD008 | 8, 16, 32   |

| Software port output enable register     | SPOER             | R/W  | H'00          | H'FFFFD00A | 8           |

| Port output enable control register 1    | POECR1            | R/W  | H'00          | H'FFFFD00B | 8           |

| Port output enable control register 2    | POECR2            | R/W  | H'7700        | H'FFFFD00C | 8, 16       |

| • Port I       | B Co | ntrol I | Regist | er L2 | (PBC | RL2) |   |   |   |            |            |            |   |   |   |   |

|----------------|------|---------|--------|-------|------|------|---|---|---|------------|------------|------------|---|---|---|---|

| Bit:           | 15   | 14      | 13     | 12    | 11   | 10   | 9 | 8 | 7 | 6          | 5          | 4          | 3 | 2 | 1 | 0 |

|                | -    | -       | -      | -     | -    | -    | - | - | - | PB5<br>MD2 | PB5<br>MD1 | PB5<br>MD0 | - | - | - | - |

| Initial value: | 0    | 0       | 0      | 0     | 0    | 0    | 0 | 0 | 0 | 0          | 0          | 0          | 0 | 0 | 0 | 0 |

| R/W:           | R    | R       | R      | R     | R    | R    | R | R | R | R/W        | R/W        | R/W        | R | R | R | R |

|                |      |         |        |       |      |      |   |   |   |            |            |            |   |   |   |   |

| Bit     | Bit Name | Initial<br>Value | R/W | Description                                                          |

|---------|----------|------------------|-----|----------------------------------------------------------------------|

| 15 to 7 | _        | All 0            | R   | Reserved                                                             |

|         |          |                  |     | These bits are always read as 0. The write value should always be 0. |

| 6       | PB5MD2   | 0                | R/W | PB5 Mode                                                             |

| 5       | PB5MD1   | 0                | R/W | Select the function of the PB5/IRQ3/TIC5U pin.                       |

| 4       | PB5MD0   | 0                | R/W | 000: PB5 I/O (port)                                                  |

|         |          |                  |     | 001: IRQ3 input (INTC)                                               |

|         |          |                  |     | 011: TIC5U input (MTU2)                                              |

|         |          |                  |     | Other than above: Setting prohibited                                 |

| 3 to 0  | _        | All 0            | R   | Reserved                                                             |

|         |          |                  |     | These bits are always read as 0. The write value should always be 0. |

#### Port B Control Register L1 (PBCRL1) ٠

| Bit:           | 15 | 14         | 13         | 12         | 11 | 10 | 9 | 8 | 7 | 6          | 5          | 4          | 3 | 2 | 1 | 0 |

|----------------|----|------------|------------|------------|----|----|---|---|---|------------|------------|------------|---|---|---|---|

|                | -  | PB3<br>MD2 | PB3<br>MD1 | PB3<br>MD0 | -  | -  | - | - | - | PB1<br>MD2 | PB1<br>MD1 | PB1<br>MD0 | - | - | - | - |

| Initial value: | 0  | 0          | 0          | 0          | 0  | 0  | 0 | 0 | 0 | 0          | 0          | 0          | 0 | 0 | 0 | 0 |

| R/W:           | R  | R/W        | R/W        | R/W        | R  | R  | R | R | R | R/W        | R/W        | R/W        | R | R | R | R |

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                       |

|-----|----------|------------------|-----|-------------------------------------------------------------------|

| 15  | _        | 0                | R   | Reserved                                                          |

|     |          |                  |     | This bit is always read as 0. The write value should always be 0. |

### • PBPRL (SH7124)

| Bit:           | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5         | 4 | 3         | 2 | 1         | 0 |

|----------------|----|----|----|----|----|----|---|---|---|---|-----------|---|-----------|---|-----------|---|

|                | -  | -  | -  | -  | -  | -  | - | - | - | - | PB5<br>PR | - | PB3<br>PR | - | PB1<br>PR | - |

| Initial value: | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | *         | 0 | *         | 0 | *         | 0 |

| R/W:           | R  | R  | R  | R  | R  | R  | R | R | R | R | R         | R | R         | R | R         | R |

| <b>D</b> |          | Initial   | <b>D</b> /14/ |                                                                                          |

|----------|----------|-----------|---------------|------------------------------------------------------------------------------------------|

| Bit      | Bit Name | Value     | R/W           | Description                                                                              |

| 15 to 6  | _        | All 0     | R             | Reserved                                                                                 |

|          |          |           |               | These bits are always read as 0. The write value should always be 0.                     |

| 5        | PB5PR    | Pin state | R             | The pin state is returned regardless of the PFC setting.<br>This bit cannot be modified. |

| 4        | —        | 0         | R             | Reserved                                                                                 |

|          |          |           |               | This bit is always read as 0. The write value should always be 0.                        |

| 3        | PB3PR    | Pin state | R             | The pin state is returned regardless of the PFC setting.<br>This bit cannot be modified. |

| 2        | _        | 0         | R             | Reserved                                                                                 |

|          |          |           |               | This bit is always read as 0. The write value should always be 0.                        |

| 1        | PB1PR    | Pin state | R             | The pin state is returned regardless of the PFC setting.<br>This bit cannot be modified. |

| 0        |          | 0         | R             | Reserved                                                                                 |

|          |          |           |               | This bit is always read as 0. The write value should always be 0.                        |

| Bit     | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                             |

|---------|----------|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31 to 8 | _        | Undefined        | R/W | Unused                                                                                                                                                                                                  |

|         |          |                  |     | Return 0.                                                                                                                                                                                               |

| 7 to 0  | EBS[7:0] | Undefined        | R/W | 128-kbyte flash memory                                                                                                                                                                                  |

|         |          |                  |     | Set the erase-block number in the range from 0 to 9.<br>0 corresponds to the EB0 block and 9 corresponds<br>to the EB9 block. An error occurs when a number<br>other than 0 to 9 (H'00 to H'09) is set. |

|         |          |                  |     | 64-kbyte flash memory                                                                                                                                                                                   |

|         |          |                  |     | Set the erase-block number in the range from 0 to 8.<br>0 corresponds to the EB0 block and 8 corresponds<br>to the EB8 block. An error occurs when a number<br>other than 0 to 8 (H'00 to H'08) is set. |

(4.2) Flash pass/fail result parameter (FPFR: general register R0 of CPU)

This parameter returns the value of the erasing processing result.

| Bit           | 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|               | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   |

| Initial value |     | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   |

| R/W           | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Bit           | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|               | -   | -   | -   | -   | -   | -   | -   | -   | -   | MD  | EE  | FK  | EB  | -   | -   | SF  |

| Initial value | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   |

| R/W           | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

|               |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Bit     | Bit Name | Initial<br>Value | R/W | Description |

|---------|----------|------------------|-----|-------------|

| 31 to 7 | _        | Undefined        | R/W | Unused      |

|         |          |                  |     | Return 0.   |

#### (7) Inquiry on user MATs

In response to the inquiry on user MATs, the boot program returns the number of user MAT areas and their addresses.

Command

H'25

- Command H'25 (1 byte): Inquiry on user MAT information

| Response                  | H'35 | Size | No. of areas |  |                          |

|---------------------------|------|------|--------------|--|--------------------------|

| First address of the area |      |      |              |  | Last address of the area |

|                           |      |      |              |  |                          |

|                           | SUM  |      |              |  |                          |

- Response H'35 (1 byte): Response to the inquiry on user MATs

- Size (1 byte): The total length of the number of areas and first and last address fields.

- Number of areas (1 byte): The number of user MAT areas.

H'01 is returned if the entire user MAT area is continuous.

- First address of the area (4 bytes)

- Last address of the area (4 bytes)

- As many pairs of first and last address field are included as there are areas.

- SUM (1 byte): Checksum

#### (8) Inquiry on erasure blocks

In response to the inquiry on erasure blocks, the boot program returns the number of erasure blocks in the user MAT and the addresses where each block starts and ends.

| Command | H'26 |  |

|---------|------|--|

|---------|------|--|

- Command H'26 (1 byte): Inquiry on erasure blocks

| Response H'36 Size No.     |     | No. of blocks |  |                           |

|----------------------------|-----|---------------|--|---------------------------|

| First address of the block |     |               |  | Last address of the block |

|                            |     |               |  |                           |

|                            | SUM |               |  |                           |

# Section 19 Power-Down Modes

This LSI supports the following power-down modes: sleep mode, software standby mode, and module standby mode.

# **19.1** Features

• Supports sleep mode, software standby mode, and module standby mode.

### 19.1.1 Types of Power-Down Modes

This LSI has the following power-down modes.

- Sleep mode

- Software standby mode

- Module standby mode

Table 19.1 shows the methods to make a transition from the program execution state, as well as the CPU and peripheral module states in each mode and the procedures for canceling each mode.

| Register     | Bit        | Bit        | Bit        | Bit        | Bit        | Bit        | Bit       | Bit       |        |

|--------------|------------|------------|------------|------------|------------|------------|-----------|-----------|--------|

| Abbreviation | 31/23/15/7 | 30/22/14/6 | 29/21/13/5 | 28/20/12/4 | 27/19/11/3 | 26/18/10/2 | 25/17/9/1 | 24/16/8/0 | Module |

| TIER_1       | TTGE       | —          | TCIEU      | TCIEV      | —          | —          | TGIEB     | TGIEA     | MTU2   |

| TSR_1        | TCFD       | —          | TCFU       | TCFV       | —          | —          | TGFB      | TGFA      |        |

| TCNT_1       |            |            |            |            |            |            |           |           |        |

|              |            |            |            |            |            |            |           |           |        |

| TGRA_1       |            |            |            |            |            |            |           |           |        |

|              |            |            |            |            |            |            |           |           | -      |

| TGRB_1       |            |            |            |            |            |            |           |           |        |

|              |            |            |            |            |            |            |           |           |        |

| TICCR        | —          | —          | —          | —          | I2BE       | I2AE       | I1BE      | I1AE      |        |

| TCR_2        | —          | CCL        | R[1:0]     | CKE        | G[1:0]     |            | TPSC[2:0] |           |        |

| TMDR_2       | —          | —          | —          | —          |            | MD         | [3:0]     |           |        |

| TIOR_2       |            | IOB        | [3:0]      | 1          |            | IOA        | [3:0]     | 1         |        |

| TIER_2       | TTGE       | —          | TCIEU      | TCIEV      | —          | —          | TGIEB     | TGIEA     |        |

| TSR_2        | TCFD       | —          | TCFU       | TCFV       | —          | —          | TGFB      | TGFA      |        |

| TCNT_2       |            |            |            |            |            |            |           |           |        |

|              |            |            |            |            |            |            |           |           |        |

| TGRA_2       |            |            |            |            |            |            |           |           |        |

|              |            |            |            |            |            |            |           |           |        |

| TGRB_2       |            |            |            |            |            |            |           |           | _      |

|              |            |            |            |            |            |            |           |           |        |

| TCNTU_5      |            |            |            |            |            |            |           |           |        |

|              |            |            |            |            |            |            |           |           |        |

| TGRU_5       |            |            |            |            |            |            |           |           |        |

|              |            |            |            |            |            |            |           |           |        |

| TCRU_5       | —          | —          | —          | —          | —          | —          | TPS       | C[1:0]    |        |

| TIORU_5      | —          | _          | _          |            | 1          | IOC[4:0]   | 1         | 1         | -      |

| TCNTV_5      |            |            |            |            |            |            |           |           |        |

|              |            |            |            |            |            |            |           |           |        |

| TGRV_5       |            |            |            |            |            |            |           |           |        |

|              |            |            |            |            |            |            |           |           |        |

| TCRV_5       |            |            | —          | —          |            | —          | TPS       | C[1:0]    |        |

| Register     | Bit         |                 |  |

|--------------|------------|------------|------------|------------|------------|------------|------------|-------------|-----------------|--|

| Abbreviation | 31/23/15/7 | 30/22/14/6 | 29/21/13/5 | 28/20/12/4 | 27/19/11/3 | 26/18/10/2 | 25/17/9/1  | 24/16/8/0   | Module          |  |

| ADCSR_1      | ADF        | ADIE       | —          | —          | TRGE       | —          | CONADF     | STC         | A/D (Channel 1) |  |

|              | CKS        | L[1:0]     | ADN        | /[1:0]     | ADCS       | CH[2:0]    |            |             |                 |  |

| ADCR_1       | —          | _          | ADST       | _          | _          | _          | _          | —           |                 |  |

|              | —          | _          | _          | _          | _          | _          | _          | —           |                 |  |

| FCCS         | FWE        | _          | _          | FLER       | _          | _          | —          | SCO         | FLASH           |  |

| FPCS         | —          | _          | _          | _          | _          | _          | _          | PPVS        | _               |  |

| FECS         | —          | _          | _          | _          | _          | —          | _          | EPVB        |                 |  |

| FKEY         |            |            |            | K          | 7:0]       |            |            |             |                 |  |

| FTDAR        | TDER       |            |            |            | TDA[6:0]   |            |            |             |                 |  |

| CMSTR        | —          | —          | —          | —          | —          | —          | —          | —           | СМТ             |  |

|              | —          | _          | _          | _          | _          | —          | STR1       | STR0        |                 |  |

| CMCSR_0      | —          | _          | _          | _          | _          | _          | —          | —           |                 |  |

|              | CMF        | CMIE       | _          | _          | _          | _          | CKS[1:0]   |             |                 |  |

| CMCNT_0      |            |            |            |            |            |            |            |             |                 |  |

|              |            |            |            |            |            |            |            |             |                 |  |

| CMCOR_0      |            |            |            |            |            |            |            |             |                 |  |

|              |            |            |            |            |            |            |            |             |                 |  |

| CMCSR_1      | _          | _          | _          | _          | _          | _          | —          | _           |                 |  |

|              | CMF        | CMIE       | _          | _          | _          | _          | CKS        | S[1:0]      |                 |  |

| CMCNT_1      |            |            |            |            |            |            |            |             |                 |  |

|              |            |            |            |            |            |            |            |             |                 |  |

| CMCOR_1      |            |            |            |            |            |            |            |             |                 |  |

|              |            |            |            |            |            |            |            |             |                 |  |

| ICSR1        | POE3F      | _          | POE1F      | POE0F      | _          | _          | _          | PIE1        | POE             |  |

|              | POE3       | M[1:0]     | _          | _          | POE1       | IM[1:0]    | POE        | DM[1:0]     |                 |  |

| OCSR1        | OSF1       | _          | _          | _          | _          |            | OCE1       | OIE1        |                 |  |

|              | _          | _          | _          | _          | _          | _          | _          | _           |                 |  |

| ICSR3        | _          | _          | _          | POE8F      | _          | _          | POE8E      | PIE3        |                 |  |

|              | _          | _          | _          | _          | _          | _          | POE        | 3M[1:0]     |                 |  |

| SPOER        | _          | _          | _          | _          | _          | _          | MTU2CH0HIZ | MTU2CH34HIZ |                 |  |

| Item                   |                                     | Symbol          | Min.                  | Тур. | Max. | Unit | Test Conditions                                                               |

|------------------------|-------------------------------------|-----------------|-----------------------|------|------|------|-------------------------------------------------------------------------------|

| Output high<br>voltage | TIOC3B, TIOC3D, TIOC4A<br>to TIOC4D | $V_{\rm OH}$    | $V_{\rm cc} - 0.8$    | _    | _    | V    | $I_{_{OH}} = -5 \text{ mA},$<br>$V_{_{CC}} = 4.5 \text{ V to } 5.5 \text{ V}$ |

|                        | WDTOVF                              | -               | $V_{\rm cc} - 0.5$    | _    |      | V    | I <sub>oH</sub> = -100 μA                                                     |

|                        | All other output pins               | -               | $V_{\text{cc}} - 0.5$ | _    | _    | V    | I <sub>oH</sub> = -200 μA                                                     |

|                        |                                     |                 | $V_{\rm cc} - 1.0$    | _    |      | V    | I <sub>он</sub> = —1 mA                                                       |

|                        |                                     |                 | V <sub>cc</sub> - 1.5 | _    | _    | V    | I <sub>он</sub> = -2 mA<br>(reference values)                                 |

| Output low voltage     | TIOC3B, TIOC3D, TIOC4A<br>to TIOC4D | $V_{_{OL}}$     | _                     |      | 1.0  | V    | $I_{oL} = 15 \text{ mA},$<br>$V_{cc} = 4.5 \text{ V to 5.5 V}$                |

|                        |                                     |                 | _                     | _    | 0.6  | V    | $I_{oL} = 10 \text{ mA},$<br>$V_{cc} = 4.5 \text{ V to 5.5 V}$                |

|                        |                                     |                 | _                     | _    | 0.44 | V    | $I_{_{OL}} = 8 \text{ mA},$<br>$V_{_{CC}} = 4.5 \text{ V to } 5.5 \text{ V}$  |

|                        | All other output pins               | -               |                       | _    | 0.4  | V    | I <sub>oL</sub> = 1.6 mA                                                      |

| Input<br>capacitance   | All input pins                      | C <sub>in</sub> | _                     | _    | 20   | pF   | $V_{in} = 0 V$<br>f = 1 MHz<br>Ta = 25°C                                      |

| Supply current         | Normal operation                    | I <sub>cc</sub> | _                     | 52   | 70   | mA   | lφ = 50 MHz<br>(SH7125, SH7124)                                               |

|                        |                                     |                 |                       | 35   | 50   | mA   | lφ = 50 MHz<br>(SH71251A, SH71241A,<br>SH71250A, SH71240A)                    |

|                        | Sleep                               | _               | _                     | 33   | 50   | mA   | lφ = 50 MHz<br>(SH7125, SH7124)                                               |

|                        |                                     |                 |                       | 22   | 30   | mA   | lφ = 50 MHz<br>(SH71251A, SH71241A,<br>SH71250A, SH71240A)                    |

|                        | Software standby                    | -               | _                     | _    | 5    | mA   | $T_{a} \leq 50^{\circ}C$                                                      |

|                        |                                     |                 | _                     | _    | 15   | mA   | $50^{\circ}C < T_{a}$                                                         |

| Analog power           | During A/D conversion               | $AI_{cc}$       | _                     | 3    | 5    | mA   | The value per module                                                          |

| supply current         | Waiting for A/D conversion          | -               | _                     | _    | 2    | mA   | The value per module                                                          |

|                        | Standby                             | -               |                       | _    | 15   | μA   |                                                                               |

[Operating Precautions]

1. When the A/D converter is not used, do not leave the  $\mathrm{AV}_{\mathrm{cc}}$  and  $\mathrm{AV}_{\mathrm{ss}}$  pins open.

RENESAS

2. The supply current was measured when V  $_{\rm IH}$  (Min.) = V  $_{\rm cc}$  - 0.5 V, V  $_{\rm IL}$  (Max.) = 0.5 V, with all output pins unloaded.

#### Table 21.3 Permitted Output Current Values

Conditions:  $V_{cc} = AV_{cc} = 4.0 \text{ V to } 5.5 \text{ V}, V_{ss} = PLLV_{ss} = AV_{ss} = 0 \text{ V},$   $T_a = -20 \text{ to } +85^{\circ}\text{C} \text{ (consumer specifications)},$  $T_a = -40 \text{ to } +85^{\circ}\text{C} \text{ (industrial specifications)}$

| Item                                               | Symbol                         | Min. | Тур. | Max. | Unit |

|----------------------------------------------------|--------------------------------|------|------|------|------|

| Permissible current in low-level output (per pin   | ) I <sub>ol</sub>              |      |      | 2.0* | mA   |

| Permissible current in low-level output (total)    | $\Sigma \mid_{OL}$             |      |      | 80   | mA   |

| Permissible current in high-level output (per pin) | — <b>І</b> <sub>он</sub>       | —    |      | 2.0* | mA   |

| Permissible current in high-level output (total)   | $\Sigma - \mathbf{I}_{\rm OH}$ | _    |      | 25   | mA   |

[Operating Precautions]

To assure LSI reliability, do not exceed the output values listed in table 21.3.

Note: \*  $I_{_{OL}} = 15 \text{ mA} (Max.)/-I_{_{OH}} = 5 \text{ mA} (Max.)$  for pins PE9 and PE11 to PE15. However, at least three pins are permitted to have simultaneously  $I_{_{OL}}/-I_{_{OH}} > 2.0 \text{ mA}$  among these pins.

# 21.3 AC Characteristics

Signals input to this LSI are basically handled as signals in synchronization with a clock. The setup and hold times for input pins must be followed.

#### Table 21.4 Maximum Operating Frequency

Conditions:  $V_{cc} = AV_{cc} = 4.0 \text{ V}$  to 5.5 V,  $V_{ss} = PLLV_{ss} = AV_{ss} = 0 \text{ V}$ ,  $T_a = -20 \text{ to } +85^{\circ}\text{C}$  (consumer specifications),  $T_a = -40 \text{ to } +85^{\circ}\text{C}$  (industrial specifications)

| Item      |                               | Symbol | Min. | Тур. | Max. | Unit | Remarks |

|-----------|-------------------------------|--------|------|------|------|------|---------|

| Operating | CPU (Iø)                      | f      | 10   | _    | 50   | MHz  |         |

| frequency | Peripheral module (P $\phi$ ) |        | 10   | _    | 40   |      |         |

| Item                                                           | Page | Revi                  | sion (Se                               | e ma                            | nuar                     | for Details)                                                                                                                                                                                                                                                                                                                              |

|----------------------------------------------------------------|------|-----------------------|----------------------------------------|---------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15.1.2 Port A Control Registers<br>L1 to L4 (PACRL1 to PACRL4) | 529  | Table                 | e amend                                |                                 |                          |                                                                                                                                                                                                                                                                                                                                           |

| <ul> <li>Port A Control Register L1<br/>(PACRL1)</li> </ul>    |      | Bit<br>14<br>13<br>12 | Bit Name<br>PA3MD2<br>PA3MD1<br>PA3MD0 | Initial<br>Value<br>0<br>0<br>0 | R/W<br>R/W<br>R/W        | Description           PA3 Mode           Select the function of the PA3/IRQ1/RXD1/TRST pin.           When the E10A <sup>®</sup> is in use (ASEMD0 = low), function is fixed to TRST input.           000: PA3 I/O (port)           001: RXD1 input (SCI)           111: IRQ1 input (INTC)           Other than above: Setting prohibited |

|                                                                | 530  | Note<br>Note          | (5                                     | SH712                           | 51A a                    | t be used on the 32 Kbyte<br>and SH71241A) and 16 Kbyte<br>and SH71240A) versions.                                                                                                                                                                                                                                                        |

| Port A Control Register L3     (PACRL3)                        | 531  | Table                 |                                        |                                 |                          |                                                                                                                                                                                                                                                                                                                                           |

|                                                                |      | Bit<br>6<br>5<br>4    | Bit Name<br>PA9MD2<br>PA9MD1<br>PA9MD0 | Value<br>0<br>0<br>0            | R/W<br>R/W<br>R/W<br>R/W | Description PA9 Mode Select the function of the PA9/TCLKD/TXD2/TD0/POE8 pin. When the E10A* is in use (ASEMID0 = low), function is fixed to TD0 output. 000: PA9 I/O (port) 001: TCLKD input (MTU2) 110: TXD2 output (SCI) 111: POE8 input (POE) Other than above: Setting prohibited                                                     |

|                                                                | 532  | Table                 | e amend                                |                                 |                          |                                                                                                                                                                                                                                                                                                                                           |

|                                                                |      | Bit<br>2<br>1<br>0    | Bit Name<br>PA8MD2<br>PA8MD1<br>PA8MD0 | Initial<br>Value<br>0<br>0<br>0 | R/W<br>R/W<br>R/W        | Description           PA8 Mode           Select the function of the PA8/TCLKC/RXD2/TDI pin.           When the E10A <sup>®</sup> is in use (ASEMD0 = low), function is fixed to TDI input.           000: PA8 I/O (port)           001: TCLKC input (MTU2)           110: RXD2 input (SCI)           Other than above: Setting prohibited |

|                                                                |      | Note                  |                                        |                                 |                          |                                                                                                                                                                                                                                                                                                                                           |

|                                                                |      | Note                  | (5                                     | SH712                           | 51A a                    | t be used on the 32 Kbyte<br>and SH71241A) and 16 Kbyte<br>and SH71240A) versions.                                                                                                                                                                                                                                                        |

#### Item

| nem                            | i ugo | nevision (see Manual for Details)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|--------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 16.1 Port A                    | 554   | Figure amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| Figure 16.1 Port A (SH7125)    |       | PA15 (I/O)/TXD1 (autput)           PA14 (UO)/RXD1 (input)           PA14 (UO)/RXD1 (input)           PA14 (UO)/RXD1 (input)           PA15 (UO)/SCK1 (UO)           PA15 (UO)/SCK0 (UO)           PA11 (UO)/TXD0 (autput)/ADTRG (input)           PA11 (UO)/TXD0 (autput)/ADTRG (input)           PA11 (UO)/TXD0 (autput)/ADTRG (input)           PA11 (UO)/TXD1 (input)/TXD2 (autput)/TD0*(input)           PA11 (UO)/TXD1 (input)/TXD1 (autput)/TD0*(input)           PA8 (UO)/TCLK6 (input)/SCK2 (INO/TCK* (input)           PA8 (UO)/TCLK6 (input)/SCK1 (IOO)           PA4 (UO)/RD2 (input)/XD1 (autput)/TBS* (input)           PA8 (UO)/TCLK6 (input)/TXD1 (autput)/TBS* (input)           PA8 (UO)/FDCX (input)/XD1 (autput)/TBS* (input)           PA8 (UO)/FDCX (input)/XD2 (autput) |  |  |  |  |  |

| Figure 16.2 Port A (SH7124)    | 554   | Note:         The TDO. TDI. TCK. TMS, and TBST pins are not supported on the 32 Kbyte (SH71251A and SH71241A) and<br>16 Kbyte (SH71250A and SH71240A) versions.           Figure amended         PA6 (I/O)/TCLKD (input)/TXD2 (output)/TDO" (output)/POE8 (input)           PA8 (I/O)/TCLKD (input)/TXD2 (output)/TDO" (output)/POE8 (input)         PA8 (I/O)/TCLKD (input)/TXD2 (output)/TDO" (output)/POE8 (input)           Port A         PA8 (I/O)/TCLKA (input)         PA8 (I/O)/TCLKA (input)           PA1 (I/O)/TCLKA (input)         PA8 (I/O)/TCLKA (input)           PA1 (I/O)/TCLKB (input)/TXD1 (output)/TKST* (input)         PA8 (I/O)/TCLKA (input)           PA1 (I/O)/FOEF (input)/TXD1 (output)/TKST* (input)         PA8 (I/O)/FOEF (input)/TXD1 (input)/TKST* (input)                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 16.5 Usage Notes               | 577   | PA0 (I/O)FOE5 (mput)/RXD0 (mput)  Note: * The TDO, TDI, TCK, TMS, and TRST pins are not supported on the 32 Kbyte (SH71251A and SH71241A) and 16 Kbyte (SH71250A and SH71240A) versions.  Newly added                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| 16.5.1 Handling of Unused Pins |       | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 17. Flash Memory (ROM)         | 579   | Description amended<br>This LSI has 128-Kbyte, 64-Kbyte, 32-Kbyte, or 16-<br>Kbyte on-chip flash memory. The flash memory has th<br>following features.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

REJ09B0243-0500

# Page Revision (See Manual for Details)

Item