#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betuils                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | TriCore™                                                                         |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 100MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, FIFO, I <sup>2</sup> C, IrDA, SPI, UART/USART, USB              |

| Peripherals                | DMA, POR, PWM, WDT                                                               |

| Number of I/O              | 72                                                                               |

| Program Memory Size        | -                                                                                |

| Program Memory Type        | ROMIess                                                                          |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 144К х 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.43V ~ 1.58V                                                                    |

| Data Converters            | -                                                                                |

| Oscillator Type            | External                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 208-LBGA                                                                         |

| Supplier Device Package    | P-LBGA-208-2                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/tc1130l100ebgbbfxuma1 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Edition 2005-02 Published by Infineon Technologies AG, St.-Martin-Strasse 53, 81669 München, Germany © Infineon Technologies AG 2005. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as a guarantee of characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

## TC1130

#### Advance Information

#### **General Device Information**

## 2.3 Pin Configuration

|         | Α            | В     | С     | D                | E               | F                                                               | G               | н                | J                | к               | L               | М                | N                | Р                       | R               | т             |    |

|---------|--------------|-------|-------|------------------|-----------------|-----------------------------------------------------------------|-----------------|------------------|------------------|-----------------|-----------------|------------------|------------------|-------------------------|-----------------|---------------|----|

| 16      | Reser<br>ved | P3.10 | P3.11 | P3.12            | P2.15           | P2.14                                                           | P2.11           | P2.9             | P2.8             | P2.7            | VDDOSC          | XTAL1            | XTAL2            | V <sub>DD</sub><br>OSC3 | V <sub>SS</sub> | Reser<br>ved  | 16 |

| 15      | P3.0         | P3.1  | P3.8  | P3.2             | P3.3            | P3.6                                                            | P3.5            | P3.9             | P3.15            | P2.12           | V <sub>ss</sub> | F0.3             | P2.4             | F0.1                    | F0.9            | D-            | 15 |

| 14      | P1.9         | P1.10 | P1.11 | P1.14            | P1.13           | P1.15                                                           | P3.4            | P3.7             | P3.14            | P2.13           | HW<br>CFG1      | HW<br>CFG0       | P2.5             | P2.3                    | F0.10           | D+            | 14 |

| 13      | P1.8         | P1.7  | P1.5  | V <sub>DDP</sub> | V <sub>SS</sub> | P1.12                                                           | V <sub>DD</sub> | V <sub>ss</sub>  | V <sub>DDP</sub> | P3.13           | P2.10           | V <sub>SS</sub>  | V <sub>DDP</sub> | P2.2                    | F0.8            | TDI           | 13 |

| 12      |              |       |       |                  |                 |                                                                 |                 |                  |                  |                 | n               | P2.6             | P2.0             | P0.5                    | так             | 12            |    |

| 11      | BAA          | ADV   | P1.4  | P1.0             |                 | С                                                               | onfig<br>f      |                  | ion (t<br>C113   |                 | iew)            |                  | P0.0             | P2.1                    | P0.4            | TRST          | 11 |

| 10      | A17          | A18   | A19   | A20              |                 |                                                                 | V <sub>DD</sub> | V <sub>SS</sub>  | V <sub>SS</sub>  | V <sub>DD</sub> |                 |                  | P0.7             | P0.2                    | P0.6            | πю            | 10 |

| 9       | A16          | WAIT  | 3     | <u>C30</u>       |                 |                                                                 | V <sub>DD</sub> | V <sub>SS</sub>  | V <sub>SS</sub>  | V <sub>DD</sub> |                 |                  | P0.11            | P0.12                   | P4.1            | TMS           | 9  |

| 8       | A15          | cs    | AD0   | ଟ୍ଟ              |                 |                                                                 | V <sub>DD</sub> | V <sub>SS</sub>  | V <sub>SS</sub>  | V <sub>DD</sub> |                 |                  | P0.14            | P0.13                   | P4.0            | TRCLK         | 8  |

| 7       | BC3          | BC2   | AD1   | AD 16            |                 | V <sub>DD</sub> V <sub>SS</sub> V <sub>SS</sub> V <sub>DD</sub> |                 |                  |                  |                 |                 |                  |                  | P0.15                   | P4.5            | NMI           | 7  |

| 6       | BC1          | AD2   | AD3   | RAS              |                 |                                                                 |                 |                  |                  |                 |                 |                  |                  | P4.4                    | P4.6            | HW<br>CFG2    | 6  |

| 5       | BC0          | AD17  | AD4   | CAS              |                 |                                                                 |                 |                  |                  |                 |                 |                  | HDRS             | P4.7                    | PORST           | BRKIN         | 5  |

| 4       | AD18         | AD 19 | AD20  | V <sub>DDP</sub> | V <sub>SS</sub> | AD28                                                            | AD29            | V <sub>DDP</sub> | V <sub>SS</sub>  | A14             | OKE             | V <sub>DDP</sub> | V <sub>SS</sub>  | A23                     | A22             | A21           | 4  |

| 3       | AD5          | AD21  | AD7   | AD25             | AD11            | AD 12                                                           | AD 15           | AD 30            | A10              | A11             | A12             | A13              |                  | MR/W                    | ALE             | RD/WR         | 3  |

| 2       | AD6          | AD22  | AD8   | AD 9             | AD26            | AD27                                                            | AD31            | AD14             | A5               | A6              | A7              | A8               | A9               | RD                      | MII_<br>RXCLK   | MII_<br>TXCLK | 2  |

| 1       | Reser<br>ved | AD23  | AD24  | BFCLKI           | BFCLKO          | AD 10                                                           | AD13            | SDOLKO           | SDOLKI           | AO              | A1              | A2               | A3               | A4                      | MII_<br>MDIO    | Reser<br>ved  | 1  |

|         | A            | В     | С     | D                | E               | F                                                               | G               | Н                | J                | к               | L               | М                | Ν                | Р                       | R               | Т             |    |

|         |              |       |       |                  |                 |                                                                 |                 |                  |                  |                 |                 |                  |                  | MCF                     | -0495           | 0mod          |    |

| <b></b> |              |       |       |                  |                 |                                                                 |                 |                  |                  |                 |                 |                  |                  |                         |                 |               |    |

Figure 2-3 TC1130 Pins: P-BGA-208 Package (top view)

#### **General Device Information**

## Table 2-1Pin Definitions and Functions (cont'd)

| Symbol | Pin | In<br>Out   | PU/<br>PD <sup>1)</sup> | Functions                   |                                                                                                  |

|--------|-----|-------------|-------------------------|-----------------------------|--------------------------------------------------------------------------------------------------|

| P0.12  | P9  |             | PUC                     | RXDCAN2<br>RCLK0A<br>REQ4   | CAN node 2 receiver input<br>MLI0 receive channel clock input A<br>External Trigger Input 4      |

| P0.13  | P8  | 0<br> <br>0 | PUC                     | TXDCAN2<br>REQ5<br>RREADY0A | CAN node 2 transmitter output<br>External Trigger Input 5<br>MLI0 receive channel ready output A |

| P0.14  | N8  |             | PUC                     | RXDCAN3<br>REQ6<br>RVALID0A | CAN node 3 receiver input<br>External Trigger Input 6<br>MLI0 receive channel valid input A      |

| P0.15  | P7  | 0<br> <br>  | PUC                     | TXDCAN3<br>REQ7<br>RDATA0A  | CAN node 3 transmitter output<br>External Trigger Input 7<br>MLI0 receive channel data input A   |

#### **General Device Information**

#### Table 2-1Pin Definitions and Functions (cont'd)

| Symbol       | Pin | In<br>Out | PU/<br>PD <sup>1)</sup> | Functions |                                                      |

|--------------|-----|-----------|-------------------------|-----------|------------------------------------------------------|

| P1.7         | B13 | I         | PUC                     | MII_RXDV  | Ethernet Controller receive data valid<br>input line |

|              |     | I         |                         | SWCFG7    | Software configuration 7                             |

|              |     | 0         |                         | OCDSA_7   | OCDS L2 Debug Line A7                                |

| P1.8         | A13 | I         | PUC                     | MII_CRS   | Ethernet Controller carrier input line               |

|              |     |           |                         | SWCFG8    | Software configuration 8                             |

| <b>D</b> / A |     | 0         |                         | OCDSA_8   | OCDS L2 Debug Line A8                                |

| P1.9         | A14 |           | PUC                     | MII_COL   | Ethernet Controller collision input line             |

|              |     |           |                         | SWCFG9    | Software configuration 9                             |

| D1 10        | D14 | 0         |                         | OCDSA_9   | OCDS L2 Debug Line A9                                |

| P1.10        | B14 |           | PUC                     | MII_RXD0  | Ethernet Controller receive data input<br>line 0     |

|              |     | 1         |                         | SWCFG10   | Software configuration 10                            |

|              |     | 0         |                         | OCDSA_10  | OCDS L2 Debug Line A10                               |

| P1.11        | C14 | 1         | PUC                     | MII_RXD1  | Ethernet Controller receive data input<br>line 1     |

|              |     | I         |                         | SWCFG11   | Software configuration 11                            |

|              |     | 0         |                         | OCDSA_11  | OCDS L2 Debug Line A1                                |

|              |     | 0         |                         | SLSO0_1   | SSC0 Slave Select output 1                           |

| P1.12        | F13 | 1         | PUC                     | MII_RXD2  | Ethernet Controller receive data input<br>line 2     |

|              |     | I         |                         | SWCFG12   | Software configuration 12                            |

|              |     | 0         |                         | OCDSA_12  | OCDS L2 Debug Line A12                               |

|              |     | 0         |                         | SLSO1_1   | SSC1 Slave Select output 1                           |

| P1.13        | E14 |           | PUC                     | MII_RXD3  | Ethernet Controller receive data input<br>line 3     |

|              |     | I         |                         | SWCFG13   | Software configuration 13                            |

|              |     | 0         |                         | OCDSA_13  | OCDS L2 Debug Line A13                               |

|              |     | 0         |                         | SLSO0_2   | SSC0 Slave Select output 2                           |

| P1.14        | D14 | I         | PUC                     | MII_RXER  | Ethernet Controller receive error input<br>line      |

|              |     | 0         |                         | SLSO1_2   | SSC1 Slave Select output 2                           |

|              |     | I         |                         | SWCFG14   | Software configuration 14                            |

|              |     | 0         |                         | OCDSA_14  | OCDS L2 Debug Line A14                               |

| P1.15        | F14 | 1         | PUC                     | SLSI0     | SSC0 Slave Select Input                              |

|              |     | 0         |                         | RMW       | EBU Read Modify Write                                |

|              |     | Ι         |                         | SWCFG15   | Software configuration 15                            |

|              |     | 0         |                         | OCDSA_15  | OCDS L2 Debug Line A15                               |

#### **General Device Information**

## Table 2-1 Pin Definitions and Functions (cont'd)

| Symbol | Pin | In<br>Out             | PU/<br>PD <sup>1)</sup> | Functions                                                                                                                      |                                                                                                                                                       |  |  |

|--------|-----|-----------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| P3     |     | I/O                   |                         | <b>Port 3</b><br>Port 3 is a 16-bit bi-directional general purpose I/O<br>port which can be alternatively used for MLI1, CCU61 |                                                                                                                                                       |  |  |

| P3.0   | A15 | 0                     | PUC                     | OCDSB_0<br>COUT61 3                                                                                                            | OCDS Level 2 debug lines.<br>OCDS L2 Debug Line B0<br>CCU61 compare channel 3 output                                                                  |  |  |

| P3.1   | B15 | 0<br>I/O              | PUC                     | OCDSB_1<br>CC61_0                                                                                                              | OCDS L2 Debug Line B1<br>CCU61 input/output of capture/                                                                                               |  |  |

| P3.2   | D15 | 0<br>0                | PUC                     | OCDSB_2<br>COUT61_0                                                                                                            | compare channel 0<br>OCDS L2 Debug Line B2<br>CCU61 output of capture/compare                                                                         |  |  |

| P3.3   | E15 | 0<br>I/O              | PUC                     | OCDSB_3<br>CC61_1                                                                                                              | channel 0<br>OCDS L2 Debug Line B3<br>CCU61 input/output of capture/                                                                                  |  |  |

| P3.4   | G14 | 0<br>0                | PUC                     | OCDSB_4<br>COUT61_1                                                                                                            | compare channel 1<br>OCDS L2 Debug Line B4<br>CCU61 output of capture/compare                                                                         |  |  |

| P3.5   | G15 | 0<br>I/O              | PUC                     | OCDSB_5<br>CC61_2                                                                                                              | channel 1<br>OCDS L2 Debug Line B5<br>CCU61 input/output of capture/                                                                                  |  |  |

| P3.6   | F15 | 0<br>0                | PUC                     | OCDSB_6<br>COUT61_2                                                                                                            | compare channel 2<br>OCDS L2 Debug Line B6<br>CCU61 output of capture/compare                                                                         |  |  |

| P3.7   | H14 | 0<br>I                | PUC                     | OCDSB_7<br>CTRAP1                                                                                                              | channel 2<br>OCDS L2 Debug Line B7<br>CCU61 trap input                                                                                                |  |  |

| P3.8   | C15 | 0<br>0<br>1<br>0      | PUC                     | SLSO0_5<br>OCDSB_8<br>CCPOS1_0<br>TCLK1                                                                                        | SSC0 Slave Select output 5<br>OCDS L2 Debug Line B8<br>CCU61 Hall input signal 0<br>MLI1 transmit channel clock output                                |  |  |

| P3.9   | H15 | 0<br>0<br>1           | PUC                     | SLSO1_5<br>OCDSB_9<br>CCPOS1_1<br>TREADY1                                                                                      | SSC1 Slave Select output 5<br>OCDS L2 Debug Line B9<br>CCU61 Hall input signal 1<br>MLI1 transmit channel ready input                                 |  |  |

| P3.10  | B16 | 0<br>0<br>1<br>0<br>0 | PUC                     | SLSO0_6<br>OCDSB_10<br>CCPOS1_2<br>TVALID1<br>SLSO1_6                                                                          | SSC0 Slave Select output 6<br>OCDS L2 Debug Line B10<br>CCU61 Hall input signal 2<br>MLI1 transmit channel valid output<br>SSC1 Slave Select output 6 |  |  |

#### **Functional Description**

#### Features:

The FPI Bus is designed with the requirements of high-performance systems in mind. The features are:

- Core independent

- Multimaster capability (up to 16 masters)

- Demultiplexed operation

- Clock synchronous

- Peak transfer rate of up to 800 Mbytes/sec (@ 100 MHz bus clock)

- Address and data bus scalable (address bus up to 32 bits, data bus up to 64 bits)

- 8-/16-/32- and 64-bit data transfers

- · Broad range of transfer types from single to multiple data transfers

- · Split transaction support for agents with long response time

- Burst transfer capability

- EMI and power consumption minimized

## 3.4.3 LFI

The LMB-to-FPI Interface (LFI) block provides the circuitry to interface (bridge) the FPI bus and the Local Memory Bus (LMB).

#### LFI Features:

- Full support for bus transactions found within current TriCore<sup>™</sup> 1.3 based systems:

- Single 8/16/32-bit Write/Read transfers from FPI to LMB

- Single 8/16/32/64-bit Write/Read transfers from LMB to FPI

- Read-Modify-Write transfers of 8/16/32-bit in both directions

- Burst transactions of 2, 4 or 8 data beats from the FPI to the LMB

- Burst transactions of 2 or 4 data beats from the LMB to the FPI

- Address decoding and translation as required by TriCore<sup>™</sup> 1.3 implementation

- · FPI master interface supports full pipelining on FPI bus

- LMB master interface supports pipelining on LMB within the scope of the LMB specification

- FPI master interface can act as default master on FPI bus

- Programmable support for split LMB to FPI read transactions

- Retry generation on both FPI and LMB buses

- Full support for abort, retry, error and FPI timeout conditions

- Flexible LMB/FPI clock ratio support including dynamic clock switching support

- LFI core clock may be shut down when no transactions are being issued to LFI from either bus and the LFI has no transactions in progress, thus saving power.

## TC1130

#### **Advance Information**

#### **Functional Description**

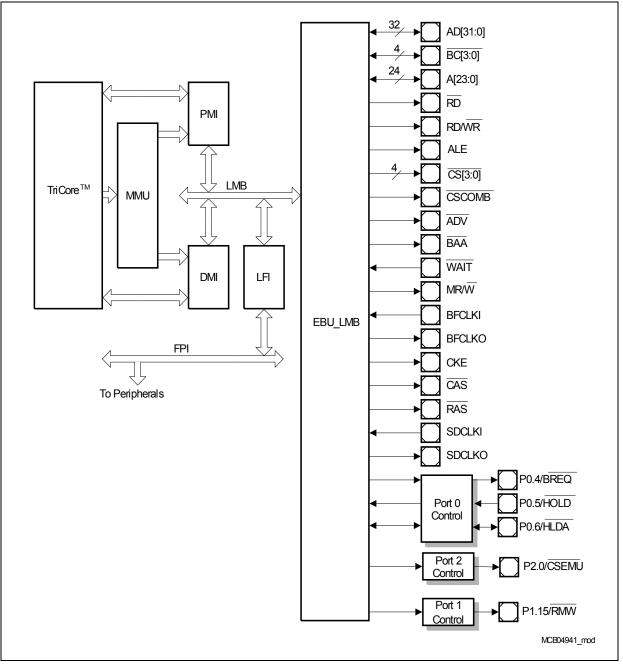

#### 3.5 LMB External Bus Unit

The LMB External Bus Control Unit (EBU) of the TC1130 is the interface between external resources, like memories and peripheral units, and the internal resources connected to on-chip buses if enabled. The basic structure and external interconnections of the EBU are shown in **Figure 3-1**.

Figure 3-1 EBU Structure and Interface

#### **Functional Description**

#### 3.7 Interrupt System

An interrupt request can be serviced by the CPU, which is called "Service Provider". Interrupt requests are referred to as "Service Requests" in this document.

Each peripheral in the TC1130 can generate service requests. Additionally, the Bus Control Unit, the Debug Unit, the DMA Controller and even the CPU itself can generate service requests to the Service Provider. As shown in **Figure 3-3**, each unit that can generate service requests is connected to one or multiple Service Request Nodes (SRN). Each SRN contains a Service Request Control Register mod\_SRC, where "mod" is the identifier of the unit requesting service. The SRNs are connected to the Interrupt Control Unit (ICU) via the CPU Interrupt Arbitration Bus. The ICU arbitrates service requests for the CPU and administers the Interrupt Arbitration Bus.

Units that can generate service requests are:

- Asynchronous/Synchronous Serial Interfaces (ASC0, ASC1 and ASC2) with 4 SRNs each

- High-Speed Synchronous Serial Interfaces (SSC0 and SSC1) with 3 SRNs each

- Inter IC Interface (IIC) with 3 SRNs

- Universal Serial Bus (USB) with 8 SRNs

- Micro Link Interface MLI0 with 4 SRNs and MLI1 with 2 SRNs

- General Purpose Timer Unit (GPTU) with 8 SRNs

- Capture/Compare Unit (CCU60 and CCU61) with 4 SRNs each

- MultiCAN (CAN) with 16 SRNs

- Ethernet Controller with 9 SRNs

- External Interrupts with 4 SRNs

- Direct Memory Access Controller (DMA) with 4 SRNs

- DMA Bus with 1 SRN

- System Timer (STM) with 2 SRNs

- Bus Control Units (SBCU and LBCU) with 1 SRN each

- Central Processing Unit (CPU) with 4 SRNs

- Floating Point Unit (FPU) with 1 SRN

- Debug Unit (OCDS) with 1 SRN

The CPU can make service requests directly to itself (via the ICU). The CPU Service Request Nodes are activated through software.

#### **Functional Description**

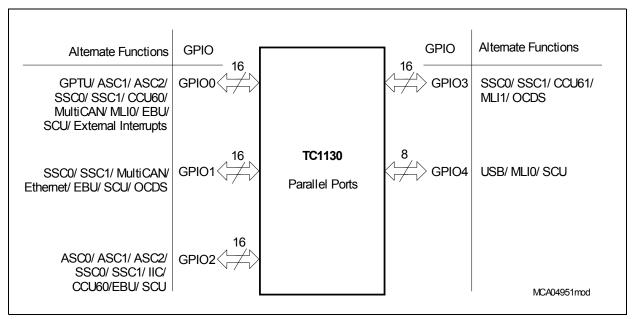

#### 3.8 Parallel Ports

The TC1130 has 72 digital input/output port lines, which are organized into four parallel 16-bit ports and one parallel 8-bit port, Port P0 to Port P4 with 3.3 V nominal voltage.

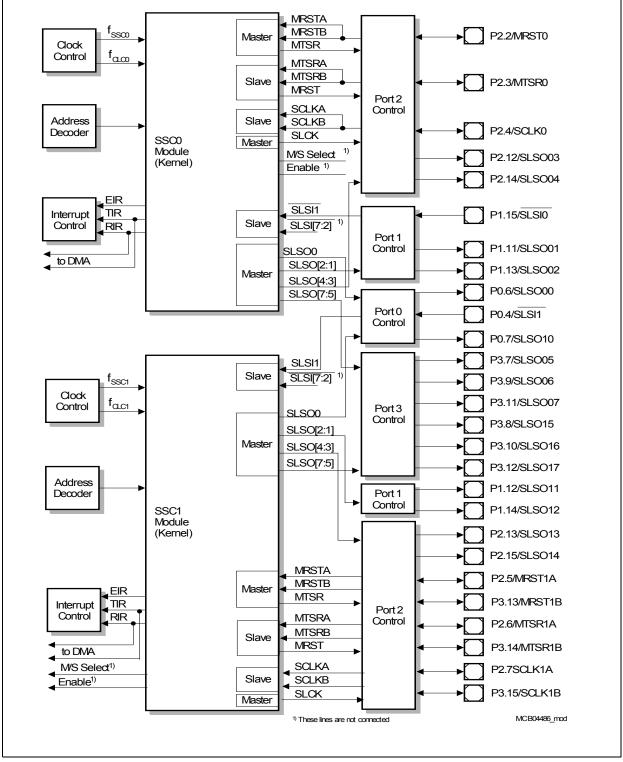

The digital parallel ports can be used as general purpose I/O lines or they can perform input/output functions for the on-chip peripheral units. An overview on the port-to-peripheral unit assignment is shown in **Figure 3-4**.

Figure 3-4 Parallel Ports of the TC1130

## **Functional Description**

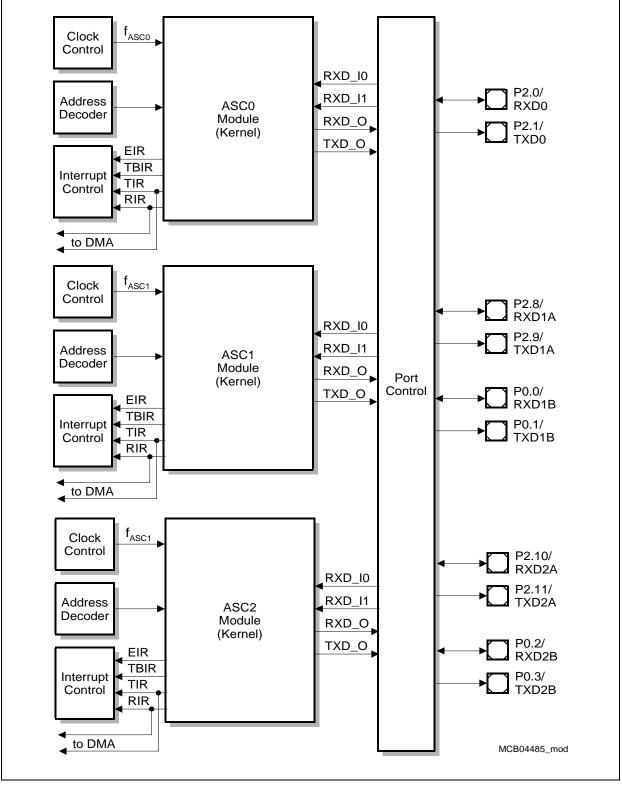

Figure 3-5 General Block Diagram of the ASC Interfaces

#### **Functional Description**

Figure 3-6 General Block Diagram of the SSC Interfaces

#### **Functional Description**

The bit timings for the CAN nodes are derived from the peripheral clock ( $f_{CAN}$ ) and are programmable up to a data rate of 1 MBaud. A pair of receive and transmit pins connects each CAN node to a bus transceiver.

#### Features:

- Compliant to ISO 11898

- CAN functionality according to CAN specification V2.0 B (active)

- Dedicated control registers are provided for each CAN node

- A data transfer rate up to 1 MBaud is supported

- Flexible and powerful message transfer control and error handling capabilities are implemented

- Advanced CAN bus bit timing analysis and baud rate detection can be performed for each CAN node via the frame counter

- Full-CAN functionality: A set of 128 message objects can be individually

- allocated (assigned) to any CAN node

- configured as transmit or receive object

- setup to handle frames with 11-bit or 29-bit identifier

- counted or assigned a timestamp via a frame counter

- configured to remote monitoring mode

- Advanced Acceptance Filtering:

- Each message object provides an individual acceptance mask to filter incoming frames.

- A message object can be configured to accept only standard or only extended frames or to accept both standard and extended frames.

- Message objects can be grouped into 4 priority classes.

- The selection of the message to be transmitted first can be performed on the basis of frame identifier, IDE bit and RTR bit according to CAN arbitration rules.

- Advanced Message Object Functionality:

- Message objects can be combined to build FIFO message buffers of arbitrary size, which is only limited by the total number of message objects.

- Message objects can be linked to form a gateway to automatically transfer frames between two different CAN buses. A single gateway can link any two CAN nodes. An arbitrary number of gateways may be defined.

- Advanced Data Management:

- The Message objects are organized in double chained lists.

- List reorganizations may be performed at any time, even during full operation of the CAN nodes.

- A powerful, command driven list controller manages the organization of the list structure and ensures consistency of the list.

- Message FIFOs are based on the list structure and can easily be scaled in size during CAN operation.

#### **Functional Description**

The Micro Link Serial Bus Interface is dedicated to the serial communication between the other Infineon 32-bit controllers with MLI. The communication is intended to be fast due to an address translation system, and it is not necessary to have any special program in the second controller.

### Features:

- Serial communication from the MLI transmitter to MLI receiver of another controller

- Module supports connection of each MLI with up to four MLI from other controllers

- Fully transparent read/write access supported (= remote programming)

- Complete address range of target controller available

- Special protocol to transfer data, address offset, or address offset and data

- Error control using a parity bit

- 32-bit, 16-bit, and 8-bit data transfers

- · Address offset width: from 1- to 16-bit

- Baud rate: f<sub>MLI</sub> / 2 (symmetric shift clock approach), baud rate definition by the corresponding fractional divider

#### **Functional Description**

RB and TB provide on-chip data buffering whereas DMUR and DMUT perform data transfer from/to the shared memory.

Two interfaces are provided by the Ethernet Controller module:

- MII interface for connection of Ethernet PHYs via 18 Input/Output lines

- Master/slave FPI bus interface for connection to the on-chip system bus for data transfer as well as configuration

#### Features:

- Media Independent Interface (MII) according to IEEE 802.3

- Supports 10 or 100 Mbit/sec MII-based Physical devices

- Supports Full Duplex Ethernet

- Supports data transfer between Ethernet Controller and COM-DRAM

- Supports data transfer between Ethernet Controller and SDRAM via EBU

- 256 x 32 bit Receive buffer and Transmit buffer each

- Supports burst transfers up to 8 x 32 Bytes

### Media Access Controller (MAC)

- 100/10 Mbit/sec operations

- Full IEEE 802.3 compliance

- Station management signaling

- Large on-chip CAM (Content Addressable Memory)

- · Full duplex mode

- 80-byte transmit FIFO

- 16-byte receive FIFO

- PAUSE Operation

- Flexible MAC Control Support

- Supports Long Packet mode and Short Packet mode

- PAD generation

### Media Independent Interface (MII)

- Media independence

- · Multi-vendor point of interoperability

- Supports connection of MAC layer and Physical (PHY) layer devices

- · Capable of supporting both 100 Mbit/sec and 10 Mbit/sec data rates

- Data and delimiters are synchronous to clock references

- Provides independent four bits wide transmit and receive data paths

- Supports connection of PHY layer and Station Management (STA) devices

- · Provides a simple management interface

- Capable of driving a limited length of shielded cable

#### **Functional Description**

# TC1130

## Table 3-5 Load Capacitors Select (cont'd)

| Fundamental Mode Crystal Frequency<br>(approx., MHz) | Load Capacitors<br>C1, C2 (pF) |  |  |  |  |

|------------------------------------------------------|--------------------------------|--|--|--|--|

| 20                                                   | 10                             |  |  |  |  |

| 24                                                   | 10                             |  |  |  |  |

A block capacitor between  $V_{DDOSC3}$  and  $V_{SSOSC},\ V_{DDOSC}$  and  $V_{SSOSC}$  is recommended, too.

**Electrical Parameters**

#### 4.2 DC Parameters

#### 4.2.1 Input/Output Characteristics

| $V_{SS} = 0 V; T_A = -40$ | <b>C</b> to +125 | <b>Q</b> |

|---------------------------|------------------|----------|

|---------------------------|------------------|----------|

| Parameter                              | Symbol               | Limit | Values                 | Unit       | <b>Test Condition</b>                     |  |  |  |  |  |  |

|----------------------------------------|----------------------|-------|------------------------|------------|-------------------------------------------|--|--|--|--|--|--|

|                                        |                      | min.  | max.                   |            |                                           |  |  |  |  |  |  |

| GPIO pins, Dedicated pins and EBU pins |                      |       |                        |            |                                           |  |  |  |  |  |  |

| Input low voltage                      | V <sub>IL</sub> SR   | -0.3  | 0.8                    | V          | LvTTL                                     |  |  |  |  |  |  |

| Input high voltage                     | V <sub>IH</sub> SR   | 2.0   | V <sub>DDP</sub> + 0.3 | V          | LvTTL                                     |  |  |  |  |  |  |

| Output low voltage                     | V <sub>OL</sub> CC   | _     | 0.4                    | V          | I <sub>OL</sub> = 2mA                     |  |  |  |  |  |  |

| Output high voltage                    | V <sub>OH</sub> CC   | 2.4   | -                      | V          | I <sub>OH</sub> = -2mA                    |  |  |  |  |  |  |

| Pull-up current 1)                     | I <sub>PUA</sub>  CC |       |                        | А          | V <sub>IN</sub> = 0V                      |  |  |  |  |  |  |

|                                        | I <sub>PUC</sub>  CC |       |                        | Α          | V <sub>IN</sub> = 0V                      |  |  |  |  |  |  |

| Pull-down current <sup>2)</sup>        | I <sub>PDA</sub>  CC | -     | 156                    | FA         | $V_{IN} = V_{DDP}$                        |  |  |  |  |  |  |

|                                        | I <sub>PDC</sub>  CC | -     | 15.7                   | <b>F</b> A | $V_{IN} = V_{DDP}$                        |  |  |  |  |  |  |

| Input leakage current 3)               | I <sub>OZ1</sub> CC  | -     | r350                   | nA         | $0 < V_{IN} < V_{DDP}$                    |  |  |  |  |  |  |

| Pin Capacitance <sup>4)</sup>          | C <sub>IO</sub> CC   | _     | 10                     | pF         | f = 1 MHz<br>T <sub>A</sub> = 25 <b>C</b> |  |  |  |  |  |  |

<sup>1)</sup> The current is applicable to the pins, for which a pull-up has been specified. Refer to Table 2-1. I<sub>PUx</sub> refers to the pull-up current for type x in absolute values.

<sup>2)</sup> The current is applicable to the pins, for which a pull-down has been specified. Refer to Table 2-1. I<sub>PDx</sub> refers to the pull-down current for type x in absolute values.

<sup>3)</sup> Excluded following pins: NMI, TRST, TCK, TDI, TMS, MII\_TXCLK, MII\_RXCLK, MII\_MDIO, ALE, P2.1,HWCFG0, HWCFG1, HWCFG2, BRKIN, PORST, HDRST.

<sup>4)</sup> Not subject to production test, verified by design/characterization.

TC1130

**Electrical Parameters**