#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

÷ХГ

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                              |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 40MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                 |

| Number of I/O              | 65                                                                           |

| Program Memory Size        | 1MB (1M x 8)                                                                 |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 256K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                                  |

| Data Converters            | A/D - 12b SAR                                                                |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TJ)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 125-VFBGA                                                                    |

| Supplier Device Package    | 125-BGA (7x7)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32jg12b500f1024il125-cr |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1. Feature List

The EFM32JG12 highlighted features are listed below.

## ARM Cortex-M3 CPU platform

- High performance 32-bit processor @ up to 40 MHz

- Memory Protection Unit

- Wake-up Interrupt Controller

- Flexible Energy Management System

- 64 µA/MHz in Active Mode (EM0)

- 2.1 µA EM2 Deep Sleep current (256 kB RAM retention and RTCC running from LFXO)

- 1.5  $\mu A$  EM2 Deep Sleep current (16 kB RAM retention and RTCC running from LFRCO)

- 1.81  $\mu\text{A}$  EM3 Stop current (State and 256 kB RAM retention, CRYOTIMER running from ULFRCO)

- 0.39 µA EM4H Hibernate Mode (128 byte RAM retention)

- Up to 1024 kB flash program memory

- Dual-bank with read-while-write support

- Up to 256 kB RAM data memory

- Up to 65 General Purpose I/O Pins

- Configurable push-pull, open-drain, pull-up/down, input filter, drive strength

- Configurable peripheral I/O locations

- Asynchronous external interrupts

- Output state retention and wake-up from Shutoff Mode

- Hardware Cryptography

- AES 128/256-bit keys

- ECC B/K163, B/K233, P192, P224, P256

- SHA-1 and SHA-2 (SHA-224 and SHA-256)

- True random number generator (TRNG)

- Security Management Unit (SMU)

- Fine-grained access control for on-chip peripherals

- Timers/Counters

- 2× 16-bit Timer/Counter

- 3 + 4 Compare/Capture/PWM channels

- 2× 32-bit Timer/Counter

- 3 + 4 Compare/Capture/PWM channels

- 1× 32-bit Real Time Counter and Calendar

- 1× 32-bit Ultra Low Energy CRYOTIMER for periodic wakeup from any Energy Mode

- 16-bit Low Energy Timer for waveform generation

- 3× 16-bit Pulse Counter with asynchronous operation

- 2× Watchdog Timer with dedicated RC oscillator

- 8 Channel DMA Controller

- 12 Channel Peripheral Reflex System (PRS) for autonomous inter-peripheral signaling

- Communication Interfaces

- 4× Universal Synchronous/Asynchronous Receiver/ Transmitter

- UART/SPI/SmartCard (ISO 7816)/IrDA/I2S/LIN

- Triple buffered full/half-duplex operation with flow control

- Low Energy UART

- Autonomous operation with DMA in Deep Sleep Mode

- 2× I<sup>2</sup>C Interface with SMBus support

- Address recognition in EM3 Stop Mode

- Ultra Low-Power Precision Analog Peripherals

- 12-bit 1 Msps SAR Analog to Digital Converter (ADC)

- 2× Analog Comparator (ACMP)

- 2× 12-bit 500 ksps Digital to Analog Converter (VDAC)

- 3× Operational Amplifier (OPAMP)

- Digital to Analog Current Converter (IDAC)

- Multi-channel Capacitive Sense Interface (CSEN)

- Up to 54 pins connected to analog channels (APORT) shared between analog peripherals

## Low-Energy Sensor Interface (LESENSE)

- Autonomous sensor monitoring in deep sleep mode

- Wide range of supported sensors, including LC sensors and capacitive touch switches

- Up to 16 channels

- Ultra efficient Power-on Reset and Brown-Out Detector

- Debug Interface

- 2-pin Serial Wire Debug interface

- 1-pin Serial Wire Viewer

- JTAG (programming only)

- Embedded Trace Macrocell (ETM)

- Wide Operating Range

- 1.8 V to 3.8 V single power supply

- Integrated DC-DC, down to 1.8 V output with up to 200 mA load current for system

- Standard (-40 °C to 85 °C  $T_{AMB})$  and Extended (-40 °C to 125 °C  $T_J)$  temperature grades available

- Packages

- 7 mm × 7 mm QFN48

- 7 mm × 7 mm BGA125

- Pre-Programmed UART Bootloader

- Full Software Support

- CMSIS register definitions

- Low-power Hardware Abstraction Layer (HAL)

- Portable software components

- Third-party middleware

- Free and available example code

### 3.5.4 Low Energy Timer (LETIMER)

The unique LETIMER is a 16-bit timer that is available in energy mode EM2 Deep Sleep in addition to EM1 Sleep and EM0 Active. This allows it to be used for timing and output generation when most of the device is powered down, allowing simple tasks to be performed while the power consumption of the system is kept at an absolute minimum. The LETIMER can be used to output a variety of waveforms with minimal software intervention. The LETIMER is connected to the Real Time Counter and Calendar (RTCC), and can be configured to start counting on compare matches from the RTCC.

### 3.5.5 Ultra Low Power Wake-up Timer (CRYOTIMER)

The CRYOTIMER is a 32-bit counter that is capable of running in all energy modes. It can be clocked by either the 32.768 kHz crystal oscillator (LFXO), the 32.768 kHz RC oscillator (LFRCO), or the 1 kHz RC oscillator (ULFRCO). It can provide periodic Wakeup events and PRS signals which can be used to wake up peripherals from any energy mode. The CRYOTIMER provides a wide range of interrupt periods, facilitating flexible ultra-low energy operation.

### 3.5.6 Pulse Counter (PCNT)

The Pulse Counter (PCNT) peripheral can be used for counting pulses on a single input or to decode quadrature encoded inputs. The clock for PCNT is selectable from either an external source on pin PCTNn\_S0IN or from an internal timing reference, selectable from among any of the internal oscillators, except the AUXHFRCO. The module may operate in energy mode EM0 Active, EM1 Sleep, EM2 Deep Sleep, and EM3 Stop.

#### 3.5.7 Watchdog Timer (WDOG)

The watchdog timer can act both as an independent watchdog or as a watchdog synchronous with the CPU clock. It has windowed monitoring capabilities, and can generate a reset or different interrupts depending on the failure mode of the system. The watchdog can also monitor autonomous systems driven by PRS.

#### 3.6 Communications and Other Digital Peripherals

#### 3.6.1 Universal Synchronous/Asynchronous Receiver/Transmitter (USART)

The Universal Synchronous/Asynchronous Receiver/Transmitter is a flexible serial I/O module. It supports full duplex asynchronous UART communication with hardware flow control as well as RS-485, SPI, MicroWire and 3-wire. It can also interface with devices supporting:

- ISO7816 SmartCards

- IrDA

- I<sup>2</sup>S

### 3.6.2 Low Energy Universal Asynchronous Receiver/Transmitter (LEUART)

The unique LEUART<sup>TM</sup> provides two-way UART communication on a strict power budget. Only a 32.768 kHz clock is needed to allow UART communication up to 9600 baud. The LEUART includes all necessary hardware to make asynchronous serial communication possible with a minimum of software intervention and energy consumption.

#### 3.6.3 Inter-Integrated Circuit Interface (I<sup>2</sup>C)

The I<sup>2</sup>C module provides an interface between the MCU and a serial I<sup>2</sup>C bus. It is capable of acting as both a master and a slave and supports multi-master buses. Standard-mode, fast-mode and fast-mode plus speeds are supported, allowing transmission rates from 10 kbit/s up to 1 Mbit/s. Slave arbitration and timeouts are also available, allowing implementation of an SMBus-compliant system. The interface provided to software by the I<sup>2</sup>C module allows precise timing control of the transmission process and highly automated transfers. Automatic recognition of slave addresses is provided in active and low energy modes.

#### 3.6.4 Peripheral Reflex System (PRS)

The Peripheral Reflex System provides a communication network between different peripheral modules without software involvement. Peripheral modules producing Reflex signals are called producers. The PRS routes Reflex signals from producers to consumer peripherals which in turn perform actions in response. Edge triggers and other functionality can be applied by the PRS. The PRS allows peripheral to act autonomously without waking the MCU core, saving power.

## 4.1.7 Brown Out Detector (BOD)

| Parameter              | Symbol                    | Test Condition               | Min | Тур | Max | Unit |

|------------------------|---------------------------|------------------------------|-----|-----|-----|------|

| DVDD BOD threshold     | V <sub>DVDDBOD</sub>      | DVDD rising                  | —   | _   | TBD | V    |

|                        |                           | DVDD falling (EM0/EM1)       | TBD | _   | _   | V    |

|                        |                           | DVDD falling (EM2/EM3)       | TBD | _   | _   | V    |

| DVDD BOD hysteresis    | V <sub>DVDDBOD_HYST</sub> |                              | —   | 18  | _   | mV   |

| DVDD BOD response time | tDVDDBOD_DELAY            | Supply drops at 0.1V/µs rate | —   | 2.4 | _   | μs   |

| AVDD BOD threshold     | V <sub>AVDDBOD</sub>      | AVDD rising                  | —   | _   | TBD | V    |

|                        |                           | AVDD falling (EM0/EM1)       | TBD |     | _   | V    |

|                        |                           | AVDD falling (EM2/EM3)       | TBD | _   | _   | V    |

| AVDD BOD hysteresis    | VAVDDBOD_HYST             |                              | _   | 20  |     | mV   |

| AVDD BOD response time | tavddbod_delay            | Supply drops at 0.1V/µs rate | —   | 2.4 | _   | μs   |

| EM4 BOD threshold      | V <sub>EM4DBOD</sub>      | AVDD rising                  | _   |     | TBD | V    |

|                        |                           | AVDD falling                 | TBD | _   | _   | V    |

| EM4 BOD hysteresis     | V <sub>EM4BOD_HYST</sub>  |                              | _   | 25  | _   | mV   |

| EM4 BOD response time  | t <sub>EM4BOD_DELAY</sub> | Supply drops at 0.1V/µs rate | —   | 300 | _   | μs   |

### Table 4.9. Brown Out Detector (BOD)

## 4.1.11 Voltage Monitor (VMON)

| Parameter                          | Symbol                  | Test Condition                                                   | Min  | Тур  | Мах | Unit |

|------------------------------------|-------------------------|------------------------------------------------------------------|------|------|-----|------|

| Supply current (including I_SENSE) | IVMON                   | In EM0 or EM1, 1 supply moni-<br>tored                           | _    | 6.3  | TBD | μA   |

|                                    |                         | In EM0 or EM1, 4 supplies moni-<br>tored                         | —    | 12.5 | TBD | μA   |

|                                    |                         | In EM2, EM3 or EM4, 1 supply monitored and above threshol        | —    | 62   | _   | nA   |

|                                    |                         | In EM2, EM3 or EM4, 1 supply monitored and below threshold       | _    | 62   | _   | nA   |

|                                    |                         | In EM2, EM3 or EM4, 4 supplies monitored and all above threshold | —    | 99   |     | nA   |

|                                    |                         | In EM2, EM3 or EM4, 4 supplies monitored and all below threshold | —    | 99   |     | nA   |

| Loading of monitored supply        | I <sub>SENSE</sub>      | In EM0 or EM1                                                    | _    | 2    | _   | μA   |

|                                    |                         | In EM2, EM3 or EM4                                               | _    | 2    |     | nA   |

| Threshold range                    | V <sub>VMON_RANGE</sub> |                                                                  | 1.62 | —    | 3.4 | V    |

| Threshold step size                | N <sub>VMON_STESP</sub> | Coarse                                                           | _    | 200  |     | mV   |

|                                    |                         | Fine                                                             | _    | 20   |     | mV   |

| Response time                      | t <sub>VMON_RES</sub>   | Supply drops at 1V/µs rate                                       | —    | 460  | —   | ns   |

| Hysteresis                         | V <sub>VMON_HYST</sub>  |                                                                  | _    | 26   | _   | mV   |

### Table 4.18. Voltage Monitor (VMON)

| Parameter                                 | Symbol                 | Test Condition                                             | Min | Тур  | Мах | Unit |

|-------------------------------------------|------------------------|------------------------------------------------------------|-----|------|-----|------|

| Hysteresis (V <sub>CM</sub> = 1.25 V,     | V <sub>ACMPHYST</sub>  | HYSTSEL <sup>5</sup> = HYST0                               | TBD |      | TBD | mV   |

| $BIASPROG^4 = 0x10, FULL-BIAS^4 = 1)$     |                        | HYSTSEL <sup>5</sup> = HYST1                               | TBD | 18   | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST2                               | TBD | 32   | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST3                               | TBD | 44   | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST4                               | TBD | 55   | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST5                               | TBD | 65   | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST6                               | TBD | 77   | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST7                               | TBD | 86   | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST8                               | TBD |      | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST9                               | TBD | -18  | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST10                              | TBD | -32  | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST11                              | TBD | -43  | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST12                              | TBD | -54  | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST13                              | TBD | -64  | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST14                              | TBD | -74  | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST15                              | TBD | -85  | TBD | mV   |

| Comparator delay <sup>3</sup>             | t <sub>ACMPDELAY</sub> | $BIASPROG^4 = 1$ , $FULLBIAS^4 = 0$                        | _   | 30   | _   | μs   |

|                                           |                        | BIASPROG <sup>4</sup> = 0x10, FULLBIAS <sup>4</sup><br>= 0 | _   | 3.7  | _   | μs   |

|                                           |                        | BIASPROG <sup>4</sup> = 0x02, FULLBIAS <sup>4</sup><br>= 1 | —   | 360  | _   | ns   |

|                                           |                        | BIASPROG <sup>4</sup> = 0x20, FULLBIAS <sup>4</sup><br>= 1 | —   | 35   | _   | ns   |

| Offset voltage                            | VACMPOFFSET            | BIASPROG <sup>4</sup> =0x10, FULLBIAS <sup>4</sup><br>= 1  | TBD | _    | TBD | mV   |

| Reference voltage                         | V <sub>ACMPREF</sub>   | Internal 1.25 V reference                                  | TBD | 1.25 | TBD | V    |

|                                           |                        | Internal 2.5 V reference                                   | TBD | 2.5  | TBD | V    |

| Capacitive sense internal re-<br>sistance | R <sub>CSRES</sub>     | CSRESSEL <sup>6</sup> = 0                                  | _   | inf  | _   | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 1                                  | —   | 15   | —   | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 2                                  | —   | 27   | —   | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 3                                  | _   | 39   |     | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 4                                  | _   | 51   | —   | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 5                                  |     | 102  |     | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 6                                  |     | 164  |     | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 7                                  | _   | 239  |     | kΩ   |

| D                                                       | <b>A</b>                 |                                                     | <b>N</b> 41 - | -    |     | 11.14 |

|---------------------------------------------------------|--------------------------|-----------------------------------------------------|---------------|------|-----|-------|

| Parameter                                               | Symbol                   | Test Condition                                      | Min           | Тур  | Мах | Unit  |

| Signal to noise and distortion ratio (1 kHz sine wave), | SNDR <sub>DAC</sub>      | 500 ksps, single-ended, internal<br>1.25V reference | —             | 60.4 | _   | dB    |

| Noise band limited to 250 kHz                           |                          | 500 ksps, single-ended, internal<br>2.5V reference  | —             | 61.6 | —   | dB    |

|                                                         |                          | 500 ksps, single-ended, 3.3V<br>VDD reference       | -             | 64.0 | _   | dB    |

|                                                         |                          | 500 ksps, differential, internal<br>1.25V reference | _             | 63.3 | _   | dB    |

|                                                         |                          | 500 ksps, differential, internal<br>2.5V reference  | _             | 64.4 | _   | dB    |

|                                                         |                          | 500 ksps, differential, 3.3V VDD reference          | _             | 65.8 | _   | dB    |

| Signal to noise and distortion ratio (1 kHz sine wave). | SNDR <sub>DAC_BAND</sub> | 500 ksps, single-ended, internal 1.25V reference    | _             | 65.3 | _   | dB    |

| Noise band limited to 22 kHz.                           |                          | 500 ksps, single-ended, internal<br>2.5V reference  | _             | 66.7 | _   | dB    |

|                                                         |                          | 500 ksps, differential, 3.3V VDD reference          | _             | 68.5 | —   | dB    |

|                                                         |                          | 500 ksps, differential, internal<br>1.25V reference | _             | 67.8 | —   | dB    |

|                                                         |                          | 500 ksps, differential, internal<br>2.5V reference  | _             | 69.0 | _   | dB    |

|                                                         |                          | 500 ksps, single-ended, 3.3V<br>VDD reference       | _             | 70.0 | _   | dB    |

| Total harmonic distortion                               | THD                      |                                                     | _             | 70.2 | _   | dB    |

| Differential non-linearity <sup>3</sup>                 | DNL <sub>DAC</sub>       |                                                     | TBD           |      | TBD | LSB   |

| Intergral non-linearity                                 | INL <sub>DAC</sub>       |                                                     | TBD           | _    | TBD | LSB   |

| Offset error <sup>5</sup>                               | V <sub>OFFSET</sub>      | T <sub>J</sub> = 25 °C                              | TBD           |      | TBD | mV    |

|                                                         |                          | -40 °C ≤ T <sub>J</sub> ≤ 85 °C                     | TBD           |      | TBD | mV    |

| Gain error <sup>5</sup>                                 | V <sub>GAIN</sub>        | T <sub>J</sub> = 25 °C                              | TBD           |      | TBD | %     |

|                                                         |                          | -40 °C ≤ T <sub>J</sub> ≤ 85 °C                     | TBD           |      | TBD | %     |

| External load capactiance,<br>OUTSCALE=0                | C <sub>LOAD</sub>        |                                                     | _             | _    | 75  | pF    |

### Note:

1. Supply current specifications are for VDAC circuitry operating with static output only and do not include current required to drive the load.

2. In differential mode, the output is defined as the difference between two single-ended outputs. Absolute voltage on each output is limited to the single-ended range.

3. Entire range is monotonic and has no missing codes.

- 4. Current from HFPERCLK is dependent on HFPERCLK frequency. This current contributes to the total supply current used when the clock to the DAC module is enabled in the CMU.

- 5. Gain is calculated by measuring the slope from 10% to 90% of full scale. Offset is calculated by comparing actual VDAC output at 10% of full scale to ideal VDAC output at 10% of full scale with the measured gain.

6. PSRR calculated as 20 \* log<sub>10</sub>( $\Delta$ VDD /  $\Delta$ V<sub>OUT</sub>), VDAC output at 90% of full scale

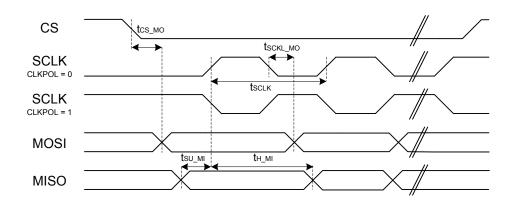

### 4.1.21 USART SPI

## **SPI Master Timing**

## Table 4.30. SPI Master Timing

| Parameter                      | Symbol               | Test Condition | Min                          | Тур | Max  | Unit |

|--------------------------------|----------------------|----------------|------------------------------|-----|------|------|

| SCLK period <sup>1 3 2</sup>   | t <sub>SCLK</sub>    |                | 2 *<br>t <sub>HFPERCLK</sub> | _   | _    | ns   |

| CS to MOSI <sup>1 3</sup>      | t <sub>CS_MO</sub>   |                | 0                            | —   | 13.3 | ns   |

| SCLK to MOSI <sup>1 3</sup>    | t <sub>SCLK_MO</sub> |                | 0                            | —   | 8    | ns   |

| MISO setup time <sup>1 3</sup> | t <sub>SU_MI</sub>   | IOVDD = 1.62 V | 90                           | _   | —    | ns   |

|                                |                      | IOVDD = 3.0 V  | 40                           | —   | —    | ns   |

| MISO hold time <sup>1 3</sup>  | t <sub>H_MI</sub>    |                | 10                           | _   | -    | ns   |

| Note:                          |                      |                |                              |     |      |      |

#### Note:

1. Applies for both CLKPHA = 0 and CLKPHA = 1 (figure only shows CLKPHA = 0).

2. t<sub>HFPERCLK</sub> is one period of the selected HFPERCLK.

3. Measurement done with 8 pF output loading at 10% and 90% of  $V_{DD}$  (figure shows 50% of  $V_{DD}$ ).

Figure 4.1. SPI Master Timing Diagram

## 6. Pin Definitions

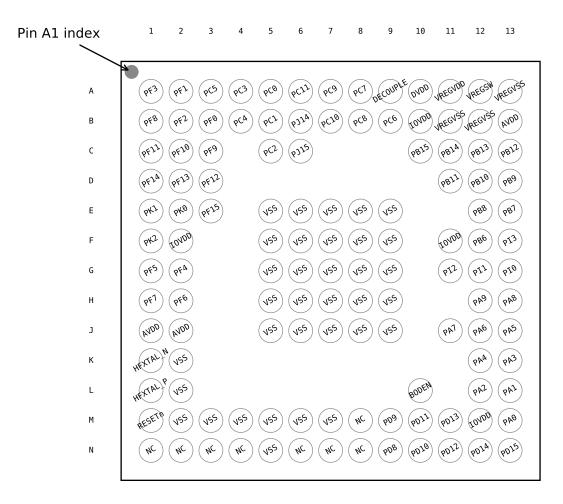

### 6.1 EFM32JG12B5xx in BGA125 Device Pinout

Figure 6.1. EFM32JG12B5xx in BGA125 Device Pinout

|       | Pin      |                                                  | Pin Alternate Functi                                                                                                                                                                                                                                                                                                                                                                                                                    | ionality / Description                                                                                                                                                                                                                                                                                     |                                                                                                            |

|-------|----------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Pin # | Pin Name | Analog                                           | Timers                                                                                                                                                                                                                                                                                                                                                                                                                                  | Communication                                                                                                                                                                                                                                                                                              | Other                                                                                                      |

| N9    | PD8      | BUSDY BUSCX                                      | WTIM0_CC1 #30<br>WTIM0_CC2 #28<br>WTIM0_CDTI0 #24<br>WTIM0_CDTI1 #22<br>WTIM0_CDTI2 #20<br>WTIM1_CC0 #16<br>WTIM1_CC1 #14<br>WTIM1_CC2 #12<br>WTIM1_CC3 #10                                                                                                                                                                                                                                                                             | US3_TX #0 US3_RX<br>#31 US3_CLK #30<br>US3_CS #29 US3_CTS<br>#28 US3_RTS #27                                                                                                                                                                                                                               | LES_CH0                                                                                                    |

| N10   | PD10     | BUSDY BUSCX                                      | TIM0_CC0 #18<br>TIM0_CC1 #17<br>TIM0_CC2 #16<br>TIM0_CDTI0 #15<br>TIM0_CDTI0 #15<br>TIM0_CDTI2 #13<br>TIM1_CC0 #18<br>TIM1_CC1 #17<br>TIM1_CC2 #16<br>TIM1_CC3 #15<br>WTIM0_CDT10 #26<br>WTIM0_CDT10 #26<br>WTIM0_CDT11 #24<br>WTIM0_CDT12 #22<br>WTIM1_CC1 #16<br>WTIM1_CC1 #16<br>WTIM1_CC2 #14<br>WTIM1_CC3 #12 LE-<br>TIM0_OUT0 #18 LE-<br>TIM0_OUT0 #18 LE-<br>TIM0_OUT1 #17<br>PCNT0_S0IN #18<br>PCNT0_S1IN #17                   | US0_TX #18 US0_RX<br>#17 US0_CLK #16<br>US0_CS #15 US0_CTS<br>#14 US0_RTS #13<br>US1_TX #18 US1_RX<br>#17 US1_CLK #16<br>US1_CS #15 US1_CTS<br>#14 US1_RTS #13<br>US3_TX #2 US3_RX #1<br>US3_CLK #0 US3_CS<br>#31 US3_CTS #30<br>US3_RTS #29<br>LEU0_TX #18<br>LEU0_RX #17<br>I2C0_SDA #18<br>I2C0_SCL #17 | CMU_CLK1 #4<br>PRS_CH3 #9 PRS_CH4<br>#1 PRS_CH5 #0<br>PRS_CH6 #12<br>ACMP0_O #18<br>ACMP1_O #18<br>LES_CH2 |

| N11   | PD12     | VDAC0_OUT1ALT /<br>OPA1_OUTALT #0<br>BUSDY BUSCX | TIM0_CC0 #20<br>TIM0_CC1 #19<br>TIM0_CC2 #18<br>TIM0_CDTI0 #17<br>TIM0_CDTI0 #17<br>TIM0_CDTI1 #16<br>TIM0_CDTI2 #15<br>TIM1_CC0 #20<br>TIM1_CC1 #19<br>TIM1_CC2 #18<br>TIM1_CC3 #17<br>WTIM0_CDTI0 #28<br>WTIM0_CDTI1 #26<br>WTIM0_CDTI1 #26<br>WTIM0_CDT12 #24<br>WTIM1_CC0 #20<br>WTIM1_CC1 #18<br>WTIM1_CC2 #16<br>WTIM1_CC3 #14 LE-<br>TIM0_OUT0 #20 LE-<br>TIM0_OUT0 #20 LE-<br>TIM0_OUT1 #19<br>PCNT0_S0IN #20<br>PCNT0_S1IN #19 | US0_TX #20 US0_RX<br>#19 US0_CLK #18<br>US0_CS #17 US0_CTS<br>#16 US0_RTS #15<br>US1_TX #20 US1_RX<br>#19 US1_CLK #18<br>US1_CS #17 US1_CTS<br>#16 US1_RTS #15<br>US3_TX #4 US3_RX #3<br>US3_CLK #2 US3_CS<br>#1 US3_CTS #0<br>US3_RTS #31<br>LEU0_TX #20<br>LEU0_RX #19<br>I2C0_SDA #20<br>I2C0_SCL #19   | PRS_CH3 #11<br>PRS_CH4 #3 PRS_CH5<br>#2 PRS_CH6 #14<br>ACMP0_O #20<br>ACMP1_O #20<br>LES_CH4               |

| Pin Pin Alternate Functionality / Description |          |                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                      |                                                                                                                            |

|-----------------------------------------------|----------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Pin #                                         | Pin Name | Analog                                                     | Timers                                                                                                                                                                                                                                                                                                                                                                                                                | Communication                                                                                                                                                                                                                                                                                        | Other                                                                                                                      |

| N12                                           | PD14     | BUSDY BUSCX<br>VDAC0_OUT1 /<br>OPA1_OUT                    | TIM0_CC0 #22<br>TIM0_CC1 #21<br>TIM0_CC2 #20<br>TIM0_CDTI0 #19<br>TIM0_CDTI1 #18<br>TIM0_CDTI2 #17<br>TIM1_CC0 #22<br>TIM1_CC1 #21<br>TIM1_CC2 #20<br>TIM1_CC3 #19<br>WTIM0_CDTI0 #30<br>WTIM0_CDTI0 #30<br>WTIM0_CDTI1 #28<br>WTIM0_CDT12 #26<br>WTIM1_CC1 #20<br>WTIM1_CC1 #20<br>WTIM1_CC2 #18<br>WTIM1_CC3 #16 LE-<br>TIM0_OUT0 #22 LE-<br>TIM0_OUT0 #22 LE-<br>TIM0_OUT1 #21<br>PCNT0_S0IN #22<br>PCNT0_S1IN #21 | US0_TX #22 US0_RX<br>#21 US0_CLK #20<br>US0_CS #19 US0_CTS<br>#18 US0_RTS #17<br>US1_TX #22 US1_RX<br>#21 US1_CLK #20<br>US1_CS #19 US1_CTS<br>#18 US1_RTS #17<br>US3_TX #6 US3_RX #5<br>US3_CLK #4 US3_CS<br>#3 US3_CTS #2<br>US3_RTS #1 LEU0_TX<br>#22 LEU0_RX #21<br>I2C0_SDA #22<br>I2C0_SCL #21 | CMU_CLK0 #5<br>PRS_CH3 #13<br>PRS_CH4 #5 PRS_CH5<br>#4 PRS_CH6 #16<br>ACMP0_O #22<br>ACMP1_O #22<br>LES_CH6<br>GPIO_EM4WU4 |

| N13                                           | PD15     | VDAC0_OUT0ALT /<br>OPA0_OUTALT #2<br>BUSCY BUSDX<br>OPA1_N | TIM0_CC0 #23<br>TIM0_CC1 #22<br>TIM0_CC2 #21<br>TIM0_CDTI0 #20<br>TIM0_CDTI1 #19<br>TIM0_CDTI2 #18<br>TIM1_CC0 #23<br>TIM1_CC1 #22<br>TIM1_CC2 #21<br>TIM1_CC3 #20<br>WTIM0_CDTI0 #31<br>WTIM0_CDTI0 #31<br>WTIM0_CDTI1 #29<br>WTIM0_CDTI2 #27<br>WTIM1_CC0 #23<br>WTIM1_CC1 #21<br>WTIM1_CC3 #17 LE-<br>TIM0_OUT0 #23 LE-<br>TIM0_OUT0 #23 LE-<br>TIM0_OUT1 #22<br>PCNT0_S0IN #23<br>PCNT0_S1IN #22                  | US0_TX #23 US0_RX<br>#22 US0_CLK #21<br>US0_CS #20 US0_CTS<br>#19 US0_RTS #18<br>US1_TX #23 US1_RX<br>#22 US1_CLK #21<br>US1_CS #20 US1_CTS<br>#19 US1_RTS #18<br>US3_TX #7 US3_RX #6<br>US3_CLK #5 US3_CS<br>#4 US3_CTS #3<br>US3_RTS #2 LEU0_TX<br>#23 LEU0_RX #22<br>I2C0_SDA #23<br>I2C0_SCL #22 | CMU_CLK1 #5<br>PRS_CH3 #14<br>PRS_CH4 #6 PRS_CH5<br>#5 PRS_CH6 #17<br>ACMP0_O #23<br>ACMP1_O #23<br>LES_CH7 DBG_SWO<br>#2  |

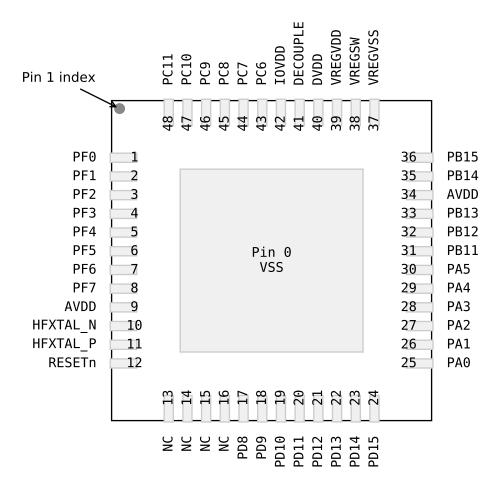

Figure 6.2. EFM32JG12B5xx in QFN48 Device Pinout

|       | Pin      |             | Pin Alternate Funct                                                                                                                                                                                                                                                                                                                                                             | ionality / Description                                                                                                                                                                                                                                                                                        |                                                                                                            |

|-------|----------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Pin # | Pin Name | Analog      | Timers                                                                                                                                                                                                                                                                                                                                                                          | Communication                                                                                                                                                                                                                                                                                                 | Other                                                                                                      |

| 0     | VSS      | Ground      |                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                               |                                                                                                            |

| 1     | PF0      | BUSBY BUSAX | TIM0_CC0 #24<br>TIM0_CC1 #23<br>TIM0_CC2 #22<br>TIM0_CDTI0 #21<br>TIM0_CDTI1 #20<br>TIM0_CDTI2 #19<br>TIM1_CC0 #24<br>TIM1_CC1 #23<br>TIM1_CC2 #22<br>TIM1_CC3 #21<br>WTIM0_CDTI1 #30<br>WTIM0_CDTI2 #28<br>WTIM1_CC0 #24<br>WTIM1_CC1 #22<br>WTIM1_CC2 #20<br>WTIM1_CC3 #18 LE-<br>TIM0_OUT0 #24 LE-<br>TIM0_OUT1 #23<br>PCNT0_S0IN #24<br>PCNT0_S1IN #23                      | US0_TX #24 US0_RX<br>#23 US0_CLK #22<br>US0_CS #21 US0_CTS<br>#20 US0_RTS #19<br>US1_TX #24 US1_RX<br>#23 US1_CLK #22<br>US1_CS #21 US1_CTS<br>#20 US1_RTS #19<br>US2_TX #14 US2_RX<br>#13 US2_CLK #12<br>US2_CS #11 US2_CTS<br>#10 US2_RTS #9<br>LEU0_TX #24<br>LEU0_RX #23<br>I2C0_SDA #24<br>I2C0_SCL #23  | PRS_CH0 #0 PRS_CH1<br>#7 PRS_CH2 #6<br>PRS_CH3 #5<br>ACMP0_O #24<br>ACMP1_O #24<br>DBG_SWCLKTCK<br>BOOT_TX |

| 2     | PF1      | BUSAY BUSBX | TIM0_CC0 #25<br>TIM0_CC1 #24<br>TIM0_CC2 #23<br>TIM0_CDTI0 #22<br>TIM0_CDTI1 #21<br>TIM0_CDTI2 #20<br>TIM1_CC0 #25<br>TIM1_CC1 #24<br>TIM1_CC2 #23<br>TIM1_CC3 #22<br>WTIM0_CDTI1 #31<br>WTIM0_CDTI2 #29<br>WTIM1_CC0 #25<br>WTIM1_CC1 #23<br>WTIM1_CC1 #23<br>WTIM1_CC3 #19 LE-<br>TIM0_OUT0 #25 LE-<br>TIM0_OUT0 #25 LE-<br>TIM0_OUT1 #24<br>PCNT0_S0IN #25<br>PCNT0_S1IN #24 | US0_TX #25 US0_RX<br>#24 US0_CLK #23<br>US0_CS #22 US0_CTS<br>#21 US0_RTS #20<br>US1_TX #25 US1_RX<br>#24 US1_CLK #23<br>US1_CS #22 US1_CTS<br>#21 US1_RTS #20<br>US2_TX #15 US2_RX<br>#14 US2_CLK #13<br>US2_CS #12 US2_CTS<br>#11 US2_RTS #10<br>LEU0_TX #25<br>LEU0_RX #24<br>I2C0_SDA #25<br>I2C0_SCL #24 | PRS_CH0 #1 PRS_CH1<br>#0 PRS_CH2 #7<br>PRS_CH3 #6<br>ACMP0_O #25<br>ACMP1_O #25<br>DBG_SWDIOTMS<br>BOOT_RX |

### Table 6.3. EFM32JG12B5xx in QFN48 Device Pinout

|       | Pin      | onality / Description                                      |                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                          |                                                                                              |

|-------|----------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| Pin # | Pin Name | Analog                                                     | Timers                                                                                                                                                                                                                                                                                                                                                                                                             | Communication                                                                                                                                                                                                                                                                                            | Other                                                                                        |

| 21    | PD12     | VDAC0_OUT1ALT /<br>OPA1_OUTALT #0<br>BUSDY BUSCX           | TIM0_CC0 #20<br>TIM0_CC1 #19<br>TIM0_CC2 #18<br>TIM0_CDTI0 #17<br>TIM0_CDTI1 #16<br>TIM0_CDTI2 #15<br>TIM1_CC0 #20<br>TIM1_CC1 #19<br>TIM1_CC2 #18<br>TIM1_CC2 #18<br>TIM1_CC3 #17<br>WTIM0_CDTI0 #28<br>WTIM0_CDTI1 #26<br>WTIM0_CDT12 #24<br>WTIM1_CC0 #20<br>WTIM1_CC1 #18<br>WTIM1_CC2 #16<br>WTIM1_CC3 #14 LE-<br>TIM0_OUT0 #20 LE-<br>TIM0_OUT0 #20 LE-<br>TIM0_OUT1 #19<br>PCNT0_S0IN #20<br>PCNT0_S1IN #19 | US0_TX #20 US0_RX<br>#19 US0_CLK #18<br>US0_CS #17 US0_CTS<br>#16 US0_RTS #15<br>US1_TX #20 US1_RX<br>#19 US1_CLK #18<br>US1_CS #17 US1_CTS<br>#16 US1_RTS #15<br>US3_TX #4 US3_RX #3<br>US3_CLK #2 US3_CS<br>#1 US3_CTS #0<br>US3_RTS #31<br>LEU0_TX #20<br>LEU0_RX #19<br>I2C0_SDA #20<br>I2C0_SCL #19 | PRS_CH3 #11<br>PRS_CH4 #3 PRS_CH5<br>#2 PRS_CH6 #14<br>ACMP0_O #20<br>ACMP1_O #20<br>LES_CH4 |

| 22    | PD13     | VDAC0_OUT0ALT /<br>OPA0_OUTALT #1<br>BUSCY BUSDX<br>OPA1_P | TIM0_CC0 #21<br>TIM0_CC1 #20<br>TIM0_CC2 #19<br>TIM0_CDTI0 #18<br>TIM0_CDTI1 #17<br>TIM0_CDTI2 #16<br>TIM1_CC0 #21<br>TIM1_CC1 #20<br>TIM1_CC2 #19<br>TIM1_CC3 #18<br>WTIM0_CDTI0 #29<br>WTIM0_CDTI0 #29<br>WTIM0_CDTI1 #27<br>WTIM0_CDTI2 #25<br>WTIM1_CC0 #21<br>WTIM1_CC1 #19<br>WTIM1_CC3 #15 LE-<br>TIM0_OUT0 #21 LE-<br>TIM0_OUT0 #21 LE-<br>TIM0_OUT1 #20<br>PCNT0_S0IN #21<br>PCNT0_S1IN #20               | US0_TX #21 US0_RX<br>#20 US0_CLK #19<br>US0_CS #18 US0_CTS<br>#17 US0_RTS #16<br>US1_TX #21 US1_RX<br>#20 US1_CLK #19<br>US1_CS #18 US1_CTS<br>#17 US1_RTS #16<br>US3_TX #5 US3_RX #4<br>US3_CLK #3 US3_CS<br>#2 US3_CTS #1<br>US3_RTS #0 LEU0_TX<br>#21 LEU0_RX #20<br>I2C0_SDA #21<br>I2C0_SCL #20     | PRS_CH3 #12<br>PRS_CH4 #4 PRS_CH5<br>#3 PRS_CH6 #15<br>ACMP0_O #21<br>ACMP1_O #21<br>LES_CH5 |

|       | Pin      |                         | Pin Alternate Funct                                                                                                                                                                                                                                                                                                                                                           | ionality / Description                                                                                                                                                                                    |                                                                                                                            |

|-------|----------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Pin # | Pin Name | Analog                  | Timers                                                                                                                                                                                                                                                                                                                                                                        | Communication                                                                                                                                                                                             | Other                                                                                                                      |

| 32    | PB12     | BUSDY BUSCX<br>OPA2_OUT | TIM0_CC0 #7<br>TIM0_CC1 #6<br>TIM0_CC2 #5<br>TIM0_CDTI0 #4<br>TIM0_CDTI1 #3<br>TIM0_CDTI2 #2<br>TIM1_CC0 #7<br>TIM1_CC1 #6<br>TIM1_CC2 #5<br>TIM1_CC3 #4<br>WTIM0_CC0 #16<br>WTIM0_CC1 #14<br>WTIM0_CC1 #14<br>WTIM0_CC1 #14<br>WTIM0_CDT10 #8<br>WTIM0_CDT10 #8<br>WTIM0_CDT11 #6<br>WTIM1_CC0 #0 LE-<br>TIM0_OUT0 #7 LE-<br>TIM0_OUT1 #6<br>PCNT0_S0IN #7<br>PCNT0_S1IN #6  | US0_TX #7 US0_RX #6<br>US0_CLK #5 US0_CS<br>#4 US0_CTS #3<br>US0_RTS #2 US1_TX<br>#7 US1_RX #6<br>US1_CLK #5 US1_CS<br>#4 US1_CTS #3<br>US1_RTS #2 LEU0_TX<br>#7 LEU0_RX #6<br>I2C0_SDA #7<br>I2C0_SCL #6 | PRS_CH6 #7 PRS_CH7<br>#6 PRS_CH8 #5<br>PRS_CH9 #4<br>ACMP0_0 #7<br>ACMP1_0 #7                                              |

| 33    | PB13     | BUSCY BUSDX<br>OPA2_N   | TIM0_CC0 #8<br>TIM0_CC1 #7<br>TIM0_CC2 #6<br>TIM0_CDTI0 #5<br>TIM0_CDTI1 #4<br>TIM0_CDTI2 #3<br>TIM1_CC0 #8<br>TIM1_CC1 #7<br>TIM1_CC2 #6<br>TIM1_CC3 #5<br>WTIM0_CC0 #17<br>WTIM0_CC1 #15<br>WTIM0_CC1 #15<br>WTIM0_CDT10 #9<br>WTIM0_CDT10 #9<br>WTIM0_CDT11 #7<br>WTIM0_CDT12 #5<br>WTIM1_CC0 #1 LE-<br>TIM0_OUT0 #8 LE-<br>TIM0_OUT1 #7<br>PCNT0_S0IN #8<br>PCNT0_S1IN #7 | US0_TX #8 US0_RX #7<br>US0_CLK #6 US0_CS<br>#5 US0_CTS #4<br>US0_RTS #3 US1_TX<br>#8 US1_RX #7<br>US1_CLK #6 US1_CS<br>#5 US1_CTS #4<br>US1_RTS #3 LEU0_TX<br>#8 LEU0_RX #7<br>I2C0_SDA #8<br>I2C0_SCL #7 | CMU_CLKI0 #0<br>PRS_CH6 #8 PRS_CH7<br>#7 PRS_CH8 #6<br>PRS_CH9 #5<br>ACMP0_O #8<br>ACMP1_O #8<br>DBG_SWO #1<br>GPIO_EM4WU9 |

| 34    | AVDD     | Analog power supply .   | ·                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                           | ·                                                                                                                          |

|       | Pin      |                                                                                                          | Pin Alternate Funct                                                                                                                                                                                                                                                                                                                                                                               | ionality / Description                                                                                                                                                                                        |                                                                                                 |  |

|-------|----------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--|

| Pin # | Pin Name | Analog                                                                                                   | Timers                                                                                                                                                                                                                                                                                                                                                                                            | Communication                                                                                                                                                                                                 | Other                                                                                           |  |

| 35    | PB14     | BUSDY BUSCX<br>LFXTAL_N                                                                                  | TIM0_CC0 #9<br>TIM0_CC1 #8<br>TIM0_CC2 #7<br>TIM0_CDTI0 #6<br>TIM0_CDTI1 #5<br>TIM0_CDTI2 #4<br>TIM1_CC0 #9<br>TIM1_CC1 #8<br>TIM1_CC2 #7<br>TIM1_CC3 #6<br>WTIM0_CC0 #18<br>WTIM0_CC1 #16<br>WTIM0_CC1 #16<br>WTIM0_CC1 #16<br>WTIM0_CDTI0 #10<br>WTIM0_CDT11 #8<br>WTIM0_CDT12 #6<br>WTIM1_CC0 #2<br>WTIM1_CC1 #0 LE-<br>TIM0_OUT1 #8<br>PCNT0_S0IN #9<br>PCNT0_S0IN #9                         | US0_TX #9 US0_RX #8<br>US0_CLK #7 US0_CS<br>#6 US0_CTS #5<br>US0_RTS #4 US1_TX<br>#9 US1_RX #8<br>US1_CLK #7 US1_CS<br>#6 US1_CTS #5<br>US1_RTS #4 LEU0_TX<br>#9 LEU0_RX #8<br>I2C0_SDA #9<br>I2C0_SCL #8     | CMU_CLK1 #1<br>PRS_CH6 #9 PRS_CH7<br>#8 PRS_CH8 #7<br>PRS_CH9 #6<br>ACMP0_O #9<br>ACMP1_O #9    |  |

| 36    | PB15     | BUSCY BUSDX<br>LFXTAL_P                                                                                  | TIM0_CC0 #10<br>TIM0_CC1 #9<br>TIM0_CC2 #8<br>TIM0_CDTI0 #7<br>TIM0_CDTI1 #6<br>TIM0_CDTI2 #5<br>TIM1_CC0 #10<br>TIM1_CC1 #9<br>TIM1_CC2 #8<br>TIM1_CC3 #7<br>WTIM0_CC0 #19<br>WTIM0_CC0 #19<br>WTIM0_CC1 #17<br>WTIM0_CC1 #17<br>WTIM0_CDT10 #11<br>WTIM0_CDT11 #9<br>WTIM0_CDT12 #7<br>WTIM1_CC0 #3<br>WTIM1_CC1 #1 LE-<br>TIM0_OUT0 #10 LE-<br>TIM0_OUT1 #9<br>PCNT0_S0IN #10<br>PCNT0_S1IN #9 | US0_TX #10 US0_RX<br>#9 US0_CLK #8<br>US0_CS #7 US0_CTS<br>#6 US0_RTS #5<br>US1_TX #10 US1_RX<br>#9 US1_CLK #8<br>US1_CS #7 US1_CTS<br>#6 US1_RTS #5<br>LEU0_TX #10<br>LEU0_RX #9 I2C0_SDA<br>#10 I2C0_SCL #9 | CMU_CLK0 #1<br>PRS_CH6 #10<br>PRS_CH7 #9 PRS_CH8<br>#8 PRS_CH9 #7<br>ACMP0_O #10<br>ACMP1_O #10 |  |

| 37    | VREGVSS  | Voltage regulator VSS                                                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                                                                                                                                                                             |                                                                                                 |  |

| 38    | VREGSW   | DCDC regulator switching                                                                                 | node                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                               |                                                                                                 |  |

| 39    | VREGVDD  | Voltage regulator VDD inp                                                                                | out                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                               |                                                                                                 |  |

| 40    | DVDD     | Digital power supply .                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                               |                                                                                                 |  |

| 41    | DECOUPLE | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin. |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                               |                                                                                                 |  |

| 42    | IOVDD    | Digital IO power supply .                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                               |                                                                                                 |  |

| Alternate     |         |         |          |          |          |          |          |          |                      |

|---------------|---------|---------|----------|----------|----------|----------|----------|----------|----------------------|

| Functionality | 0 - 3   | 4 - 7   | 8 - 11   | 12 - 15  | 16 - 19  | 20 - 23  | 24 - 27  | 28 - 31  | Description          |

| WTIM0_CC0     | 0: PA0  | 4: PA4  | 8: PA8   | 12: PB8  | 16: PB12 | 20: PC0  | 24: PC4  | 28: PC8  | Wide timer 0 Cap-    |

|               | 1: PA1  | 5: PA5  | 9: PA9   | 13: PB9  | 17: PB13 | 21: PC1  | 25: PC5  | 29: PC9  | ture Compare in-     |

|               | 2: PA2  | 6: PA6  | 10: PB6  | 14: PB10 | 18: PB14 | 22: PC2  | 26: PC6  | 30: PC10 | put / output channel |

|               | 3: PA3  | 7: PA7  | 11: PB7  | 15: PB11 | 19: PB15 | 23: PC3  | 27: PC7  | 31: PC11 | 0.                   |

| WTIM0_CC1     | 0: PA2  | 4: PA6  | 8: PB6   | 12: PB10 | 16: PB14 | 20: PC2  | 24: PC6  | 28: PC10 | Wide timer 0 Cap-    |

|               | 1: PA3  | 5: PA7  | 9: PB7   | 13: PB11 | 17: PB15 | 21: PC3  | 25: PC7  | 29: PC11 | ture Compare in-     |

|               | 2: PA4  | 6: PA8  | 10: PB8  | 14: PB12 | 18: PC0  | 22: PC4  | 26: PC8  | 30: PD8  | put / output channel |

|               | 3: PA5  | 7: PA9  | 11: PB9  | 15: PB13 | 19: PC1  | 23: PC5  | 27: PC9  | 31: PD9  | 1.                   |

| WTIM0_CC2     | 0: PA4  | 4: PA8  | 8: PB8   | 12: PB12 | 16: PC0  | 20: PC4  | 24: PC8  | 28: PD8  | Wide timer 0 Cap-    |

|               | 1: PA5  | 5: PA9  | 9: PB9   | 13: PB13 | 17: PC1  | 21: PC5  | 25: PC9  | 29: PD9  | ture Compare in-     |

|               | 2: PA6  | 6: PB6  | 10: PB10 | 14: PB14 | 18: PC2  | 22: PC6  | 26: PC10 | 30: PD10 | put / output channel |

|               | 3: PA7  | 7: PB7  | 11: PB11 | 15: PB15 | 19: PC3  | 23: PC7  | 27: PC11 | 31: PD11 | 2.                   |

| WTIM0_CDTI0   | 0: PA8  | 4: PB8  | 8: PB12  | 12: PC0  | 16: PC4  | 20: PC8  | 24: PD8  | 28: PD12 | Wide timer 0 Com-    |

|               | 1: PA9  | 5: PB9  | 9: PB13  | 13: PC1  | 17: PC5  | 21: PC9  | 25: PD9  | 29: PD13 | plimentary Dead      |

|               | 2: PB6  | 6: PB10 | 10: PB14 | 14: PC2  | 18: PC6  | 22: PC10 | 26: PD10 | 30: PD14 | Time Insertion       |

|               | 3: PB7  | 7: PB11 | 11: PB15 | 15: PC3  | 19: PC7  | 23: PC11 | 27: PD11 | 31: PD15 | channel 0.           |

| WTIM0_CDTI1   | 0: PB6  | 4: PB10 | 8: PB14  | 12: PC2  | 16: PC6  | 20: PC10 | 24: PD10 | 28: PD14 | Wide timer 0 Com-    |

|               | 1: PB7  | 5: PB11 | 9: PB15  | 13: PC3  | 17: PC7  | 21: PC11 | 25: PD11 | 29: PD15 | plimentary Dead      |

|               | 2: PB8  | 6: PB12 | 10: PC0  | 14: PC4  | 18: PC8  | 22: PD8  | 26: PD12 | 30: PF0  | Time Insertion       |

|               | 3: PB9  | 7: PB13 | 11: PC1  | 15: PC5  | 19: PC9  | 23: PD9  | 27: PD13 | 31: PF1  | channel 1.           |

| WTIM0_CDTI2   | 0: PB8  | 4: PB12 | 8: PC0   | 12: PC4  | 16: PC8  | 20: PD8  | 24: PD12 | 28: PF0  | Wide timer 0 Com-    |

|               | 1: PB9  | 5: PB13 | 9: PC1   | 13: PC5  | 17: PC9  | 21: PD9  | 25: PD13 | 29: PF1  | plimentary Dead      |

|               | 2: PB10 | 6: PB14 | 10: PC2  | 14: PC6  | 18: PC10 | 22: PD10 | 26: PD14 | 30: PF2  | Time Insertion       |

|               | 3: PB11 | 7: PB15 | 11: PC3  | 15: PC7  | 19: PC11 | 23: PD11 | 27: PD15 | 31: PF3  | channel 2.           |

| WTIM1_CC0     | 0: PB12 | 4: PC0  | 8: PC4   | 12: PC8  | 16: PD8  | 20: PD12 | 24: PF0  | 28: PF4  | Wide timer 1 Cap-    |

|               | 1: PB13 | 5: PC1  | 9: PC5   | 13: PC9  | 17: PD9  | 21: PD13 | 25: PF1  | 29: PF5  | ture Compare in-     |

|               | 2: PB14 | 6: PC2  | 10: PC6  | 14: PC10 | 18: PD10 | 22: PD14 | 26: PF2  | 30: PF6  | put / output channel |

|               | 3: PB15 | 7: PC3  | 11: PC7  | 15: PC11 | 19: PD11 | 23: PD15 | 27: PF3  | 31: PF7  | 0.                   |

| WTIM1_CC1     | 0: PB14 | 4: PC2  | 8: PC6   | 12: PC10 | 16: PD10 | 20: PD14 | 24: PF2  | 28: PF6  | Wide timer 1 Cap-    |

|               | 1: PB15 | 5: PC3  | 9: PC7   | 13: PC11 | 17: PD11 | 21: PD15 | 25: PF3  | 29: PF7  | ture Compare in-     |

|               | 2: PC0  | 6: PC4  | 10: PC8  | 14: PD8  | 18: PD12 | 22: PF0  | 26: PF4  | 30: PF8  | put / output channel |

|               | 3: PC1  | 7: PC5  | 11: PC9  | 15: PD9  | 19: PD13 | 23: PF1  | 27: PF5  | 31: PF9  | 1.                   |

| WTIM1_CC2     | 0: PC0  | 4: PC4  | 8: PC8   | 12: PD8  | 16: PD12 | 20: PF0  | 24: PF4  | 28: PF8  | Wide timer 1 Cap-    |

|               | 1: PC1  | 5: PC5  | 9: PC9   | 13: PD9  | 17: PD13 | 21: PF1  | 25: PF5  | 29: PF9  | ture Compare in-     |

|               | 2: PC2  | 6: PC6  | 10: PC10 | 14: PD10 | 18: PD14 | 22: PF2  | 26: PF6  | 30: PF10 | put / output channel |

|               | 3: PC3  | 7: PC7  | 11: PC11 | 15: PD11 | 19: PD15 | 23: PF3  | 27: PF7  | 31: PF11 | 2.                   |

| WTIM1_CC3     | 0: PC2  | 4: PC6  | 8: PC10  | 12: PD10 | 16: PD14 | 20: PF2  | 24: PF6  | 28: PF10 | Wide timer 1 Cap-    |

|               | 1: PC3  | 5: PC7  | 9: PC11  | 13: PD11 | 17: PD15 | 21: PF3  | 25: PF7  | 29: PF11 | ture Compare in-     |

|               | 2: PC4  | 6: PC8  | 10: PD8  | 14: PD12 | 18: PF0  | 22: PF4  | 26: PF8  | 30: PF12 | put / output channel |

|               | 3: PC5  | 7: PC9  | 11: PD9  | 15: PD13 | 19: PF1  | 23: PF5  | 27: PF9  | 31: PF13 | 3.                   |

### 6.4 Analog Port (APORT) Client Maps

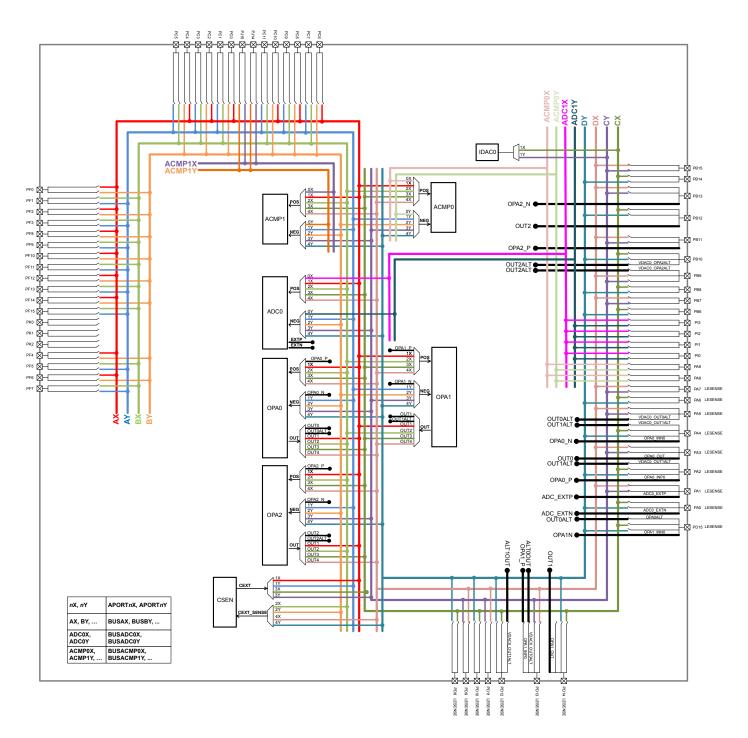

The Analog Port (APORT) is an infrastructure used to connect chip pins with on-chip analog clients such as analog comparators, ADCs, DACs, etc. The APORT consists of a set of shared buses, switches, and control logic needed to configurably implement the signal routing. Figure 6.3 APORT Connection Diagram on page 111 Shows the APORT routing for this device family. A complete description of APORT functionality can be found in the Reference Manual.

Figure 6.3. APORT Connection Diagram

Client maps for each analog circuit using the APORT are shown in the following tables. The maps are organized by bus, and show the peripheral's port connection, the shared bus, and the connection from specific bus channel numbers to GPIO pins.

In general, enumerations for the pin selection field in an analog peripheral's register can be determined by finding the desired pin connection in the table and then combining the value in the Port column (APORT\_\_), and the channel identifier (CH\_\_). For example, if pin

| Port           | Bus   | CH31 | CH30 | CH29 | CH28 | CH27 | CH26 | CH25 | CH24 | CH23 | CH22 | CH21 | CH20 | CH19 | CH18 | CH17 | CH16 | CH15 | CH14 | CH13 | CH12 | CH11 | CH10 | CH9 | CH8 | CH7  | CH6  | CH5  | CH4  | CH3  | CH2  | CH1 | CH0 |

|----------------|-------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----|-----|------|------|------|------|------|------|-----|-----|

| OPA0_N         |       |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |     |      |      |      |      |      |      |     |     |

| APORT1Y        | BUSAY | PF15 |      | PF13 |      | PF11 |      | PF9  |      | PF7  |      | PF5  |      | PF3  |      | PF1  |      |      |      |      |      | PC11 |      | PC9 |     | PC7  |      | PC5  |      | PC3  |      | PC1 |     |

| APORT2Y        | BUSBY |      | PF14 |      | PF12 |      | PF10 |      | PF8  |      | PF6  |      | PF4  |      | PF2  |      | PF0  |      |      |      |      |      | PC10 |     | PC8 |      | 9CG  |      | PC4  |      | PC2  |     | PC0 |

| <b>APORT3Y</b> | BUSCY | PB15 |      | PB13 |      | PB11 |      | PB9  |      | PB7  |      |      |      |      |      |      |      | PA7  |      | PA5  |      | PA3  |      | PA1 |     | PD15 |      | PD13 |      | PD11 |      | PD9 |     |

| APORT4Y        | BUSDY |      | PB14 |      | PB12 |      | PB10 |      | PB8  |      | PB6  |      |      |      |      |      |      |      | PA6  |      | PA4  |      | PA2  |     | PA0 |      | PD14 |      | PD12 |      | PD10 |     | PD8 |

| OF             | A0_   | P    |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |     |      |      |      |      |      |      |     |     |

| APORT1X        | BUSAX |      | PF14 |      | PF12 |      | PF10 |      | PF8  |      | PF6  |      | PF4  |      | PF2  |      | PF0  |      |      |      |      |      | PC10 |     | PC8 |      | PC6  |      | PC4  |      | PC2  |     | PC0 |

| APORT2X        | BUSBX | PF15 |      | PF13 |      | PF11 |      | PF9  |      | PF7  |      | PF5  |      | PF3  |      | PF1  |      |      |      |      |      | PC11 |      | PC9 |     | PC7  |      | PC5  |      | PC3  |      | PC1 |     |

| APORT3X        | BUSCX |      | PB14 |      | PB12 |      | PB10 |      | PB8  |      | PB6  |      |      |      |      |      |      |      | PA6  |      | PA4  |      | PA2  |     | PA0 |      | PD14 |      | PD12 |      | PD10 |     | PD8 |

| APORT4X        | BUSDX | PB15 |      | PB13 |      | PB11 |      | PB9  |      | PB7  |      |      |      |      |      |      |      | PA7  |      | PA5  |      | PA3  |      | PA1 |     | PD15 |      | PD13 |      | PD11 |      | PD9 |     |

# Table 6.11. VDAC0 / OPA Bus and Pin Mapping

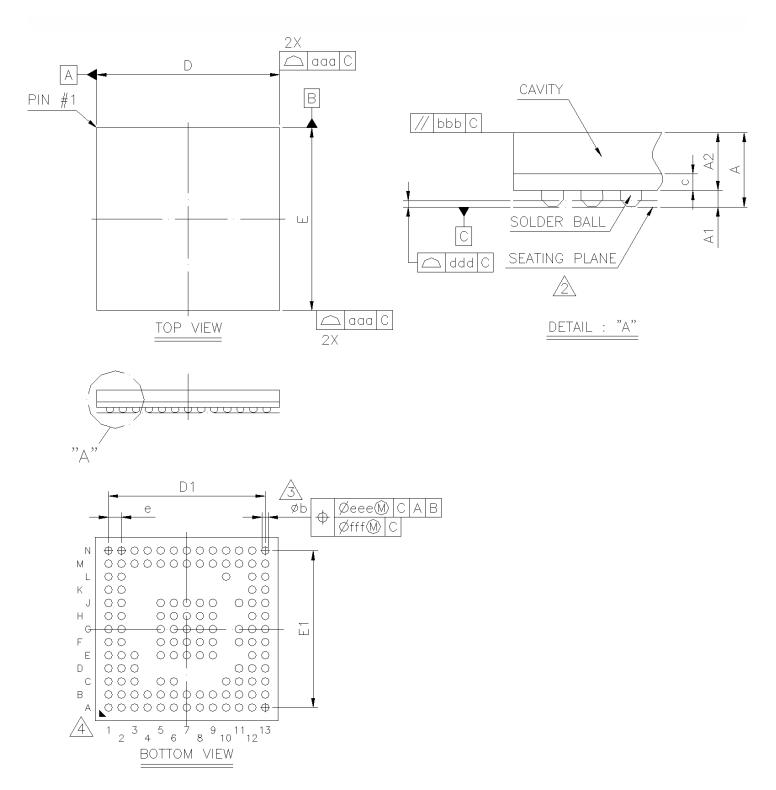

## 7. BGA125 Package Specifications

### 7.1 BGA125 Package Dimensions

Figure 7.1. BGA125 Package Drawing

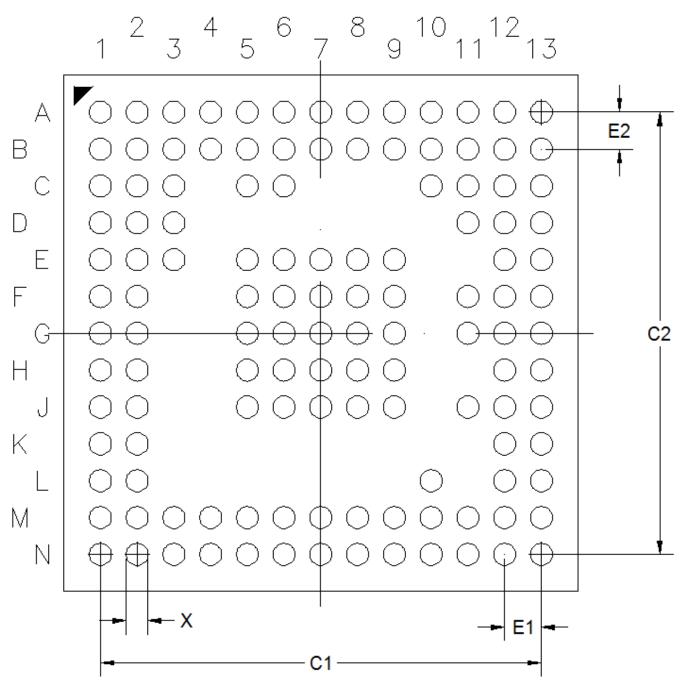

### 7.2 BGA125 PCB Land Pattern

Figure 7.2. BGA125 PCB Land Pattern Drawing