Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

E·XFl

| betans                  |                                                            |

|-------------------------|------------------------------------------------------------|

| Product Status          | Active                                                     |

| Туре                    | Fixed Point                                                |

| Interface               | Host Interface, SSI, SCI                                   |

| Clock Rate              | 200MHz                                                     |

| Non-Volatile Memory     | ROM (576B)                                                 |

| On-Chip RAM             | 576kB                                                      |

| Voltage - I/O           | 3.30V                                                      |

| Voltage - Core          | 1.60V                                                      |

| Operating Temperature   | -40°C ~ 100°C                                              |

| Mounting Type           | Surface Mount                                              |

| Package / Case          | 196-LBGA                                                   |

| Supplier Device Package | 196-MAPBGA (15x15)                                         |

| Purchase URL            | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=dsp56321vf200 |

|                         |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Feature                      | Description                                                                                                                                                                  |                                                                                                                                                                                                                                                                         |                      |                                      |                      |             |         |      |  |  |  |  |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------------------|----------------------|-------------|---------|------|--|--|--|--|

|                              | <ul> <li>192 × 24-bit bootstrap ROM</li> <li>192 K × 24-bit RAM total</li> <li>Program RAM, instruction cache, X data RAM, and Y data RAM sizes are programmable:</li> </ul> |                                                                                                                                                                                                                                                                         |                      |                                      |                      |             |         |      |  |  |  |  |

|                              | Program RAM<br>Size                                                                                                                                                          | Instruction<br>Cache Size                                                                                                                                                                                                                                               | X Data RAM<br>Size*  | Y Data RAM<br>Size*                  | Instruction<br>Cache | MSW2        | MSW1    | MSWO |  |  |  |  |

|                              | $32 \text{ K} \times 24 \text{-bit}$                                                                                                                                         | 0                                                                                                                                                                                                                                                                       | 80 K × 24-bit        | 80 K × 24-bit                        | disabled             | 0           | 0       | 0    |  |  |  |  |

|                              | 31 K × 24-bit                                                                                                                                                                | $1024 \times 24$ -bit                                                                                                                                                                                                                                                   | 80 K × 24-bit        | 80 K × 24-bit                        | enabled              | 0           | 0       | 0    |  |  |  |  |

|                              | 40 K × 24-bit                                                                                                                                                                | 0                                                                                                                                                                                                                                                                       | 76 K × 24-bit        | 76 K × 24-bit                        | disabled             | 0           | 0       | 1    |  |  |  |  |

|                              | $39 \text{ K} \times 24 \text{-bit}$                                                                                                                                         | $1024 \times 24$ -bit                                                                                                                                                                                                                                                   | 76 K × 24-bit        | 76 K × 24-bit                        | enabled              | 0           | 0       | 1    |  |  |  |  |

|                              | 48 K × 24-bit                                                                                                                                                                | 0                                                                                                                                                                                                                                                                       | 72 K $\times$ 24-bit | $72 \text{ K} \times 24 \text{-bit}$ | disabled             | 0           | 1       | 0    |  |  |  |  |

|                              | 47 K × 24-bit                                                                                                                                                                | $1024 \times 24$ -bit                                                                                                                                                                                                                                                   | 72 K $\times$ 24-bit | $72 \text{ K} \times 24$ -bit        | enabled              | 0           | 1       | 0    |  |  |  |  |

| Internal Memories            | 64 K × 24-bit                                                                                                                                                                | 0                                                                                                                                                                                                                                                                       | 64 K × 24-bit        | $64 \text{ K} \times 24$ -bit        | disabled             | 0           | 1       | 1    |  |  |  |  |

|                              | 63 K × 24-bit                                                                                                                                                                | $1024 \times 24$ -bit                                                                                                                                                                                                                                                   | 64 K $\times$ 24-bit | $64 \text{ K} \times 24$ -bit        | enabled              | 0           | 1       | 1    |  |  |  |  |

|                              | $72 \text{ K} \times 24 \text{-bit}$                                                                                                                                         | 0                                                                                                                                                                                                                                                                       | 60 K × 24-bit        | 60 K × 24-bit                        | disabled             | 1           | 0       | 0    |  |  |  |  |

|                              | 71 K × 24-bit                                                                                                                                                                | $1024 \times 24$ -bit                                                                                                                                                                                                                                                   | 60  K 	imes 24-bit   | 60 K × 24-bit                        | enabled              | 1           | 0       | 0    |  |  |  |  |

|                              | 80 K × 24-bit                                                                                                                                                                | 0                                                                                                                                                                                                                                                                       | 56 K $\times$ 24-bit | 56 K × 24-bit                        | disabled             | 1           | 0       | 1    |  |  |  |  |

|                              | $79 \text{ K} \times 24 \text{-bit}$                                                                                                                                         | $1024 \times 24$ -bit                                                                                                                                                                                                                                                   | 56 K $\times$ 24-bit | 56 K × 24-bit                        | enabled              | 1           | 0       | 1    |  |  |  |  |

|                              | 96 K × 24-bit                                                                                                                                                                | 0                                                                                                                                                                                                                                                                       | 48 K $\times$ 24-bit | 48 K × 24-bit                        | disabled             | 1           | 1       | 0    |  |  |  |  |

|                              | 95 K $\times$ 24-bit                                                                                                                                                         | $1024 \times 24$ -bit                                                                                                                                                                                                                                                   | 48 K $\times$ 24-bit | 48 K $\times$ 24-bit                 | enabled              | 1           | 1       | 0    |  |  |  |  |

|                              | 112 K × 24-bit                                                                                                                                                               | 0                                                                                                                                                                                                                                                                       | 40 K $\times$ 24-bit | 40 K $\times$ 24-bit                 | disabled             | 1           | 1       | 1    |  |  |  |  |

|                              | 111 K × 24-bit                                                                                                                                                               | $1024 \times 24$ -bit                                                                                                                                                                                                                                                   | 40 K $\times$ 24-bit | 40 K $\times$ 24-bit                 | enabled              | 1           | 1       | 1    |  |  |  |  |

|                              | *Includes 12 K >                                                                                                                                                             | < 24-bit shared m                                                                                                                                                                                                                                                       | emory (that is, 24   | 4 K total memory                     | shared by the        | e core and  | the EFC | OP)  |  |  |  |  |

| External Memory<br>Expansion | <ul> <li>Data memory<br/>lines</li> <li>Program mem<br/>address lines</li> <li>External memory</li> <li>Chip select log</li> </ul>                                           | bit words memor                                                                                                                                                                                                                                                         | y space using        | the stand                            |                      |             |         |      |  |  |  |  |

| Power Dissipation            | <ul><li>Wait and Stop</li><li>Fully static des</li></ul>                                                                                                                     | <ul> <li>Very low-power CMOS design</li> <li>Wait and Stop low-power standby modes</li> <li>Fully static design specified to operate down to 0 Hz (dc)</li> <li>Optimized power management circuitry (instruction-dependent, peripheral-dependent, and mode-</li> </ul> |                      |                                      |                      |             |         |      |  |  |  |  |

| Packaging                    | Molded array                                                                                                                                                                 | plastic-ball grid a                                                                                                                                                                                                                                                     | rray (MAP-BGA)       | package in lead-f                    | ree or lead-be       | earing vers | sions.  |      |  |  |  |  |

#### Table 1. DSP56321 Features (Continued)

# **Target Applications**

DSP56321 applications require high performance, low power, small packaging, and a large amount of internal memory. The EFCOP can accelerate general filtering applications. Examples include:

- Wireless and wireline infrastructure applications

- Multi-channel wireless local loop systems

- Security encryption systems

- Home entertainment systems

- DSP resource boards

- High-speed modem banks

- IP telephony

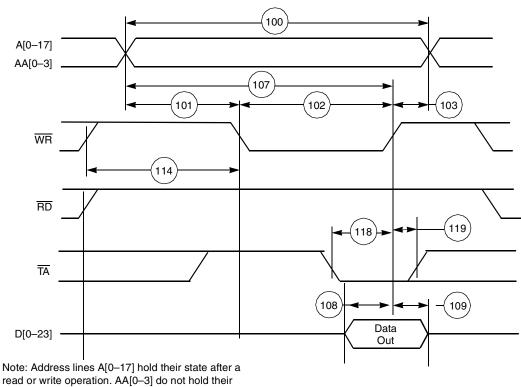

# 1.4 External Memory Expansion Port (Port A)

**Note:** When the DSP56321 enters a low-power standby mode (stop or wait), it releases bus mastership and tristates the relevant Port A signals: A[0–17], D[0–23], AA[0–3], RD, WR, BB.

## 1.4.1 External Address Bus

| Signal Name | Туре   | State During<br>Reset, Stop,<br>or Wait | Signal Description                                                                                                                                                                                                                                                                                        |

|-------------|--------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A[0–17]     | Output | Tri-stated                              | Address Bus—When the DSP is the bus master, A[0–17] are active-high outputs that specify the address for external program and data memory accesses. Otherwise, the signals are tri-stated. To minimize power dissipation, A[0–17] do not change state when external memory spaces are not being accessed. |

Table 1-5. External Address Bus Signals

### 1.4.2 External Data Bus

Table 1-6.

External Data Bus Signals

| Signal Name | Туре          | State During<br>Reset | State During<br>Stop or Wait                                           | Signal Description                                                                                                                                                                                                                                                                                                                                                |

|-------------|---------------|-----------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[0–23]     | Input/ Output | Ignored Input         | Last state:<br><i>Input</i> : Ignored<br><i>Output</i> :<br>Last value | <b>Data Bus</b> —When the DSP is the bus master, D[0–23] are active-high, bidirectional input/outputs that provide the bidirectional data bus for external program and data memory accesses. Otherwise, D[0–23] drivers are tristated. If the last state is output, these lines have weak keepers to maintain the last output state if all drivers are tristated. |

### 1.4.3 External Bus Control

| Table 1-7. | External Bus Control Signals |

|------------|------------------------------|

|------------|------------------------------|

| Signal Name | Туре   | State During<br>Reset, Stop, or<br>Wait | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|--------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |        |                                         | Address Attribute—When defined as AA, these signals can be used as chip selects or additional address lines. The default use defines a priority scheme under which only one AA signal can be asserted at a time. Setting the AA priority disable (APD) bit (Bit 14) of the Operating Mode Register, the priority mechanism is disabled and the lines can be used together as four external lines that can be decoded externally into 16 chip select signals. |

| RD          | Output | Tri-stated                              | <b>Read Enable</b> —When the DSP is the bus master, $\overline{RD}$ is an active-low output that is asserted to read external memory on the data bus (D[0–23]). Otherwise, $\overline{RD}$ is tri-stated.                                                                                                                                                                                                                                                    |

| WR          | Output | Tri-stated                              | <b>Write Enable</b> —When the DSP is the bus master, $\overline{WR}$ is an active-low output that is asserted to write external memory on the data bus (D[0–23]). Otherwise, the signals are tri-stated.                                                                                                                                                                                                                                                     |

# 1.5 Interrupt and Mode Control

The interrupt and mode control signals select the chip operating mode as it comes out of hardware reset. After **RESET** is deasserted, these inputs are hardware interrupt request lines.

| Signal Name | Туре  | State During<br>Reset    | Signal Description                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|-------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODA        | Input | Schmitt-trigger<br>Input | <b>Mode Select A</b> —MODA, MODB, MODC, and MODD select one of 16 initial chip operating modes, latched into the Operating Mode Register when the RESET signal is deasserted.                                                                                                                                                                                                            |

| ĪRQĀ        | Input |                          | <b>External Interrupt Request A</b> —After reset, this input becomes a level-<br>sensitive or negative-edge-triggered, maskable interrupt request input during<br>normal instruction processing. If the processor is in the STOP or WAIT<br>standby state and IRQA is asserted, the processor exits the STOP or WAIT<br>state.                                                           |

| MODB        | Input | Schmitt-trigger<br>Input | <b>Mode Select B</b> —MODA, MODB, MODC, and MODD select one of 16 initial chip operating modes, latched into the Operating Mode Register when the RESET signal is deasserted.                                                                                                                                                                                                            |

| ĪRQB        | Input |                          | <b>External Interrupt Request B</b> —After reset, this input becomes a level-<br>sensitive or negative-edge-triggered, maskable interrupt request input during<br>normal instruction processing. If the processor is in the WAIT standby state<br>and IRQB is asserted, the processor exits the WAIT state.                                                                              |

| MODC        | Input | Schmitt-trigger<br>Input | <b>Mode Select C</b> —MODA, MODB, MODC, and MODD select one of 16 initial chip operating modes, latched into the Operating Mode Register when the RESET signal is deasserted.                                                                                                                                                                                                            |

| IRQC        | Input |                          | <b>External Interrupt Request C</b> —After reset, this input becomes a level-<br>sensitive or negative-edge-triggered, maskable interrupt request input during<br>normal instruction processing. If the processor is in the WAIT standby state<br>and IRQC is asserted, the processor exits the WAIT state.                                                                              |

| MODD        | Input | Schmitt-trigger<br>Input | <b>Mode Select D</b> —MODA, MODB, MODC, and MODD select one of 16 initial chip operating modes, latched into the Operating Mode Register when the RESET signal is deasserted.                                                                                                                                                                                                            |

| ĪRQD        | Input |                          | <b>External Interrupt Request D</b> —After reset, this input becomes a level-<br>sensitive or negative-edge-triggered, maskable interrupt request input during<br>normal instruction processing. If the processor is in the WAIT standby state<br>and IRQD is asserted, the processor exits the WAIT state.                                                                              |

| RESET       | Input | Schmitt-trigger<br>Input | <b>Reset</b> —Places the chip in the Reset state and resets the internal phase generator. The Schmitt-trigger input allows a slowly rising input (such as a capacitor charging) to reset the chip reliably. When the RESET signal is deasserted, the initial chip operating mode is latched from the MODA, MODB, MODC, and MODD inputs. The RESET signal must be asserted after powerup. |

| PINIT       | Input | Schmitt-trigger<br>Input | <b>PLL Initial</b> —During assertion of RESET, the value of PINIT determines whether the DPLL is enabled or disabled.                                                                                                                                                                                                                                                                    |

| NMI         | Input |                          | Nonmaskable Interrupt—After RESET deassertion and during normal instruction processing, this Schmitt-trigger input is the negative-edge-triggered NMI request.                                                                                                                                                                                                                           |

## 2.2 Thermal Characteristics

| Thermal Resistance Characteristic                                                 | Symbol                 | MAP-BGA<br>Value | Unit |

|-----------------------------------------------------------------------------------|------------------------|------------------|------|

| Junction-to-ambient, natural convection, single-layer board (1s) <sup>1,2</sup>   | R <sub>θJA</sub>       | 44               | °C/W |

| Junction-to-ambient, natural convection, four-layer board (2s2p) <sup>1,3</sup>   | R <sub>θJMA</sub>      | 25               | °C/W |

| Junction-to-ambient, @200 ft/min air flow, single-layer board (1s) <sup>1,3</sup> | $R_{\theta JMA}$       | 35               | °C/W |

| Junction-to-ambient, @200 ft/min air flow, four-layer board (2s2p) <sup>1,3</sup> | $R_{	extsf{	heta}JMA}$ | 22               | °C/W |

| Junction-to-board <sup>4</sup>                                                    | R <sub>θJB</sub>       | 13               | °C/W |

| Junction-to-case thermal resistance <sup>5</sup>                                  | R <sub>θJC</sub>       | 7                | °C/W |

Table 2-2. Thermal Characteristics

**Notes:** 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

2. Per SEMI G38-87 and JEDEC JESD51-2 with the single-layer board horizontal.

**3.** Per JEDEC JESD51-6 with the board horizontal.

4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

# **2.3 DC Electrical Characteristics**

| Characteristics                                                                                                                                                                               | Symbol                                                  | Min                                   | Тур        | Max                                                                     | Unit        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------|------------|-------------------------------------------------------------------------|-------------|

| Supply voltage <sup>1</sup> :<br>• Core (V <sub>CCQL</sub> )<br>• I/O (V <sub>CCQH</sub> , V <sub>CCA</sub> , V <sub>CCD</sub> , V <sub>CCC</sub> , V <sub>CCH</sub> , and V <sub>CCS</sub> ) |                                                         | 1.5<br>3.0                            | 1.6<br>3.3 | 1.7<br>3.6                                                              | V<br>V      |

| Input high voltage<br>• D[0-23], BG, BB, TA<br>• MOD/IRQ <sup>2</sup> RESET, PINIT/NMI and all<br>JTAG/ESSI/SCI/Timer/HI08 pins<br>• EXTAL <sup>9</sup>                                       | V <sub>IH</sub><br>V <sub>IHP</sub><br>V <sub>IHX</sub> | 2.0<br>2.0<br>0.8 × V <sub>CCQH</sub> | <br>       | V <sub>CCQH</sub> + 0.3<br>V <sub>CCQH</sub> + 0.3<br>V <sub>CCQH</sub> | ><br>><br>> |

| Input low voltage<br>• D[0–23], BG, BB, TA, MOD/IRQ <sup>2</sup> , RESET, PINIT<br>• All JTAG/ESSI/SCI/Timer/HI08 pins<br>• EXTAL <sup>9</sup>                                                | V <sub>IL</sub><br>V <sub>ILP</sub><br>V <sub>ILX</sub> | -0.3<br>-0.3<br>-0.3                  |            | 0.8<br>0.8<br>$0.2 \times V_{CCQH}$                                     | V<br>V<br>V |

| Input leakage current                                                                                                                                                                         | I <sub>IN</sub>                                         | -10                                   | —          | 10                                                                      | μΑ          |

| High impedance (off-state) input current<br>(@ 2.4 V / 0.4 V)                                                                                                                                 | I <sub>TSI</sub>                                        | -10                                   | —          | 10                                                                      | μA          |

| Output high voltage <sup>8</sup><br>• TTL $(I_{OH} = -0.4 \text{ mA})^6$<br>• CMOS $(I_{OH} = -10 \mu A)^6$                                                                                   | V <sub>OH</sub>                                         | 2.4<br>V <sub>CCQH</sub> – 0.01       |            |                                                                         | V<br>V      |

| Output low voltage <sup>8</sup><br>• TTL ( $I_{OL} = 3.0 \text{ mA}$ ) <sup>6</sup><br>• CMOS ( $I_{OL} = 10 \text{ µA}$ ) <sup>6</sup>                                                       | V <sub>OL</sub>                                         |                                       | —          | 0.4<br>0.01                                                             | V<br>V      |

| Table 2-3. | DC Electrical | Characteristics <sup>7</sup> |

|------------|---------------|------------------------------|

|------------|---------------|------------------------------|

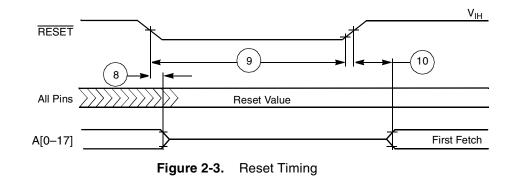

### Table 2-7. Reset, Stop, Mode Select, and Interrupt Timing<sup>5</sup> (CONTINUED)

|        |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                        | 200 MHz                                                                                   |                                                                                                                          | 220 MHz                                                                                                       |                                                                                                                  | 240                                                                                      | 240 MHz                                                                 |                                                            | 275 MHz                                                     |                                              |

|--------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------|

| No.    |                      | Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Expression                                                                                                                                                                                                                                                                                                                                                                             | Min                                                                                       | Max                                                                                                                      | Min                                                                                                           | Max                                                                                                              | Min                                                                                      | Мах                                                                     | Min                                                        | Мах                                                         | Unit                                         |

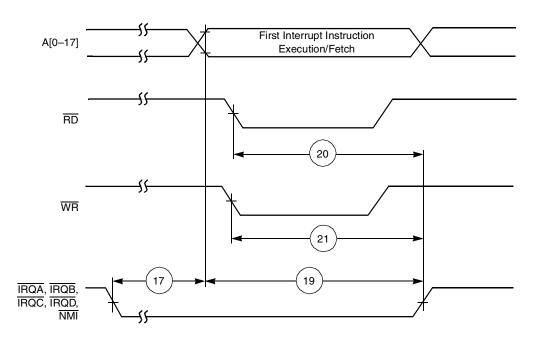

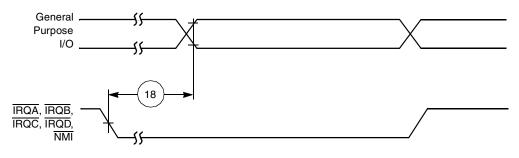

| Notes: | 1.                   | When fast interrupts are used and IRQA, IRQB, IRQC, and IRQD are defined as level-sensitive, timings 19 through 21 apply to prevent multiple interrupt service. To avoid these timing restrictions, the deasserted Edge-triggered mode is recommended when fast interrupts are used. Long interrupts are recommended for Level-sensitive mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                           |                                                                                                                          |                                                                                                               |                                                                                                                  |                                                                                          |                                                                         |                                                            |                                                             |                                              |

|        | 2.                   | This timing depends on seve<br>• For DPLL disable, using int<br>Bit 1 = 0), a stabilization dela<br>Stop delay (Operating Mode<br>it is not recommended, and t<br>• For DPLL disable, using inte<br>delay is required and recove<br>• For DPLL disable, using ex<br>PCTL Bit 1 and Operating M<br>• For DPLL enable, if PCTL E<br>DPLL lock procedure duration<br>by the stop delay counter. St<br>• The DPLT value for DPLL of                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ral settings:<br>ernal oscillator (DPLL Contr<br>by is required to assure that<br>Register Bit 6 = 0) provides<br>hese specifications do not g<br>ernal oscillator (PCTL Bit 2 =<br>ry is minimal (Operating Mo<br>ternal clock (PCTL Bit 2 = 1<br>ode Register Bit 6 settings.<br>Bit 1 is 0, the DPLL is shut d<br>n is defined in <b>Table 2-6</b> and<br>op recovery ends when the | rol Regi<br>the ose<br>the pro-<br>guarant<br>= 0) and<br>ode Reg<br>l), no si<br>lown du | ister (PC<br>cillator is<br>oper dela<br>cee timing<br>d oscillat<br>gister Bit<br>tabilizatio<br>uring Sto<br>e refined | TL) Bit 2<br>stable I<br>ay. While<br>gs for th<br>or enabl<br>6 settin<br>on delay<br>p. Recov<br>after sili | 2 = 0) an<br>before pri<br>e Operat<br>at case.<br>ed durin<br>g is igno<br>r is requi<br>vering fro<br>con chai | d oscilla<br>rograms<br>ing Mod<br>g Stop (I<br>red).<br>red and<br>om Stop<br>racteriza | are exec<br>e Registe<br>PCTL Bit<br>recovery<br>requires<br>tion. This | cuted. Re<br>er Bit 6 =<br>1 = 1), r<br>time is<br>the DPI | esetting<br>= 1 can t<br>no stabili<br>defined<br>_L to loc | the<br>be set<br>izatior<br>by the<br>k. The |

|        | 3.<br>4.<br>5.<br>6. | <ol> <li>Periodically sampled and not 100 percent tested.</li> <li>For an external clock generator, RESET duration is measured while RESET is asserted, V<sub>CC</sub> is valid, and the EXTAL active and valid.</li> <li>For an internal oscillator, RESET duration is measured while RESET is asserted and V<sub>CC</sub> is valid. The specified timin the crystal oscillator stabilization time after power-up. This number is affected both by the specifications of the crystal components connected to the oscillator and reflects worst case conditions. When the V<sub>CC</sub> is valid, but the other "required RESET duration" conditions (as specified above) have not been yet m device circuitry is in an uninitialized state that can result in significant power consumption and heat-up. Designs should this state to the shortest possible duration.</li> </ol> |                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                           |                                                                                                                          |                                                                                                               |                                                                                                                  |                                                                                          |                                                                         | timing re<br>/stal and<br>et met, t                        | eflects<br>d othe                                           |                                              |

|        | 7.                   | WS = number of wait states<br>Use the expression to compu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | (measured in clock cycles,                                                                                                                                                                                                                                                                                                                                                             | number                                                                                    | · · · · C).                                                                                                              |                                                                                                               |                                                                                                                  |                                                                                          |                                                                         |                                                            |                                                             |                                              |

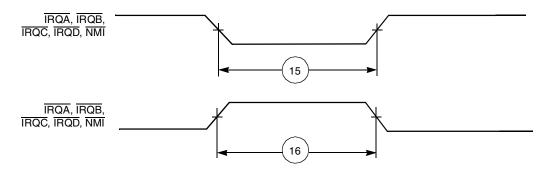

a) First Interrupt Instruction Execution

b) General-Purpose I/O

Figure 2-4. External Fast Interrupt Timing

Figure 2-5. External Interrupt Timing (Negative Edge-Triggered)

state after a read or write operation.

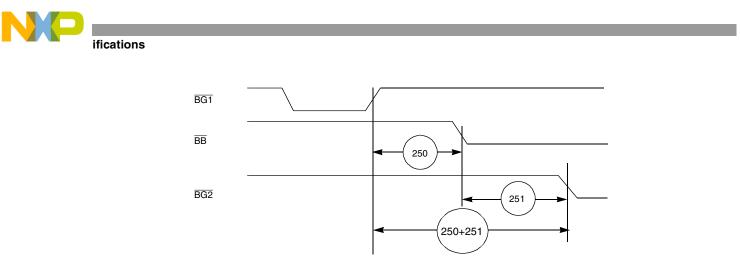

### 2.4.5.2 Asynchronous Bus Arbitration Timings

| No.   | Characteristics                                                                                      | Expression   | 200 MHz |      | 220 MHz |      | 240 MHz |      | 275 Mhz |      | Uni |

|-------|------------------------------------------------------------------------------------------------------|--------------|---------|------|---------|------|---------|------|---------|------|-----|

|       |                                                                                                      |              | Min     | Max  | Min     | Max  | Min     | Max  | Min     | Max  | t   |

| 250   | $\overline{\text{BB}}$ assertion window from $\overline{\text{BG}}$ input deassertion.               | 2.5 × Tc + 5 |         | 17.5 |         | 16.4 | —       | 15.4 | —       | 14.1 | ns  |

| 251   | Delay from $\overline{BB}$ assertion to $\overline{BG}$ assertion                                    | 2 × Tc + 5   | 15      | —    | 14.1    |      | 13.3    |      | 12.27   | _    | ns  |

| Notes | Notes: 1. Bit 13 in the Operating Mode Register must be set to enable Asynchronous Arbitration mode. |              |         |      |         |      |         |      |         |      |     |

| Table 2-9. | Asynchronous | <b>Bus Timings</b> |

|------------|--------------|--------------------|

|------------|--------------|--------------------|

2. To guarantee timings 250 and 251, it is recommended that you assert non-overlapping BG inputs to different DSP56300 devices (on the same bus), as shown in Figure 2-12, where BG1 is the BG signal for one DSP56300 device while BG2 is the BG signal for a second DSP56300 device.

Figure 2-12. Asynchronous Bus Arbitration Timing

The asynchronous bus arbitration is enabled by internal synchronization circuits on  $\overline{BG}$  and  $\overline{BB}$  inputs. These synchronization circuits add delay from the external signal until it is exposed to internal logic. As a result of this delay, a DSP56300 part may assume mastership and assert  $\overline{BB}$ , for some time after  $\overline{BG}$  is deasserted. This is the reason for timing 250.

Once  $\overline{BB}$  is asserted, there is a synchronization delay from  $\overline{BB}$  assertion to the time this assertion is exposed to other DSP56300 components that are potential masters on the same bus. If  $\overline{BG}$  input is asserted before that time, and  $\overline{BG}$  is asserted and  $\overline{BB}$  is deasserted, another DSP56300 component may assume mastership at the same time. Therefore, some non-overlap period between one  $\overline{BG}$  input active to another  $\overline{BG}$  input active is required. Timing 251 ensures that overlaps are avoided.

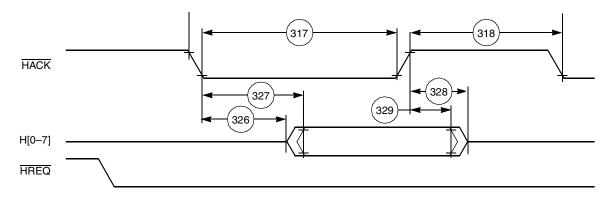

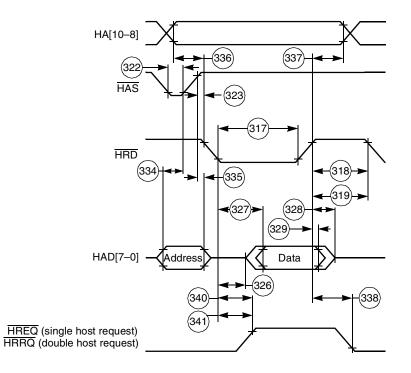

## 2.4.6 Host Interface Timing

| No. | Characteristic <sup>10</sup>                                                                                                                                                                                                                          | Expression                 | 200 MHz |     | 220 MHz |     | 240 MHz |     | 275 MHz |     | Uni |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------|-----|---------|-----|---------|-----|---------|-----|-----|

| NO. | Characteristic                                                                                                                                                                                                                                        | Expression                 | Min     | Max | Min     | Max | Min     | Max | Min     | Max | t   |

| 317 | Read data strobe assertion width <sup>5</sup><br>HACK assertion width                                                                                                                                                                                 | T <sub>C</sub> + 4.95      | 9.95    | _   | 9.05    | —   | 8.3     | _   | 7.77    |     | ns  |

| 318 | Read data strobe deassertion width <sup>5</sup><br>HACK deassertion width                                                                                                                                                                             |                            | 4.95    | _   | 4.5     | —   | 4.13    | —   | 4.0     | _   | ns  |

| 319 | Read data strobe deassertion width <sup>5</sup> after<br>"Last Data Register" reads <sup>8,11</sup> , or between two<br>consecutive CVR, ICR, or ISR reads <sup>3</sup><br>HACK deassertion width after "Last Data<br>Register" reads <sup>8,11</sup> | 2.5 × T <sub>C</sub> + 3.3 | 15.8    | _   | 14.7    | —   | 13.7    | _   | 12.39   |     | ns  |

| 320 | Write data strobe assertion width <sup>6</sup>                                                                                                                                                                                                        |                            | 6.6     | _   | 6.0     |     | 5.5     | _   | 5.1     |     | ns  |

| 321 | <ul> <li>Write data strobe deassertion width<sup>8</sup></li> <li>HACK write deassertion width</li> <li>after ICR, CVR and "Last Data Register"<br/>writes</li> </ul>                                                                                 | 2.5 × T <sub>C</sub> + 3.3 | 15.8    | _   | 14.7    | _   | 13.7    | _   | 12.39   | _   | ns  |

|     | <ul> <li>after IVR writes, or<br/>after TXH:TXM:TXL writes (with HLEND=<br/>0), or<br/>after TXL:TXM:TXH writes (with HLEND =<br/>1)</li> </ul>                                                                                                       |                            | 8.25    | _   | 7.5     | _   | 6.88    | _   | 6.28    | _   | ns  |

| 322 | HAS assertion width                                                                                                                                                                                                                                   |                            | 4.95    | —   | 4.5     | _   | 4.13    | _   | 4.0     | _   | ns  |

**Table 2-10.**Host Interface Timings<sup>1,2,12</sup>

Table 2-10.

Host Interface Timings<sup>1,2,12</sup> (Continued)

| No     |     | Characteristic <sup>10</sup> Expression                                                                                                                                                                                                                                                  | 200 MHz          |          | 220 MHz           |        | 240 MHz |         | 275 MHz |     | Uni |   |

|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------|-------------------|--------|---------|---------|---------|-----|-----|---|

| No.    |     |                                                                                                                                                                                                                                                                                          | Expression       | Min      | Max               | Min    | Max     | Min     | Max     | Min | Мах | t |

| Notes: | 1.  | See the Programmer's Model section in                                                                                                                                                                                                                                                    | n the chapter on | the HI08 | 3 in the <i>l</i> | DSP563 | 21 Refe | rence M | anual.  |     |     |   |

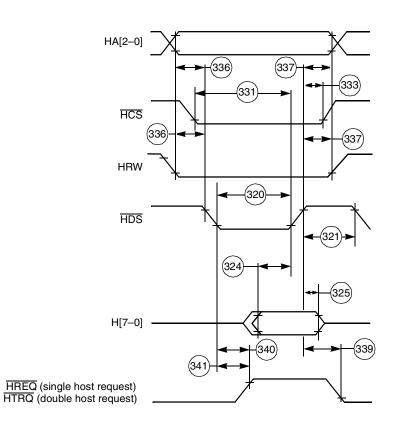

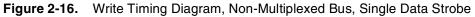

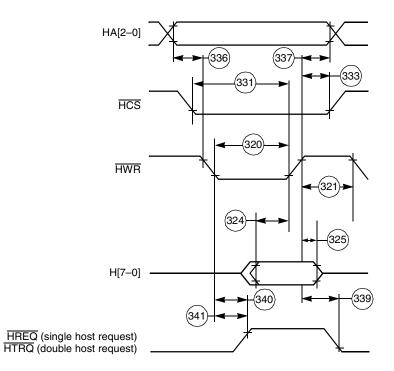

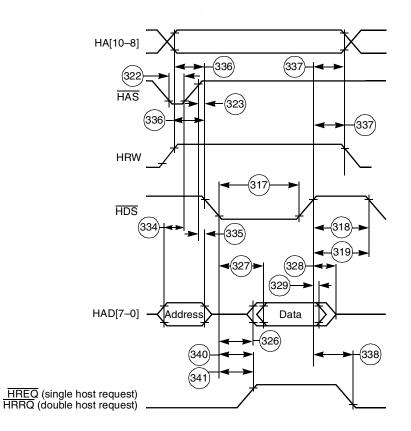

|        | 2.  | In the timing diagrams below, the controls pins are drawn as active low. The pin polarity is programmable.                                                                                                                                                                               |                  |          |                   |        |         |         |         |     |     |   |

|        | 3.  | This timing is applicable only if two consecutive reads from one of these registers are executed.                                                                                                                                                                                        |                  |          |                   |        |         |         |         |     |     |   |

|        | 4.  | The data strobe is Host Read (HRD) or Host Write (HWR) in the Dual Data Strobe mode and Host Data Strobe (HDS) in the Single Data Strobe mode.                                                                                                                                           |                  |          |                   |        |         |         |         |     |     |   |

|        | 5.  | The read data strobe is HRD in the Dual Data Strobe mode and HDS in the Single Data Strobe mode.                                                                                                                                                                                         |                  |          |                   |        |         |         |         |     |     |   |

|        | 6.  | The write data strobe is HWR in the Dual Data Strobe mode and HDS in the Single Data Strobe mode.                                                                                                                                                                                        |                  |          |                   |        |         |         |         |     |     |   |

|        | 7.  | The host request is HREQ in the Single Host Request mode and HRRQ and HTRQ in the Double Host Request mode.                                                                                                                                                                              |                  |          |                   |        |         |         |         |     |     |   |

|        | 8.  | The "Last Data Register" is the register at address \$7, which is the last location to be read or written in data transfers. This is RXL/TXL in the Big Endian mode (HLEND = 0; HLEND is the Interface Control Register bit 7—ICR[7]), or RXH/TXH in the Little Endian mode (HLEND = 1). |                  |          |                   |        |         |         |         |     |     |   |

|        | 9.  | In this calculation, the host request signal is pulled up by a 4.7 k $\Omega$ resistor in the Open-drain mode.                                                                                                                                                                           |                  |          |                   |        |         |         |         |     |     |   |

|        | 10. | $V_{CCOH} = 3.3 V \pm 0.3 V$ , $V_{CCOL} = 1.6 V$                                                                                                                                                                                                                                        |                  |          |                   |        |         |         |         |     |     |   |

|        | 11. |                                                                                                                                                                                                                                                                                          |                  |          |                   |        |         |         |         |     |     |   |

|        | 12  | After the external host writes a new value to the ICR, the HI08 will be ready for operation after three DSP clock cycles $(3 \times Tc)$ .                                                                                                                                               |                  |          |                   |        |         |         |         |     |     |   |

Figure 2-13. Host Interrupt Vector Register (IVR) Read Timing Diagram

Figure 2-17. Write Timing Diagram, Non-Multiplexed Bus, Double Data Strobe

Figure 2-18. Read Timing Diagram, Multiplexed Bus, Single Data Strobe

Figure 2-19. Read Timing Diagram, Multiplexed Bus, Double Data Strobe

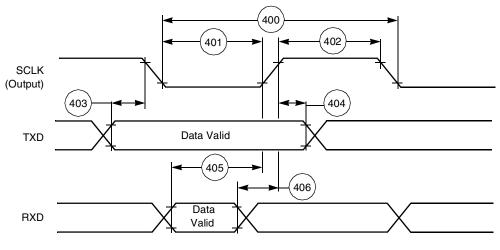

a) Internal Clock

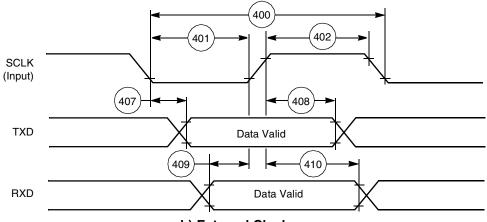

b) External Clock

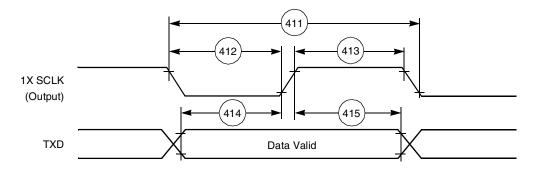

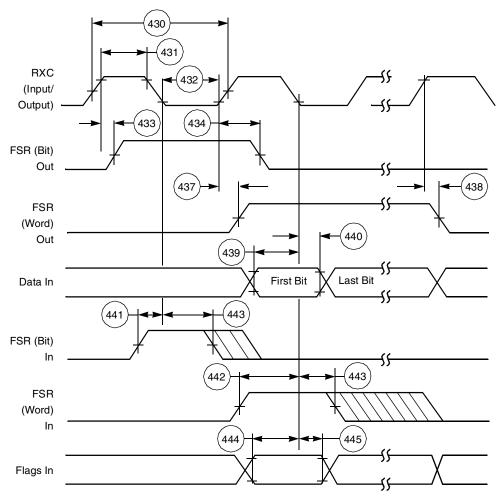

Figure 2-22. SCI Synchronous Mode Timing

Figure 2-23. SCI Asynchronous Mode Timing

### 2.4.9 Timer Timing

Table 2-13. Timer Timings

| No.     | Characteristics                                                                                                                                          | Expression                    | 200 MHz   |     | 220 MHz   |     | 240 MHz   |     | 240 MHz   |     | Unit |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------|-----|-----------|-----|-----------|-----|-----------|-----|------|

| NO.     |                                                                                                                                                          |                               | Min       | Max | Min       | Max | Min       | Max | Min       | Max | Unit |

| 480 T   | TIO Low                                                                                                                                                  | $2 \times T_{C} + 2.0$        | 12.0      |     | 11.1      | -   | 10.3      | —   | 9.27      | _   | ns   |

| 481 T   | TIO High                                                                                                                                                 | $2 \times T_{C} + 2.0$        | 12.0      |     | 11.1      |     | 10.3      | _   | 9.27      | _   | ns   |

| ri<br>a | Synchronous delay time from Timer input<br>rising edge to the external memory<br>address out valid caused by the first<br>nterrupt instruction execution | 10.25 × T <sub>C</sub> + 10.0 | 61.2<br>5 | _   | 56.6<br>4 | _   | 52.7<br>4 | —   | 47.2<br>7 | _   | ns   |

The maximum frequency of pulses generated by a timer will be defined after device characterization is completed.

In the timing diagrams below, TIO is drawn using the rising edge as the reference. TIO polarity is programmable in the Timer Control/Status Register (TCSR). Refer to the DSP56321 Reference Manual for details.

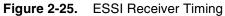

# 2.4.11 JTAG Timing

| NI - | Ob any standarding                                                         | All freq | All frequencies |        |  |  |

|------|----------------------------------------------------------------------------|----------|-----------------|--------|--|--|

| No.  | Characteristics                                                            | Min      | Max             | – Unit |  |  |

| 500  | TCK frequency of operation (1/( $T_C \times 3$ ); absolute maximum 22 MHz) | 0.0      | 22.0            | MHz    |  |  |

| 501  | TCK cycle time in Crystal mode                                             | 45.0     | _               | ns     |  |  |

| 502  | TCK clock pulse width measured at 1.6 V                                    | 20.0     | _               | ns     |  |  |

| 503  | TCK rise and fall times                                                    | 0.0      | 3.0             | ns     |  |  |

| 504  | Boundary scan input data setup time                                        | 5.0      | _               | ns     |  |  |

| 505  | Boundary scan input data hold time                                         | 24.0     | _               | ns     |  |  |

| 506  | TCK low to output data valid                                               | 0.0      | 40.0            | ns     |  |  |

| 507  | TCK low to output high impedance                                           | 0.0      | 40.0            | ns     |  |  |

| 508  | TMS, TDI data setup time                                                   | 5.0      | _               | ns     |  |  |

| 509  | TMS, TDI data hold time                                                    | 25.0     | _               | ns     |  |  |

| 510  | TCK low to TDO data valid                                                  | 0.0      | 44.0            | ns     |  |  |

| 511  | TCK low to TDO high impedance                                              | 0.0      | 44.0            | ns     |  |  |

| 512  | TRST assert time                                                           | 100.0    | —               | ns     |  |  |

| 513  | TRST setup time to TCK low                                                 | 40.0     | —               | ns     |  |  |

Table 2-14. JTAG Timing

Figure 2-28. Test Clock Input Timing Diagram

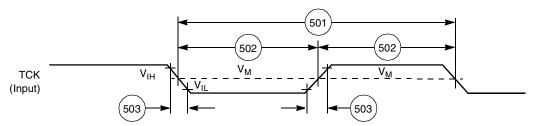

## 2.4.12 OnCE Module TimIng

DE

| No.   | Characteristics                                                                                                                                                              | Expression                  | All Freq | Unit |      |  |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|----------|------|------|--|--|

| NO.   | Characteristics                                                                                                                                                              | Expression                  | Min      | Max  | Unit |  |  |

| 500   | TCK frequency of operation (1/(T <sub>C</sub> $\times$ 3); maximum 22 MHz)                                                                                                   | Max 22.0 MHz                | 0.0      | 22.0 | MHz  |  |  |

| 514   | DE assertion time in order to enter Debug mode                                                                                                                               | $1.5 	imes T_{C} + 10.0$    | 20.0     | —    | ns   |  |  |

| 515   | Response time when DSP56321 is executing NOP instructions from internal memory                                                                                               | 5.5 × T <sub>C</sub> + 30.0 | —        | 67.0 | ns   |  |  |

| 516   | Debug acknowledge assertion time                                                                                                                                             | $3 \times T_{C} + 5.0$      | 25.0     | —    | ns   |  |  |

| Note: | : $V_{CCQH} = 3.3 \text{ V} \pm 0.3 \text{ V}, V_{CCQL} = 1.6 \text{ V} \pm 0.1 \text{ V}; T_J = -40^{\circ}\text{C} \text{ to } +100 ^{\circ}\text{C}, C_L = 50 \text{ pF}$ |                             |          |      |      |  |  |

Table 2-15.

OnCE Module Timing

Figure 2-32. OnCE—Debug Request

# 3.1 Package Description

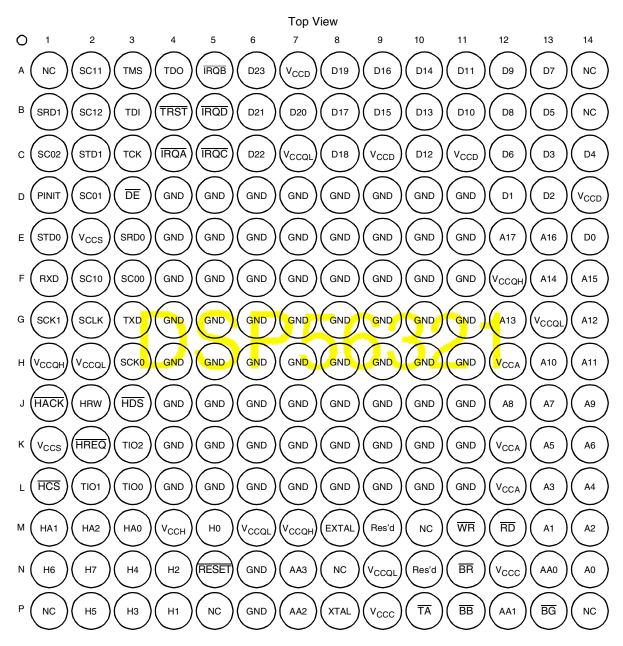

Top and bottom views of the MAP-BGA packages are shown in Figure 3-1 and Figure 3-2 with their pin-outs.

Figure 3-1. DSP56321 MAP-BGA Package, Top View

on Considerations

#### **Equation 4:** $I = 50 \times 10^{-12} \times 3.3 \times 33 \times 10^{6} = 5.48 \ mA$

The maximum internal current ( $I_{CCI}$ max) value reflects the typical possible switching of the internal buses on bestcase operation conditions—not necessarily a real application case. The typical internal current ( $I_{CCItyp}$ ) value reflects the average switching of the internal buses on typical operating conditions.

Perform the following steps for applications that require very low current consumption:

- **1.** Set the EBD bit when you are not accessing external memory.

- 2. Minimize external memory accesses, and use internal memory accesses.

- **3.** Minimize the number of pins that are switching.

- 4. Minimize the capacitive load on the pins.

- 5. Connect the unused inputs to pull-up or pull-down resistors.

- 6. Disable unused peripherals.

- 7. Disable unused pin activity (for example, CLKOUT, XTAL).

One way to evaluate power consumption is to use a current-per-MIPS measurement methodology to minimize specific board effects (that is, to compensate for measured board current not caused by the DSP). A benchmark power consumption test algorithm is listed in **Appendix A**. Use the test algorithm, specific test current measurements, and the following equation to derive the current-per-MIPS value.

Equation 5: / MIPS =

$$I$$

/ MHz =  $(I_{typF2} - I_{typF1})$ / (F2 - F1)

Where:

| uency)              |

|---------------------|

| ency lower than F2) |

|                     |

**Note:** F1 should be significantly less than F2. For example, F2 could be 66 MHz and F1 could be 33 MHz. The degree of difference between F1 and F2 determines the amount of precision with which the current rating can be determined for an application.

# 4.4 Input (EXTAL) Jitter Requirements

The allowed jitter on the frequency of EXTAL is 0.5 percent. If the rate of change of the frequency of EXTAL is slow (that is, it does not jump between the minimum and maximum values in one cycle) or the frequency of the jitter is fast (that is, it does not stay at an extreme value for a long time), then the allowed jitter can be 2 percent. The phase and frequency jitter performance results are valid only if the input jitter is less than the prescribed values.

M IALO EOU O ; IRQA Mode Interrupt Priority Level (low) M\_IAL1 EQU 1 ; IRQA Mode Interrupt Priority Level (high) ; IRQA Mode Trigger Mode M\_IAL2 EQU 2 ; IRQB Mode Mask M\_IBL EQU \$38 ; IRQB Mode Interrupt Priority Level (low) M\_IBL0 EQU 3 BLUBLJBLJEQUICLEQU \$1C0ICLICLEQU 6ICLIEQU 7ICL2EQU 8IDLEQU 900IDLEQU 10IDL 200EQU 11EQU 400EQU 400EQU 53000EQU 5400EQU 5400EQU 55EQU 5000EQU 5000EQU 5000EQU 515EQU 515EQU 52000EQU 53000EQU 53000EQU 54000EQU 55EQU 5000EQU 5000EQU 5000EQU 5000EQU 5000EQU 5000EQU 5000EQU 5000EQU 5000EQU 50000EQU 500000EQU 500000EQU 500000EQU 50000 ; IRQB Mode Interrupt Priority Level (high) ; IRQB Mode Trigger Mode M\_IBL1 EQU 4 M\_HPL EQU \$3 ; Host Interrupt Priority Level Mask M\_HPL0 EQU 0 ; Host Interrupt Priority Level (low) M\_HPL1 EQU 1; Host Interrupt Priority Level (high)M\_SOL EQU \$C; SSI0 Interrupt Priority Level MaskM\_SOL0 EQU 2; SSI0 Interrupt Priority Level (low)M\_SOL1 EQU 3; SSI0 Interrupt Priority Level (high)M\_S1L EQU \$30; SSI1 Interrupt Priority Level (MaskM\_S1L0 EQU 4; SSI1 Interrupt Priority Level (low)M\_S1L1 EQU 5; SSI1 Interrupt Priority Level (low)M\_S2L2 EQU \$C0; SCI Interrupt Priority Level (high)M\_SCL0 EQU 6; SCI Interrupt Priority Level (low)M\_SCL1 EQU 7; SCI Interrupt Priority Level (high)M\_T0L EQU \$300; TIMER Interrupt Priority Level MaskM\_T0L0 EQU 8; TIMER Interrupt Priority Level (low) M\_HPL1 EQU 1 ; Host Interrupt Priority Level (high) M\_TOLO EQU 8 ; TIMER Interrupt Priority Level (low) M\_TOL1 EQU 9 ; TIMER Interrupt Priority Level (high) ;------; EQUATES for TIMER ; ; Register Addresses Of TIMER0 ; ; Timer 0 Control/Status Register M\_TCSR0 EQU \$FFFF8F

#### Pr Consumption Benchmark

```

M DPR0 EOU 17

; DMA Channel Priority Level (low)

; DMA Channel Priority Level (high)

M_DPR1 EQU 18

M_DTM EQU $380000

; DMA Transfer Mode Mask (DTM2-DTM0)

; DMA Transfer Mode 0

M_DTM0 EQU 19

; DMA Transfer Mode 1

M_DTM1 EQU 20

M_DTM2 EQU 21

; DMA Transfer Mode 2

M DIE EOU 22

; DMA Interrupt Enable bit

M_DE EQU 23

; DMA Channel Enable bit

DMA Status Register

;

M DTD EOU $3F

; Channel Transfer Done Status MASK (DTD0-DTD5)

; DMA Channel Transfer Done Status 0

M DTDO EOU O

; DMA Channel Transfer Done Status 1

M DTD1 EOU 1

M_DTD2 EQU 2

; DMA Channel Transfer Done Status 2

M_DTD3 EQU 3

; DMA Channel Transfer Done Status 3

; DMA Channel Transfer Done Status 4

M_DTD4 EQU 4

; DMA Channel Transfer Done Status 5

; DMA Active State

M_DTD5 EQU 5

M_DACT EQU 8

M_DCH EQU $E00

; DMA Active Channel Mask (DCH0-DCH2)

M_DCH0 EQU 9

; DMA Active Channel 0

; DMA Active Channel 1

M_DCH1 EQU 10

M_DCH2 EQU 11

; DMA Active Channel 2

;-----

;

EQUATES for Enhanced Filter Co-Processor (EFCOP)

;

;

;------

M_FDIREQU$FFFFB0; EFCOP Data Input RegisterM_FDOREQU$FFFFB1; EFCOP Data Output RegisterM_FKIREQU$FFFFB2; EFCOP K-Constant RegisterM_FCNTEQU$FFFFB3; EFCOP Filter CounterM_FCSREQU$FFFFB4; EFCOP Control Status RegisterM_FACREQU$FFFFB5; EFCOP ALU Control RegisterM_FDBAEQU$FFFFB6; EFCOP Data Base AddressM_FCBAEQU$FFFFB7; EFCOP Coefficient Base AddressM_FDCHEQU$FFFFB8; EFCOP Decimation/Channel Register

;------

;

EQUATES for Phase Locked Loop (PLL)

;

;------

Register Addresses Of PLL

;

$FFFFD0

M_DMFR EQU

M_DPSC EQU

$FFFFD0

M_PCTL EQU

$FFFFD1

; PLL Control Register

PLL Control Register

;

$F

M_MFI

EQU

$F

M_MFN

EQU

$7F0

M_MFD

EQU

$3F800

M_PDF

EQU

$3C0000

M MFI

EQU

; Multiplication Factor Intager Bits Mask (MFI0-MFI3)

; Multiplication Factor Bits Mask (MFN0-MFN6)

; Multiplication Factor Bits Mask (MFD0-MFD6)

; PreDivider Factor Bits Mask (PD0-PD3)

M_CPLM EQU 22

;

23

M_MFO EQU

;

EQU $70

M_CDF

; Division Factor Bits Mask (DF0-DF2)

```

; Non-Maskable interrupts •\_\_\_\_\_ ; Hardware RESET I\_RESET EQU I\_VEC+\$00 I STACK EQU I\_VEC+\$02 ; Stack Error ; Illegal Instruction I\_ILL EQU I\_VEC+\$04 I\_DBG EQU I\_VEC+\$06 ; Debug Request ; Trap I\_TRAP EQU I\_VEC+\$08 I\_NMI EQU I\_VEC+\$0A ; Non Maskable Interrupt :-----; Interrupt Request Pins ;------; IRQA I\_IRQA EQU I\_VEC+\$10 I\_IRQB EQU I\_VEC+\$12 ; IRQB I\_IRQC EQU I\_VEC+\$14 ; IRQC I\_IRQD EQU I\_VEC+\$16 ; IRQD ;------; DMA Interrupts ; DMA Channel 0 I\_DMA0 EQU I\_VEC+\$18 I\_DMA1 EQU I\_VEC+\$1A ; DMA Channel 1 I\_DMA2 EQU I\_VEC+\$1C ; DMA Channel 2 I\_DMA3 EQU I\_VEC+\$1E I\_DMA4 EQU I\_VEC+\$20 ; DMA Channel 3 ; DMA Channel 4 I\_DMA5 EQU I\_VEC+\$22 ; DMA Channel 5 ;------; Timer Interrupts ; TIMER 0 compare I\_TIMOC EQU I\_VEC+\$24 ; TIMER 0 overflow I\_TIM1C EQU I\_VEC+\$28 ; TIMER 1 compare I\_TIM10F EQU I\_VEC+\$2A ; TIMER 1 overflow I\_TIM2C EQU I\_VEC+\$2C ; TIMER 2 compare I\_TIM2OF EQU I\_VEC+\$2E ; TIMER 2 overflow ; ESSI Interrupts ;------I\_SIORD EQU I\_VEC+\$30 ; ESSI0 Receive Data I\_SIORDE EQU I\_VEC+\$32 I\_SIORLS EQU I\_VEC+\$34 ; ESSI0 Receive Data w/ exception Status ; ESSI0 Receive last slot I\_SIOTD EQU I\_VEC+\$36 ; ESSIO Transmit data I\_SIOTDE EQU I\_VEC+\$38 ; ESSI0 Transmit Data w/ exception Status I\_SIOTLS EQU I\_VEC+\$3A ; ESSI0 Transmit last slot ; ESSI1 Receive Data I\_SI1RD EQU I\_VEC+\$40 ; ESSI1 Receive Data w/ exception Status I\_SI1RDE EQU I\_VEC+\$42 ; ESSI1 Receive last slot I\_SI1TD EQU I\_VEC+\$46 ; ESSI1 Transmit data ; ESSI1 Transmit Data w/ exception Status I\_SI1TDE EQU I\_VEC+\$48 I\_SI1TLS EQU I\_VEC+\$4A ; ESSI1 Transmit last slot ;------; SCI Interrupts I\_SCIRD EQU I\_VEC+\$50 ; SCI Receive Data I\_SCIRDE EQU I\_VEC+\$52 I\_SCITD EQU I\_VEC+\$54 I\_SCIIL EQU I\_VEC+\$56 ; SCI Receive Data With Exception Status ; SCI Transmit Data ; SCI Idle Line I\_SCITM EQU I\_VEC+\$58 ; SCI Timer