# E·XFL

### NXP USA Inc. - DSP56321VF200R2 Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

### Details

| Details                 |                                                                         |

|-------------------------|-------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                |

| Туре                    | Fixed Point                                                             |

| Interface               | Host Interface, SSI, SCI                                                |

| Clock Rate              | 200MHz                                                                  |

| Non-Volatile Memory     | ROM (576B)                                                              |

| On-Chip RAM             | 576kB                                                                   |

| Voltage - I/O           | 3.30V                                                                   |

| Voltage - Core          | 1.60V                                                                   |

| Operating Temperature   | -40°C ~ 100°C (TJ)                                                      |

| Mounting Type           | Surface Mount                                                           |

| Package / Case          | 196-BGA                                                                 |

| Supplier Device Package | 196-MAPBGA (15x15)                                                      |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/dsp56321vf200r2 |

|                         |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

|           |       | Data Sheet Conventions                          | ii   |

|-----------|-------|-------------------------------------------------|------|

|           |       | Features                                        | iii  |

|           |       | Target Applications                             | iv   |

|           |       | Product Documentation                           | v    |

| Chapter 1 | Signa | als/Connections                                 |      |

| -         | 1.1   | Power                                           |      |

|           | 1.2   | Ground                                          |      |

|           | 1.3   | Clock                                           |      |

|           | 1.4   | External Memory Expansion Port (Port A)         |      |

|           | 1.5   | Interrupt and Mode Control                      |      |

|           | 1.6   | Host Interface (HI08)                           |      |

|           | 1.7   | Enhanced Synchronous Serial Interface 0 (ESSI0) |      |

|           | 1.8   | Enhanced Synchronous Serial Interface 1 (ESSI1) |      |

|           | 1.9   | Serial Communication Interface (SCI)            |      |

|           | 1.10  | Timers                                          |      |

|           | 1.11  | JTAG and OnCE Interface                         | 1-14 |

| Chapter 2 | Spec  | ifications                                      |      |

| •         | 2.1   | Maximum Ratings                                 |      |

|           | 2.2   | Thermal Characteristics                         |      |

|           | 2.3   | DC Electrical Characteristics                   |      |

|           | 2.4   | AC Electrical Characteristics                   |      |

| Chapter 3 | Pack  | aging                                           |      |

| •         | 3.1   | Package Description                             |      |

|           | 3.2   | MAP-BGA Package Mechanical Drawing              |      |

| Chapter 4 | Desid | gn Considerations                               |      |

| •         | 4.1   | Thermal Design Considerations                   |      |

|           | 4.2   | Electrical Design Considerations                |      |

|           | 4.3   | Power Consumption Considerations                |      |

|           | 4.4   | Input (EXTAL) Jitter Requirements               |      |

|           |       |                                                 |      |

Appendix A Power Consumption Benchmark

### **Data Sheet Conventions**

OVERBAR

Indicates a signal that is active when pulled low (For example, the RESET pin is active when low.)

"asserted" Means that a high true (active high) signal is high or that a low true (active low) signal is low "deasserted" Means that a high true (active high) signal is low or that a low true (active low) signal is high

| Examples: | Signal/Symbol | Logic State | Signal State | Voltage                          |

|-----------|---------------|-------------|--------------|----------------------------------|

|           | PIN           | True        | Asserted     | V <sub>IL</sub> /V <sub>OL</sub> |

|           | PIN           | False       | Deasserted   | $V_{IH}/V_{OH}$                  |

|           | PIN           | True        | Asserted     | $V_{IH}/V_{OH}$                  |

|           | PIN           | False       | Deasserted   | $V_{IL}/V_{OL}$                  |

Note: Values for  $V_{IL}$ ,  $V_{OL}$ ,  $V_{IH}$ , and  $V_{OH}$  are defined by individual product specifications.

# Signals/Connections

The DSP56321 input and output signals are organized into functional groups as shown in **Table 1-1**. **Figure 1-1** diagrams the DSP56321 signals by functional group. The remainder of this chapter describes the signal pins in each functional group.

| Functional Group                                                                                                                                                                                                                                                                                                                                |                           |                     |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------|--|

| Power (V <sub>CC</sub> )                                                                                                                                                                                                                                                                                                                        |                           | 20                  |  |

| Ground (GND)                                                                                                                                                                                                                                                                                                                                    |                           | 66                  |  |

| Clock                                                                                                                                                                                                                                                                                                                                           |                           | 2                   |  |

| Address bus                                                                                                                                                                                                                                                                                                                                     |                           | 18                  |  |

| Data bus                                                                                                                                                                                                                                                                                                                                        | Port A <sup>1</sup>       | 24                  |  |

| Bus control                                                                                                                                                                                                                                                                                                                                     |                           | 10                  |  |

| Interrupt and mode control                                                                                                                                                                                                                                                                                                                      |                           |                     |  |

| Host interface (HI08)                                                                                                                                                                                                                                                                                                                           | Port B <sup>2</sup>       | 16                  |  |

| Enhanced synchronous serial interface (ESSI) Ports C and D <sup>3</sup>                                                                                                                                                                                                                                                                         |                           |                     |  |

| Serial communication interface (SCI)                                                                                                                                                                                                                                                                                                            | Port E <sup>4</sup>       | 3                   |  |

| Timer                                                                                                                                                                                                                                                                                                                                           |                           | 3                   |  |

| OnCE/JTAG Port                                                                                                                                                                                                                                                                                                                                  |                           | 6                   |  |

| <ol> <li>Port A signals define the external memory interface port, including the</li> <li>Port B signals are the HI08 port signals multiplexed with the GPIO sig</li> <li>Port C and D signals are the two ESSI port signals multiplexed with the</li> <li>Port E signals are the SCI port signals multiplexed with the GPIO signals</li> </ol> | nals.<br>ne GPIO signals. | nd control signals. |  |

| Table 1-1. | DSP56321  | Functional  | Signal  | Groupings |

|------------|-----------|-------------|---------|-----------|

|            | DOI 00021 | i unotionui | orginar | aroupingo |

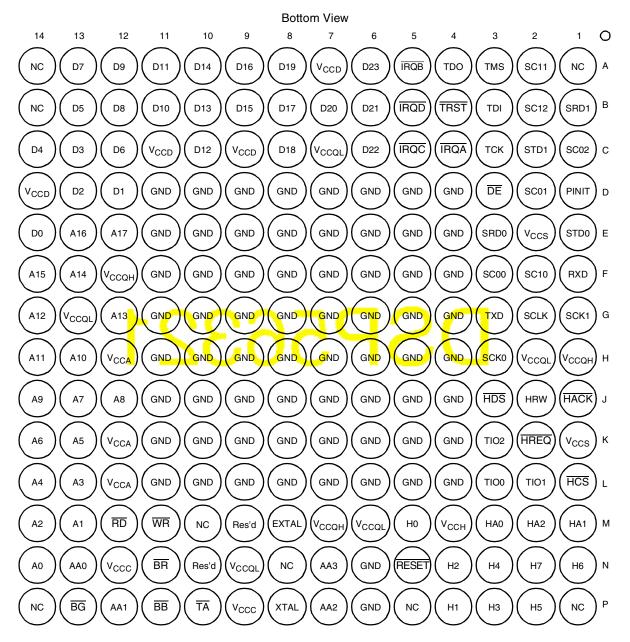

Chapter 3). There are also two reserved lines.

Eight signal lines are not connected internally. These are designated as no connect (NC) in the package description (see

**Note:** This chapter refers to a number of configuration registers used to select individual multiplexed signal functionality. See the *DSP56321 Reference Manual* for details on these configuration registers.

5.

## 1.1 Power

| Power Name        | Description                                                                                                                                                                                         |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| V <sub>CCQL</sub> | Quiet Core (Low) Power—An isolated power for the core processing and clock logic. This input must be isolated externally from all other chip power inputs.                                          |  |  |  |

| V <sub>CCQH</sub> | Quiet External (High) Power—A quiet power source for I/O lines. This input must be tied externally to all other chip power inputs, <i>except</i> V <sub>CCQL</sub> .                                |  |  |  |

| V <sub>CCA</sub>  | Address Bus Power—An isolated power for sections of the address bus I/O drivers. This input must be tied externally to all other chip power inputs, <i>except</i> V <sub>CCQL</sub> .               |  |  |  |

| V <sub>CCD</sub>  | <b>Data Bus Power</b> —An isolated power for sections of the data bus I/O drivers. This input must be tied externally to all other chip power inputs, <i>except</i> V <sub>CCQL</sub> .             |  |  |  |

| V <sub>CCC</sub>  | Bus Control Power—An isolated power for the bus control I/O drivers. This input must be tied externally to all other chip power inputs, <i>except</i> V <sub>CCQL</sub> .                           |  |  |  |

| V <sub>CCH</sub>  | Host Power—An isolated power for the HI08 I/O drivers. This input must be tied externally to all other chip power inputs, <i>except</i> V <sub>CCQL</sub> .                                         |  |  |  |

| V <sub>CCS</sub>  | <b>ESSI, SCI, and Timer Power</b> —An isolated power for the ESSI, SCI, and timer I/O drivers. This input must be tied externally to all other chip power inputs, <i>except</i> V <sub>CCQL</sub> . |  |  |  |

| Note: The user m  | ust provide adequate external decoupling capacitors for all power connections.                                                                                                                      |  |  |  |

### Table 1-2. Power Inputs

# 1.2 Ground

### Table 1-3. Grounds

| Name              | Description                                                                                  |  |  |

|-------------------|----------------------------------------------------------------------------------------------|--|--|

| GND               | Ground—Connected to an internal device ground plane.                                         |  |  |

| Note: The user mu | Note: The user must provide adequate external decoupling capacitors for all GND connections. |  |  |

# 1.3 Clock

### Table 1-4. Clock Signals

| Signal Name | Туре   | State During<br>Reset | Signal Description                                                                                                                                   |

|-------------|--------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTAL       | Input  | Input                 | External Clock/Crystal Input—Interfaces the internal crystal oscillator input to an external crystal or an external clock.                           |

| XTAL        | Output | Chip-driven           | <b>Crystal Output</b> —Connects the internal crystal oscillator output to an external crystal. If an external clock is used, leave XTAL unconnected. |

als/Connections

| Signal Name                                                                                                                                                                                                                                                                                                                                                                                      | Туре            | State During<br>Reset <sup>1,2</sup> | Signal Description                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCK1                                                                                                                                                                                                                                                                                                                                                                                             | Input/Output    | Ignored Input                        | Serial Clock—Provides the serial bit rate clock for the ESSI. The SCK1 is a clock input or output used by both the transmitter and receiver in synchronous modes or by the transmitter in asynchronous modes.                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                  |                 |                                      | Although an external serial clock can be independent of and asynchronous to<br>the DSP system clock, it must exceed the minimum clock cycle time of 6T (that<br>is, the system clock frequency must be at least three times the external ESSI<br>clock frequency). The ESSI needs at least three DSP phases inside each half of<br>the serial clock. |

| PD3                                                                                                                                                                                                                                                                                                                                                                                              | Input or Output |                                      | <b>Port D 3</b> —The default configuration following reset is GPIO input PD3. When configured as PD3, signal direction is controlled through the Port D Direction Register. The signal can be configured as an ESSI signal SCK1 through the Port D Control Register.                                                                                 |

| SRD1                                                                                                                                                                                                                                                                                                                                                                                             | Input           | Ignored Input                        | Serial Receive Data—Receives serial data and transfers the data to the ESSI Receive Shift Register. SRD1 is an input when data is being received.                                                                                                                                                                                                    |

| PD4                                                                                                                                                                                                                                                                                                                                                                                              | Input or Output |                                      | <b>Port D 4</b> —The default configuration following reset is GPIO input PD4. When configured as PD4, signal direction is controlled through the Port D Direction Register. The signal can be configured as an ESSI signal SRD1 through the Port D Control Register.                                                                                 |

| STD1                                                                                                                                                                                                                                                                                                                                                                                             | Output          | Ignored Input                        | Serial Transmit Data—Transmits data from the Serial Transmit Shift Register.<br>STD1 is an output when data is being transmitted.                                                                                                                                                                                                                    |

| PD5                                                                                                                                                                                                                                                                                                                                                                                              | Input or Output |                                      | <b>Port D 5</b> —The default configuration following reset is GPIO input PD5. When configured as PD5, signal direction is controlled through the Port D Direction Register. The signal can be configured as an ESSI signal STD1 through the Port D Control Register.                                                                                 |

| <ol> <li>In the Stop state, the signal maintains the last state as follows:         <ul> <li>If the last state is input, the signal is an ignored input.</li> <li>If the last state is output, these lines have weak keepers that maintain the last output state even if the drivers are tri-stated.</li> </ul> </li> <li>The Wait processing state does not affect the signal state.</li> </ol> |                 |                                      |                                                                                                                                                                                                                                                                                                                                                      |

Table 1-12.

Enhanced Serial Synchronous Interface 1 (Continued)

# 1.9 Serial Communication Interface (SCI)

The SCI provides a full duplex port for serial communication with other DSPs, microprocessors, or peripherals such as modems.

| Signal Name | Туре            | State During<br>Reset <sup>1,2</sup> | Signal Description                                                                                                                                                                                                                                                 |

|-------------|-----------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXD         | Input           | Ignored Input                        | Serial Receive Data—Receives byte-oriented serial data and transfers it to the SCI Receive Shift Register.                                                                                                                                                         |

| PE0         | Input or Output |                                      | <b>Port E 0</b> —The default configuration following reset is GPIO input PE0. When configured as PE0, signal direction is controlled through the Port E Direction Register. The signal can be configured as an SCI signal RXD through the Port E Control Register. |

| TXD         | Output          | Ignored Input                        | Serial Transmit Data—Transmits data from the SCI Transmit Data Register.                                                                                                                                                                                           |

| PE1         | Input or Output |                                      | <b>Port E 1</b> —The default configuration following reset is GPIO input PE1. When configured as PE1, signal direction is controlled through the Port E Direction Register. The signal can be configured as an SCI signal TXD through the Port E Control Register. |

Table 1-13.

Serial Communication Interface

| Table 1-13. | Serial Communication | Interface | (Continued) |

|-------------|----------------------|-----------|-------------|

|-------------|----------------------|-----------|-------------|

| Signal Name                                                                                                                                                                                                                                                                                                                                                                                      | Туре            | State During<br>Reset <sup>1,2</sup> | Signal Description                                                                                                                                                                                                                                                  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SCLK                                                                                                                                                                                                                                                                                                                                                                                             | Input/Output    | Ignored Input                        | Serial Clock—Provides the input or output clock used by the transmitter and/or the receiver.                                                                                                                                                                        |  |

| PE2                                                                                                                                                                                                                                                                                                                                                                                              | Input or Output |                                      | <b>Port E 2</b> —The default configuration following reset is GPIO input PE2. When configured as PE2, signal direction is controlled through the Port E Direction Register. The signal can be configured as an SCI signal SCLK through the Port E Control Register. |  |

| <ol> <li>In the Stop state, the signal maintains the last state as follows:         <ul> <li>If the last state is input, the signal is an ignored input.</li> <li>If the last state is output, these lines have weak keepers that maintain the last output state even if the drivers are tri-stated.</li> </ul> </li> <li>The Wait processing state does not affect the signal state.</li> </ol> |                 |                                      |                                                                                                                                                                                                                                                                     |  |

## 1.10 Timers

The DSP56321 has three identical and independent timers. Each timer can use internal or external clocking and can either interrupt the DSP56321 after a specified number of events (clocks) or signal an external device after counting a specific number of internal events.

| Signal Name      | Туре                                                                                               | State During<br>Reset <sup>1,2</sup>           | Signal Description                                                                                                                                                                                                                            |

|------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TIO0             | Input or Output                                                                                    | Ignored Input                                  | <b>Timer 0 Schmitt-Trigger Input/Output</b> — When Timer 0 functions as an external event counter or in measurement mode, TIO0 is used as input. When Timer 0 functions in watchdog, timer, or pulse modulation mode, TIO0 is used as output. |

|                  |                                                                                                    |                                                | The default mode after reset is GPIO input. TIO0 can be changed to output or configured as a timer I/O through the Timer 0 Control/Status Register (TCSR0).                                                                                   |

| TIO1             | Input or Output                                                                                    | Ignored Input                                  | <b>Timer 1 Schmitt-Trigger Input/Output</b> — When Timer 1 functions as an external event counter or in measurement mode, TIO1 is used as input. When Timer 1 functions in watchdog, timer, or pulse modulation mode, TIO1 is used as output. |

|                  |                                                                                                    |                                                | The default mode after reset is GPIO input. TIO1 can be changed to output or configured as a timer I/O through the Timer 1 Control/Status Register (TCSR1).                                                                                   |

| TIO2             | Input or Output                                                                                    | Ignored Input                                  | <b>Timer 2 Schmitt-Trigger Input/Output</b> — When Timer 2 functions as an external event counter or in measurement mode, TIO2 is used as input. When Timer 2 functions in watchdog, timer, or pulse modulation mode, TIO2 is used as output. |

|                  |                                                                                                    |                                                | The default mode after reset is GPIO input. TIO2 can be changed to output or configured as a timer I/O through the Timer 2 Control/Status Register (TCSR2).                                                                                   |

| • If t<br>• If t | he Stop state, the sig<br>he last state is input,<br>he last state is outpu<br>Wait processing sta | the signal is an igno<br>t, these lines have w | ored input.<br>yeak keepers that maintain the last output state even if the drivers are tri-stated.                                                                                                                                           |

| Table 1-14. | Triple Timer Signals |

|-------------|----------------------|

|             | The Third Orginalo   |

### 1.11 JTAG and OnCE Interface

The DSP56300 family and in particular the DSP56321 support circuit-board test strategies based on the IEEE® Std. 1149.1<sup>™</sup> test access port and boundary scan architecture, the industry standard developed under the sponsorship of the Test Technology Committee of IEEE and the JTAG. The OnCE module provides a means to interface nonintrusively with the DSP56300 core and its peripherals so that you can examine registers, memory, or on-chip peripherals. Functions of the OnCE module are provided through the JTAG TAP signals. For programming models, see the chapter on debugging support in the DSP56300 Family Manual.

| Signal<br>Name | Туре          | State During<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------|---------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| тск            | Input         | Input                 | Test Clock—A test clock input signal to synchronize the JTAG test logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TDI            | Input         | Input                 | <b>Test Data Input</b> —A test data serial input signal for test instructions and data. TDI is sampled on the rising edge of TCK and has an internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TDO            | Output        | Tri-stated            | <b>Test Data Output</b> —A test data serial output signal for test instructions and data. TDO is actively driven in the shift-IR and shift-DR controller states. TDO changes on the falling edge of TCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TMS            | Input         | Input                 | <b>Test Mode Select</b> —Sequences the test controller's state machine. TMS is sampled on the rising edge of TCK and has an internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TRST           | Input         | Input                 | <b>Test Reset</b> —Înitializes the test controller asynchronously. TRST has an internal pull-up resistor. TRST must be asserted during and after power-up (see EB610/D for details).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DE             | Input/ Output | Input                 | <b>Debug Event</b> —As an input, initiates Debug mode from an external command controller, and, as an open-drain output, acknowledges that the chip has entered Debug mode. As an input, DE causes the DSP56300 core to finish executing the current instruction, save the instruction pipeline information, enter Debug mode, and wait for commands to be entered from the debug serial input line. This signal is asserted as an output for three clock cycles when the chip enters Debug mode as a result of a debug request or as a result of meeting a breakpoint condition. The DE has an internal pull-up resistor. This signal is not a standard part of the JTAG TAP controller. The signal connects directly to the OnCE module to initiate debug mode directly or to provide a direct external indication that the chip has entered Debug mode. All other interface with the OnCE module must occur through the JTAG port. |

| Table 1-15. | JTAG/OnCE Interface |

|-------------|---------------------|

|             |                     |

### 2.2 Thermal Characteristics

| Thermal Resistance Characteristic                                                 | Symbol            | MAP-BGA<br>Value | Unit |

|-----------------------------------------------------------------------------------|-------------------|------------------|------|

| Junction-to-ambient, natural convection, single-layer board (1s) <sup>1,2</sup>   | R <sub>θJA</sub>  | 44               | °C/W |

| Junction-to-ambient, natural convection, four-layer board (2s2p) <sup>1,3</sup>   | R <sub>θJMA</sub> | 25               | °C/W |

| Junction-to-ambient, @200 ft/min air flow, single-layer board (1s) <sup>1,3</sup> | R <sub>θJMA</sub> | 35               | °C/W |

| Junction-to-ambient, @200 ft/min air flow, four-layer board (2s2p) <sup>1,3</sup> | $R_{	heta JMA}$   | 22               | °C/W |

| Junction-to-board <sup>4</sup>                                                    | R <sub>θJB</sub>  | 13               | °C/W |

| Junction-to-case thermal resistance <sup>5</sup>                                  | R <sub>θJC</sub>  | 7                | °C/W |

Table 2-2. Thermal Characteristics

**Notes:** 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

2. Per SEMI G38-87 and JEDEC JESD51-2 with the single-layer board horizontal.

**3.** Per JEDEC JESD51-6 with the board horizontal.

4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

### **2.3 DC Electrical Characteristics**

| Characteristics                                                                                                                                                                               | Symbol                                                  | Min                                   | Тур        | Max                                                                     | Unit        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------|------------|-------------------------------------------------------------------------|-------------|

| Supply voltage <sup>1</sup> :<br>• Core (V <sub>CCQL</sub> )<br>• I/O (V <sub>CCQH</sub> , V <sub>CCA</sub> , V <sub>CCD</sub> , V <sub>CCC</sub> , V <sub>CCH</sub> , and V <sub>CCS</sub> ) |                                                         | 1.5<br>3.0                            | 1.6<br>3.3 | 1.7<br>3.6                                                              | V<br>V      |

| Input high voltage<br>• D[0-23], BG, BB, TA<br>• MOD/IRQ <sup>2</sup> RESET, PINIT/NMI and all<br>JTAG/ESSI/SCI/Timer/HI08 pins<br>• EXTAL <sup>9</sup>                                       | V <sub>IH</sub><br>V <sub>IHP</sub><br>V <sub>IHX</sub> | 2.0<br>2.0<br>0.8 × V <sub>CCQH</sub> | <br>       | V <sub>CCQH</sub> + 0.3<br>V <sub>CCQH</sub> + 0.3<br>V <sub>CCQH</sub> | ><br>><br>> |

| Input low voltage<br>• D[0–23], BG, BB, TA, MOD/IRQ <sup>2</sup> , RESET, PINIT<br>• All JTAG/ESSI/SCI/Timer/HI08 pins<br>• EXTAL <sup>9</sup>                                                | V <sub>IL</sub><br>V <sub>ILP</sub><br>V <sub>ILX</sub> | -0.3<br>-0.3<br>-0.3                  |            | 0.8<br>0.8<br>$0.2 \times V_{CCQH}$                                     | V<br>V<br>V |

| Input leakage current                                                                                                                                                                         | I <sub>IN</sub>                                         | -10                                   | —          | 10                                                                      | μΑ          |

| High impedance (off-state) input current<br>(@ 2.4 V / 0.4 V)                                                                                                                                 | I <sub>TSI</sub>                                        | -10                                   | _          | 10                                                                      | μA          |

| Output high voltage <sup>8</sup><br>• TTL $(I_{OH} = -0.4 \text{ mA})^6$<br>• CMOS $(I_{OH} = -10 \mu A)^6$                                                                                   | V <sub>OH</sub>                                         | 2.4<br>V <sub>CCQH</sub> – 0.01       |            |                                                                         | V<br>V      |

| Output low voltage <sup>8</sup><br>• TTL ( $I_{OL} = 3.0 \text{ mA}$ ) <sup>6</sup><br>• CMOS ( $I_{OL} = 10 \text{ µA}$ ) <sup>6</sup>                                                       | V <sub>OL</sub>                                         |                                       | —          | 0.4<br>0.01                                                             | V<br>V      |

| Table 2-3. | DC Electrical | Characteristics <sup>7</sup> |

|------------|---------------|------------------------------|

|------------|---------------|------------------------------|

| Table 2-7. | Reset, Stop, Mode Select, and Interrupt Timing <sup>5</sup> | (CONTINUED) |

|------------|-------------------------------------------------------------|-------------|

|------------|-------------------------------------------------------------|-------------|

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                            | 200           | MHz                          | 220         | MHz                          | 240           | MHz                          | 275           | MHz                             |                      |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------|------------------------------|-------------|------------------------------|---------------|------------------------------|---------------|---------------------------------|----------------------|

| No. | Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Expression                                                                 | Min           | Max                          | Min         | Мах                          | Min           | Max                          | Min           | Max                             | Unit                 |

|     | Delay from RD assertion to interrupt request deassertion for level sensitive fast interrupts <sup>1, 6, 7</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | (WS + 3.25) × T <sub>C</sub> –<br>10.94                                    | _             | Note 7                       |             | Note 7                       | _             | Note 7                       | _             | Note 7                          | ns                   |

|     | Delay from $\overline{\text{WR}}$ assertion to interrupt<br>request deassertion for level sensitive<br>fast interrupts <sup>1, 6, 7</sup><br>• SRAM WS = 3<br>• SRAM WS $\geq$ 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | (WS + 3) × T <sub>C</sub> – 10.94<br>(WS + 2.5) × T <sub>C</sub> – 10.94   |               | Note 7<br>Note 7             |             | Note 7<br>Note 7             |               | Note 7<br>Note 7             |               | Note 7<br>Note 7                | ns<br>ns             |

|     | Duration for IRQA assertion to recover from Stop state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                            | 8.0           | —                            | 8.0         | —                            | 8.0           | —                            | 8.0           | —                               | ns                   |

|     | <ul> <li>Delay from IRQA assertion to fetch of first instruction (when exiting Stop)<sup>2, 3</sup></li> <li>DPLL is not active during Stop (PCTL Bit 1 = 0) and Stop delay is enabled (Operating Mode Register Bit 6 = 0)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DPLT + (128K × T <sub>C</sub> )                                            | 662.2<br>μs   | 209.9<br>ms                  | 662.2<br>μs | 209.9<br>ms                  | 662.2<br>μs   | 209.9<br>ms                  | 662.2<br>μs   | 209.9<br>ms                     | _                    |

|     | <ul> <li>DPLL is not active during Stop<br/>(PCTL Bit 1 = 0) and Stop delay is<br/>not enabled (Operating Mode<br/>Register Bit 6 = 1)</li> <li>DPLL is active during Stop (PCTL<br/>Bit 1 = 1; Implies No Stop Delay)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DPLT + (23.75 ± 0.5) ×<br>T <sub>C</sub><br>(10.0 ± 1.75) × T <sub>C</sub> | 6.9<br>41.25  | 188.8<br>58.8                | 6.9<br>37.5 | 188.8<br>53.3                | 6.9<br>34.4   | 188.8<br>49.0                | 6.9<br>30.0   | 43.0                            | μs<br>ns             |

|     | <ul> <li>Duration of level sensitive IRQA assertion to ensure interrupt service (when exiting Stop)<sup>2, 3</sup></li> <li>DPLL is not active during Stop (PCTL bit 1 = 0) and Stop delay is enabled (Operating Mode Register Transport of the sensitive of</li></ul> | DPLT + (128 K × T <sub>C</sub> )                                           | 805.4         |                              | 805.4       |                              | 805.4         |                              | 805.4         | _                               | μs                   |

|     | <ul> <li>(PCTL bit 1 = 0) and Stop delay is<br/>not enabled (Operating Mode<br/>Register Bit 6 = 1)</li> <li>DPLL is active during Stop ((PCTL</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DPLT + (20.5 ±0.5) × T <sub>C</sub><br>5.5 × T <sub>C</sub>                | 150.1<br>27.5 | _                            | 150.1<br>25 | _                            | 150.1<br>22.9 | _                            | 150.1<br>20.0 | _                               | μs<br>ns             |

| 27  | bit 1 = 0; implies no Stop delay)<br>Interrupt Request Rate<br>• HI08, ESSI, SCI, Timer<br>• DMA<br>• IRQ, NMI (edge trigger)<br>• IRQ, NMI (level trigger)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12T <sub>C</sub><br>8T <sub>C</sub><br>8T <sub>C</sub><br>12T <sub>C</sub> |               | 60.0<br>40.0<br>40.0<br>60.0 |             | 54.6<br>36.4<br>36.4<br>54.6 |               | 50.0<br>33.4<br>33.4<br>50.0 |               | 43.7<br>29.2<br>29.2<br>43.7    | ns<br>ns<br>ns<br>ns |

| 28  | <ul> <li>DMA Request Rate</li> <li>Data read from HI08, ESSI, SCI</li> <li>Data write to HI08, ESSI, SCI</li> <li>Timer</li> <li>IRQ, NMI (edge trigger)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6T <sub>C</sub><br>7T <sub>C</sub><br>2T <sub>C</sub><br>3T <sub>C</sub>   |               | 30.0<br>35.0<br>10.0<br>15.0 |             | 27.3<br>31.9<br>9.1<br>13.7  |               | 25.0<br>29.2<br>8.3<br>12.5  | <br>          | 21.84<br>25.48<br>7.28<br>10.92 | ns<br>ns<br>ns<br>ns |

|     | Delay from IRQA, IRQB, IRQC, IRQD,<br>NMI assertion to external memory<br>(DMA source) access address out<br>valid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4.25 × T <sub>C</sub> + 2.0                                                | 23.25         |                              | 21.34       |                              | 19.72         |                              | 17.45         | _                               | ns                   |

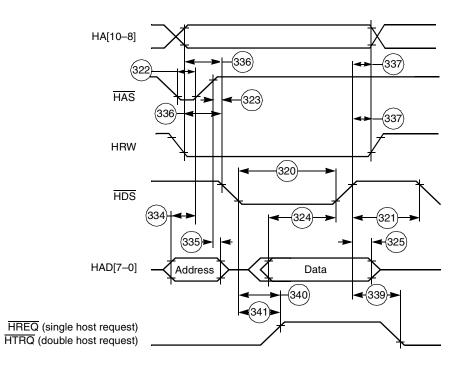

Figure 2-20. Write Timing Diagram, Multiplexed Bus, Single Data Strobe

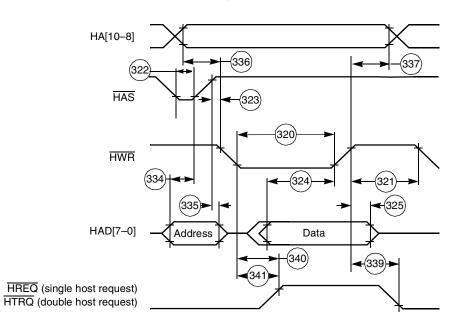

Figure 2-21. Write Timing Diagram, Multiplexed Bus, Double Data Strobe

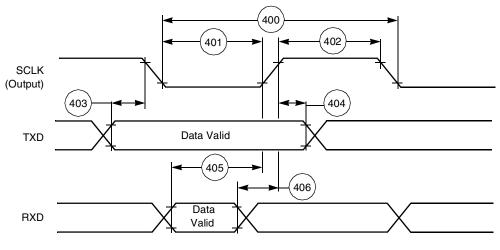

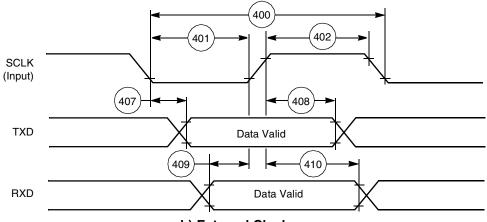

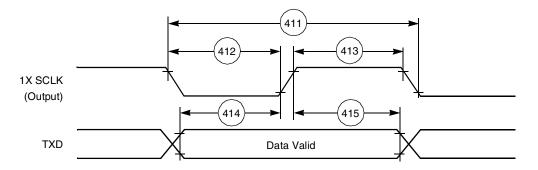

#### **SCI** Timing 2.4.7

| N   | o. Characteristics <sup>1</sup> Symbol Expression                     |                               | 200 MHz 220 MH                        |       |      | MHz   | /Hz 240 MHz |       |      | 275 MHz |       |          |

|-----|-----------------------------------------------------------------------|-------------------------------|---------------------------------------|-------|------|-------|-------------|-------|------|---------|-------|----------|

| No. | Characteristics'                                                      | Symbol                        | Expression                            | Min   | Мах  | Min   | Мах         | Min   | Max  | Min     | Мах   | Uni<br>t |