Welcome to E-XFL.COM

### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

### Details

E·XFl

| Details                 |                                                            |

|-------------------------|------------------------------------------------------------|

| Product Status          | Active                                                     |

| Туре                    | Fixed Point                                                |

| Interface               | Host Interface, SSI, SCI                                   |

| Clock Rate              | 220MHz                                                     |

| Non-Volatile Memory     | ROM (576B)                                                 |

| On-Chip RAM             | 576kB                                                      |

| Voltage - I/O           | 3.30V                                                      |

| Voltage - Core          | 1.60V                                                      |

| Operating Temperature   | -40°C ~ 100°C (TJ)                                         |

| Mounting Type           | Surface Mount                                              |

| Package / Case          | 196-BGA                                                    |

| Supplier Device Package | 196-MAPBGA (15x15)                                         |

| Purchase URL            | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=dsp56321vf220 |

|                         |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Features

Table 1 lists the features of the DSP56321 device.

| Feature                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High-Performance<br>DSP56300 Core      | <ul> <li>275 million multiply-accumulates per second (MMACS) (550 MMACS using the EFCOP in filtering applications) with a 275 MHz clock at 1.6 V core and 3.3 V I/O</li> <li>Object code compatible with the DSP56000 core with highly parallel instruction set</li> <li>Data arithmetic logic unit (Data ALU) with fully pipelined 24 × 24-bit parallel Multiplier-Accumulator (MAC), 56-bit parallel barrel shifter (fast shift and normalization; bit stream generation and parsing), conditional ALU instructions, and 24-bit or 16-bit arithmetic support under software control</li> <li>Program control unit (PCU) with position independent code (PIC) support, addressing modes optimized for DSP applications (including immediate offsets), internal instruction cache controller, internal memory-expandable hardware stack, nested hardware DO loops, and fast auto-return interrupts</li> <li>Direct memory access (DMA) with six DMA channels supporting internal and external accesses; one-, two-, and three-dimensional transfers (including circular buffering); end-of-block-transfer interrupts; and triggering from interrupt lines and all peripherals</li> <li>Phase-lock loop (PLL) allows change of low-power divide factor (DF) without loss of lock and output clock with skew elimination</li> <li>Hardware debugging support including on-chip emulation (OnCE) module, Joint Test Action Group (JTAG) test access port (TAP)</li> </ul> |

| Enhanced Filter<br>Coprocessor (EFCOP) | <ul> <li>Internal 24 × 24-bit filtering and echo-cancellation coprocessor that runs in parallel to the DSP core</li> <li>Operation at the same frequency as the core (up to 275 MHz)</li> <li>Support for a variety of filter modes, some of which are optimized for cellular base station applications: <ul> <li>Real finite impulse response (FIR) with real taps</li> <li>Complex FIR with complex taps</li> <li>Complex FIR generating pure real or pure imaginary outputs alternately</li> <li>A 4-bit decimation factor in FIR filters, thus providing a decimation ratio up to 16</li> <li>Direct form 1 (DFI) Infinite Impulse Response (IIR) filter</li> <li>Four scaling factors (1, 4, 8, 16) for IIR output</li> <li>Adaptive FIR filter with true least mean square (LMS) coefficient updates</li> <li>Adaptive FIR filter with delayed LMS coefficient updates</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Internal Peripherals                   | <ul> <li>Enhanced 8-bit parallel host interface (HI08) supports a variety of buses (for example, ISA) and provides glueless connection to a number of industry-standard microcomputers, microprocessors, and DSPs</li> <li>Two enhanced synchronous serial interfaces (ESSI), each with one receiver and three transmitters (allows six-channel home theater)</li> <li>Serial communications interface (SCI) with baud rate generator</li> <li>Triple timer module</li> <li>Up to 34 programmable general-purpose input/output (GPIO) pins, depending on which peripherals are enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

### Table 1. DSP56321 Features

DSP56321 Technical Data, Rev. 11

# Signals/Connections

The DSP56321 input and output signals are organized into functional groups as shown in **Table 1-1**. **Figure 1-1** diagrams the DSP56321 signals by functional group. The remainder of this chapter describes the signal pins in each functional group.

| Functional Group                                                                                                                                                                                                                                                                                                                                |                           |                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------|

| Power (V <sub>CC</sub> )                                                                                                                                                                                                                                                                                                                        |                           | 20                  |

| Ground (GND)                                                                                                                                                                                                                                                                                                                                    |                           | 66                  |

| Clock                                                                                                                                                                                                                                                                                                                                           |                           | 2                   |

| Address bus                                                                                                                                                                                                                                                                                                                                     |                           | 18                  |

| Data bus                                                                                                                                                                                                                                                                                                                                        | Port A <sup>1</sup>       | 24                  |

| Bus control                                                                                                                                                                                                                                                                                                                                     |                           | 10                  |

| Interrupt and mode control                                                                                                                                                                                                                                                                                                                      |                           | 6                   |

| Host interface (HI08) Port B <sup>2</sup>                                                                                                                                                                                                                                                                                                       |                           | 16                  |

| Enhanced synchronous serial interface (ESSI) Ports C and D <sup>3</sup>                                                                                                                                                                                                                                                                         |                           | 12                  |

| Serial communication interface (SCI) Port E <sup>4</sup>                                                                                                                                                                                                                                                                                        |                           | 3                   |

| Timer                                                                                                                                                                                                                                                                                                                                           |                           |                     |

| OnCE/JTAG Port                                                                                                                                                                                                                                                                                                                                  |                           |                     |

| <ol> <li>Port A signals define the external memory interface port, including the</li> <li>Port B signals are the HI08 port signals multiplexed with the GPIO sig</li> <li>Port C and D signals are the two ESSI port signals multiplexed with the</li> <li>Port E signals are the SCI port signals multiplexed with the GPIO signals</li> </ol> | nals.<br>ne GPIO signals. | nd control signals. |

| Table 1-1. | DSP56321  | Functional | Signal  | Groupings |

|------------|-----------|------------|---------|-----------|

|            | DOI 00021 | i unononui | orginar | aroupingo |

Chapter 3). There are also two reserved lines.

Eight signal lines are not connected internally. These are designated as no connect (NC) in the package description (see

**Note:** This chapter refers to a number of configuration registers used to select individual multiplexed signal functionality. See the *DSP56321 Reference Manual* for details on these configuration registers.

5.

# 1.1 Power

| Power Name        | Description                                                                                                                                                                                         |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CCQL</sub> | Quiet Core (Low) Power—An isolated power for the core processing and clock logic. This input must be isolated externally from all other chip power inputs.                                          |

| V <sub>CCQH</sub> | Quiet External (High) Power—A quiet power source for I/O lines. This input must be tied externally to all other chip power inputs, <i>except</i> V <sub>CCQL</sub> .                                |

| V <sub>CCA</sub>  | Address Bus Power—An isolated power for sections of the address bus I/O drivers. This input must be tied externally to all other chip power inputs, <i>except</i> V <sub>CCQL</sub> .               |

| V <sub>CCD</sub>  | <b>Data Bus Power</b> —An isolated power for sections of the data bus I/O drivers. This input must be tied externally to all other chip power inputs, <i>except</i> V <sub>CCQL</sub> .             |

| V <sub>CCC</sub>  | Bus Control Power—An isolated power for the bus control I/O drivers. This input must be tied externally to all other chip power inputs, <i>except</i> V <sub>CCQL</sub> .                           |

| V <sub>CCH</sub>  | Host Power—An isolated power for the HI08 I/O drivers. This input must be tied externally to all other chip power inputs, <i>except</i> V <sub>CCQL</sub> .                                         |

| V <sub>CCS</sub>  | <b>ESSI, SCI, and Timer Power</b> —An isolated power for the ESSI, SCI, and timer I/O drivers. This input must be tied externally to all other chip power inputs, <i>except</i> V <sub>CCQL</sub> . |

| Note: The user m  | ust provide adequate external decoupling capacitors for all power connections.                                                                                                                      |

### Table 1-2. Power Inputs

# 1.2 Ground

### Table 1-3. Grounds

| Name                                                                                         | Description                                          |  |

|----------------------------------------------------------------------------------------------|------------------------------------------------------|--|

| GND                                                                                          | Ground—Connected to an internal device ground plane. |  |

| Note: The user must provide adequate external decoupling capacitors for all GND connections. |                                                      |  |

# 1.3 Clock

### Table 1-4. Clock Signals

| Signal Name | Туре   | State During<br>Reset | Signal Description                                                                                                                                   |

|-------------|--------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTAL       | Input  | Input                 | External Clock/Crystal Input—Interfaces the internal crystal oscillator input to an external crystal or an external clock.                           |

| XTAL        | Output | Chip-driven           | <b>Crystal Output</b> —Connects the internal crystal oscillator output to an external crystal. If an external clock is used, leave XTAL unconnected. |

# 1.6 Host Interface (HI08)

The HI08 provides a fast, 8-bit, parallel data port that connects directly to the host bus. The HI08 supports a variety of standard buses and connects directly to a number of industry-standard microcomputers, microprocessors, DSPs, and DMA hardware.

### 1.6.1 Host Port Usage Considerations

Careful synchronization is required when the system reads multiple-bit registers that are written by another asynchronous system. This is a common problem when two asynchronous systems are connected (as they are in the Host port). The considerations for proper operation are discussed in **Table 1-9**.

| Action                                        | Description                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Asynchronous read of receive byte registers   | When reading the receive byte registers, Receive register High (RXH), Receive register Middle (RXM), or Receive register Low (RXL), the host interface programmer should use interrupts or poll the Receive register Data Full (RXDF) flag that indicates data is available. This assures that the data in the receive byte registers is valid.                                                        |

| Asynchronous write to transmit byte registers | The host interface programmer should not write to the transmit byte registers, Transmit register High (TXH), Transmit register Middle (TXM), or Transmit register Low (TXL), unless the Transmit register Data Empty (TXDE) bit is set indicating that the transmit byte registers are empty. This guarantees that the transmit byte registers transfer valid data to the Host Receive (HRX) register. |

| Asynchronous write to host vector             | The host interface programmer must change the Host Vector (HV) register only when the Host Command bit (HC) is clear. This practice guarantees that the DSP interrupt control logic receives a stable vector.                                                                                                                                                                                          |

| Table 1-9. | Host Port Usage Considerations |

|------------|--------------------------------|

|------------|--------------------------------|

### 1.6.2 Host Port Configuration

HI08 signal functions vary according to the programmed configuration of the interface as determined by the 16 bits in the HI08 Port Control Register.

| Signal Name | Туре            | State During<br>Reset <sup>1,2</sup> | Signal Description                                                                                                                                                                                        |

|-------------|-----------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| H[0–7]      | Input/Output    | Ignored Input                        | <b>Host Data</b> —When the HI08 is programmed to interface with a non-multiplexed host bus and the HI function is selected, these signals are lines 0–7 of the bidirectional Data bus.                    |

| HAD[0-7]    | Input/Output    |                                      | <b>Host Address</b> —When the HI08 is programmed to interface with a multiplexed host bus and the HI function is selected, these signals are lines 0–7 of the bidirectional multiplexed Address/Data bus. |

| PB[0-7]     | Input or Output |                                      | <b>Port B 0–7</b> —When the HI08 is configured as GPIO through the HI08 Port Control Register, these signals are individually programmed as inputs or outputs through the HI08 Data Direction Register.   |

Table 1-10. Host Interface

als/Connections

# 1.7 Enhanced Synchronous Serial Interface 0 (ESSI0)

Two synchronous serial interfaces (ESSI0 and ESSI1) provide a full-duplex serial port for serial communication with a variety of serial devices, including one or more industry-standard codecs, other DSPs, microprocessors, and peripherals that implement the Freescale serial peripheral interface (SPI).

| Signal Name | Туре            | State During<br>Reset <sup>1,2</sup> | Signal Description                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|-----------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SC00        | Input or Output | Ignored Input                        | <b>Serial Control 0</b> —For asynchronous mode, this signal is used for the receive clock I/O (Schmitt-trigger input). For synchronous mode, this signal is used either for transmitter 1 output or for serial I/O flag 0.                                                                                                                                                                                 |

| PC0         | Input or Output |                                      | <b>Port C 0</b> —The default configuration following reset is GPIO input PC0. When configured as PC0, signal direction is controlled through the Port C Direction Register. The signal can be configured as ESSI signal SC00 through the Port C Control Register.                                                                                                                                          |

| SC01        | Input/Output    | Ignored Input                        | <b>Serial Control 1</b> —For asynchronous mode, this signal is the receiver frame sync I/O. For synchronous mode, this signal is used either for transmitter 2 output or for serial I/O flag 1.                                                                                                                                                                                                            |

| PC1         | Input or Output |                                      | <b>Port C 1</b> —The default configuration following reset is GPIO input PC1. When configured as PC1, signal direction is controlled through the Port C Direction Register. The signal can be configured as an ESSI signal SC01 through the Port C Control Register.                                                                                                                                       |

| SC02        | Input/Output    | Ignored Input                        | Serial Control Signal 2—The frame sync for both the transmitter and receiver<br>in synchronous mode, and for the transmitter only in asynchronous mode. When<br>configured as an output, this signal is the internally generated frame sync signal.<br>When configured as an input, this signal receives an external frame sync signal<br>for the transmitter (and the receiver in synchronous operation). |

| PC2         | Input or Output |                                      | <b>Port C 2</b> —The default configuration following reset is GPIO input PC2. When configured as PC2, signal direction is controlled through the Port C Direction Register. The signal can be configured as an ESSI signal SC02 through the Port C Control Register.                                                                                                                                       |

| SCK0        | Input/Output    | Ignored Input                        | <b>Serial Clock</b> —Provides the serial bit rate clock for the ESSI. The SCK0 is a clock input or output, used by both the transmitter and receiver in synchronous modes or by the transmitter in asynchronous modes.                                                                                                                                                                                     |

|             |                 |                                      | Although an external serial clock can be independent of and asynchronous to<br>the DSP system clock, it must exceed the minimum clock cycle time of 6T (that<br>is, the system clock frequency must be at least three times the external ESSI<br>clock frequency). The ESSI needs at least three DSP phases inside each half of<br>the serial clock.                                                       |

| PC3         | Input or Output |                                      | <b>Port C 3</b> —The default configuration following reset is GPIO input PC3. When configured as PC3, signal direction is controlled through the Port C Direction Register. The signal can be configured as an ESSI signal SCK0 through the Port C Control Register.                                                                                                                                       |

| SRD0        | Input           | Ignored Input                        | Serial Receive Data—Receives serial data and transfers the data to the ESSI Receive Shift Register. SRD0 is an input when data is received.                                                                                                                                                                                                                                                                |

| PC4         | Input or Output |                                      | <b>Port C 4</b> —The default configuration following reset is GPIO input PC4. When configured as PC4, signal direction is controlled through the Port C Direction Register. The signal can be configured as an ESSI signal SRD0 through the Port C Control Register.                                                                                                                                       |

| Table 1-11. | Enhanced Synchronous Serial Interface 0 |

|-------------|-----------------------------------------|

|             | Ennancea eynomeneae eena maenaee e      |

### 2.2 Thermal Characteristics

| Thermal Resistance Characteristic                                                 | Symbol            | MAP-BGA<br>Value | Unit |

|-----------------------------------------------------------------------------------|-------------------|------------------|------|

| Junction-to-ambient, natural convection, single-layer board (1s) <sup>1,2</sup>   | R <sub>θJA</sub>  | 44               | °C/W |

| Junction-to-ambient, natural convection, four-layer board (2s2p) <sup>1,3</sup>   | R <sub>θJMA</sub> | 25               | °C/W |

| Junction-to-ambient, @200 ft/min air flow, single-layer board (1s) <sup>1,3</sup> | R <sub>θJMA</sub> | 35               | °C/W |

| Junction-to-ambient, @200 ft/min air flow, four-layer board (2s2p) <sup>1,3</sup> | R <sub>θJMA</sub> | 22               | °C/W |

| Junction-to-board <sup>4</sup>                                                    | R <sub>θJB</sub>  | 13               | °C/W |

| Junction-to-case thermal resistance <sup>5</sup>                                  | R <sub>θJC</sub>  | 7                | °C/W |

Table 2-2. Thermal Characteristics

**Notes:** 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

2. Per SEMI G38-87 and JEDEC JESD51-2 with the single-layer board horizontal.

**3.** Per JEDEC JESD51-6 with the board horizontal.

4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

## **2.3 DC Electrical Characteristics**

| Characteristics                                                                                                                                                                               | Symbol                                                  | Min                                   | Тур        | Max                                                                     | Unit        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------|------------|-------------------------------------------------------------------------|-------------|

| Supply voltage <sup>1</sup> :<br>• Core (V <sub>CCQL</sub> )<br>• I/O (V <sub>CCQH</sub> , V <sub>CCA</sub> , V <sub>CCD</sub> , V <sub>CCC</sub> , V <sub>CCH</sub> , and V <sub>CCS</sub> ) |                                                         | 1.5<br>3.0                            | 1.6<br>3.3 | 1.7<br>3.6                                                              | V<br>V      |

| Input high voltage<br>• D[0-23], BG, BB, TA<br>• MOD/IRQ <sup>2</sup> RESET, PINIT/NMI and all<br>JTAG/ESSI/SCI/Timer/HI08 pins<br>• EXTAL <sup>9</sup>                                       | V <sub>IH</sub><br>V <sub>IHP</sub><br>V <sub>IHX</sub> | 2.0<br>2.0<br>0.8 × V <sub>CCQH</sub> | <br>       | V <sub>CCQH</sub> + 0.3<br>V <sub>CCQH</sub> + 0.3<br>V <sub>CCQH</sub> | ><br>><br>> |

| Input low voltage<br>• D[0–23], BG, BB, TA, MOD/IRQ <sup>2</sup> , RESET, PINIT<br>• All JTAG/ESSI/SCI/Timer/HI08 pins<br>• EXTAL <sup>9</sup>                                                | V <sub>IL</sub><br>V <sub>ILP</sub><br>V <sub>ILX</sub> | -0.3<br>-0.3<br>-0.3                  |            | 0.8<br>0.8<br>$0.2 \times V_{CCQH}$                                     | V<br>V<br>V |

| Input leakage current                                                                                                                                                                         | I <sub>IN</sub>                                         | -10                                   | —          | 10                                                                      | μΑ          |

| High impedance (off-state) input current<br>(@ 2.4 V / 0.4 V)                                                                                                                                 | I <sub>TSI</sub>                                        | -10                                   | _          | 10                                                                      | μA          |

| Output high voltage <sup>8</sup><br>• TTL $(I_{OH} = -0.4 \text{ mA})^6$<br>• CMOS $(I_{OH} = -10 \mu A)^6$                                                                                   | V <sub>OH</sub>                                         | 2.4<br>V <sub>CCQH</sub> – 0.01       |            |                                                                         | V<br>V      |

| Output low voltage <sup>8</sup><br>• TTL ( $I_{OL} = 3.0 \text{ mA}$ ) <sup>6</sup><br>• CMOS ( $I_{OL} = 10 \text{ µA}$ ) <sup>6</sup>                                                       | V <sub>OL</sub>                                         |                                       | —          | 0.4<br>0.01                                                             | V<br>V      |

| Table 2-3. | DC Electrical | Characteristics <sup>7</sup> |

|------------|---------------|------------------------------|

|------------|---------------|------------------------------|

Table 2-6.

CLKGEN and DPLL Characteristics (Continued)

|                 | Characteristics |                             | 0                                                                               | 200         | MHz          | 220        | MHz          | 240         | MHz         | 275         | MHz      | 11 |

|-----------------|-----------------|-----------------------------|---------------------------------------------------------------------------------|-------------|--------------|------------|--------------|-------------|-------------|-------------|----------|----|

| Characteristics |                 | Symbol                      | Min                                                                             | Мах         | Min          | Мах        | Min          | Мах         | Min         | Мах         | Unit     |    |

| Notes:          | 1.              | Refer to the DSP56321 L     | the DSP56321 User's Manual for a detailed description of register reset values. |             |              |            |              |             |             |             |          |    |

|                 | 2.              | The total multiplication fa | ctor (MF) in                                                                    | ncludes bo  | oth integer  | and fracti | onal parts   | (that is, M | F = MFI +   | MFN/MFE     | D).      |    |

|                 | 3.              | The numerator (MFN) sh      | ould be les                                                                     | s than the  | denomina     | tor (MFD)  | ).           |             |             |             |          |    |

|                 | 4.              | DPLL lock procedure dur     | ation is spe                                                                    | ecified for | the case w   | hen an e   | kternal cloo | ck source   | is supplied | I to the EX | TAL pin. |    |

|                 | 5.              | Frequency-only Lock Mo      | ock Mode or non-integer MF, after partial reset.                                |             |              |            |              |             |             |             |          |    |

|                 | 6.              | Frequency and Phase Lo      | ck Mode, i                                                                      | nteger MF   | , after full | reset.     |              |             |             |             |          |    |

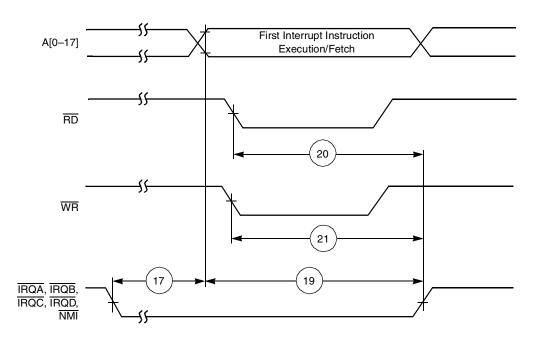

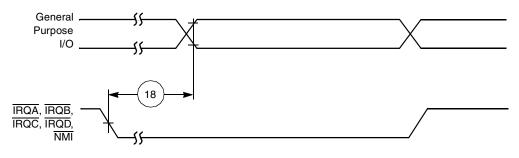

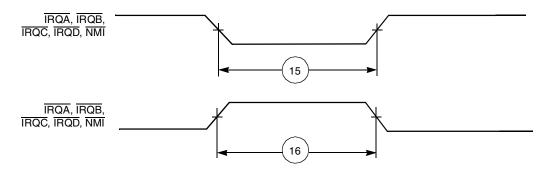

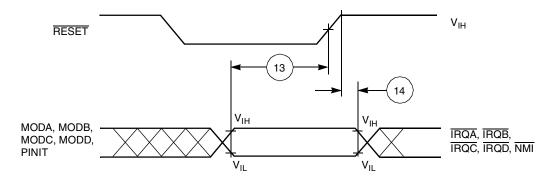

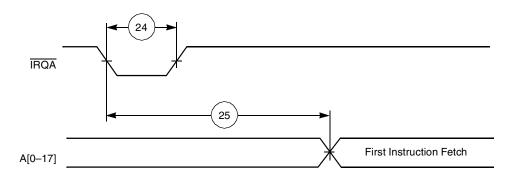

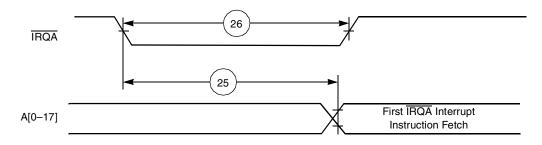

### 2.4.4 Reset, Stop, Mode Select, and Interrupt Timing

|     |                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                               | 200                                          | MHz     | 220                                            | MHz     | 240                                            | MHz     | 275                                           | MHz     |                                  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|---------|------------------------------------------------|---------|------------------------------------------------|---------|-----------------------------------------------|---------|----------------------------------|

| No. | Characteristics                                                                                                                                                                                                                                                                                                                     | Expression                                                                                                                                                                                                    | Min                                          | Max     | Min                                            | Max     | Min                                            | Max     | Min                                           | Max     | Unit                             |

|     | Delay from RESET assertion to all pins at reset value <sup>3</sup>                                                                                                                                                                                                                                                                  | —                                                                                                                                                                                                             | —                                            | 26      | —                                              | 26      |                                                | 26      | -                                             | 26      | ns                               |

| 9   | <ul> <li>Required RESET duration<sup>4</sup></li> <li>Power on, external clock<br/>generator, DPLL disabled</li> <li>Power on, external clock<br/>generator, DPLL enabled</li> <li>Power on, internal oscillator</li> <li>During STOP, XTAL disabled</li> <li>During STOP, XTAL enabled</li> <li>During normal operation</li> </ul> | $50 \times \text{ET}_{\text{C}}$ $1000 \times \text{ET}_{\text{C}}$ $75000 \times \text{ET}_{\text{C}}$ $75000 \times \text{ET}_{\text{C}}$ $2.5 \times \text{T}_{\text{C}}$ $2.5 \times \text{T}_{\text{C}}$ | 250.0<br>5.0<br>0.375<br>0.375<br>12.5<br>17 |         | 227.5<br>4.55<br>0.341<br>0.341<br>11.38<br>16 |         | 208.5<br>4.17<br>0.313<br>0.313<br>10.43<br>15 |         | 182.0<br>3.64<br>0.273<br>0.273<br>9.1<br>9.1 |         | ns<br>μs<br>ms<br>ms<br>ns<br>ns |

| 10  | Delay from asynchronous RESET<br>deassertion to first external address<br>output (internal reset deassertion)<br>• Minimum<br>• Maximum                                                                                                                                                                                             | 3.25 × T <sub>C</sub> + 2.0                                                                                                                                                                                   | 18.25<br>—                                   | <br>180 | 16.77                                          | <br>163 | 15.55<br>—                                     | <br>150 | 13.82<br>—                                    | <br>140 | ns<br>ns                         |

| 13  | Mode select setup time                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                               | 30.0                                         | _       | 30.0                                           | -       | 30.0                                           | -       | 30.0                                          | _       | ns                               |

| 14  | Mode select hold time                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                               | 0.0                                          | _       | 0.0                                            | _       | 0.0                                            | _       | 0.0                                           | _       | ns                               |

| 15  | Minimum edge-triggered interrupt request assertion width                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                               | 4.0                                          | _       | 4.0                                            | _       | 4.0                                            | _       | 4.0                                           | —       | ns                               |

| 16  | Minimum edge-triggered interrupt<br>request deassertion width                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                               | 4.0                                          | -       | 4.0                                            | _       | 4.0                                            | _       | 4.0                                           | —       | ns                               |

| 17  | <ul> <li>Delay from IRQA, IRQB, IRQC, IRQD,</li> <li>NMI assertion to external memory access address out valid</li> <li>Caused by first interrupt instruction fetch</li> <li>Caused by first interrupt instruction execution</li> </ul>                                                                                             | $4.25 \times T_{C} + 2.0$<br>$7.25 \times T_{C} + 2.0$                                                                                                                                                        | 23.25<br>38.25                               | _       | 21.24<br>34.99                                 | _       | 19.72<br>32.23                                 | _       | 17.45<br>28.36                                | _       | ns<br>ns                         |

|     | Delay from IRQA, IRQB, IRQC, IRQD,<br>NMI assertion to general-purpose<br>transfer output valid caused by first<br>interrupt instruction execution                                                                                                                                                                                  | $8.9 	imes T_{C}$                                                                                                                                                                                             | 44.5                                         | _       | 40.45                                          | _       | 37.0                                           | _       | 32.37                                         | _       | ns                               |

|     | Delay from address output valid<br>caused by first interrupt instruction<br>execute to interrupt request<br>deassertion for level sensitive fast<br>interrupts <sup>1, 6, 7</sup>                                                                                                                                                   | (WS + 3.75) × T <sub>C</sub> –<br>10.94                                                                                                                                                                       | _                                            | Note 7  |                                                | Note 7  |                                                | Note 7  | _                                             | Note 7  | ns                               |

Table 2-7.

Reset, Stop, Mode Select, and Interrupt Timing<sup>5</sup>

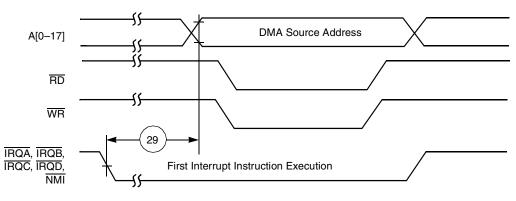

a) First Interrupt Instruction Execution

b) General-Purpose I/O

Figure 2-4. External Fast Interrupt Timing

Figure 2-5. External Interrupt Timing (Negative Edge-Triggered)

Figure 2-6. Operating Mode Select Timing

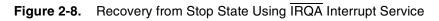

Figure 2-7. Recovery from Stop State Using IRQA

Figure 2-9. External Memory Access (DMA Source) Timing

Table 2-10.

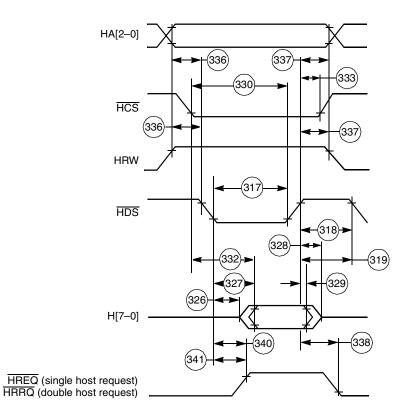

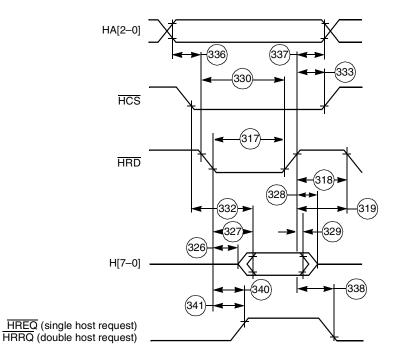

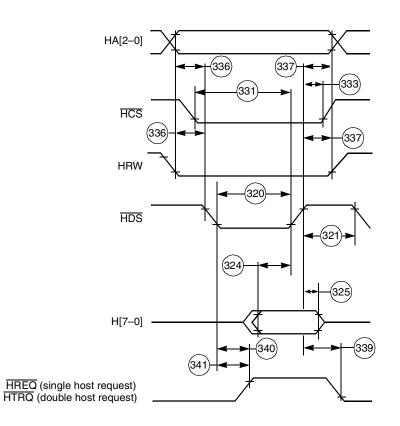

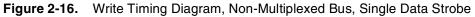

Host Interface Timings<sup>1,2,12</sup> (Continued)

| No.    |     | Characteristic <sup>10</sup>                                                                                                               | Expression                                                                                                                                                                                                                                               | 200        | MHz               | 220       | MHz        | 240      | MHz       | 275      | MHz      | Uni    |  |

|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------|-----------|------------|----------|-----------|----------|----------|--------|--|

| NO.    |     | Characteristic                                                                                                                             | Expression                                                                                                                                                                                                                                               | Min        | Max               | Min       | Max        | Min      | Max       | Min      | Мах      | t      |  |

| Notes: | 1.  | See the Programmer's Model section in                                                                                                      | n the chapter on                                                                                                                                                                                                                                         | the HI08   | 3 in the <i>l</i> | DSP563    | 21 Refe    | rence M  | anual.    |          |          |        |  |

|        | 2.  | In the timing diagrams below, the contr                                                                                                    | ols pins are drav                                                                                                                                                                                                                                        | vn as ac   | tive low.         | . The pir | n polarity | is progr | ammabl    | e.       |          |        |  |

|        | 3.  | This timing is applicable only if two con                                                                                                  | secutive reads f                                                                                                                                                                                                                                         | rom one    | of these          | e registe | rs are ex  | ecuted.  |           |          |          |        |  |

|        | 4.  | The data strobe is Host Read (HRD) or Single Data Strobe mode.                                                                             | <sup>-</sup> Host Write (HW                                                                                                                                                                                                                              | (R) in the | e Dual D          | ata Stro  | be mode    | e and Ho | ost Data  | Strobe   | (HDS) ir | n the  |  |

|        | 5.  | The read data strobe is HRD in the Dua                                                                                                     | al Data Strobe m                                                                                                                                                                                                                                         | ode and    | I HDS in          | the Sin   | gle Data   | Strobe   | mode.     |          |          |        |  |

|        | 6.  | The write data strobe is HWR in the Dual Data Strobe mode and HDS in the Single Data Strobe mode.                                          |                                                                                                                                                                                                                                                          |            |                   |           |            |          |           |          |          |        |  |

|        | 7.  | The host request is HREQ in the Single                                                                                                     | e Host Request r                                                                                                                                                                                                                                         | node an    | d HRRC            | and H     | rRQ in th  | ne Doub  | le Host I | Request  | mode.    |        |  |

|        | 8.  | <b>e e</b>                                                                                                                                 | The "Last Data Register" is the register at address \$7, which is the last location to be read or written in data transfers. This is RXL/TXL in the Big Endian mode (HLEND = 0; HLEND is the Interface Control Register bit 7—ICR[7]), or RXH/TXH in the |            |                   |           |            |          |           |          |          |        |  |

|        | 9.  | In this calculation, the host request signal is pulled up by a 4.7 k $\Omega$ resistor in the Open-drain mode.                             |                                                                                                                                                                                                                                                          |            |                   |           |            |          |           |          |          |        |  |

|        | 10. | $V_{CCOH} = 3.3 V \pm 0.3 V$ , $V_{CCOL} = 1.6 V$                                                                                          |                                                                                                                                                                                                                                                          |            |                   |           |            |          |           |          |          |        |  |

|        | 11. |                                                                                                                                            | om the "Last Da                                                                                                                                                                                                                                          | ta Regis   | ter" is fo        | llowed b  | y a read   |          | e RXL, F  | XM, or I | RXH reg  | isters |  |

|        | 12  | After the external host writes a new value to the ICR, the HI08 will be ready for operation after three DSP clock cycles ( $3 \times$ Tc). |                                                                                                                                                                                                                                                          |            |                   |           |            |          |           |          |          |        |  |

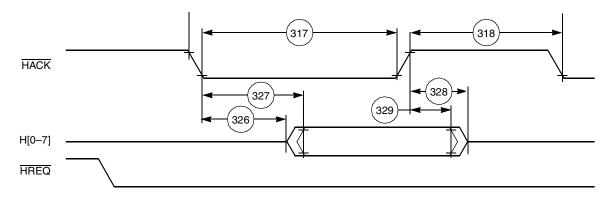

Figure 2-13. Host Interrupt Vector Register (IVR) Read Timing Diagram

Figure 2-14. Read Timing Diagram, Non-Multiplexed Bus, Single Data Strobe

Figure 2-15. Read Timing Diagram, Non-Multiplexed Bus, Double Data Strobe

Figure 2-17. Write Timing Diagram, Non-Multiplexed Bus, Double Data Strobe

| Table 3-1. | Signal List by Ball Number |

|------------|----------------------------|

|------------|----------------------------|

| Ball<br>No. | Signal Name        | Ball<br>No. | Signal Name       | Ball<br>No. | Signal Name      |

|-------------|--------------------|-------------|-------------------|-------------|------------------|

| A1          | Not Connected (NC) | B12         | D8                | D9          | GND              |

| A2          | SC11 or PD1        | B13         | D5                | D10         | GND              |

| A3          | TMS                | B14         | NC                | D11         | GND              |

| A4          | TDO                | C1          | SC02 or PC2       | D12         | D1               |

| A5          | MODB/IRQB          | C2          | STD1 or PD5       | D13         | D2               |

| A6          | D23                | C3          | тск               | D14         | V <sub>CCD</sub> |

| A7          | V <sub>CCD</sub>   | C4          | MODA/IRQA         | E1          | STD0 or PC5      |

| A8          | D19                | C5          | MODC/IRQC         | E2          | V <sub>CCS</sub> |

| A9          | D16                | C6          | D22               | E3          | SRD0 or PC4      |

| A10         | D14                | C7          | V <sub>CCQL</sub> | E4          | GND              |

| A11         | D11                | C8          | D18               | E5          | GND              |

| A12         | D9                 | C9          | V <sub>CCD</sub>  | E6          | GND              |

| A13         | D7                 | C10         | D12               | E7          | GND              |

| A14         | NC                 | C11         | V <sub>CCD</sub>  | E8          | GND              |

| B1          | SRD1 or PD4        | C12         | D6                | E9          | GND              |

| B2          | SC12 or PD2        | C13         | D3                | E10         | GND              |

| B3          | TDI                | C14         | D4                | E11         | GND              |

| B4          | TRST               | D1          | PINIT/NMI         | E12         | A17              |

| B5          | MODD/IRQD          | D2          | SC01 or PC1       | E13         | A16              |

| B6          | D21                | D3          | DE                | E14         | D0               |

| B7          | D20                | D4          | GND               | F1          | RXD or PE0       |

| B8          | D17                | D5          | GND               | F2          | SC10 or PD0      |

| B9          | D15                | D6          | GND               | F3          | SC00 or PC0      |

| B10         | D13                | D7          | GND               | F4          | GND              |

| B11         | D10                | D8          | GND               | F5          | GND              |

aging

| Table 3-2. | Signal List b | y Signal Name | (Continued) |

|------------|---------------|---------------|-------------|

|------------|---------------|---------------|-------------|

| Signal Name | Ball<br>No. | Signal Name | Ball<br>No. | Signal Name | Ball<br>No. |

|-------------|-------------|-------------|-------------|-------------|-------------|

| GND         | F9          | GND         | K4          | HA1         | M1          |

| GND         | F10         | GND         | K5          | HA10        | L1          |

| GND         | F11         | GND         | K6          | HA2         | M2          |

| GND         | G4          | GND         | K7          | HA8         | M1          |

| GND         | G5          | GND         | K8          | HA9         | M2          |

| GND         | G6          | GND         | K9          | HACK/HACK   | J1          |

| GND         | G7          | GND         | K10         | HAD0        | M5          |

| GND         | G8          | GND         | K11         | HAD1        | P4          |

| GND         | G9          | GND         | L4          | HAD2        | N4          |

| GND         | G10         | GND         | L5          | HAD3        | P3          |

| GND         | G11         | GND         | L6          | HAD4        | N3          |

| GND         | H4          | GND         | L7          | HAD5        | P2          |

| GND         | H5          | GND         | L8          | HAD6        | N1          |

| GND         | H6          | GND         | L9          | HAD7        | N2          |

| GND         | H7          | GND         | L10         | HAS/HAS     | M3          |

| GND         | H8          | GND         | L11         | HCS/HCS     | L1          |

| GND         | H9          | GND         | N6          | HDS/HDS     | J3          |

| GND         | H10         | GND         | P6          | HRD/HRD     | J2          |

| GND         | H11         | HO          | M5          | HREQ/HREQ   | K2          |

| GND         | J4          | H1          | P4          | HRRQ/HRRQ   | J1          |

| GND         | J5          | H2          | N4          | HRW         | J2          |

| GND         | J6          | НЗ          | P3          | HTRQ/HTRQ   | K2          |

| GND         | J7          | H4          | N3          | HWR/HWR     | J3          |

| GND         | J8          | H5          | P2          | ĪRQĀ        | C4          |

| GND         | J9          | H6          | N2          | IRQB        | A5          |

| GND         | J10         | H7          | N2          | IRQC        | C5          |

| GND         | J11         | HA0         | М3          | ĪRQD        | B5          |

### on Considerations

- To define a value approximately equal to a junction-to-board thermal resistance, the thermal resistance is measured from the junction to the point at which the leads attach to the case.

- If the temperature of the package case  $(T_T)$  is determined by a thermocouple, thermal resistance is computed from the value obtained by the equation  $(T_J T_T)/P_D$ .

As noted earlier, the junction-to-case thermal resistances quoted in this data sheet are determined using the first definition. From a practical standpoint, that value is also suitable to determine the junction temperature from a case thermocouple reading in forced convection environments. In natural convection, the use of the junction-to-case thermal resistance to estimate junction temperature from a thermocouple reading on the case of the package will yield an estimate of a junction temperature slightly higher than actual temperature. Hence, the new thermal metric, thermal characterization parameter or  $\Psi_{JT}$ , has been defined to be  $(T_J - T_T)/P_D$ . This value gives a better estimate of the junction temperature in natural convection when the surface temperature of the package is used. Remember that surface temperature readings of packages are subject to significant errors caused by inadequate attachment of the sensor to the surface and to errors caused by heat loss to the sensor. The recommended technique is to attach a 40-gauge thermocouple wire and bead to the top center of the package with thermally conductive epoxy.

# 4.2 Electrical Design Considerations

### CAUTION

This device contains protective circuitry to guard against damage due to high static voltage or electrical fields. However, normal precautions are advised to avoid application of any voltages higher than maximum rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for example, either GND or  $V_{CC}$ ).

Use the following list of recommendations to ensure correct DSP operation.

- Provide a low-impedance path from the board power supply to each  $V_{CC}$  pin on the DSP and from the board ground to each GND pin.

- Use at least four 0.01–0.1  $\mu$ F bypass capacitors for V<sub>CCQL</sub> (core) and at least six 0.01–0.1  $\mu$ F bypass capacitors for the other V<sub>CC</sub> (I/O) power connections positioned as closely as possible to the four sides of the package to connect the power sources to GND.

- Ensure that capacitor leads and associated printed circuit traces that connect to the chip  $V_{CC}$  and GND pins are less than 0.5 inch per capacitor lead.

- Use at least a four-layer PCB with two inner layers for  $V_{CC}$  and GND.

- Because the DSP output signals have fast rise and fall times, PCB trace lengths should be minimal. This recommendation particularly applies to the address and data buses as well as the IRQA, IRQB, IRQC, IRQD, TA, and BG pins. Maximum PCB trace lengths on the order of 6 inches are recommended.

### Pr Consumption Benchmark

M HOD EOU \$8 ; Host Request Open Drain mode , Host Request Open Brain Mode

; Host Data Strobe Polarity

; Host Address Strobe Polarity

; Host Multiplexed bus select

; Host Double/Single Strobe select

; Host Chip Select Polarity

; Host Request Polaritv M\_HDSP EQU \$9 M\_HASP EQU \$A M\_HMUX EQU \$B M\_HD\_HS EQU \$C M\_HCSP EQU \$D ; Host Request Polarity M\_HRP EQU \$E M\_HAP EQU \$F ; Host Acknowledge Polarity ;-----; EOUATES for Serial Communications Interface (SCI) ; ; M\_STXH EQU \$FFFF97 ; SCI Transmit Data Register (high) M\_STXM EQU \$FFFF96 ; SCI Transmit Data Register (middle) M\_STXL EQU \$FFFF95 ; SCI Transmit Data Register (low) M\_SRXH EQU \$FFFF9A ; SCI Receive Data Register (high) M\_SRXM EQU \$FFFF99 ; SCI Receive Data Register (middle) M\_SRXL EQU \$FFFF98 ; SCI Receive Data Register (low) M\_STXA EQU \$FFFF94 ; SCI Receive Data Register (low) M\_STXA EQU \$FFFF94 ; SCI Transmit Address Register M\_SCR EQU \$FFFF95 ; SCI Control Register M\_SCR EQU \$FFFF95 ; SCI Status Register M\_SCCR EQU \$FFFF98 ; SCI Clock Control Register ; SCI Control Register ; Register Addresses SCI Control Register Bit Flags ; M\_WDS EQU \$7 ; Word Select Mask (WDS0-WDS3) ; we ; SCI Shi. ; Send Break ; Wakeup Mode Select ; Receiver Wakeup Enable ; Wired-OR Mode Select ; SCI Receiver Enable ; SCI Transmitter Enable ; SCI Transmitter Enable ; Idle Line Interrupt Enable ; SCI Receive Interrupt Enable ; SCI Transmit Interrupt Enable ; Timer Interrupt Enable ; Timer Interrupt Rate ; SCI Clock Polarity SCI Error Interrupt Enable (F M\_WDS0 EQU 0 ; Word Select 0 M\_WDS1 EQU 1 M\_WDS2 EQU 2 M\_SSFTD EQU 3 M\_SBK EQU 4 M\_WAKE EQU 5 M\_RWU EQU 6 M\_WOMS EQU 7 M\_SCRE EQU 8 M\_SCTE EQU 9 M\_ILIE EQU 10 M\_SCRIE EQU 11 M\_SCTIE EQU 12 M\_TMIE EQU 13 M\_TIR EQU 14 M\_SCKP EQU 15 M\_REIE EQU 16 ; SCI Error Interrupt Enable (REIE) SCI Status Register Bit Flags ; M TRNE EOU 0 ; Transmitter Empty M\_TDRE EQU 1 ; Transmit Data Register Empty M\_RDRF EQU 2 ; Receive Data Register Full M\_IDLE EQU 3 ; Idle Line Flag M\_OR EQU 4 ; Overrun Error Flag M\_PE EQU 5 ; Parity Error ; Framing Error Flag M\_FE EQU 6 M\_R8 EQU 7 ; Received Bit 8 (R8) Address ; SCI Clock Control Register

M IALO EOU O ; IRQA Mode Interrupt Priority Level (low) M\_IAL1 EQU 1 ; IRQA Mode Interrupt Priority Level (high) ; IRQA Mode Trigger Mode M\_IAL2 EQU 2 ; IRQB Mode Mask M\_IBL EQU \$38 ; IRQB Mode Interrupt Priority Level (low) M\_IBL0 EQU 3 BLUBLJBLJEQUICLEQU \$1C0ICLICLEQU 6ICLIEQU 7ICL2EQU 8IDLEQU 900IDLEQU 10IDL 200EQU 11EQU 400EQU 400EQU 53000EQU 5400EQU 5400EQU 55EQU 5000EQU 5000EQU 5000EQU 515EQU 515EQU 52000EQU 52000EQU 53000EQU 53000EQU 54000EQU 55EQU 5000EQU 5000EQU 5000EQU 5000EQU 5000EQU 5000EQU 5000EQU 5000EQU 50000EQU 500000EQU 500000EQU 500000EQU 5000 ; IRQB Mode Interrupt Priority Level (high) ; IRQB Mode Trigger Mode M\_IBL1 EQU 4 M\_HPL EQU \$3 ; Host Interrupt Priority Level Mask M\_HPL0 EQU 0 ; Host Interrupt Priority Level (low) M\_HPL1 EQU 1; Host Interrupt Priority Level (high)M\_SOL EQU \$C; SSI0 Interrupt Priority Level MaskM\_SOL0 EQU 2; SSI0 Interrupt Priority Level (low)M\_SOL1 EQU 3; SSI0 Interrupt Priority Level (high)M\_S1L EQU \$30; SSI1 Interrupt Priority Level (MaskM\_S1L0 EQU 4; SSI1 Interrupt Priority Level (low)M\_S1L1 EQU 5; SSI1 Interrupt Priority Level (low)M\_S2L2 EQU \$C0; SCI Interrupt Priority Level (high)M\_SCL0 EQU 6; SCI Interrupt Priority Level (low)M\_SCL1 EQU 7; SCI Interrupt Priority Level (high)M\_T0L EQU \$300; TIMER Interrupt Priority Level MaskM\_T0L0 EQU 8; TIMER Interrupt Priority Level (low) M\_HPL1 EQU 1 ; Host Interrupt Priority Level (high) M\_TOLO EQU 8 ; TIMER Interrupt Priority Level (low) M\_TOL1 EQU 9 ; TIMER Interrupt Priority Level (high) ;------; EQUATES for TIMER ; ; Register Addresses Of TIMER0 ; ; Timer 0 Control/Status Register M\_TCSR0 EQU \$FFFF8F

### r Consumption Benchmark

M\_TLR0 EQU \$FFFF8E ; TIMER0 Load Reg M\_ILKO EQU ŞFFFF8E M\_TCPR0 EQU ŞFFFF8D M\_TCR0 EQU ŞFFFF8C ; TIMER0 Compare Register ; TIMER0 Count Register Register Addresses Of TIMER1 ; M\_TCSR1 EQU \$FFFF8B; TIMER1 Control/Status ReM\_TLR1 EQU \$FFFF8A; TIMER1 Load RegM\_TCPR1 EQU \$FFFF89; TIMER1 Compare RegisterM\_TCR1 EQU \$FFFF88; TIMER1 Count Register ; TIMER1 Control/Status Register Register Addresses Of TIMER2 ; M\_TCSR2 EQU \$FFFF87; TIMER2 Control/Status RegisterM\_TLR2 EQU \$FFFF86; TIMER2 Load RegM\_TCPR2 EQU \$FFFF85; TIMER2 Compare RegisterM\_TCR2 EQU \$FFFF84; TIMER2 Count RegisterM\_TPLR EQU \$FFFF83; TIMER Prescaler Load RegisterM\_TPCR EQU \$FFFF82; TIMER Prescalar Count Register : Timer Control/Status Register Bit Flags M\_TE EQU 0 M\_TOIE EQU 1 M\_TCIE EQU 2 M\_TC EQU \$F0 M\_INV EQU 8 M\_TRM EQU 9 M\_DIR EQU 11 M\_DI EQU 12 M\_DO EQU 13 M\_PCE EQU 15 M\_TOF EQU 20 M TCF EOU 21 M TE EOU O ; Timer Enable ; Timer Overflow Interrupt Enable ; Timer Compare Interrupt Enable ; Timer Control Mask (TC0-TC3) ; Inverter Bit ; Timer Restart Mode ; Direction Bit ; Data Input ; Data Output ; Prescaled Clock Enable ; Timer Overflow Flag M\_TCF EQU 21 ; Timer Compare Flag ; Timer Prescaler Register Bit Flags M\_PS EQU \$600000 ; Prescaler Source Mask M\_PS0 EQU 21 M\_PS1 EQU 22 ; Timer Control Bits M\_TC0 EQU 4 M\_TC1 EQU 5 ; Timer Control 0 M\_TC1 EQU 5 M\_TC2 EQU 6 ; Timer Control 1 ; Timer Control 2 M\_TC3 EQU 7 ; Timer Control 3 ;-----; EQUATES for Direct Memory Access (DMA) ; ; ;------Register Addresses Of DMA M\_DSTR EQU FFFF4 ; DMA Status Register M\_DOR0 EQU \$FFFFF3 ; DMA Offset Register 0 M\_DOR1 EQU \$FFFFF2 ; DMA Offset Register 1 M\_DOR2 EQU \$FFFFF1 ; DMA Offset Register 2 M\_DOR3 EQU \$FFFFF0 ; DMA Offset Register 3

### **Ordering Information**

Consult a Freescale Semiconductor sales office or authorized distributor to determine product availability and place an order.

| Part     | Supply<br>Voltage | Package Type                   | Pin<br>Count | Core<br>Frequency<br>(MHz) | Solder Spheres | Order Number  |

|----------|-------------------|--------------------------------|--------------|----------------------------|----------------|---------------|

| DSP56321 | 1.6 V core        | Molded Array Process-Ball Grid | 196          | 200                        | Lead-free      | DSP56321VL200 |

|          | 3.3 V I/O         | Array (MAP-BGA)                |              |                            | Lead-bearing   | DSP56321VF200 |

|          |                   |                                |              | 220                        | Lead-free      | DSP56321VL220 |

|          |                   |                                |              |                            | Lead-bearing   | DSP56321VF220 |

|          |                   |                                |              | 240                        | Lead-free      | DSP56321VL240 |

|          |                   |                                |              |                            | Lead-bearing   | DSP56321VF240 |

|          |                   |                                |              | 275                        | Lead-free      | DSP56321VL275 |

|          |                   |                                |              |                            | Lead-bearing   | DSP56321VF275 |

### How to Reach Us:

Home Page: www.freescale.com

E-mail:

support@freescale.com

### USA/Europe or Locations not listed:

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GMBH Technical Information Center Schatzbogen 7 81829 München, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064, Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T. Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Document Order No.: DSP56321 Rev. 11 2/2005 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2001, 2005.