Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

### Details

E·XFl

| Details                 |                                                            |

|-------------------------|------------------------------------------------------------|

| Product Status          | Active                                                     |

| Туре                    | Fixed Point                                                |

| Interface               | Host Interface, SSI, SCI                                   |

| Clock Rate              | 220MHz                                                     |

| Non-Volatile Memory     | ROM (576B)                                                 |

| On-Chip RAM             | 576kB                                                      |

| Voltage - I/O           | 3.30V                                                      |

| Voltage - Core          | 1.60V                                                      |

| Operating Temperature   | -40°C ~ 100°C                                              |

| Mounting Type           | Surface Mount                                              |

| Package / Case          | 196-LBGA                                                   |

| Supplier Device Package | 196-MAPBGA (15x15)                                         |

| Purchase URL            | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=dsp56321vl220 |

|                         |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Product Documentation**

The documents listed in **Table 2** are required for a complete description of the DSP56321 device and are necessary to design properly with the part. Documentation is available from a local Freescale distributor, a Freescale semiconductor sales office, or a Freescale Semiconductor Literature Distribution Center. For documentation updates, visit the Freescale DSP website. See the contact information on the back cover of this document.

| Name                         | Description                                                                                               | Order Number                     |

|------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------|

| DSP56321<br>Reference Manual | Detailed functional description of the DSP56321 memory configuration, operation, and register programming | DSP56321RM                       |

| DSP56300 Family<br>Manual    | Detailed description of the DSP56300 family processor core and instruction set                            | DSP56300FM                       |

| Application Notes            | Documents describing specific applications or optimized device operation including code examples          | See the DSP56321 product website |

| Table 2.         DSP56321 Documentation |

|-----------------------------------------|

|-----------------------------------------|

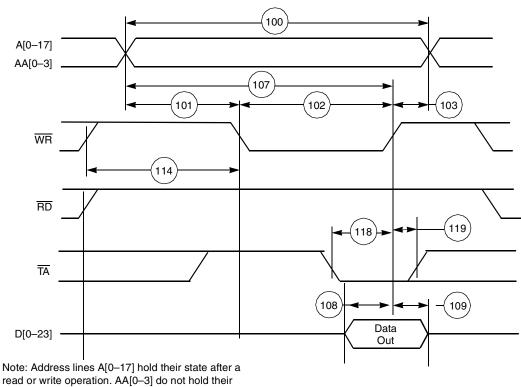

# 1.4 External Memory Expansion Port (Port A)

**Note:** When the DSP56321 enters a low-power standby mode (stop or wait), it releases bus mastership and tristates the relevant Port A signals: A[0–17], D[0–23], AA[0–3], RD, WR, BB.

### 1.4.1 External Address Bus

| Signal Name | Туре   | State During<br>Reset, Stop,<br>or Wait | Signal Description                                                                                                                                                                                                                                                                                        |

|-------------|--------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A[0–17]     | Output | Tri-stated                              | Address Bus—When the DSP is the bus master, A[0–17] are active-high outputs that specify the address for external program and data memory accesses. Otherwise, the signals are tri-stated. To minimize power dissipation, A[0–17] do not change state when external memory spaces are not being accessed. |

Table 1-5. External Address Bus Signals

### 1.4.2 External Data Bus

Table 1-6.

External Data Bus Signals

| Signal Name | Туре          | State During<br>Reset | State During<br>Stop or Wait                                           | Signal Description                                                                                                                                                                                                                                                                                                                                                |

|-------------|---------------|-----------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[0–23]     | Input/ Output | Ignored Input         | Last state:<br><i>Input</i> : Ignored<br><i>Output</i> :<br>Last value | <b>Data Bus</b> —When the DSP is the bus master, D[0–23] are active-high, bidirectional input/outputs that provide the bidirectional data bus for external program and data memory accesses. Otherwise, D[0–23] drivers are tristated. If the last state is output, these lines have weak keepers to maintain the last output state if all drivers are tristated. |

### 1.4.3 External Bus Control

| Table 1-7. | External Bus Control Signals |

|------------|------------------------------|

|------------|------------------------------|

| Signal Name | Туре   | State During<br>Reset, Stop, or<br>Wait | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|--------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AA[0-3]     | Output | Tri-stated                              | Address Attribute—When defined as AA, these signals can be used as chip selects or additional address lines. The default use defines a priority scheme under which only one AA signal can be asserted at a time. Setting the AA priority disable (APD) bit (Bit 14) of the Operating Mode Register, the priority mechanism is disabled and the lines can be used together as four external lines that can be decoded externally into 16 chip select signals. |

| RD          | Output | Tri-stated                              | <b>Read Enable</b> —When the DSP is the bus master, $\overline{RD}$ is an active-low output that is asserted to read external memory on the data bus (D[0–23]). Otherwise, $\overline{RD}$ is tri-stated.                                                                                                                                                                                                                                                    |

| WR          | Output | Tri-stated                              | <b>Write Enable</b> —When the DSP is the bus master, $\overline{WR}$ is an active-low output that is asserted to write external memory on the data bus (D[0–23]). Otherwise, the signals are tri-stated.                                                                                                                                                                                                                                                     |

| Table 1-10. | Host Interface | (Continued) |

|-------------|----------------|-------------|

|-------------|----------------|-------------|

| Signal Name        | Туре                                                                                               | State During<br>Reset <sup>1,2</sup>           | Signal Description                                                                                                                                                                                                                                                                                                                                                                |

|--------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HDS/HDS            | Input                                                                                              | Ignored Input                                  | <b>Host Data Strobe</b> —When the HI08 is programmed to interface with a single-<br>data-strobe host bus and the HI function is selected, this signal is the host data<br>strobe (HDS) Schmitt-trigger input. The polarity of the data strobe is<br>programmable but is configured as active-low (HDS) following reset.                                                           |

| HWR/HWR            | Input                                                                                              |                                                | <b>Host Write Data</b> —When the HI08 is programmed to interface with a double-<br>data-strobe host bus and the HI function is selected, this signal is the host write<br>data strobe (HWR) Schmitt-trigger input. The polarity of the data strobe is<br>programmable but is configured as active-low (HWR) following reset.                                                      |

| PB12               | Input or Output                                                                                    |                                                | <b>Port B 12</b> —When the HI08 is configured as GPIO through the HI08 Port Control Register, this signal is individually programmed as an input or output through the HI08 Data Direction Register.                                                                                                                                                                              |

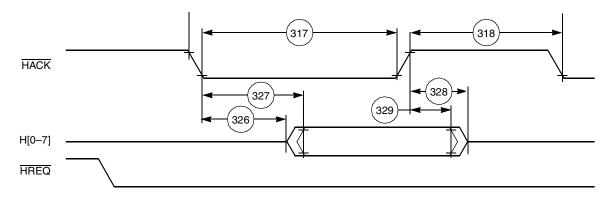

| HREQ/HREQ          | Output                                                                                             | Ignored Input                                  | <b>Host Request</b> —When the HI08 is programmed to interface with a single host request host bus and the HI function is selected, this signal is the host request (HREQ) output. The polarity of the host request is programmable but is configured as active-low (HREQ) following reset. The host request may be programmed as a driven or open-drain output.                   |

| HTRQ/HTRQ          | Output                                                                                             |                                                | <b>Transmit Host Request</b> —When the HI08 is programmed to interface with a double host request host bus and the HI function is selected, this signal is the transmit host request (HTRQ) output. The polarity of the host request is programmable but is configured as active-low (HTRQ) following reset. The host request may be programmed as a driven or open-drain output. |

| PB14               | Input or Output                                                                                    |                                                | <b>Port B 14</b> —When the HI08 is configured as GPIO through the HI08 Port Control Register, this signal is individually programmed as an input or output through the HI08 Data Direction Register.                                                                                                                                                                              |

| HACK/HACK          | Input                                                                                              | Ignored Input                                  | <b>Host Acknowledge</b> —When the HI08 is programmed to interface with a single host request host bus and the HI function is selected, this signal is the host acknowledge (HACK) Schmitt-trigger input. The polarity of the host acknowledge is programmable but is configured as active-low (HACK) after reset.                                                                 |

| HRRQ/HRRQ          | Output                                                                                             |                                                | <b>Receive Host Request</b> —When the HI08 is programmed to interface with a double host request host bus and the HI function is selected, this signal is the receive host request (HRRQ) output. The polarity of the host request is programmable but is configured as active-low (HRRQ) after reset. The host request may be programmed as a driven or open-drain output.       |

| PB15               | Input or Output                                                                                    |                                                | <b>Port B 15</b> —When the HI08 is configured as GPIO through the HI08 Port Control Register, this signal is individually programmed as an input or output through the HI08 Data Direction Register.                                                                                                                                                                              |

| • If ti<br>• If ti | he Stop state, the sig<br>he last state is input,<br>he last state is outpu<br>Wait processing sta | the signal is an igno<br>t, these lines have w | ored input.<br>veak keepers that maintain the last output state even if the drivers are tri-stated.                                                                                                                                                                                                                                                                               |

als/Connections

# 1.7 Enhanced Synchronous Serial Interface 0 (ESSI0)

Two synchronous serial interfaces (ESSI0 and ESSI1) provide a full-duplex serial port for serial communication with a variety of serial devices, including one or more industry-standard codecs, other DSPs, microprocessors, and peripherals that implement the Freescale serial peripheral interface (SPI).

| Signal Name | Туре            | State During<br>Reset <sup>1,2</sup> | Signal Description                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|-----------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SC00        | Input or Output | Ignored Input                        | <b>Serial Control 0</b> —For asynchronous mode, this signal is used for the receive clock I/O (Schmitt-trigger input). For synchronous mode, this signal is used either for transmitter 1 output or for serial I/O flag 0.                                                                                                                                                                                 |

| PC0         | Input or Output |                                      | <b>Port C 0</b> —The default configuration following reset is GPIO input PC0. When configured as PC0, signal direction is controlled through the Port C Direction Register. The signal can be configured as ESSI signal SC00 through the Port C Control Register.                                                                                                                                          |

| SC01        | Input/Output    | Ignored Input                        | <b>Serial Control 1</b> —For asynchronous mode, this signal is the receiver frame sync I/O. For synchronous mode, this signal is used either for transmitter 2 output or for serial I/O flag 1.                                                                                                                                                                                                            |

| PC1         | Input or Output |                                      | <b>Port C 1</b> —The default configuration following reset is GPIO input PC1. When configured as PC1, signal direction is controlled through the Port C Direction Register. The signal can be configured as an ESSI signal SC01 through the Port C Control Register.                                                                                                                                       |

| SC02        | Input/Output    | Ignored Input                        | Serial Control Signal 2—The frame sync for both the transmitter and receiver<br>in synchronous mode, and for the transmitter only in asynchronous mode. When<br>configured as an output, this signal is the internally generated frame sync signal.<br>When configured as an input, this signal receives an external frame sync signal<br>for the transmitter (and the receiver in synchronous operation). |

| PC2         | Input or Output |                                      | <b>Port C 2</b> —The default configuration following reset is GPIO input PC2. When configured as PC2, signal direction is controlled through the Port C Direction Register. The signal can be configured as an ESSI signal SC02 through the Port C Control Register.                                                                                                                                       |

| SCK0        | Input/Output    | Ignored Input                        | <b>Serial Clock</b> —Provides the serial bit rate clock for the ESSI. The SCK0 is a clock input or output, used by both the transmitter and receiver in synchronous modes or by the transmitter in asynchronous modes.                                                                                                                                                                                     |

|             |                 |                                      | Although an external serial clock can be independent of and asynchronous to<br>the DSP system clock, it must exceed the minimum clock cycle time of 6T (that<br>is, the system clock frequency must be at least three times the external ESSI<br>clock frequency). The ESSI needs at least three DSP phases inside each half of<br>the serial clock.                                                       |

| PC3         | Input or Output |                                      | <b>Port C 3</b> —The default configuration following reset is GPIO input PC3. When configured as PC3, signal direction is controlled through the Port C Direction Register. The signal can be configured as an ESSI signal SCK0 through the Port C Control Register.                                                                                                                                       |

| SRD0        | Input           | Ignored Input                        | Serial Receive Data—Receives serial data and transfers the data to the ESSI Receive Shift Register. SRD0 is an input when data is received.                                                                                                                                                                                                                                                                |

| PC4         | Input or Output |                                      | <b>Port C 4</b> —The default configuration following reset is GPIO input PC4. When configured as PC4, signal direction is controlled through the Port C Direction Register. The signal can be configured as an ESSI signal SRD0 through the Port C Control Register.                                                                                                                                       |

| Table 1-11. | Enhanced Synchronous Serial Interface 0 |

|-------------|-----------------------------------------|

|             | Ennancea eynomeneae eena maenaee e      |

### 2.2 Thermal Characteristics

| Thermal Resistance Characteristic                                                 | Symbol            | MAP-BGA<br>Value | Unit |

|-----------------------------------------------------------------------------------|-------------------|------------------|------|

| Junction-to-ambient, natural convection, single-layer board (1s) <sup>1,2</sup>   | R <sub>θJA</sub>  | 44               | °C/W |

| Junction-to-ambient, natural convection, four-layer board (2s2p) <sup>1,3</sup>   | R <sub>θJMA</sub> | 25               | °C/W |

| Junction-to-ambient, @200 ft/min air flow, single-layer board (1s) <sup>1,3</sup> | R <sub>θJMA</sub> | 35               | °C/W |

| Junction-to-ambient, @200 ft/min air flow, four-layer board (2s2p) <sup>1,3</sup> | $R_{	heta JMA}$   | 22               | °C/W |

| Junction-to-board <sup>4</sup>                                                    | R <sub>θJB</sub>  | 13               | °C/W |

| Junction-to-case thermal resistance <sup>5</sup>                                  | R <sub>θJC</sub>  | 7                | °C/W |

Table 2-2. Thermal Characteristics

**Notes:** 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

2. Per SEMI G38-87 and JEDEC JESD51-2 with the single-layer board horizontal.

**3.** Per JEDEC JESD51-6 with the board horizontal.

4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

## **2.3 DC Electrical Characteristics**

| Characteristics                                                                                                                                                                               | Symbol                                                  | Min                                   | Тур        | Max                                                                     | Unit        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------|------------|-------------------------------------------------------------------------|-------------|

| Supply voltage <sup>1</sup> :<br>• Core (V <sub>CCQL</sub> )<br>• I/O (V <sub>CCQH</sub> , V <sub>CCA</sub> , V <sub>CCD</sub> , V <sub>CCC</sub> , V <sub>CCH</sub> , and V <sub>CCS</sub> ) |                                                         | 1.5<br>3.0                            | 1.6<br>3.3 | 1.7<br>3.6                                                              | V<br>V      |

| Input high voltage<br>• D[0-23], BG, BB, TA<br>• MOD/IRQ <sup>2</sup> RESET, PINIT/NMI and all<br>JTAG/ESSI/SCI/Timer/HI08 pins<br>• EXTAL <sup>9</sup>                                       | V <sub>IH</sub><br>V <sub>IHP</sub><br>V <sub>IHX</sub> | 2.0<br>2.0<br>0.8 × V <sub>CCQH</sub> | <br>       | V <sub>CCQH</sub> + 0.3<br>V <sub>CCQH</sub> + 0.3<br>V <sub>CCQH</sub> | ><br>><br>> |

| Input low voltage<br>• D[0–23], BG, BB, TA, MOD/IRQ <sup>2</sup> , RESET, PINIT<br>• All JTAG/ESSI/SCI/Timer/HI08 pins<br>• EXTAL <sup>9</sup>                                                | V <sub>IL</sub><br>V <sub>ILP</sub><br>V <sub>ILX</sub> | -0.3<br>-0.3<br>-0.3                  |            | 0.8<br>0.8<br>$0.2 \times V_{CCQH}$                                     | V<br>V<br>V |

| Input leakage current                                                                                                                                                                         | I <sub>IN</sub>                                         | -10                                   | —          | 10                                                                      | μΑ          |

| High impedance (off-state) input current<br>(@ 2.4 V / 0.4 V)                                                                                                                                 | I <sub>TSI</sub>                                        | -10                                   | —          | 10                                                                      | μA          |

| Output high voltage <sup>8</sup><br>• TTL $(I_{OH} = -0.4 \text{ mA})^6$<br>• CMOS $(I_{OH} = -10 \mu A)^6$                                                                                   | V <sub>OH</sub>                                         | 2.4<br>V <sub>CCQH</sub> – 0.01       |            |                                                                         | V<br>V      |

| Output low voltage <sup>8</sup><br>• TTL ( $I_{OL} = 3.0 \text{ mA}$ ) <sup>6</sup><br>• CMOS ( $I_{OL} = 10 \text{ µA}$ ) <sup>6</sup>                                                       | V <sub>OL</sub>                                         |                                       | —          | 0.4<br>0.01                                                             | V<br>V      |

| Table 2-3. | DC Electrical | Characteristics <sup>7</sup> |

|------------|---------------|------------------------------|

|------------|---------------|------------------------------|

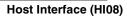

| Table 2-7. | Reset, Stop, Mode Select, and Interrupt Timing <sup>5</sup> | (CONTINUED) |

|------------|-------------------------------------------------------------|-------------|

|------------|-------------------------------------------------------------|-------------|

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                            | 200           | MHz                          | 220         | MHz                          | 240           | MHz                          | 275           | MHz                             |                      |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------|------------------------------|-------------|------------------------------|---------------|------------------------------|---------------|---------------------------------|----------------------|

| No. | Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Expression                                                                 | Min Max       |                              | Min Max     |                              | Min           | Max Min                      |               | Max                             | Unit                 |

|     | Delay from RD assertion to interrupt request deassertion for level sensitive fast interrupts <sup>1, 6, 7</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | (WS + 3.25) × T <sub>C</sub> –<br>10.94                                    |               | Note 7                       |             | Note 7                       | _             | Note 7                       | _             | Note 7                          | ns                   |

|     | Delay from $\overline{\text{WR}}$ assertion to interrupt<br>request deassertion for level sensitive<br>fast interrupts <sup>1, 6, 7</sup><br>• SRAM WS = 3<br>• SRAM WS $\geq$ 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | (WS + 3) × T <sub>C</sub> – 10.94<br>(WS + 2.5) × T <sub>C</sub> – 10.94   |               | Note 7<br>Note 7             |             | Note 7<br>Note 7             |               | Note 7<br>Note 7             |               | Note 7<br>Note 7                | ns<br>ns             |

|     | Duration for IRQA assertion to recover from Stop state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                            | 8.0           | —                            | 8.0         | —                            | 8.0           | —                            | 8.0           | —                               | ns                   |

|     | <ul> <li>Delay from IRQA assertion to fetch of first instruction (when exiting Stop)<sup>2, 3</sup></li> <li>DPLL is not active during Stop (PCTL Bit 1 = 0) and Stop delay is enabled (Operating Mode Register Bit 6 = 0)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DPLT + (128K × T <sub>C</sub> )                                            | 662.2<br>μs   | 209.9<br>ms                  | 662.2<br>μs | 209.9<br>ms                  | 662.2<br>μs   | 209.9<br>ms                  | 662.2<br>μs   | 209.9<br>ms                     | _                    |

|     | <ul> <li>DPLL is not active during Stop<br/>(PCTL Bit 1 = 0) and Stop delay is<br/>not enabled (Operating Mode<br/>Register Bit 6 = 1)</li> <li>DPLL is active during Stop (PCTL<br/>Bit 1 = 1; Implies No Stop Delay)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DPLT + (23.75 ± 0.5) ×<br>T <sub>C</sub><br>(10.0 ± 1.75) × T <sub>C</sub> | 6.9<br>41.25  | 188.8<br>58.8                | 6.9<br>37.5 | 188.8<br>53.3                | 6.9<br>34.4   | 188.8<br>49.0                | 6.9<br>30.0   | 43.0                            | μs<br>ns             |

|     | <ul> <li>Duration of level sensitive IRQA assertion to ensure interrupt service (when exiting Stop)<sup>2, 3</sup></li> <li>DPLL is not active during Stop (PCTL bit 1 = 0) and Stop delay is enabled (Operating Mode Register Transport of the sensitive of</li></ul> | DPLT + (128 K × T <sub>C</sub> )                                           | 805.4         |                              | 805.4       |                              | 805.4         |                              | 805.4         | _                               | μs                   |

|     | <ul> <li>(PCTL bit 1 = 0) and Stop delay is<br/>not enabled (Operating Mode<br/>Register Bit 6 = 1)</li> <li>DPLL is active during Stop ((PCTL</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DPLT + (20.5 ±0.5) × T <sub>C</sub><br>5.5 × T <sub>C</sub>                | 150.1<br>27.5 | _                            | 150.1<br>25 | _                            | 150.1<br>22.9 | _                            | 150.1<br>20.0 | _                               | μs<br>ns             |

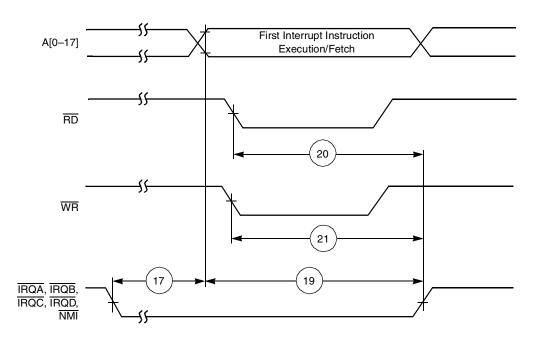

| 27  | bit 1 = 0; implies no Stop delay)<br>Interrupt Request Rate<br>• HI08, ESSI, SCI, Timer<br>• DMA<br>• IRQ, NMI (edge trigger)<br>• IRQ, NMI (level trigger)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12T <sub>C</sub><br>8T <sub>C</sub><br>8T <sub>C</sub><br>12T <sub>C</sub> |               | 60.0<br>40.0<br>40.0<br>60.0 | <br>        | 54.6<br>36.4<br>36.4<br>54.6 |               | 50.0<br>33.4<br>33.4<br>50.0 |               | 43.7<br>29.2<br>29.2<br>43.7    | ns<br>ns<br>ns<br>ns |

| 28  | <ul> <li>DMA Request Rate</li> <li>Data read from HI08, ESSI, SCI</li> <li>Data write to HI08, ESSI, SCI</li> <li>Timer</li> <li>IRQ, NMI (edge trigger)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6T <sub>C</sub><br>7T <sub>C</sub><br>2T <sub>C</sub><br>3T <sub>C</sub>   | <br> <br>     | 30.0<br>35.0<br>10.0<br>15.0 |             | 27.3<br>31.9<br>9.1<br>13.7  |               | 25.0<br>29.2<br>8.3<br>12.5  | <br>          | 21.84<br>25.48<br>7.28<br>10.92 | ns<br>ns<br>ns<br>ns |

|     | Delay from IRQA, IRQB, IRQC, IRQD,<br>NMI assertion to external memory<br>(DMA source) access address out<br>valid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4.25 × T <sub>C</sub> + 2.0                                                | 23.25         |                              | 21.34       |                              | 19.72         |                              | 17.45         | _                               | ns                   |

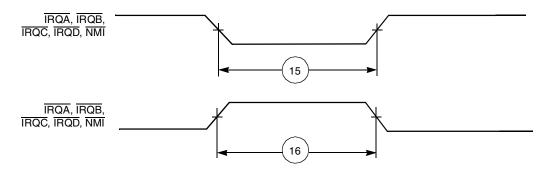

a) First Interrupt Instruction Execution

b) General-Purpose I/O

Figure 2-4. External Fast Interrupt Timing

Figure 2-5. External Interrupt Timing (Negative Edge-Triggered)

state after a read or write operation.

### 2.4.5.2 Asynchronous Bus Arbitration Timings

| No.                                                                                                         | Characteristics                                                                        | Expression   | 200 | MHz  | 220  | MHz  | 240  | MHz  | 275   | Mhz  | Uni |  |

|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------|-----|------|------|------|------|------|-------|------|-----|--|

| NO.                                                                                                         | Unaracteristics                                                                        | Expression   | Min | Max  | Min  | Max  | Min  | Max  | Min   | Max  | t   |  |

| 250                                                                                                         | $\overline{\text{BB}}$ assertion window from $\overline{\text{BG}}$ input deassertion. | 2.5 × Tc + 5 |     | 17.5 |      | 16.4 | —    | 15.4 | —     | 14.1 | ns  |  |

| 251                                                                                                         | Delay from $\overline{BB}$ assertion to $\overline{BG}$ assertion                      | 2 × Tc + 5   | 15  | —    | 14.1 |      | 13.3 |      | 12.27 | _    | ns  |  |

| <b>Notes:</b> 1. Bit 13 in the Operating Mode Register must be set to enable Asynchronous Arbitration mode. |                                                                                        |              |     |      |      |      |      |      |       |      |     |  |

| Table 2-9. | Asynchronous | <b>Bus Timings</b> |

|------------|--------------|--------------------|

|------------|--------------|--------------------|

2. To guarantee timings 250 and 251, it is recommended that you assert non-overlapping BG inputs to different DSP56300 devices (on the same bus), as shown in Figure 2-12, where BG1 is the BG signal for one DSP56300 device while BG2 is the BG signal for a second DSP56300 device.

Table 2-10.

Host Interface Timings<sup>1,2,12</sup> (Continued)

| No.                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                   | Characteristic <sup>10</sup>                                                                                                                                                                                                                                                             | Expression      | 200      | MHz        | 220 MHz  |          | 240 MHz |          | 275 MHz  |           | Uni    |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------|------------|----------|----------|---------|----------|----------|-----------|--------|--|

| NO.                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                   | Characteristic                                                                                                                                                                                                                                                                           | Expression      | Min      | Max        | Min      | Max      | Min     | Max      | Min      | Мах       | t      |  |

| Notes:                                                                                                                                                                                                                          | 1.                                                                                                                                                                                                                                                                                                                                                                                                | See the Programmer's Model section in the chapter on the HI08 in the DSP56321 Reference Manual.                                                                                                                                                                                          |                 |          |            |          |          |         |          |          |           |        |  |

|                                                                                                                                                                                                                                 | <ol> <li>In the timing diagrams below, the controls pins are drawn as active low. The pin polarity is programmable.</li> <li>This timing is applicable only if two consecutive reads from one of these registers are executed.</li> <li>The data strobe is Host Read (HRD) or Host Write (HWR) in the Dual Data Strobe mode and Host Data Strobe (HDS) in the Single Data Strobe mode.</li> </ol> |                                                                                                                                                                                                                                                                                          |                 |          |            |          |          |         |          |          |           |        |  |

|                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                          |                 |          |            |          |          |         |          |          |           |        |  |

|                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                          |                 |          |            |          |          | n the   |          |          |           |        |  |

| <ol> <li>The read data strobe is HRD in the Dual Data Strobe mode and HDS in the Single Data Strobe mode.</li> <li>The write data strobe is HWR in the Dual Data Strobe mode and HDS in the Single Data Strobe mode.</li> </ol> |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                          |                 |          |            |          |          |         |          |          |           |        |  |

|                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                          |                 |          |            | a Strobe | mode.    |         |          |          |           |        |  |

|                                                                                                                                                                                                                                 | 7.                                                                                                                                                                                                                                                                                                                                                                                                | The host request is HREQ in the Single Host Request mode and HRRQ and HTRQ in the Double Host Request mode.                                                                                                                                                                              |                 |          |            |          |          |         |          |          |           |        |  |

|                                                                                                                                                                                                                                 | 8.                                                                                                                                                                                                                                                                                                                                                                                                | The "Last Data Register" is the register at address \$7, which is the last location to be read or written in data transfers. This is RXL/TXL in the Big Endian mode (HLEND = 0; HLEND is the Interface Control Register bit 7—ICR[7]), or RXH/TXH in the Little Endian mode (HLEND = 1). |                 |          |            |          |          |         |          |          |           |        |  |

|                                                                                                                                                                                                                                 | 9.                                                                                                                                                                                                                                                                                                                                                                                                | In this calculation, the host request signal is pulled up by a 4.7 k $\Omega$ resistor in the Open-drain mode.                                                                                                                                                                           |                 |          |            |          |          |         |          |          |           |        |  |

|                                                                                                                                                                                                                                 | 10.                                                                                                                                                                                                                                                                                                                                                                                               | $V_{CCOH} = 3.3 V \pm 0.3 V$ , $V_{CCOL} = 1.6 V$                                                                                                                                                                                                                                        |                 |          |            |          |          |         |          |          |           |        |  |

|                                                                                                                                                                                                                                 | 11.                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                          | om the "Last Da | ta Regis | ter" is fo | llowed b | y a read |         | e RXL, F | XM, or I | RXH reg   | isters |  |

|                                                                                                                                                                                                                                 | 12                                                                                                                                                                                                                                                                                                                                                                                                | After the external host writes a new value                                                                                                                                                                                                                                               | -               |          |            |          | -        |         |          |          | (a aa)(2) | . To   |  |

Figure 2-13. Host Interrupt Vector Register (IVR) Read Timing Diagram

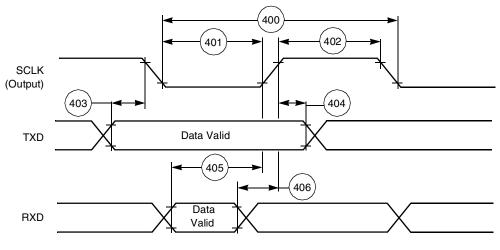

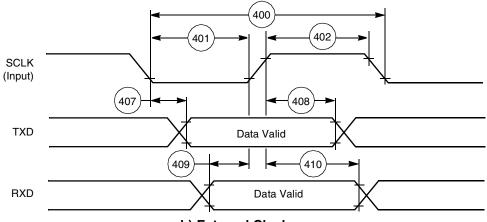

#### **SCI** Timing 2.4.7

| N   | 0h                                                                    | 0                             | Formerstein                           | 200   | MHz  | 220 MHz |      | z 240 MHz |      | 275 MHz |       | Uni |

|-----|-----------------------------------------------------------------------|-------------------------------|---------------------------------------|-------|------|---------|------|-----------|------|---------|-------|-----|

| No. | Characteristics <sup>1</sup>                                          | Symbol                        | Expression                            | Min   | Мах  | Min     | Мах  | Min       | Max  | Min     | Мах   | t   |

| 400 | Synchronous clock cycle                                               | t <sub>SCC</sub> <sup>2</sup> | $16 \times T_C$                       | 80.0  |      | 72.8    | _    | 66.7      | —    | 58.0    | _     | ns  |

| 401 | Clock low period                                                      |                               | t <sub>SCC</sub> /2 -10.0             | 30.0  |      | 26.4    |      | 23.4      |      | 19.0    |       | ns  |

| 402 | Clock high period                                                     |                               | t <sub>SCC</sub> /2 -10.0             | 30.0  |      | 26.4    |      | 23.4      |      | 19.0    |       | ns  |

| 403 | Output data setup to<br>clock falling edge<br>(internal clock)        |                               | $t_{SCC}/4 + 0.5 \times T_C - 17.0$   | 5.5   | —    | 3.5     | —    | 1.76      | —    | -0.68   | _     | ns  |

| 404 | Output data hold after<br>clock rising edge (internal<br>clock)       |                               | $t_{SCC}/4$ –1.5 × T <sub>C</sub>     | 13    |      | 11.5    | _    | 10        | _    | 9.04    | _     | ns  |

| 405 | Input data setup time<br>before clock rising edge<br>(internal clock) |                               | $t_{SCC}/4 + 0.5 \times T_{C} + 25.0$ | 47.5  |      | 45.5    |      | 43.8      |      | 41.32   |       | ns  |

| 406 | Input data not valid<br>before clock rising edge<br>(internal clock)  |                               | $t_{SCC}/4 + 0.5 \times T_C - 5.5$    | _     | 17.0 | _       | 15.0 | _         | 13.8 | _       | 10.81 | ns  |

| 407 | Clock falling edge to<br>output data valid (external<br>clock)        |                               |                                       | _     | 32.0 | _       | 32.0 | _         | 32.0 | _       | 32.0  | ns  |

| 408 | Output data hold after<br>clock rising edge<br>(external clock)       |                               | T <sub>C</sub> + 8.0                  | 13.0  | _    | 12.6    |      | 12.2      | _    | 11.64   | _     | ns  |

| 409 | Input data setup time<br>before clock rising edge<br>(external clock) |                               |                                       | 0.0   | _    | 0.0     |      | 0.0       | _    | 0.0     | _     | ns  |

| 410 | Input data hold time after<br>clock rising edge<br>(external clock)   |                               |                                       | 9.0   | _    | 9.0     | _    | 9.0       | _    | 9.0     | _     | ns  |

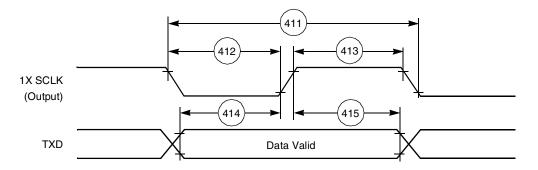

| 411 | Asynchronous clock cycle                                              | t <sub>ACC</sub> <sup>3</sup> | $64 \times T_C$                       | 320.0 |      | 291.2   |      | 266.9     | _    | 232.0   |       | ns  |