# E·XFL

#### NXP USA Inc. - SPAKDSP321VF275 Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

| Details                 |                                                                         |

|-------------------------|-------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                |

| Туре                    | Fixed Point                                                             |

| Interface               | Host Interface, SSI, SCI                                                |

| Clock Rate              | 275MHz                                                                  |

| Non-Volatile Memory     | ROM (576B)                                                              |

| On-Chip RAM             | 576kB                                                                   |

| Voltage - I/O           | 3.30V                                                                   |

| Voltage - Core          | 1.60V                                                                   |

| Operating Temperature   | -40°C ~ 105°C (TJ)                                                      |

| Mounting Type           | Surface Mount                                                           |

| Package / Case          | 196-BGA                                                                 |

| Supplier Device Package | 196-MAPBGA (15x15)                                                      |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/spakdsp321vf275 |

|                         |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### External Memory Expansion Port (Port A)

| Signal Name | Туре          | State During<br>Reset, Stop, or<br>Wait                                                                                                                                                                                   | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TA          | Input         | Ignored Input                                                                                                                                                                                                             | Transfer Acknowledge—If the DSP56321 is the bus master and there is no<br>external bus activity, or the DSP56321 is not the bus master, the TA input is<br>ignored. The TA input is a data transfer acknowledge (DTACK) function that can<br>extend an external bus cycle indefinitely. Any number of wait states (1,<br>2infinity) can be added to the wait states inserted by the bus control register<br>(BCR) by keeping TA deasserted. In typical operation, TA is deasserted at the<br>start of a bus cycle, is asserted to enable completion of the bus cycle, and is<br>                                                                                                                                                                                                                                                                                                                                                                                       |

| BR          | Output        | Reset: Output<br>(deasserted)<br>State during<br>Stop/Wait<br>depends on BRH<br>bit setting:<br>• BRH = 0: Output<br>(deasserted)<br>• BRH = 1:<br>Maintains last<br>state (that is, if<br>asserted, remains<br>asserted) | <b>Bus Request</b> —Asserted when the DSP requests bus mastership. $\overline{BR}$ is deasserted when the DSP no longer needs the bus. $\overline{BR}$ may be asserted or deasserted independently of whether the DSP56321 is a bus master or a bus slave. Bus "parking" allows $\overline{BR}$ to be deasserted even though the DSP56321 is the bus master. (See the description of bus "parking" in the $\overline{BB}$ signal description.) The bus request hold (BRH) bit in the BCR allows $\overline{BR}$ to be asserted under software control even though the DSP does not need the bus. $\overline{BR}$ is typically sent to an external bus arbitrator that controls the priority, parking, and tenure of each master on the same external bus. $\overline{BR}$ is affected only by DSP requests for the external bus, never for the internal bus. During hardware reset, $\overline{BR}$ is deasserted and the arbitration is reset to the bus slave state. |

| BG          | Input         | Ignored Input                                                                                                                                                                                                             | Bus Grant—Asserted by an external bus arbitration circuit when the DSP56321         becomes the next bus master. When BG is asserted, the DSP56321 must wait         until BB is deasserted before taking bus mastership. When BG is deasserted,         bus mastership is typically given up at the end of the current bus cycle. This may         occur in the middle of an instruction that requires more than one external bus         cycle for execution.         To ensure proper operation, the user must set the asynchronous bus arbitration         enable (ABE) bit (Bit 13) in the Operating Mode Register. When this bit is set,         BG and BB are synchronized internally. This adds a required delay between the         deassertion of an initial BG input and the assertion of a subsequent BG input.                                                                                                                                            |

| BB          | Input/ Output | Ignored Input                                                                                                                                                                                                             | <ul> <li>Bus Busy—Indicates that the bus is active. Only after BB is deasserted can the pending bus master become the bus master (and then assert the signal again). The bus master may keep BB asserted after ceasing bus activity regardless of whether BR is asserted or deasserted. Called "bus parking," this allows the current bus master to reuse the bus without rearbitration until another device requires the bus. BB is deasserted by an "active pull-up" method (that is, BB is driven high and then released and held high by an external pull-up resistor).</li> <li>Notes: 1. See BG for additional information.</li> <li>2. BB requires an external pull-up resistor.</li> </ul>                                                                                                                                                                                                                                                                     |

als/Connections

|             |                 | Table 1-10.                          | Host Interface (Continued)                                                                                                                                                                                                                                                                                   |

|-------------|-----------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Name | Туре            | State During<br>Reset <sup>1,2</sup> | Signal Description                                                                                                                                                                                                                                                                                           |

| HA0         | Input           | Ignored Input                        | Host Address Input 0—When the HI08 is programmed to interface with a nonmultiplexed host bus and the HI function is selected, this signal is line 0 of the host address input bus.                                                                                                                           |

| HAS/HAS     | Input           |                                      | <b>Host Address Strobe</b> —When the HI08 is programmed to interface with a multiplexed host bus and the HI function is selected, this signal is the host address strobe (HAS) Schmitt-trigger input. The polarity of the address strobe is programmable but is configured active-low (HAS) following reset. |

| PB8         | Input or Output |                                      | <b>Port B 8</b> —When the HI08 is configured as GPIO through the HI08 Port Control Register, this signal is individually programmed as an input or output through the HI08 Data Direction Register.                                                                                                          |

| HA1         | Input           | Ignored Input                        | <b>Host Address Input 1</b> —When the HI08 is programmed to interface with a nonmultiplexed host bus and the HI function is selected, this signal is line 1 of the host address (HA1) input bus.                                                                                                             |

| HA8         | Input           |                                      | <b>Host Address 8</b> —When the HI08 is programmed to interface with a multiplexed host bus and the HI function is selected, this signal is line 8 of the host address (HA8) input bus.                                                                                                                      |

| PB9         | Input or Output |                                      | <b>Port B 9</b> —When the HI08 is configured as GPIO through the HI08 Port Control Register, this signal is individually programmed as an input or output through the HI08 Data Direction Register.                                                                                                          |

| HA2         | Input           | Ignored Input                        | <b>Host Address Input 2</b> —When the HI08 is programmed to interface with a nonmultiplexed host bus and the HI function is selected, this signal is line 2 of the host address (HA2) input bus.                                                                                                             |

| HA9         | Input           |                                      | <b>Host Address 9</b> —When the HI08 is programmed to interface with a multiplexed host bus and the HI function is selected, this signal is line 9 of the host address (HA9) input bus.                                                                                                                      |

| PB10        | Input or Output |                                      | <b>Port B 10</b> —When the HI08 is configured as GPIO through the HI08 Port Control Register, this signal is individually programmed as an input or output through the HI08 Data Direction Register.                                                                                                         |

| HCS/HCS     | Input           | Ignored Input                        | <b>Host Chip Select</b> —When the HI08 is programmed to interface with a nonmultiplexed host bus and the HI function is selected, this signal is the host chip select (HCS) input. The polarity of the chip select is programmable but is configured active-low (HCS) after reset.                           |

| HA10        | Input           |                                      | <b>Host Address 10</b> —When the HI08 is programmed to interface with a multiplexed host bus and the HI function is selected, this signal is line 10 of the host address (HA10) input bus.                                                                                                                   |

| PB13        | Input or Output |                                      | <b>Port B 13</b> —When the HI08 is configured as GPIO through the HI08 Port Control Register, this signal is individually programmed as an input or output through the HI08 Data Direction Register.                                                                                                         |

| HRW         | Input           | Ignored Input                        | Host Read/Write—When the HI08 is programmed to interface with a single-<br>data-strobe host bus and the HI function is selected, this signal is the Host<br>Read/Write (HRW) input.                                                                                                                          |

#### Table 1-10. Host Interface (Continued)

HI08 Data Direction Register.

is configured as active-low (HRD) after reset.

**Host Read Data**—When the HI08 is programmed to interface with a doubledata-strobe host bus and the HI function is selected, this signal is the HRD strobe Schmitt-trigger input. The polarity of the data strobe is programmable but

Port B 11—When the HI08 is configured as GPIO through the HI08 Port Control

Register, this signal is individually programmed as an input or output through the

HRD/HRD

PB11

Input

Input or Output

### 1.11 JTAG and OnCE Interface

The DSP56300 family and in particular the DSP56321 support circuit-board test strategies based on the IEEE® Std. 1149.1<sup>™</sup> test access port and boundary scan architecture, the industry standard developed under the sponsorship of the Test Technology Committee of IEEE and the JTAG. The OnCE module provides a means to interface nonintrusively with the DSP56300 core and its peripherals so that you can examine registers, memory, or on-chip peripherals. Functions of the OnCE module are provided through the JTAG TAP signals. For programming models, see the chapter on debugging support in the DSP56300 Family Manual.

| Signal<br>Name | Туре          | State During<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------|---------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| тск            | Input         | Input                 | Test Clock—A test clock input signal to synchronize the JTAG test logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TDI            | Input         | Input                 | <b>Test Data Input</b> —A test data serial input signal for test instructions and data. TDI is sampled on the rising edge of TCK and has an internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TDO            | Output        | Tri-stated            | <b>Test Data Output</b> —A test data serial output signal for test instructions and data. TDO is actively driven in the shift-IR and shift-DR controller states. TDO changes on the falling edge of TCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TMS            | Input         | Input                 | <b>Test Mode Select</b> —Sequences the test controller's state machine. TMS is sampled on the rising edge of TCK and has an internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TRST           | Input         | Input                 | <b>Test Reset</b> —Înitializes the test controller asynchronously. TRST has an internal pull-up resistor. TRST must be asserted during and after power-up (see EB610/D for details).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DE             | Input/ Output | Input                 | <b>Debug Event</b> —As an input, initiates Debug mode from an external command controller, and, as an open-drain output, acknowledges that the chip has entered Debug mode. As an input, DE causes the DSP56300 core to finish executing the current instruction, save the instruction pipeline information, enter Debug mode, and wait for commands to be entered from the debug serial input line. This signal is asserted as an output for three clock cycles when the chip enters Debug mode as a result of a debug request or as a result of meeting a breakpoint condition. The DE has an internal pull-up resistor. This signal is not a standard part of the JTAG TAP controller. The signal connects directly to the OnCE module to initiate debug mode directly or to provide a direct external indication that the chip has entered Debug mode. All other interface with the OnCE module must occur through the JTAG port. |

| Table 1-15. | JTAG/OnCE Interface |

|-------------|---------------------|

|             |                     |

# **Specifications**

The DSP56321 is fabricated in high-density CMOS with Transistor-Transistor Logic (TTL) compatible inputs and outputs.

## 2.1 Maximum Ratings

### CAUTION

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, normal precautions should be taken to avoid exceeding maximum voltage ratings. Reliability is enhanced if unused inputs are tied to an appropriate logic voltage level (for example, either GND or  $V_{CC}$ ).

In the calculation of timing requirements, adding a maximum value of one specification to a minimum value of another specification does not yield a reasonable sum. A maximum specification is calculated using a worst case variation of process parameter values in one direction. The minimum specification is calculated using the worst case for the same parameters in the opposite direction. Therefore, a "maximum" value for a specification never occurs in the same device that has a "minimum" value for another specification; adding a maximum to a minimum represents a condition that can never exist.

| Rating <sup>1</sup>                                     |                                               | Symbol                                       | Value <sup>1, 2</sup>                      | Unit                                        |    |  |

|---------------------------------------------------------|-----------------------------------------------|----------------------------------------------|--------------------------------------------|---------------------------------------------|----|--|

| Supply Voltage <sup>3</sup>                             |                                               |                                              | V <sub>CCQL</sub>                          | -0.1 to 2.25                                | V  |  |

| Input/Out                                               | put Supp                                      | ly Voltage <sup>3</sup>                      | V <sub>CCQH</sub>                          | -0.3 to 4.35                                | V  |  |

| All input v                                             | voltages                                      |                                              | V <sub>IN</sub>                            | GND – 0.3 to V <sub>CCQH</sub> + 0.3        | V  |  |

| Current drain per pin excluding V <sub>CC</sub> and GND |                                               |                                              | I                                          | 10                                          | mA |  |

| Operating temperature range                             |                                               |                                              | Т <sub>Ј</sub>                             | -40 to +100                                 | °C |  |

| Storage to                                              | emperatu                                      | ıre                                          | T <sub>STG</sub>                           | -55 to +150                                 | °C |  |

| Notes:                                                  | <ol> <li>Ab:<br/>the</li> <li>Port</li> </ol> | e maximum rating may affect device reliabili | only, and functional<br>ty or cause permar | operation at the maximum is not guaranteed. | -  |  |

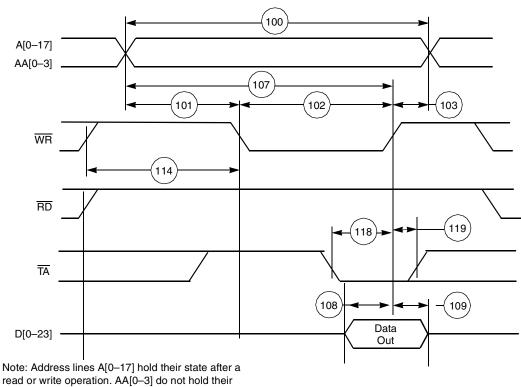

state after a read or write operation.

### 2.4.5.2 Asynchronous Bus Arbitration Timings

| No.   | Characteristics                                                                                      | Expression   | 200 MHz |      | 220 MHz |      | 240 MHz |      | 275 Mhz |      | Uni |

|-------|------------------------------------------------------------------------------------------------------|--------------|---------|------|---------|------|---------|------|---------|------|-----|

| NO.   | Unaracteristics                                                                                      |              | Min     | Max  | Min     | Max  | Min     | Max  | Min     | Max  | t   |

| 250   | $\overline{\text{BB}}$ assertion window from $\overline{\text{BG}}$ input deassertion.               | 2.5 × Tc + 5 |         | 17.5 |         | 16.4 |         | 15.4 | —       | 14.1 | ns  |

| 251   | Delay from $\overline{BB}$ assertion to $\overline{BG}$ assertion                                    | 2 × Tc + 5   | 15      | —    | 14.1    |      | 13.3    |      | 12.27   | —    | ns  |

| Notes | Notes: 1. Bit 13 in the Operating Mode Register must be set to enable Asynchronous Arbitration mode. |              |         |      |         |      |         |      |         |      |     |

| Table 2-9. | Asynchronous | <b>Bus Timings</b> |

|------------|--------------|--------------------|

|------------|--------------|--------------------|

2. To guarantee timings 250 and 251, it is recommended that you assert non-overlapping BG inputs to different DSP56300 devices (on the same bus), as shown in Figure 2-12, where BG1 is the BG signal for one DSP56300 device while BG2 is the BG signal for a second DSP56300 device.

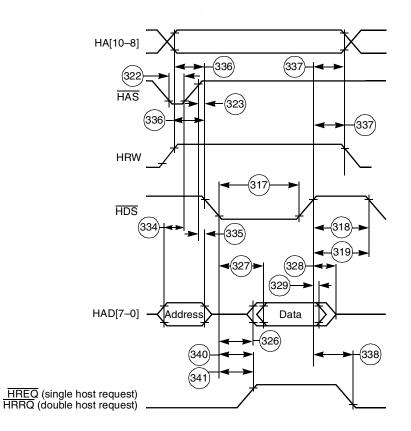

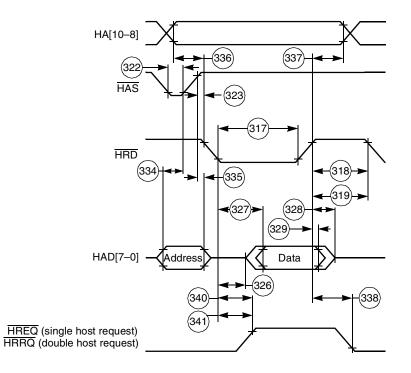

|     | Characteristic <sup>10</sup>                                                                                                                                         | Expression                     | 200 MHz   |       | 220      | MHz   | 240 MHz   |       | 275 MHz   |       | Uni      |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-----------|-------|----------|-------|-----------|-------|-----------|-------|----------|

| No. |                                                                                                                                                                      |                                | Min       | Мах   | Min      | Max   | Min       | Max   | Min       | Мах   | t        |

| 323 | HAS deassertion to data strobe assertion <sup>4</sup>                                                                                                                |                                | 0.0       | _     | 0.0      | _     | 0.0       | _     | 0.0       | _     | ns       |

| 324 | Host data input setup time before write data strobe deassertion <sup>6</sup>                                                                                         |                                | 4.95      | —     | 4.5      | —     | 4.13      | —     | 4.0       | —     | ns       |

| 325 | Host data input hold time after write data strobe deassertion <sup>6</sup>                                                                                           |                                | 1.65      | —     | 1.5      | _     | 1.38      | _     | 1.23      | —     | ns       |

| 326 | Read data strobe assertion to output data<br>active from high impedance <sup>5</sup><br>HACK assertion to output data active from high<br>impedance                  |                                | 1.65      | _     | 1.5      | _     | 1.38      | _     | 1.23      | _     | ns       |

| 327 | Read data strobe assertion to output data<br>valid <sup>5</sup><br>HACK assertion to output data valid                                                               |                                | —         | 14.78 | —        | 13.45 | _         | 12.32 |           | 10.2  | ns       |

| 328 | Read data strobe deassertion to output data<br>high impedance <sup>5</sup><br>HACK deassertion to output data high<br>impedance                                      |                                | _         | 4.95  | _        | 4.5   |           | 4.13  | 4.0       | _     | ns       |

| 329 | Output data hold time after read data strobe<br>deassertion <sup>5</sup><br>Output data hold time after HACK deassertion                                             |                                | 1.65      | —     | 1.5      | -     | 1.38      | -     | 1.23      | -     | ns       |

| 330 | HCS assertion to read data strobe deassertion <sup>5</sup>                                                                                                           | T <sub>C</sub> + 4.95          | 9.95      | _     | 9.05     | —     | 8.3       | —     | 7.77      | —     | ns       |

| 331 | HCS assertion to write data strobe deassertion <sup>6</sup>                                                                                                          |                                | 8         | —     | 8        | —     | 8         | —     | 8         | —     | ns       |

| 332 | HCS assertion to output data valid                                                                                                                                   |                                | —         | 17    | —        | 16    | _         | 15    |           | 14    | ns       |

| 333 | HCS hold time after data strobe deassertion <sup>4</sup>                                                                                                             |                                | 0.0       | —     | 0.0      | _     | 0.0       | _     | 0.0       | _     | ns       |

| 334 | Address (HAD[0-7]) setup time before HAS deassertion (HMUX=1)                                                                                                        |                                | 2.31      | —     | 2.1      | _     | 1.93      | _     | 1.76      | _     | ns       |

| 335 | Address (HAD[0–7]) hold time after HAS deassertion (HMUX=1)                                                                                                          |                                | 1.65      | —     | 1.5      | _     | 1.38      | _     | 1.23      | _     | ns       |

| 336 | HA[8–10] (HMUX=1), HA[0–2] (HMUX=0),<br>HR/W setup time before data strobe assertion <sup>4</sup><br>• Read<br>• Write                                               |                                | 0<br>2.31 | _     | 0<br>2.1 |       | 0<br>1.93 |       | 0<br>1.76 | _     | ns<br>ns |

| 337 | HA[8–10] (HMUX=1), HA[0–2] (HMUX=0), HR/ $\overline{W}$ hold time after data strobe deassertion <sup>4</sup>                                                         |                                | 1.65      | —     | 1.5      | —     | 1.38      | —     | 1.23      | —     | ns       |

| 338 | Delay from read data strobe deassertion to<br>host request assertion for "Last Data Register"<br>read <sup>5, 7, 8</sup>                                             | T <sub>C</sub> + 2.64          | 7.64      | _     | 7.19     | -     | 6.81      | -     | 6.28      | -     | ns       |

| 339 | Delay from write data strobe deassertion to<br>host request assertion for "Last Data Register"<br>write <sup>6, 7, 8</sup>                                           | 1.5 × T <sub>C</sub> +<br>2.64 | 10.14     | —     | 9.47     | —     | 8.9       | —     | 8.1       | —     | ns       |

| 340 | Delay from data strobe assertion to host<br>request deassertion for "Last Data Register"<br>read or write (HROD=0) <sup>4, 7, 8</sup>                                |                                | _         | 12.14 | _        | 11.04 |           | 10.12 |           | 9.0   | ns       |

| 341 | Delay from data strobe assertion to host<br>request deassertion for "Last Data Register"<br>read or write (HROD=1, open drain host<br>request) <sup>4, 7, 8, 9</sup> |                                | _         | 300.0 | _        | 300.0 | _         | 300.0 |           | 300.0 | ns       |

| -   | •                                                                                                                                                                    |                                | •         |       |          | •     |           | •     |           |       |          |

Table 2-10.

Host Interface Timings<sup>1,2,12</sup> (Continued)

Figure 2-18. Read Timing Diagram, Multiplexed Bus, Single Data Strobe

Figure 2-19. Read Timing Diagram, Multiplexed Bus, Double Data Strobe

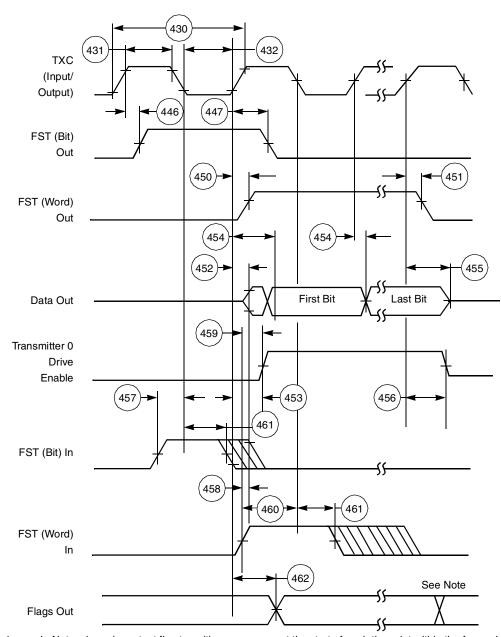

### 2.4.8 ESSI0/ESSI1 Timing

| No  | Characteristics <sup>4, 6</sup>                                         | Symbol                                 | Expression                                                | 200 MHz      |             | 220 MHz      |             | 240 MHz      |             | Hz 275 MHz   |                    | Cond-          | Unit     |

|-----|-------------------------------------------------------------------------|----------------------------------------|-----------------------------------------------------------|--------------|-------------|--------------|-------------|--------------|-------------|--------------|--------------------|----------------|----------|

| No. |                                                                         |                                        | Expression                                                | Min Max      | Min         | Max          | Min         | Max          | Min         | Max          | ition <sup>5</sup> | Unit           |          |

| 430 | Clock cycle <sup>1</sup>                                                | T <sub>ECCX</sub><br>T <sub>ECCI</sub> | $6 \times T_C \\ 8 \times T_C$                            | 30.0<br>40.0 | _           | 27.3<br>36.6 | _           | 25.0<br>33.3 | _           | 21.5<br>25.0 | _                  | x ck<br>i ck   | ns<br>ns |

| 431 | Clock high period<br>• For internal clock<br>• For external clock       |                                        | T <sub>ECCX</sub> /2 – 3.7<br>T <sub>ECCI</sub> /2 – 10.0 | 11.3<br>10.0 | _           | 9.9<br>8.2   | _           | 8.8<br>6.7   | _           | 7.21<br>2.5  | -                  |                | ns<br>ns |

| 432 | Clock low period<br>• For internal clock<br>• For external clock        |                                        | T <sub>ECCX</sub> /2 – 3.7<br>T <sub>ECCI</sub> /2 –10.0  | 11.3<br>10.0 |             | 9.9<br>8.2   |             | 8.8<br>6.7   |             | 7.21<br>2.5  |                    |                | ns<br>ns |

| 433 | RXC rising edge to FSR out (bit-length)<br>high                         |                                        |                                                           | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | _            | 12.5<br>8.3        | x ck<br>i ck a | ns       |

| 434 | RXC rising edge to FSR out (bit-length)<br>low                          |                                        |                                                           | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | _            | 12.5<br>8.3        | x ck<br>i ck a | ns       |

| 435 | RXC rising edge to FSR out (word-<br>length-relative) high <sup>2</sup> |                                        |                                                           | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | _            | 12.5<br>8.3        | x ck<br>i ck a | ns       |

| 436 | RXC rising edge to FSR out (word-<br>length-relative) low <sup>2</sup>  |                                        |                                                           | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | _            | 12.5<br>8.3        | x ck<br>i ck a | ns       |

| 437 | RXC rising edge to FSR out (word-<br>length) high                       |                                        |                                                           | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | _            | 12.5<br>8.3        | x ck<br>i ck a | ns       |

| 438 | RXC rising edge to FSR out (word-<br>length) low                        |                                        |                                                           | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | _            | 12.5<br>8.3        | x ck<br>i ck a | ns       |

| 439 | Data in setup time before RXC (SCK in Synchronous mode) falling edge    |                                        |                                                           | 5.0<br>10.0  | _<br>_      | 5.0<br>10.0  | _<br>_      | 5.0<br>10.0  | _           | 5.0<br>10.0  | _                  | x ck<br>i ck   | ns       |

| 440 | Data in hold time after RXC falling edge                                |                                        |                                                           | 3.8<br>5.0   | _           | 3.8<br>5.0   | _           | 3.8<br>5.0   | _           | 3.8<br>5.0   | _                  | x ck<br>i ck   | ns       |

| 441 | FSR input (bl, wr) high before RXC falling edge <sup>2</sup>            |                                        |                                                           | 5.0<br>10.0  | _           | 5.0<br>10.0  | _           | 5.0<br>10.0  | _           | 5.0<br>10.0  | _                  | x ck<br>i ck a | ns       |

| 442 | FSR input (wl) high before RXC falling edge                             |                                        |                                                           | 5.0<br>10.0  | _           | 5.0<br>10.0  | _           | 5.0<br>10.0  | _           | 5.0<br>10.0  | _                  | x ck<br>i ck a | ns       |

| 443 | FSR input hold time after RXC falling edge                              |                                        |                                                           | 3.8<br>5.0   | _           | 3.8<br>5.0   | _           | 3.8<br>5.0   | _           | 3.8<br>5.0   | _                  | x ck<br>i ck a | ns       |

| 444 | Flags input setup before RXC falling edge                               |                                        |                                                           | 5.0<br>10.0  | _<br>_      | 5.0<br>10.0  | _<br>_      | 5.0<br>10.0  | _           | 5.0<br>10.0  | _                  | x ck<br>i ck s | ns       |

| 445 | Flags input hold time after RXC falling edge                            |                                        |                                                           | 3.8<br>5.0   | _<br>_      | 3.8<br>5.0   | _<br>_      | 3.8<br>5.0   | _           | 3.8<br>5.0   | _                  | x ck<br>i ck s | ns       |

| 446 | TXC rising edge to FST out (bit-length) high                            |                                        |                                                           | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | _            | 12.5<br>8.3        | x ck<br>i ck   | ns       |

| 447 | TXC rising edge to FST out (bit-length) low                             |                                        |                                                           | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | _            | 12.5<br>8.3        | x ck<br>i ck   | ns       |

| 448 | TXC rising edge to FST out (word-<br>length-relative) high <sup>2</sup> |                                        |                                                           | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | _            | 12.5<br>8.3        | x ck<br>i ck   | ns       |

| 449 | TXC rising edge to FST out (word-<br>length-relative) low <sup>2</sup>  |                                        |                                                           | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | _            | 12.5<br>8.3        | x ck<br>i ck   | ns       |

| 450 | TXC rising edge to FST out (word-<br>length) high                       |                                        |                                                           | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | _            | 12.5<br>8.3        | x ck<br>i ck   | ns       |

Table 2-12. ESSI Timings

ifications

| No. | Characteristics <sup>4, 6</sup>                                        | Symbol | Everenciar | 200 MHz     |              | 200 MHz 220 MHz |              | 240 MHz     |                    | Hz 275 MHz  |              | Cond-        | Unit |

|-----|------------------------------------------------------------------------|--------|------------|-------------|--------------|-----------------|--------------|-------------|--------------------|-------------|--------------|--------------|------|

|     |                                                                        |        | Expression |             | Min          | Max             | Min          | Max         | ition <sup>5</sup> | Unit        |              |              |      |

| 451 | TXC rising edge to FST out (word-<br>length) low                       |        |            |             | 12.5<br>8.3  |                 | 12.5<br>8.3  |             | 12.5<br>8.3        | _           | 12.5<br>8.3  | x ck<br>i ck | ns   |

| 452 | TXC rising edge to data out enable from<br>high impedance              |        |            | _           | 12.5<br>8.3  |                 | 12.5<br>8.3  |             | 12.5<br>8.3        | _           | 12.5<br>8.3  | x ck<br>i ck | ns   |

| 453 | TXC rising edge to Transmitter 0 drive enable assertion                |        |            | _           | 12.5<br>13.5 |                 | 12.5<br>13.5 |             | 12.5<br>13.5       | _           | 12.5<br>13.5 | x ck<br>i ck | ns   |

| 454 | TXC rising edge to data out valid                                      |        |            | _           | 12.5<br>8.3  |                 | 12.5<br>8.3  |             | 12.5<br>8.3        | _           | 12.5<br>8.3  | x ck<br>i ck | ns   |

| 455 | TXC rising edge to data out high impedance <sup>3</sup>                |        |            | _           | 30.0<br>8.3  |                 | 30.0<br>8.3  |             | 30.0<br>8.3        | _           | 30.0<br>8.3  | x ck<br>i ck | ns   |

| 456 | TXC rising edge to Transmitter 0 drive enable deassertion <sup>3</sup> |        |            | _           | 12.5<br>8.3  |                 | 12.5<br>8.3  |             | 12.5<br>8.3        | _           | 12.5<br>8.3  | x ck<br>i ck | ns   |

| 457 | FST input (bl, wr) setup time before<br>TXC falling edge <sup>2</sup>  |        |            | 5.0<br>10.0 | _            | 5.0<br>10.0     | _            | 5.0<br>10.0 | _                  | 5.0<br>10.0 | _            | x ck<br>i ck | ns   |

| 458 | FST input (wI) to data out enable from<br>high impedance               |        |            | _           | 15.0<br>8.0  |                 | 15.0<br>8.0  |             | 15.0<br>8.0        | _           | 15.0<br>8.0  | x ck<br>i ck | ns   |

| 459 | FST input (wI) to Transmitter 0 drive enable assertion                 |        |            | _           | 15.0<br>18.0 |                 | 15.0<br>18.0 |             | 15.0<br>18.0       | _           | 15.0<br>18.0 | x ck<br>i ck | ns   |

| 460 | FST input (wl) setup time before TXC<br>falling edge                   |        |            | 5.0<br>10.0 | _<br>_       | 5.0<br>10.0     | _<br>_       | 5.0<br>10.0 | _                  | 5.0<br>10.0 | _            | x ck<br>i ck | ns   |

| 461 | FST input hold time after TXC falling edge                             |        |            | 3.8<br>5.0  | _<br>_       | 3.8<br>5.0      | _<br>_       | 3.8<br>5.0  | _                  | 3.8<br>5.0  | _            | x ck<br>i ck | ns   |

| 462 | Flag output valid after TXC rising edge                                |        |            | _           | 12.5<br>8.3  | _               | 12.5<br>8.3  | _           | 12.5<br>8.3        |             | 12.5<br>8.3  | x ck<br>i ck | ns   |

**Table 2-12.**ESSI Timings (Continued)

ESSI control register. T<sub>ECCX</sub> must be ≥ T<sub>C</sub> × 3, in accordance with the note below Table 7-1 in the DSP56321 Reference Manual. T<sub>ECCI</sub> must be ≥ T<sub>C</sub> × 4, in accordance with the explanation of CRA[PSR] and the ESSI Clock Generator Functional Block Diagram shown in Figure 7-3 of the DSP56321 Reference Manual.

The word length relative frame sume signal waveform expresses the same wave as the bit length frame sume signal waveform but

2. The word-length-relative frame sync signal waveform operates the same way as the bit-length frame sync signal waveform, but spreads from one serial clock before the first bit clock (same as the Bit Length Frame Sync signal) until the one before last bit clock of the first word in the frame.

- 3. Periodically sampled and not 100 percent tested

- 4.  $V_{CCQH} = 3.3 \text{ V} \pm 0.3 \text{ V}$ ,  $V_{CCQL} = 1.6 \text{ V} \pm 0.1 \text{ V}$ ;  $T_J = 0^{\circ}\text{C}$  to +85°C,  $C_L = 50 \text{ pF}$

TXC (SCK Pin) = Transmit Clock RXC (SC0 or SCK Pin) = Receive Clock FST (SC2 Pin) = Transmit Frame Sync FSR (SC1 or SC2 Pin) Receive Frame Sync

i ck = Internal Clock; x ck = External Clock

i ck a = Internal Clock, Asynchronous Mode (asynchronous implies that TXC and RXC are two different clocks)

i ck s = Internal Clock, Synchronous Mode (synchronous implies that TXC and RXC are the same clock)

7. In the timing diagrams below, the clocks and frame sync signals are drawn using the clock falling edge as a the first reference. Clock and frame sync polarities are programmable in Control Register B (CRB). Refer to the *DSP56321 Reference Manual* for details.

| Figure 2-24. | ESSI | Transmitter | Timing |

|--------------|------|-------------|--------|

|--------------|------|-------------|--------|

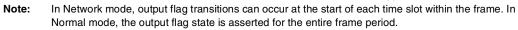

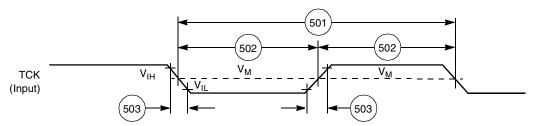

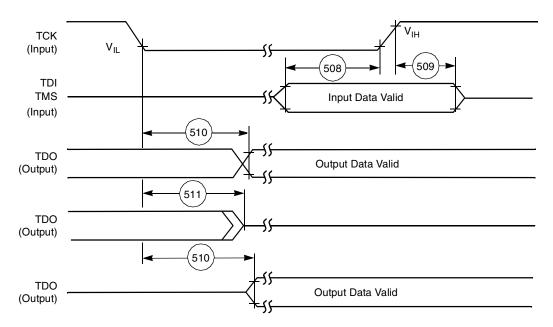

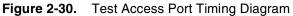

## 2.4.11 JTAG Timing

| NI - | Ob any standarding                                                         | All freq | All frequencies |        |  |  |  |

|------|----------------------------------------------------------------------------|----------|-----------------|--------|--|--|--|

| No.  | Characteristics                                                            | Min      | Max             | – Unit |  |  |  |

| 500  | TCK frequency of operation (1/( $T_C \times 3$ ); absolute maximum 22 MHz) | 0.0      | 22.0            | MHz    |  |  |  |

| 501  | TCK cycle time in Crystal mode                                             | 45.0     | _               | ns     |  |  |  |

| 502  | TCK clock pulse width measured at 1.6 V                                    | 20.0     | _               | ns     |  |  |  |

| 503  | TCK rise and fall times                                                    | 0.0      | 3.0             | ns     |  |  |  |

| 504  | Boundary scan input data setup time                                        | 5.0      | _               | ns     |  |  |  |

| 505  | Boundary scan input data hold time                                         | 24.0     | _               | ns     |  |  |  |

| 506  | TCK low to output data valid                                               | 0.0      | 40.0            | ns     |  |  |  |

| 507  | TCK low to output high impedance                                           | 0.0      | 40.0            | ns     |  |  |  |

| 508  | TMS, TDI data setup time                                                   | 5.0      | _               | ns     |  |  |  |

| 509  | TMS, TDI data hold time                                                    | 25.0     | _               | ns     |  |  |  |

| 510  | TCK low to TDO data valid                                                  | 0.0      | 44.0            | ns     |  |  |  |

| 511  | TCK low to TDO high impedance                                              | 0.0      | 44.0            | ns     |  |  |  |

| 512  | TRST assert time                                                           | 100.0    | —               | ns     |  |  |  |

| 513  | TRST setup time to TCK low                                                 | 40.0     | —               | ns     |  |  |  |

Table 2-14. JTAG Timing

Figure 2-28. Test Clock Input Timing Diagram

Figure 2-29. Boundary Scan (JTAG) Timing Diagram

Figure 2-31. TRST Timing Diagram

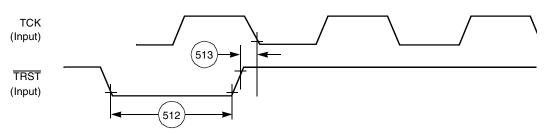

### 2.4.12 OnCE Module TimIng

DE

| No.   | Characteristics                                                                                                                                                                                       | Expression               | All Freq | Unit |      |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------|------|------|--|--|

| NO.   | Characteristics                                                                                                                                                                                       | Expression               | Min      | Max  | Unit |  |  |

| 500   | TCK frequency of operation (1/(T <sub>C</sub> $\times$ 3); maximum 22 MHz)                                                                                                                            | Max 22.0 MHz             | 0.0      | 22.0 | MHz  |  |  |

| 514   | DE assertion time in order to enter Debug mode                                                                                                                                                        | $1.5 	imes T_{C} + 10.0$ | 20.0     | —    | ns   |  |  |

| 515   | $\frac{5}{1000} \frac{1}{1000} \frac{1}{1000} \frac{1}{1000} \frac{1}{1000} \frac{1}{1000} \frac{1}{1000} \frac{1}{1000} \frac{1}{1000} \frac{1}{10000} \frac{1}{10000000000000000000000000000000000$ |                          |          |      |      |  |  |

| 516   | Debug acknowledge assertion time                                                                                                                                                                      | $3 \times T_{C} + 5.0$   | 25.0     | —    | ns   |  |  |

| Note: | : $V_{CCQH} = 3.3 \text{ V} \pm 0.3 \text{ V}, V_{CCQL} = 1.6 \text{ V} \pm 0.1 \text{ V}; T_J = -40^{\circ}\text{C} \text{ to } +100^{\circ}\text{C}, C_L = 50 \text{ pF}$                           |                          |          |      |      |  |  |

Table 2-15.

OnCE Module Timing

Figure 2-32. OnCE—Debug Request

## 3.1 Package Description

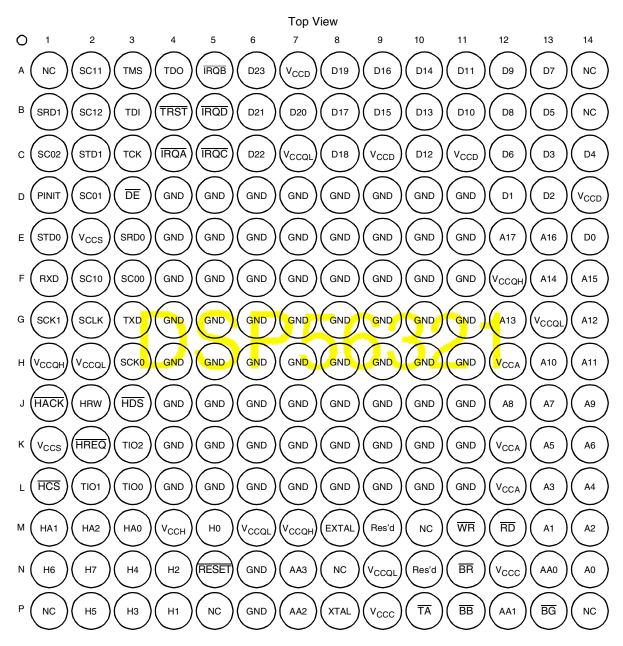

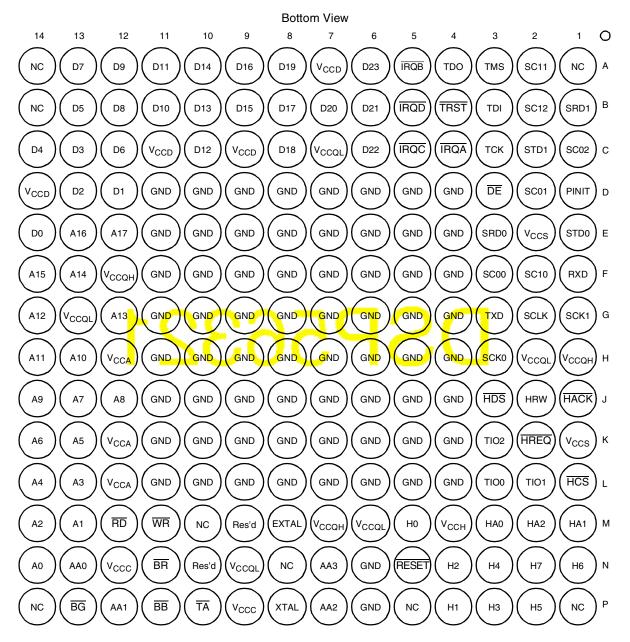

Top and bottom views of the MAP-BGA packages are shown in Figure 3-1 and Figure 3-2 with their pin-outs.

Figure 3-1. DSP56321 MAP-BGA Package, Top View

Figure 3-2. DSP56321 MAP-BGA Package, Bottom View

| Table 3-1. | Signal List by Ball Number |

|------------|----------------------------|

|------------|----------------------------|

| Ball<br>No. | Signal Name        | Ball<br>No. | Signal Name       | Ball<br>No. | Signal Name      |

|-------------|--------------------|-------------|-------------------|-------------|------------------|

| A1          | Not Connected (NC) | B12         | D8                | D9          | GND              |

| A2          | SC11 or PD1        | B13         | D5                | D10         | GND              |

| A3          | TMS                | B14         | NC                | D11         | GND              |

| A4          | TDO                | C1          | SC02 or PC2       | D12         | D1               |

| A5          | MODB/IRQB          | C2          | STD1 or PD5       | D13         | D2               |

| A6          | D23                | C3          | тск               | D14         | V <sub>CCD</sub> |

| A7          | V <sub>CCD</sub>   | C4          | MODA/IRQA         | E1          | STD0 or PC5      |

| A8          | D19                | C5          | MODC/IRQC         | E2          | V <sub>CCS</sub> |

| A9          | D16                | C6          | D22               | E3          | SRD0 or PC4      |

| A10         | D14                | C7          | V <sub>CCQL</sub> | E4          | GND              |

| A11         | D11                | C8          | D18               | E5          | GND              |

| A12         | D9                 | C9          | V <sub>CCD</sub>  | E6          | GND              |

| A13         | D7                 | C10         | D12               | E7          | GND              |

| A14         | NC                 | C11         | V <sub>CCD</sub>  | E8          | GND              |

| B1          | SRD1 or PD4        | C12         | D6                | E9          | GND              |

| B2          | SC12 or PD2        | C13         | D3                | E10         | GND              |

| B3          | TDI                | C14         | D4                | E11         | GND              |

| B4          | TRST               | D1          | PINIT/NMI         | E12         | A17              |

| B5          | MODD/IRQD          | D2          | SC01 or PC1       | E13         | A16              |

| B6          | D21                | D3          | DE                | E14         | D0               |

| B7          | D20                | D4          | GND               | F1          | RXD or PE0       |

| B8          | D17                | D5          | GND               | F2          | SC10 or PD0      |

| B9          | D15                | D6          | GND               | F3          | SC00 or PC0      |

| B10         | D13                | D7          | GND               | F4          | GND              |

| B11         | D10                | D8          | GND               | F5          | GND              |

| Signal Name | Ball<br>No. | Signal Name | Ball<br>No. | Signal Name | Ball<br>No. |

|-------------|-------------|-------------|-------------|-------------|-------------|

| MODA        | C4          | PB4         | N3          | Reserved    | M9          |

| MODB        | A5          | PB5         | P2          | Reserved    | N10         |

| MODC        | C5          | PB6         | N1          | RESET       | N5          |

| MODD        | B5          | PB7         | N2          | RXD         | F1          |

| NC          | A1          | PB8         | М3          | SC00        | F3          |

| NC          | A14         | PB9         | M1          | SC01        | D2          |

| NC          | B14         | PC0         | F3          | SC02        | C1          |

| NC          | M10         | PC1         | D2          | SC10        | F2          |

| NC          | N8          | PC2         | C1          | SC11        | A2          |

| NC          | P1          | PC3         | H3          | SC12        | B2          |

| NC          | P5          | PC4         | E3          | SCK0        | H3          |

| NC          | P14         | PC5         | E1          | SCK1        | G1          |

| NMI         | D1          | PD0         | F2          | SCLK        | G2          |

| PB0         | M5          | PD1         | A2          | SRD0        | E3          |

| PB1         | P4          | PD2         | B2          | SRD1        | B1          |

| PB10        | M2          | PD3         | G1          | STD0        | E1          |

| PB11        | J2          | PD4         | B1          | STD1        | C2          |

| PB12        | J3          | PD5         | C2          | TA          | P10         |

| PB13        | L1          | PE0         | F1          | ТСК         | C3          |

| PB14        | K2          | PE1         | G3          | TDI         | B3          |

| PB15        | J1          | PE2         | G2          | TDO         | A4          |

| PB2         | N4          | PINIT       | D1          | TIO0        | L3          |

| PB3         | P3          | RD          | M12         | TIO1        | L2          |

Table 3-2.

Signal List by Signal Name (Continued)

#### Pr Consumption Benchmark

M Z EOU 2 ; Zero M\_N EQU 3 ; Negative M\_U EQU 4 ; Unnormalized M\_E EQU 5 ; Extension M\_L EQU 6 ; Limit M\_S EQU 7 ; Scaling Bit M IO EOU 8 ; Interupt Mask Bit 0 M I1 EOU 9 ; Interupt Mask Bit 1 M\_S0 EQU 10 ; Scaling Mode Bit 0 ; Scaling Mode Bit 1 M\_S1 EQU 11 M SC EOU 13 ; Sixteen\_Bit Compatibility M DM EOU 14 ; Double Precision Multiply M LF EOU 15 ; DO-Loop Flag M FV EOU 16 ; DO-Forever Flag M\_SA EQU 17 ; Sixteen-Bit Arithmetic M\_CE EQU 19 ; Instruction Cache Enable M\_SM EQU 20 ; Arithmetic Saturation M\_RM EQU 21 ; Rounding Mode M\_CP0 EQU 22 ; bit 0 of priority bits in SR M\_CP1 EQU 23 ; bit 1 of priority bits in SR control and status bits in OMR M\_CDP EQU \$300; mask for CORE-DMA priority bits in OMR M\_MA equ0 ; Operating Mode A M\_MB equ1 ; Operating Mode B M\_MC equ2 ; Operating Mode C M\_MD equ3 ; Operating Mode D M\_EBD EQU 4 ; External Bus Disable bit in OMR M\_SD EQU 6 ; Stop Delay M\_MS EQU 7 ; Memory Switch bit in OMR M\_CDP0 EQU 8 ; bit 0 of priority bits in OMR M\_CDP1 EQU 9 ; bit 1 of priority bits in OMR M\_BEN EQU 10 ; Burst Enable M\_TAS EQU 11 ; TA Synchronize Select M\_BRT EQU 12 ; Bus Release Timing M\_ATE EQU 15 ; Address Tracing Enable bit in OMR. M\_XYS EQU 16 ; Stack Extension space select bit in OMR. ; Extensed stack UNderflow flag in OMR. M\_EUN EQU 17 M\_EOV EQU 18 ; Extended stack OVerflow flag in OMR. M\_WRP EQU 19 ; Extended WRaP flag in OMR. M\_SEN EQU 20 ; Stack Extension Enable bit in OMR.

| ;; HOST Interrupts                                                    |                                                                                  |

|-----------------------------------------------------------------------|----------------------------------------------------------------------------------|

| I_HRDF EQU I_VEC+\$60<br>I_HTDE EQU I_VEC+\$62<br>I_HC EQU I_VEC+\$64 | ; Host Receive Data Full<br>; Host Transmit Data Empty<br>; Default Host Command |

| ; EFCOP Filter Interrupts                                             |                                                                                  |

| I_FDIIE EQU I_VEC+\$68<br>I_FDOIE EQU I_VEC+\$6A                      | ; EFilter input buffer empty<br>; EFilter output buffer full                     |

| ; INTERRUPT ENDING ADDRESS                                            |                                                                                  |

| ,<br>I_INTEND EQU I_VEC+\$FF                                          | ; last address of interrupt vector space                                         |