### NXP USA Inc. - SPAKDSP321VL240 Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

| Details                 |                                                                         |

|-------------------------|-------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                |

| Туре                    | Fixed Point                                                             |

| Interface               | Host Interface, SSI, SCI                                                |

| Clock Rate              | 240MHz                                                                  |

| Non-Volatile Memory     | ROM (576B)                                                              |

| On-Chip RAM             | 576kB                                                                   |

| Voltage - I/O           | 3.30V                                                                   |

| Voltage - Core          | 1.60V                                                                   |

| Operating Temperature   | -40°C ~ 105°C (TJ)                                                      |

| Mounting Type           | Surface Mount                                                           |

| Package / Case          | 196-BGA                                                                 |

| Supplier Device Package | 196-MAPBGA (15x15)                                                      |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/spakdsp321vl240 |

|                         |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Features

Table 1 lists the features of the DSP56321 device.

| Feature                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High-Performance<br>DSP56300 Core      | <ul> <li>275 million multiply-accumulates per second (MMACS) (550 MMACS using the EFCOP in filtering applications) with a 275 MHz clock at 1.6 V core and 3.3 V I/O</li> <li>Object code compatible with the DSP56000 core with highly parallel instruction set</li> <li>Data arithmetic logic unit (Data ALU) with fully pipelined 24 × 24-bit parallel Multiplier-Accumulator (MAC), 56-bit parallel barrel shifter (fast shift and normalization; bit stream generation and parsing), conditional ALU instructions, and 24-bit or 16-bit arithmetic support under software control</li> <li>Program control unit (PCU) with position independent code (PIC) support, addressing modes optimized for DSP applications (including immediate offsets), internal instruction cache controller, internal memory-expandable hardware stack, nested hardware DO loops, and fast auto-return interrupts</li> <li>Direct memory access (DMA) with six DMA channels supporting internal and external accesses; one-, two-, and three-dimensional transfers (including circular buffering); end-of-block-transfer interrupts; and triggering from interrupt lines and all peripherals</li> <li>Phase-lock loop (PLL) allows change of low-power divide factor (DF) without loss of lock and output clock with skew elimination</li> <li>Hardware debugging support including on-chip emulation (OnCE) module, Joint Test Action Group (JTAG) test access port (TAP)</li> </ul> |

| Enhanced Filter<br>Coprocessor (EFCOP) | <ul> <li>Internal 24 × 24-bit filtering and echo-cancellation coprocessor that runs in parallel to the DSP core</li> <li>Operation at the same frequency as the core (up to 275 MHz)</li> <li>Support for a variety of filter modes, some of which are optimized for cellular base station applications: <ul> <li>Real finite impulse response (FIR) with real taps</li> <li>Complex FIR with complex taps</li> <li>Complex FIR generating pure real or pure imaginary outputs alternately</li> <li>A 4-bit decimation factor in FIR filters, thus providing a decimation ratio up to 16</li> <li>Direct form 1 (DFI) Infinite Impulse Response (IIR) filter</li> <li>Four scaling factors (1, 4, 8, 16) for IIR output</li> <li>Adaptive FIR filter with true least mean square (LMS) coefficient updates</li> <li>Adaptive FIR filter with delayed LMS coefficient updates</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Internal Peripherals                   | <ul> <li>Enhanced 8-bit parallel host interface (HI08) supports a variety of buses (for example, ISA) and provides glueless connection to a number of industry-standard microcomputers, microprocessors, and DSPs</li> <li>Two enhanced synchronous serial interfaces (ESSI), each with one receiver and three transmitters (allows six-channel home theater)</li> <li>Serial communications interface (SCI) with baud rate generator</li> <li>Triple timer module</li> <li>Up to 34 programmable general-purpose input/output (GPIO) pins, depending on which peripherals are enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

### Table 1. DSP56321 Features

# **Product Documentation**

The documents listed in **Table 2** are required for a complete description of the DSP56321 device and are necessary to design properly with the part. Documentation is available from a local Freescale distributor, a Freescale semiconductor sales office, or a Freescale Semiconductor Literature Distribution Center. For documentation updates, visit the Freescale DSP website. See the contact information on the back cover of this document.

| Name                         | Description                                                                                               | Order Number                     |

|------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------|

| DSP56321<br>Reference Manual | Detailed functional description of the DSP56321 memory configuration, operation, and register programming | DSP56321RM                       |

| DSP56300 Family<br>Manual    | Detailed description of the DSP56300 family processor core and instruction set                            | DSP56300FM                       |

| Application Notes            | Documents describing specific applications or optimized device operation including code examples          | See the DSP56321 product website |

| Table 2.         DSP56321 Documentation |

|-----------------------------------------|

|-----------------------------------------|

DSP56321 Technical Data, Rev. 11

### External Memory Expansion Port (Port A)

| Signal Name | Туре          | State During<br>Reset, Stop, or<br>Wait                                                                                                                                                                                   | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TA          | Input         | Ignored Input                                                                                                                                                                                                             | Transfer Acknowledge—If the DSP56321 is the bus master and there is no<br>external bus activity, or the DSP56321 is not the bus master, the TA input is<br>ignored. The TA input is a data transfer acknowledge (DTACK) function that can<br>extend an external bus cycle indefinitely. Any number of wait states (1,<br>2infinity) can be added to the wait states inserted by the bus control register<br>(BCR) by keeping TA deasserted. In typical operation, TA is deasserted at the<br>start of a bus cycle, is asserted to enable completion of the bus cycle, and is<br>                                                                                                                                                                                                                                                                                                                                                                                       |

| BR          | Output        | Reset: Output<br>(deasserted)<br>State during<br>Stop/Wait<br>depends on BRH<br>bit setting:<br>• BRH = 0: Output<br>(deasserted)<br>• BRH = 1:<br>Maintains last<br>state (that is, if<br>asserted, remains<br>asserted) | <b>Bus Request</b> —Asserted when the DSP requests bus mastership. $\overline{BR}$ is deasserted when the DSP no longer needs the bus. $\overline{BR}$ may be asserted or deasserted independently of whether the DSP56321 is a bus master or a bus slave. Bus "parking" allows $\overline{BR}$ to be deasserted even though the DSP56321 is the bus master. (See the description of bus "parking" in the $\overline{BB}$ signal description.) The bus request hold (BRH) bit in the BCR allows $\overline{BR}$ to be asserted under software control even though the DSP does not need the bus. $\overline{BR}$ is typically sent to an external bus arbitrator that controls the priority, parking, and tenure of each master on the same external bus. $\overline{BR}$ is affected only by DSP requests for the external bus, never for the internal bus. During hardware reset, $\overline{BR}$ is deasserted and the arbitration is reset to the bus slave state. |

| BG          | Input         | Ignored Input                                                                                                                                                                                                             | Bus Grant—Asserted by an external bus arbitration circuit when the DSP56321         becomes the next bus master. When BG is asserted, the DSP56321 must wait         until BB is deasserted before taking bus mastership. When BG is deasserted,         bus mastership is typically given up at the end of the current bus cycle. This may         occur in the middle of an instruction that requires more than one external bus         cycle for execution.         To ensure proper operation, the user must set the asynchronous bus arbitration         enable (ABE) bit (Bit 13) in the Operating Mode Register. When this bit is set,         BG and BB are synchronized internally. This adds a required delay between the         deassertion of an initial BG input and the assertion of a subsequent BG input.                                                                                                                                            |

| BB          | Input/ Output | Ignored Input                                                                                                                                                                                                             | <ul> <li>Bus Busy—Indicates that the bus is active. Only after BB is deasserted can the pending bus master become the bus master (and then assert the signal again). The bus master may keep BB asserted after ceasing bus activity regardless of whether BR is asserted or deasserted. Called "bus parking," this allows the current bus master to reuse the bus without rearbitration until another device requires the bus. BB is deasserted by an "active pull-up" method (that is, BB is driven high and then released and held high by an external pull-up resistor).</li> <li>Notes: 1. See BG for additional information.</li> <li>2. BB requires an external pull-up resistor.</li> </ul>                                                                                                                                                                                                                                                                     |

als/Connections

| Signal Name      | Туре                                                                                                | State During<br>Reset <sup>1,2</sup>           | Signal Description                                                                                                                                                                                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCK1             | Input/Output                                                                                        | Ignored Input                                  | Serial Clock—Provides the serial bit rate clock for the ESSI. The SCK1 is a clock input or output used by both the transmitter and receiver in synchronous modes or by the transmitter in asynchronous modes.                                                                                                                            |

|                  |                                                                                                     |                                                | Although an external serial clock can be independent of and asynchronous to the DSP system clock, it must exceed the minimum clock cycle time of 6T (that is, the system clock frequency must be at least three times the external ESSI clock frequency). The ESSI needs at least three DSP phases inside each half of the serial clock. |

| PD3              | Input or Output                                                                                     |                                                | <b>Port D 3</b> —The default configuration following reset is GPIO input PD3. When configured as PD3, signal direction is controlled through the Port D Direction Register. The signal can be configured as an ESSI signal SCK1 through the Port D Control Register.                                                                     |

| SRD1             | Input                                                                                               | Ignored Input                                  | Serial Receive Data—Receives serial data and transfers the data to the ESSI Receive Shift Register. SRD1 is an input when data is being received.                                                                                                                                                                                        |

| PD4              | Input or Output                                                                                     |                                                | <b>Port D 4</b> —The default configuration following reset is GPIO input PD4. When configured as PD4, signal direction is controlled through the Port D Direction Register. The signal can be configured as an ESSI signal SRD1 through the Port D Control Register.                                                                     |

| STD1             | Output                                                                                              | Ignored Input                                  | Serial Transmit Data—Transmits data from the Serial Transmit Shift Register.<br>STD1 is an output when data is being transmitted.                                                                                                                                                                                                        |

| PD5              | Input or Output                                                                                     |                                                | <b>Port D 5</b> —The default configuration following reset is GPIO input PD5. When configured as PD5, signal direction is controlled through the Port D Direction Register. The signal can be configured as an ESSI signal STD1 through the Port D Control Register.                                                                     |

| • If t<br>• If t | he Stop state, the sig<br>he last state is input,<br>he last state is outpu<br>Wait processing stat | the signal is an igno<br>t, these lines have v | ored input.<br>veak keepers that maintain the last output state even if the drivers are tri-stated.                                                                                                                                                                                                                                      |

Table 1-12.

Enhanced Serial Synchronous Interface 1 (Continued)

# 1.9 Serial Communication Interface (SCI)

The SCI provides a full duplex port for serial communication with other DSPs, microprocessors, or peripherals such as modems.

| Signal Name | Туре            | State During<br>Reset <sup>1,2</sup> | Signal Description                                                                                                                                                                                                                                                 |

|-------------|-----------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXD         | Input           | Ignored Input                        | Serial Receive Data—Receives byte-oriented serial data and transfers it to the SCI Receive Shift Register.                                                                                                                                                         |

| PE0         | Input or Output |                                      | <b>Port E 0</b> —The default configuration following reset is GPIO input PE0. When configured as PE0, signal direction is controlled through the Port E Direction Register. The signal can be configured as an SCI signal RXD through the Port E Control Register. |

| TXD         | Output          | Ignored Input                        | Serial Transmit Data—Transmits data from the SCI Transmit Data Register.                                                                                                                                                                                           |

| PE1         | Input or Output |                                      | <b>Port E 1</b> —The default configuration following reset is GPIO input PE1. When configured as PE1, signal direction is controlled through the Port E Direction Register. The signal can be configured as an SCI signal TXD through the Port E Control Register. |

Table 1-13.

Serial Communication Interface

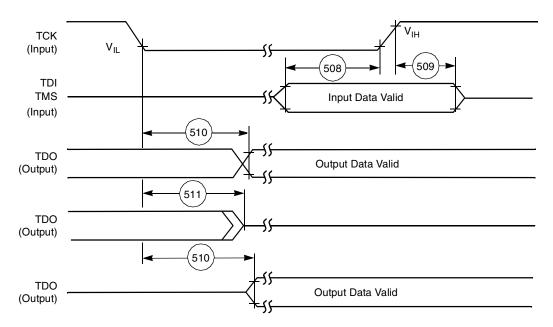

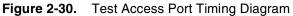

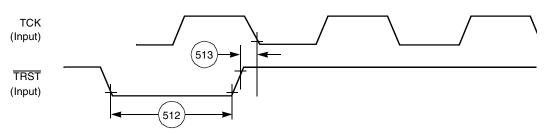

# 1.11 JTAG and OnCE Interface

The DSP56300 family and in particular the DSP56321 support circuit-board test strategies based on the IEEE® Std. 1149.1<sup>™</sup> test access port and boundary scan architecture, the industry standard developed under the sponsorship of the Test Technology Committee of IEEE and the JTAG. The OnCE module provides a means to interface nonintrusively with the DSP56300 core and its peripherals so that you can examine registers, memory, or on-chip peripherals. Functions of the OnCE module are provided through the JTAG TAP signals. For programming models, see the chapter on debugging support in the DSP56300 Family Manual.

| Signal<br>Name | Туре          | State During<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------|---------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| тск            | Input         | Input                 | Test Clock—A test clock input signal to synchronize the JTAG test logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TDI            | Input         | Input                 | <b>Test Data Input</b> —A test data serial input signal for test instructions and data. TDI is sampled on the rising edge of TCK and has an internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TDO            | Output        | Tri-stated            | <b>Test Data Output</b> —A test data serial output signal for test instructions and data. TDO is actively driven in the shift-IR and shift-DR controller states. TDO changes on the falling edge of TCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TMS            | Input         | Input                 | <b>Test Mode Select</b> —Sequences the test controller's state machine. TMS is sampled on the rising edge of TCK and has an internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TRST           | Input         | Input                 | <b>Test Reset</b> —Înitializes the test controller asynchronously. TRST has an internal pull-up resistor. TRST must be asserted during and after power-up (see EB610/D for details).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DE             | Input/ Output | Input                 | <b>Debug Event</b> —As an input, initiates Debug mode from an external command controller, and, as an open-drain output, acknowledges that the chip has entered Debug mode. As an input, DE causes the DSP56300 core to finish executing the current instruction, save the instruction pipeline information, enter Debug mode, and wait for commands to be entered from the debug serial input line. This signal is asserted as an output for three clock cycles when the chip enters Debug mode as a result of a debug request or as a result of meeting a breakpoint condition. The DE has an internal pull-up resistor. This signal is not a standard part of the JTAG TAP controller. The signal connects directly to the OnCE module to initiate debug mode directly or to provide a direct external indication that the chip has entered Debug mode. All other interface with the OnCE module must occur through the JTAG port. |

| Table 1-15. | JTAG/OnCE Interface |

|-------------|---------------------|

|             |                     |

| 190 | _                           | mA                                |

|-----|-----------------------------|-----------------------------------|

| 200 | _                           | mA                                |

| 210 | _                           | mA                                |

| 235 | _                           | mA                                |

| 25  | _                           | mA                                |

| 15  | —                           | mA                                |

| —   | 10                          | pF                                |

| v   | U <sub>CCQH</sub> voltage m | UCCQH voltage must always be high |

- 2. Refers to MODA/IRQA, MODB/IRQB, MODC/IRQC, and MODD/IRQD pins.

- 3. Section 4.3 provides a formula to compute the estimated current requirements in Normal mode. To obtain these results, all inputs must be terminated (that is, not allowed to float). Measurements are based on synthetic intensive DSP benchmarks (see **Appendix A**). The power consumption numbers in this specification are 90 percent of the measured results of this benchmark. This reflects typical DSP applications.

- 4. To obtain these results, all inputs must be terminated (that is, not allowed to float).

- 5. To obtain these results, all inputs not disconnected at Stop mode must be terminated (that is, not allowed to float), and the DPLL and on-chip crystal oscillator must be disabled.

- 6. Periodically sampled and not 100 percent tested.

- 7.  $V_{CCQH} = 3.3 \text{ V} \pm 0.3 \text{ V}$ ,  $V_{CQLC} = 1.6 \text{ V} \pm 0.1 \text{ V}$ ;  $T_J = -40^{\circ}\text{C}$  to  $+100 \text{ }^{\circ}\text{C}$ ,  $C_L = 50 \text{ pF}$

- 8. This characteristic does not apply to XTAL.

- 9. Driving EXTAL to the low  $V_{IHX}$  or the high  $V_{ILX}$  value may cause additional power consumption (DC current). To minimize power consumption, the minimum  $V_{IHX}$  should be no lower than

- $0.9 \times$   $V_{CCQH}$  and the maximum  $V_{ILX}$  should be no higher than 0.1  $\times$   $V_{CCQH}$

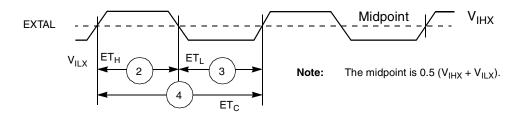

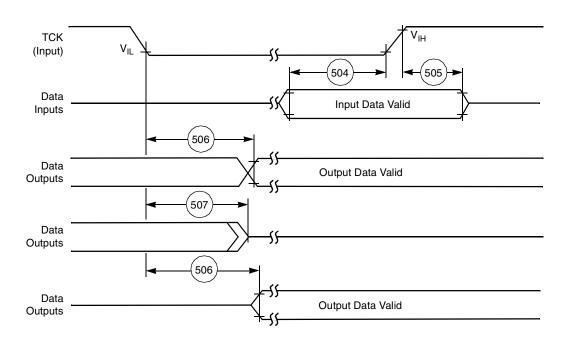

### 2.4 AC Electrical Characteristics

The timing waveforms shown in the AC electrical characteristics section are tested with a  $V_{IL}$  maximum of 0.3 V and a  $V_{IH}$  minimum of 2.4 V for all pins except EXTAL, which is tested using the input levels shown in Notes 7 and 9 of the previous table. AC timing specifications, which are referenced to a device input signal, are measured in production with respect to the 50 percent point of the respective input signal's transition. DSP56321 output levels are measured with the production test machine  $V_{OL}$  and  $V_{OH}$  reference levels set at 0.4 V and 2.4 V, respectively.

**Note:** Although the minimum value for the frequency of EXTAL is 0 MHz, the device AC test conditions are 16 MHz and rated speed with the DPLL enabled.

### 2.4.1 Internal Clocks

| Characteristics                                                                                | Symbol         | Expression          |                                                                  |                           |  |  |  |  |  |

|------------------------------------------------------------------------------------------------|----------------|---------------------|------------------------------------------------------------------|---------------------------|--|--|--|--|--|

| Cildiacteristics                                                                               | Symbol         | Min                 | Тур                                                              | Мах                       |  |  |  |  |  |

| Internal operating frequency <ul> <li>With DPLL disabled</li> <li>With DPLL enabled</li> </ul> | f              |                     | Ef/2<br>(Ef × MF)/(PDF × DF)                                     |                           |  |  |  |  |  |

| Internal clock cycle time <ul> <li>With DPLL disabled</li> <li>With DPLL enabled</li> </ul>    | т <sub>с</sub> |                     | $2 \times \text{ET}_{\text{C}}$<br>ET <sub>C</sub> × PDF × DF/MF |                           |  |  |  |  |  |

| Internal clock high period <ul> <li>With DPLL disabled</li> <li>With DPLL enabled</li> </ul>   | Т <sub>Н</sub> | $0.49 \times T_{C}$ | et <sub>c</sub><br>—                                             | <br>0.51 × T <sub>C</sub> |  |  |  |  |  |

Table 2-4. Internal Clocks

| No. | Characteristics                                                                                               | <b>•</b> • • •   | 200              | ) MHz        | 220                | MHz          | 240                | ) MHz        | 275 MHz            |              |

|-----|---------------------------------------------------------------------------------------------------------------|------------------|------------------|--------------|--------------------|--------------|--------------------|--------------|--------------------|--------------|

|     |                                                                                                               | Symbol           | Min              | Max          | Min                | Max          | Min                | Max          | Min                | Max          |

| 4   | EXTAL cycle time <sup>3</sup> <ul> <li>With DPLL disabled</li> <li>With DPLL enabled</li> </ul>               | ET <sub>C</sub>  | 5.0 ns<br>5.0 ns | ∞<br>62.5 ns | 4.55 ns<br>4.55 ns | ∞<br>62.5 ns | 4.17 ns<br>4.17 ns | ∞<br>62.5 ns | 3.64 ns<br>3.64 ns | ∞<br>62.5 ns |

| 7   | Instruction cycle time =<br>I <sub>CYC</sub> = ET <sub>C</sub><br>• With DPLL disabled<br>• With DPLL enabled | I <sub>CYC</sub> | 10 ns<br>5.0 ns  | ∞<br>1.6 μs  | 9.09 ns<br>4.55 ns | ∞<br>1.6 μs  | 8.33 ns<br>4.17 ns | ∞<br>1.6 μs  | 7.28 ns<br>3.64 ns | ∞<br>1.6 μs  |

| Table 2-5. | External Clock O | peration (Continued) | ) |

|------------|------------------|----------------------|---|

|------------|------------------|----------------------|---|

3. Measured at 50 percent of the input transition.

4. The indicated duty cycle is for the specified maximum frequency for which a part is rated. The minimum clock high or low time required for correction operation, however, remains the same at lower operating frequencies; therefore, when a lower clock frequency is used, the signal symmetry may vary from the specified duty cycle as long as the minimum high time and low time requirements are met.

Note: If an externally-supplied square wave voltage source is used, disable the internal oscillator circuit after boot-up by setting XTLD (PCTL Register bit 2 = 1—see the DSP56321 Reference Manual). The external square wave source connects to EXTAL and XTAL is not used. Figure 2-2 shows the EXTAL input signal.

Figure 2-2. External Input Clock Timing

#### 2.4.3 Clock Generator (CLKGEN) and Digital PLL (DPLL) **Characteristics**

| Table 2-6. | CLKGEN and DPLL | . Characteristics |

|------------|-----------------|-------------------|

|------------|-----------------|-------------------|

| Characteristics                              | 0h.u             | 200              | MHz              | 220              | MHz              | 240              | MHz              | 275              | MHz              | 11   |

|----------------------------------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------|

| Characteristics                              | Symbol           | Min              | Max              | Min              | Max              | Min              | Max              | Min              | Max              | Unit |

| Predivision factor                           | PDF <sup>1</sup> | 1                | 16               | 1                | 16               | 1                | 16               | 1                | 16               | _    |

| Predivider output clock frequency range      | PDFR             | 16               | 32               | 16               | 32               | 16               | 32               | 16               | 32               | MHz  |

| Total multiplication factor <sup>2</sup>     | MF               | 5                | 15               | 5                | 15               | 5                | 15               | 5                | 15               | _    |

| Multiplication factor integer part           | MFI <sup>1</sup> | 5                | 15               | 5                | 15               | 5                | 15               | 5                | 15               | _    |

| Multiplication factor numerator <sup>3</sup> | MFN              | 0                | 127              | 0                | 127              | 0                | 127              | 0                | 127              | _    |

| Multiplication factor denominator            | MFD              | 1                | 128              | 1                | 128              | 1                | 128              | 1                | 128              | _    |

| Double clock frequency range                 | DDFR             | 160              | 400              | 160              | 440              | 160              | 480              | 160              | 550              | MHz  |

| Phase lock-in time <sup>4</sup>              | DPLT             | 6.8 <sup>5</sup> | 150 <sup>6</sup> | μs   |

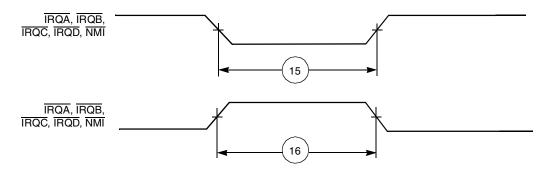

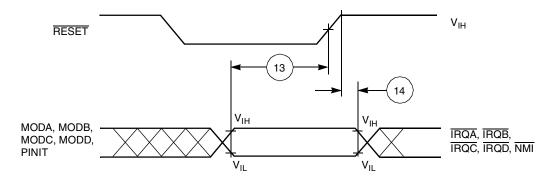

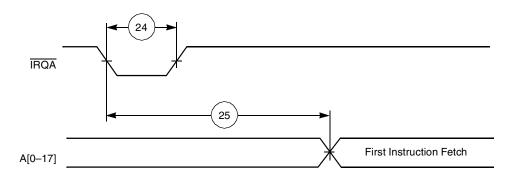

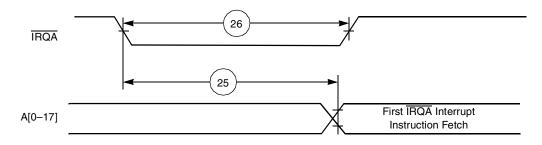

| Table 2-7. | Reset, Stop, Mode Select, and Interrupt Timing <sup>5</sup> | (CONTINUED) |

|------------|-------------------------------------------------------------|-------------|

|------------|-------------------------------------------------------------|-------------|

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                            | 200           | MHz                          | 220         | MHz                          | 240 MHz       |                              | 275 MHz       |                                 |                      |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------|------------------------------|-------------|------------------------------|---------------|------------------------------|---------------|---------------------------------|----------------------|

| No. | Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Expression                                                                 | Min           | Max                          | Min         | Мах                          | Min           | Max                          | Min           | Max                             | Unit                 |

|     | Delay from RD assertion to interrupt request deassertion for level sensitive fast interrupts <sup>1, 6, 7</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | (WS + 3.25) × T <sub>C</sub> –<br>10.94                                    | _             | Note 7                       |             | Note 7                       | _             | Note 7                       | _             | Note 7                          | ns                   |

|     | Delay from $\overline{\text{WR}}$ assertion to interrupt<br>request deassertion for level sensitive<br>fast interrupts <sup>1, 6, 7</sup><br>• SRAM WS = 3<br>• SRAM WS $\geq$ 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | (WS + 3) × T <sub>C</sub> – 10.94<br>(WS + 2.5) × T <sub>C</sub> – 10.94   |               | Note 7<br>Note 7             |             | Note 7<br>Note 7             |               | Note 7<br>Note 7             |               | Note 7<br>Note 7                | ns<br>ns             |

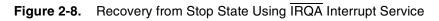

|     | Duration for IRQA assertion to recover from Stop state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                            | 8.0           | —                            | 8.0         | —                            | 8.0           | —                            | 8.0           | —                               | ns                   |

|     | <ul> <li>Delay from IRQA assertion to fetch of first instruction (when exiting Stop)<sup>2, 3</sup></li> <li>DPLL is not active during Stop (PCTL Bit 1 = 0) and Stop delay is enabled (Operating Mode Register Bit 6 = 0)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DPLT + (128K × T <sub>C</sub> )                                            | 662.2<br>μs   | 209.9<br>ms                  | 662.2<br>μs | 209.9<br>ms                  | 662.2<br>μs   | 209.9<br>ms                  | 662.2<br>μs   | 209.9<br>ms                     | _                    |

|     | <ul> <li>DPLL is not active during Stop<br/>(PCTL Bit 1 = 0) and Stop delay is<br/>not enabled (Operating Mode<br/>Register Bit 6 = 1)</li> <li>DPLL is active during Stop (PCTL<br/>Bit 1 = 1; Implies No Stop Delay)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DPLT + (23.75 ± 0.5) ×<br>T <sub>C</sub><br>(10.0 ± 1.75) × T <sub>C</sub> | 6.9<br>41.25  | 188.8<br>58.8                | 6.9<br>37.5 | 188.8<br>53.3                | 6.9<br>34.4   | 188.8<br>49.0                | 6.9<br>30.0   | 43.0                            | μs<br>ns             |

|     | <ul> <li>Duration of level sensitive IRQA assertion to ensure interrupt service (when exiting Stop)<sup>2, 3</sup></li> <li>DPLL is not active during Stop (PCTL bit 1 = 0) and Stop delay is enabled (Operating Mode Register Transport of the sensitive of</li></ul> | DPLT + (128 K × T <sub>C</sub> )                                           | 805.4         |                              | 805.4       |                              | 805.4         |                              | 805.4         | _                               | μs                   |

|     | <ul> <li>(PCTL bit 1 = 0) and Stop delay is<br/>not enabled (Operating Mode<br/>Register Bit 6 = 1)</li> <li>DPLL is active during Stop ((PCTL</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DPLT + (20.5 ±0.5) × T <sub>C</sub><br>5.5 × T <sub>C</sub>                | 150.1<br>27.5 | _                            | 150.1<br>25 | _                            | 150.1<br>22.9 | _                            | 150.1<br>20.0 | _                               | μs<br>ns             |

| 27  | bit 1 = 0; implies no Stop delay)<br>Interrupt Request Rate<br>• HI08, ESSI, SCI, Timer<br>• DMA<br>• IRQ, NMI (edge trigger)<br>• IRQ, NMI (level trigger)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12T <sub>C</sub><br>8T <sub>C</sub><br>8T <sub>C</sub><br>12T <sub>C</sub> |               | 60.0<br>40.0<br>40.0<br>60.0 | <br>        | 54.6<br>36.4<br>36.4<br>54.6 |               | 50.0<br>33.4<br>33.4<br>50.0 |               | 43.7<br>29.2<br>29.2<br>43.7    | ns<br>ns<br>ns<br>ns |

| 28  | <ul> <li>DMA Request Rate</li> <li>Data read from HI08, ESSI, SCI</li> <li>Data write to HI08, ESSI, SCI</li> <li>Timer</li> <li>IRQ, NMI (edge trigger)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6T <sub>C</sub><br>7T <sub>C</sub><br>2T <sub>C</sub><br>3T <sub>C</sub>   |               | 30.0<br>35.0<br>10.0<br>15.0 |             | 27.3<br>31.9<br>9.1<br>13.7  |               | 25.0<br>29.2<br>8.3<br>12.5  | <br>          | 21.84<br>25.48<br>7.28<br>10.92 | ns<br>ns<br>ns<br>ns |

|     | Delay from IRQA, IRQB, IRQC, IRQD,<br>NMI assertion to external memory<br>(DMA source) access address out<br>valid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4.25 × T <sub>C</sub> + 2.0                                                | 23.25         |                              | 21.34       |                              | 19.72         |                              | 17.45         | _                               | ns                   |

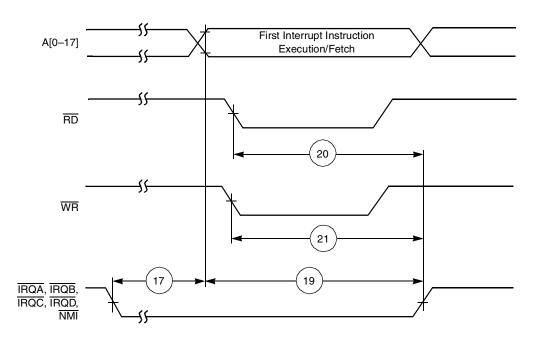

a) First Interrupt Instruction Execution

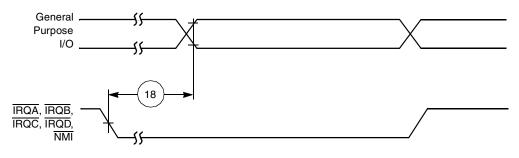

b) General-Purpose I/O

Figure 2-4. External Fast Interrupt Timing

Figure 2-5. External Interrupt Timing (Negative Edge-Triggered)

Figure 2-6. Operating Mode Select Timing

Figure 2-7. Recovery from Stop State Using IRQA

Figure 2-9. External Memory Access (DMA Source) Timing

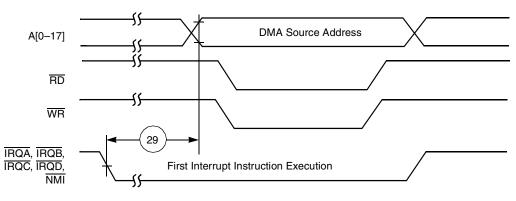

Figure 2-17. Write Timing Diagram, Non-Multiplexed Bus, Double Data Strobe

### 2.4.8 ESSI0/ESSI1 Timing

| No  | Characteristics <sup>4, 6</sup>                                         | Symbol                                 | Expression                                                | 200          | 200 MHz     |              | MHz         | 240          | MHz         | iz 275 MHz   |             | Cond-              | Unit     |

|-----|-------------------------------------------------------------------------|----------------------------------------|-----------------------------------------------------------|--------------|-------------|--------------|-------------|--------------|-------------|--------------|-------------|--------------------|----------|

| No. |                                                                         | Cymbol                                 | LAPICSSION                                                | Min          | Max         | Min          | Max         | Min          | Max         | Min          | Max         | ition <sup>5</sup> | Unit     |

| 430 | Clock cycle <sup>1</sup>                                                | T <sub>ECCX</sub><br>T <sub>ECCI</sub> | $6 \times T_C \\ 8 \times T_C$                            | 30.0<br>40.0 | _           | 27.3<br>36.6 | _           | 25.0<br>33.3 | _           | 21.5<br>25.0 | _           | x ck<br>i ck       | ns<br>ns |

| 431 | Clock high period<br>• For internal clock<br>• For external clock       |                                        | T <sub>ECCX</sub> /2 – 3.7<br>T <sub>ECCI</sub> /2 – 10.0 | 11.3<br>10.0 | _           | 9.9<br>8.2   | _           | 8.8<br>6.7   | _           | 7.21<br>2.5  | -           |                    | ns<br>ns |

| 432 | Clock low period<br>• For internal clock<br>• For external clock        |                                        | T <sub>ECCX</sub> /2 – 3.7<br>T <sub>ECCI</sub> /2 –10.0  | 11.3<br>10.0 |             | 9.9<br>8.2   |             | 8.8<br>6.7   |             | 7.21<br>2.5  |             |                    | ns<br>ns |

| 433 | RXC rising edge to FSR out (bit-length)<br>high                         |                                        |                                                           | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | x ck<br>i ck a     | ns       |

| 434 | RXC rising edge to FSR out (bit-length)<br>low                          |                                        |                                                           | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | x ck<br>i ck a     | ns       |

| 435 | RXC rising edge to FSR out (word-<br>length-relative) high <sup>2</sup> |                                        |                                                           | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | x ck<br>i ck a     | ns       |

| 436 | RXC rising edge to FSR out (word-<br>length-relative) low <sup>2</sup>  |                                        |                                                           | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | x ck<br>i ck a     | ns       |

| 437 | RXC rising edge to FSR out (word-<br>length) high                       |                                        |                                                           | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | x ck<br>i ck a     | ns       |

| 438 | RXC rising edge to FSR out (word-<br>length) low                        |                                        |                                                           | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | _            | 12.5<br>8.3 | x ck<br>i ck a     | ns       |

| 439 | Data in setup time before RXC (SCK in Synchronous mode) falling edge    |                                        |                                                           | 5.0<br>10.0  | _<br>_      | 5.0<br>10.0  | _<br>_      | 5.0<br>10.0  | _           | 5.0<br>10.0  | _           | x ck<br>i ck       | ns       |

| 440 | Data in hold time after RXC falling edge                                |                                        |                                                           | 3.8<br>5.0   | _           | 3.8<br>5.0   | _           | 3.8<br>5.0   | _           | 3.8<br>5.0   | _           | x ck<br>i ck       | ns       |

| 441 | FSR input (bl, wr) high before RXC falling edge <sup>2</sup>            |                                        |                                                           | 5.0<br>10.0  | _           | 5.0<br>10.0  | _           | 5.0<br>10.0  | _           | 5.0<br>10.0  | _           | x ck<br>i ck a     | ns       |

| 442 | FSR input (wl) high before RXC falling edge                             |                                        |                                                           | 5.0<br>10.0  | _           | 5.0<br>10.0  | _           | 5.0<br>10.0  | _           | 5.0<br>10.0  | _           | x ck<br>i ck a     | ns       |