Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | 8051                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 16MHz                                                                  |

| Connectivity               | EBI/EMI, UART/USART                                                    |

| Peripherals                | POR                                                                    |

| Number of I/O              | 32                                                                     |

| Program Memory Size        | 8KB (8K x 8)                                                           |

| Program Memory Type        | OTP                                                                    |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 256 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | -                                                                      |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 44-LCC (J-Lead)                                                        |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/p87c52sbaa-512 |

80C51 8-bit microcontroller family 4 K/8 K OTP/ROM low voltage (2.7 V-5.5 V), low power, high speed (33 MHz), 128/256 B RAM

# 80C51/87C51/80C52/87C52

# 80C52/87C52 ORDERING INFORMATION

|     | MEMORY SIZE<br>8K × 8 | TEMPERATURE RANGE °C<br>AND PACKAGE      | VOLTAGE<br>RANGE | FREQ.<br>(MHz) | DWG.#    |  |

|-----|-----------------------|------------------------------------------|------------------|----------------|----------|--|

| ROM | P80C52SBPN            | 0 to +70, Plastic Dual In-line Package   | 2.7 V to 5.5 V   | 0 to 16        | SOT129-1 |  |

| ОТР | P87C52SBPN            | 0 to +70, Plastic Dual In-line Package   | 2.7 V to 5.5 V   | 0 10 16        | 301129-1 |  |

| ROM | P80C52SBAA            | O to 170 Pleatic Leaded Ohio Comics      | 0.7.1/4- 5.5.1/  | 0 to 16        | SOT187-2 |  |

| ОТР | P87C52SBAA            | 0 to +70, Plastic Leaded Chip Carrier    | 2.7 V to 5.5 V   | 0 to 16        | 501187-2 |  |

| ROM | P80C52SBBB            | 0 to 170 Plantic Quad Flat Park          | 0.7.1/4- 5.5.1/  | 045.40         | COT207.0 |  |

| OTP | P87C52SBBB            | 0 to +70, Plastic Quad Flat Pack         | 2.7 V to 5.5 V   | 0 to 16        | SOT307-2 |  |

| ROM | P80C52SFPN            | 40 to 105 Plantia Dual la lina Pagliana  | 071/1 551/       | 0 to 16        | COT400.4 |  |

| OTP | P87C52SFPN            | –40 to +85, Plastic Dual In-line Package | 2.7 V to 5.5 V   |                | SOT129-1 |  |

| ROM | P80C52SFA A           | 40 to 105 Pleatic Londod Chin Coming     | 0.7.1/4- 5.5.1/  | 0 to 16        | SOT187-2 |  |

| OTP | P87C52SFA A           | –40 to +85, Plastic Leaded Chip Carrier  | 2.7 V to 5.5 V   | 0 10 16        | 501187-2 |  |

| ROM | P80C52SFBB            | –40 to +85, Plastic Quad Flat Pack       | 2.7 V to 5.5 V   | 0 to 16        | SOT307-2 |  |

| OTP | P87C52SFBB            | -40 to +65, Flastic Quad Flat Fack       | 2.7 V to 5.5 V   | 0 10 16        | 301307-2 |  |

| ROM | P80C52UBAA            | 0 to +70. Plastic Leaded Chip Carrier    | 5 V              | 0 to 33        | SOT187-2 |  |

| OTP | P87C52UBAA            | 0 to +70, Plastic Leaded Chip Carner     | 5 V              | 0 10 33        | 301107-2 |  |

| ROM | P80C52UBPN            | O to 170 Plantia Dual la lina Pagicara   | E.V.             | 0 to 22        | COT400.4 |  |

| ОТР | P87C52UBPN            | 0 to +70, Plastic Dual In-line Package   | 5 V              | 0 to 33        | SOT129-1 |  |

| ROM | P80C52UFA A           | -40 to +85, Plastic Leaded Chip Carrier  | 5 V              | 0 to 33        | SOT187-2 |  |

| ОТР | P87C52UFA A           | -40 to 400, Plastic Leaded Chip Carrier  | o v              | 0 10 33        | 301101-2 |  |

2000 Aug 07

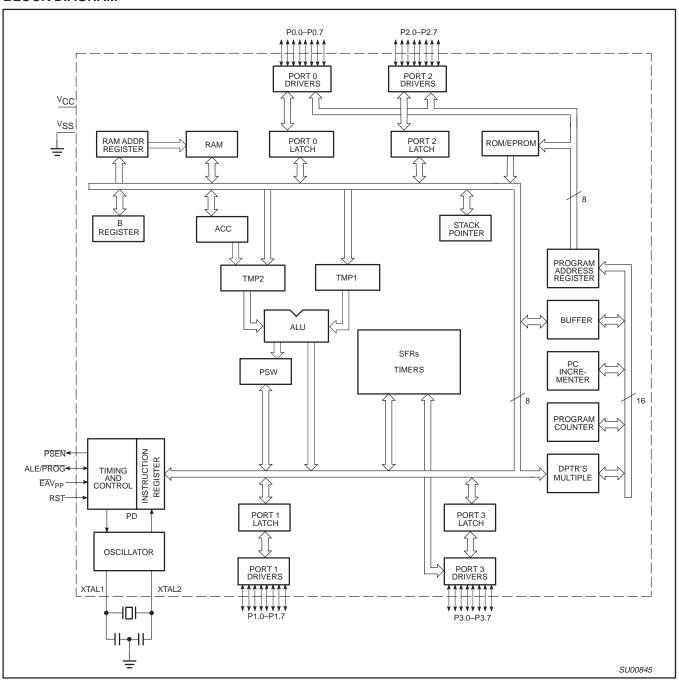

### **BLOCK DIAGRAM**

Philips Semiconductors Product specification

80C51 8-bit microcontroller family 4 K/8 K OTP/ROM low voltage (2.7 V–5.5 V), low power, high speed (33 MHz), 128/256 B RAM

# 80C51/87C51/80C52/87C52

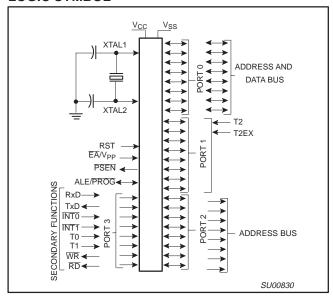

### LOGIC SYMBOL

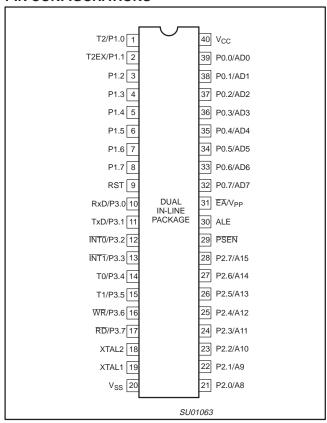

### **PIN CONFIGURATIONS**

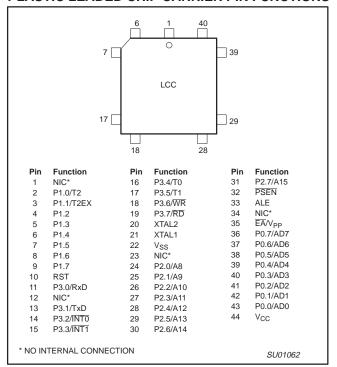

### PLASTIC LEADED CHIP CARRIER PIN FUNCTIONS

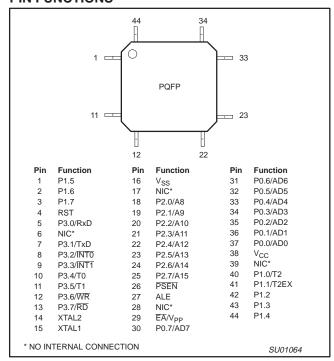

# PLASTIC QUAD FLAT PACK PIN FUNCTIONS

2000 Aug 07

6

80C51 8-bit microcontroller family 4 K/8 K OTP/ROM low voltage (2.7 V-5.5 V), low power, high speed (33 MHz), 128/256 B RAM

# 80C51/87C51/80C52/87C52

#### OSCILLATOR CHARACTERISTICS

XTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier. The pins can be configured for use as an on-chip oscillator, as shown in the logic symbol.

To drive the device from an external clock source, XTAL1 should be driven while XTAL2 is left unconnected. There are no requirements on the duty cycle of the external clock signal, because the input to the internal clock circuitry is through a divide-by-two flip-flop. However, minimum and maximum high and low times specified in the data sheet must be observed.

#### Reset

A reset is accomplished by holding the RST pin high for at least two machine cycles (24 oscillator periods), while the oscillator is running. To insure a good power-up reset, the RST pin must be high long enough to allow the oscillator time to start up (normally a few milliseconds) plus two machine cycles.

### **Stop Clock Mode**

The static design enables the clock speed to be reduced down to 0 MHz (stopped). When the oscillator is stopped, the RAM and Special Function Registers retain their values. This mode allows step-by-step utilization and permits reduced system power consumption by lowering the clock frequency down to any value. For lowest power consumption the Power Down mode is suggested.

### Idle Mode

In idle mode (see Table 2), the CPU puts itself to sleep while all of the on-chip peripherals stay active. The instruction to invoke the idle mode is the last instruction executed in the normal operating mode before the idle mode is activated. The CPU contents, the on-chip RAM, and all of the special function registers remain intact during this mode. The idle mode can be terminated either by any enabled interrupt (at which time the process is picked up at the interrupt service routine and continued), or by a hardware reset which starts the processor in the same manner as a power-on reset.

### **Power-Down Mode**

To save even more power, a Power Down mode (see Table 2) can be invoked by software. In this mode, the oscillator is stopped and the instruction that invoked Power Down is the last instruction executed. The on-chip RAM and Special Function Registers retain their values down to 2.0 V and care must be taken to return  $V_{CC}$  to the minimum specified operating voltages before the Power Down Mode is terminated.

For the 87C51 and 80C51 either a hardware reset or external interrupt can be used to exit from Power Down. Reset redefines all

the SFRs but does not change the on-chip RAM. An external interrupt allows both the SFRs and the on-chip RAM to retain their values. WUPD (AUXR1.3–Wakeup from Power Down) enables or disables the wakeup from power down with external interrupt. Where:

WUPD = 0 Disable WUPD = 1 Fnable

To properly terminate Power Down the reset or external interrupt should not be executed before  $V_{CC}$  is restored to its normal operating level and must be held active long enough for the oscillator to restart and stabilize (normally less than 10 ms).

With an external interrupt, INT0 or INT1 must be enabled and configured as level-sensitive. Holding the pin low restarts the oscillator but bringing the pin back high completes the exit. Once the interrupt is serviced, the next instruction to be executed after RETI will be the one following the instruction that put the device into Power Down.

### **LPEP**

The eprom array contains some analog circuits that are not required when  $V_{CC}$  is less than 4 V, but are required for a  $V_{CC}$  greater than 4 V. The LPEP bit (AUXR.4), when set, will powerdown these analog circuits resulting in a reduced supply current. This bit should be set ONLY for applications that operate at a  $V_{CC}$  less than 4 V.

### **Design Consideration**

• When the idle mode is terminated by a hardware reset, the device normally resumes program execution, from where it left off, up to two machine cycles before the internal reset algorithm takes control. On-chip hardware inhibits access to internal RAM in this event, but access to the port pins is not inhibited. To eliminate the possibility of an unexpected write when Idle is terminated by reset, the instruction following the one that invokes Idle should not be one that writes to a port pin or to external memory.

### **ONCE™ Mode**

The ONCE ("On-Circuit Emulation") Mode facilitates testing and debugging of systems without the device having to be removed from the circuit. The ONCE Mode is invoked by:

- 1. Pull ALE low while the device is in reset and  $\overline{\text{PSEN}}$  is high;

- 2. Hold ALE low as RST is deactivated.

While the device is in ONCE Mode, the Port 0 pins go into a float state, and the other port pins and ALE and PSEN are weakly pulled high. The oscillator circuit remains active. While the device is in this mode, an emulator or test CPU can be used to drive the circuit. Normal operation is restored when a normal reset is applied.

Table 2. External Pin Status During Idle and Power-Down Modes

| MODE       | PROGRAM MEMORY | ALE | PSEN | PORT 0 | PORT 1 | PORT 2  | PORT 3 |

|------------|----------------|-----|------|--------|--------|---------|--------|

| Idle       | Internal       | 1   | 1    | Data   | Data   | Data    | Data   |

| Idle       | External       | 1   | 1    | Float  | Data   | Address | Data   |

| Power-down | Internal       | 0   | 0    | Data   | Data   | Data    | Data   |

| Power-down | External       | 0   | 0    | Float  | Data   | Data    | Data   |

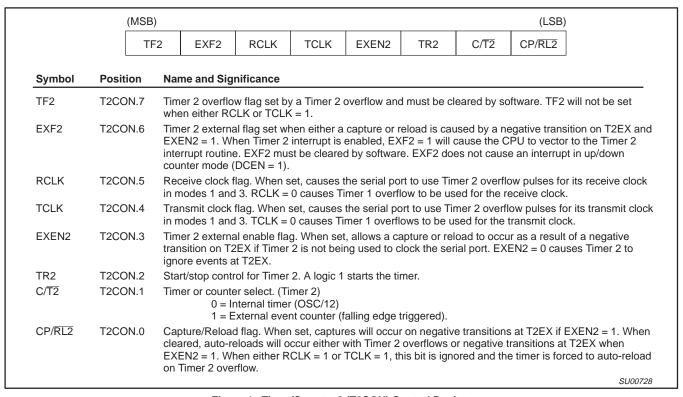

Figure 1. Timer/Counter 2 (T2CON) Control Register

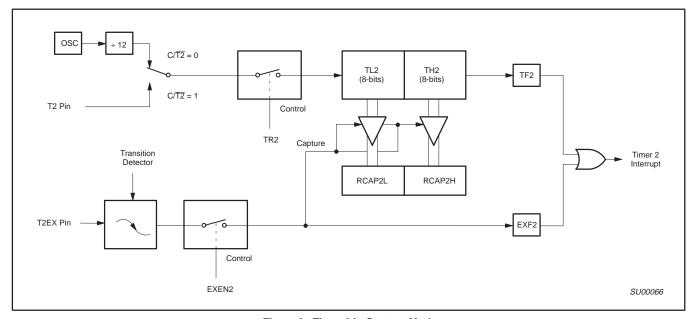

Figure 2. Timer 2 in Capture Mode

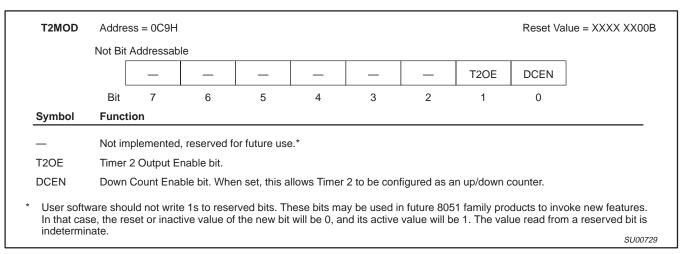

Figure 3. Timer 2 Mode (T2MOD) Control Register

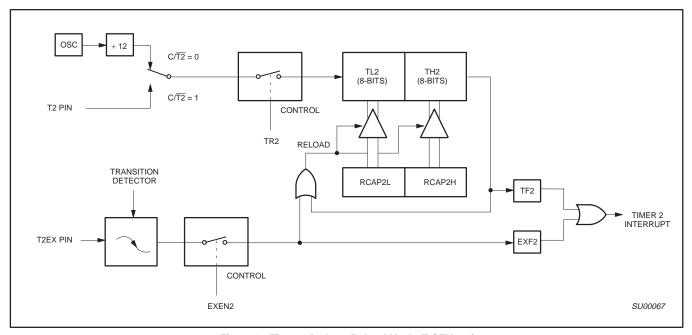

Figure 4. Timer 2 in Auto-Reload Mode (DCEN = 0)

# 80C51 8-bit microcontroller family 4 K/8 K OTP/ROM low voltage (2.7 V–5.5 V), low power, high speed (33 MHz), 128/256 B RAM

# 80C51/87C51/80C52/87C52

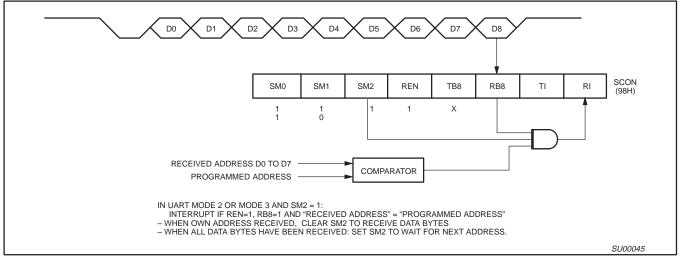

and 1 and exclude Slave 2 use address 1110 0100, since it is necessary to make bit 2 = 1 to exclude slave 2.

The Broadcast Address for each slave is created by taking the logical OR of SADDR and SADEN. Zeros in this result are trended as don't-cares. In most cases, interpreting the don't-cares as ones, the broadcast address will be FF hexadecimal.

Upon reset SADDR (SFR address 0A9H) and SADEN (SFR address 0B9H) are leaded with 0s. This produces a given address of all "don't cares" as well as a Broadcast address of all "don't cares". This effectively disables the Automatic Addressing mode and allows the microcontroller to use standard 80C51 type UART drivers which do not make use of this feature.

|                                          | S               | CON Addr                                                                                                                                                                                            | ess = 98H                   |               |             |                                |                      |             |             | Reset Value = 0000 0000B                                     |

|------------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------|-------------|--------------------------------|----------------------|-------------|-------------|--------------------------------------------------------------|

|                                          | Bit Add         | dressable                                                                                                                                                                                           |                             |               |             |                                |                      |             |             | _                                                            |

|                                          |                 | SM0/FE                                                                                                                                                                                              | SM1                         | SM2           | REN         | TB8                            | RB8                  | TI          | RI          |                                                              |

|                                          | Bit:            | 7                                                                                                                                                                                                   | 6                           | 5             | 4           | 3                              | 2                    | 1           | 0           | <u> </u>                                                     |

|                                          | (               | SMOD0 = 0                                                                                                                                                                                           | )/1)*                       |               |             |                                |                      |             |             |                                                              |

| Symbol                                   | Func            | tion                                                                                                                                                                                                |                             |               |             |                                |                      |             |             |                                                              |

| FE                                       |                 |                                                                                                                                                                                                     |                             |               |             | hen an inval<br>MOD0 bit mu    |                      |             |             | oit is not cleared by valid<br>ne FE bit.                    |

| SM0                                      | Seria           | l Port Mode                                                                                                                                                                                         | Bit 0, (SM                  | OD0 must :    | = 0 to acce | ss bit SM0)                    |                      |             |             |                                                              |

| SM1                                      | Seria<br>SM0    | I Port Mode<br>SM1                                                                                                                                                                                  | Bit 1<br><b>Mode</b>        | Descr         | iption      | Baud Rate                      | **                   |             |             |                                                              |

|                                          | 0               | 0                                                                                                                                                                                                   | 0                           | shift re      | egister     | f <sub>OSC</sub> /12           |                      |             |             |                                                              |

|                                          | 0               | 1                                                                                                                                                                                                   | 1                           | 8-bit U       |             | variable                       |                      |             |             |                                                              |

|                                          | 1               | 0                                                                                                                                                                                                   | 2                           | 9-bit U       |             | f <sub>OSC</sub> /64 or        | f <sub>OSC</sub> /32 |             |             |                                                              |

|                                          | 1               | 1                                                                                                                                                                                                   | 3                           | 9-bit U       |             | variable                       |                      |             |             |                                                              |

| SM2                                      | receiv<br>In Mo | ed 9th data                                                                                                                                                                                         | a bit (RB8)<br>2 = 1 then l | is 1, indicat | ting an add | lress, and th<br>d unless a va | e received           | byte is a G | liven or Br | oot be set unless the oadcast Address. ne received byte is a |

| REN                                      | Enab            | les serial re                                                                                                                                                                                       | ception. Se                 | t by softwa   | are to enab | le reception.                  | Clear by s           | oftware to  | disable red | ception.                                                     |

| TB8                                      | The 9           | th data bit t                                                                                                                                                                                       | hat will be                 | transmitted   | I in Modes  | 2 and 3. Set                   | or clear by          | software    | as desired  |                                                              |

| RB8                                      |                 | des 2 and 3<br>de 0, RB8 i                                                                                                                                                                          |                             |               | was receiv  | ed. In Mode                    | 1, if SM2 =          | = 0, RB8 is | the stop b  | it that was received.                                        |

| TI                                       |                 | Transmit interrupt flag. Set by hardware at the end of the 8th bit time in Mode 0, or at the beginning of the stop bit in the other modes, in any serial transmission. Must be cleared by software. |                             |               |             |                                |                      |             |             |                                                              |

| RI                                       |                 |                                                                                                                                                                                                     |                             |               |             | d of the 8th bee SM2). M       |                      |             |             | rough the stop bit time in                                   |

| TE:<br>MOD0 is locate<br>osc = oscillato |                 | 6.                                                                                                                                                                                                  |                             |               |             |                                |                      |             |             | SU00043                                                      |

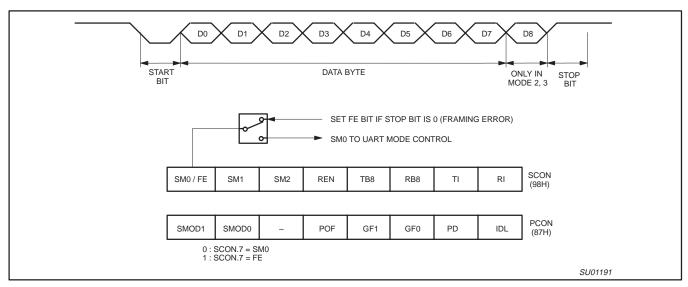

Figure 7. SCON: Serial Port Control Register

Figure 8. UART Framing Error Detection

Figure 9. UART Multiprocessor Communication, Automatic Address Recognition

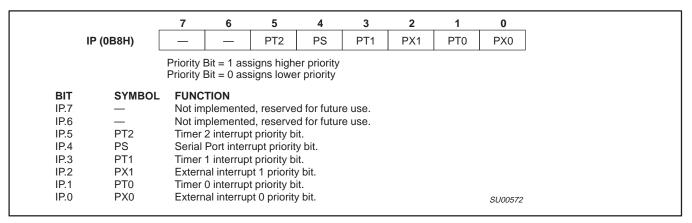

Figure 11. IP Registers

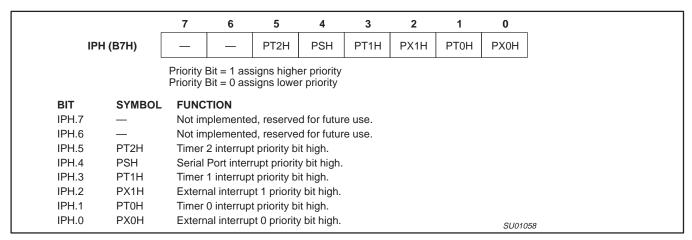

Figure 12. IPH Registers

80C51 8-bit microcontroller family 4 K/8 K OTP/ROM low voltage (2.7 V–5.5 V), low power, high speed (33 MHz), 128/256 B RAM

# 80C51/87C51/80C52/87C52

# **ABSOLUTE MAXIMUM RATINGS**1, 2, 3

| PARAMETER                                                                                    | RATING                 | UNIT |

|----------------------------------------------------------------------------------------------|------------------------|------|

| Operating temperature under bias                                                             | 0 to +70 or -40 to +85 | °C   |

| Storage temperature range                                                                    | -65 to +150            | °C   |

| Voltage on EA/V <sub>PP</sub> pin to V <sub>SS</sub>                                         | 0 to +13.0             | V    |

| Voltage on any other pin to V <sub>SS</sub>                                                  | -0.5 to +6.5           | V    |

| Maximum I <sub>OL</sub> per I/O pin                                                          | 15                     | mA   |

| Power dissipation (based on package heat transfer limitations, not device power consumption) | 1.5                    | W    |

### NOTES:

- 1. Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any conditions other than those described in the AC and DC Electrical Characteristics section of this specification is not implied.

- This product includes circuitry specifically designed for the protection of its internal devices from the damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying greater than the rated maximum.

Parameters are valid over operating temperature range unless otherwise specified. All voltages are with respect to V<sub>SS</sub> unless otherwise

- Parameters are valid over operating temperature range unless otherwise specified. All voltages are with respect to V<sub>SS</sub> unless otherwise noted.

### **AC ELECTRICAL CHARACTERISTICS**

$T_{amb} = 0$ °C to +70°C or -40°C to +85°C

|                     |        |                                                             | CLOCK FREQUENCY<br>RANGE –f |     |            |

|---------------------|--------|-------------------------------------------------------------|-----------------------------|-----|------------|

| SYMBOL              | FIGURE | PARAMETER                                                   | MIN                         | MAX | UNIT       |

| 1/t <sub>CLCL</sub> | 29     | Oscillator frequency Speed versions : S (16 MHz) U (33 MHz) | 0                           |     | MHz<br>MHz |

80C51 8-bit microcontroller family 4 K/8 K OTP/ROM low voltage (2.7 V-5.5 V), low power, high speed (33 MHz), 128/256 B RAM

# 80C51/87C51/80C52/87C52

#### DC ELECTRICAL CHARACTERISTICS

$T_{amb} = 0^{\circ}C$  to +70°C or -40°C to +85°C,  $V_{CC} = 2.7$  V to 5.5 V,  $V_{SS} = 0$  V (16 MHz devices)

| 0)/440.01        | DADAMETED                                                                                                                                     | TEST                                                                                                        |                          |                  |                          |                      |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--------------------------|------------------|--------------------------|----------------------|

| SYMBOL           | PARAMETER                                                                                                                                     | CONDITIONS                                                                                                  | MIN                      | TYP <sup>1</sup> | MAX                      | UNIT                 |

| \ /              | Lancet Laurentha and 11                                                                                                                       | 4.0 V < V <sub>CC</sub> < 5.5 V                                                                             | -0.5                     |                  | 0.2 V <sub>CC</sub> -0.1 | V                    |

| $V_{IL}$         | Input low voltage <sup>11</sup>                                                                                                               | 2.7 V <v<sub>CC&lt; 4.0 V</v<sub>                                                                           | -0.5                     |                  | 0.7                      | V                    |

| V <sub>IH</sub>  | Input high voltage (ports 0, 1, 2, 3, EA)                                                                                                     |                                                                                                             | 0.2 V <sub>CC</sub> +0.9 |                  | V <sub>CC</sub> +0.5     | V                    |

| V <sub>IH1</sub> | Input high voltage, XTAL1, RST <sup>11</sup>                                                                                                  |                                                                                                             | 0.7 V <sub>CC</sub>      |                  | V <sub>CC</sub> +0.5     | V                    |

| V <sub>OL</sub>  | Output low voltage, ports 1, 2, 8                                                                                                             | $V_{CC} = 2.7 \text{ V}$ $I_{OL} = 1.6 \text{ mA}^2$                                                        |                          |                  | 0.4                      | V                    |

| V <sub>OL1</sub> | Output low voltage, port 0, ALE, PSEN8, 7                                                                                                     | $V_{CC} = 2.7 \text{ V}$<br>$I_{OL} = 3.2 \text{ mA}^2$                                                     |                          |                  | 0.4                      | V                    |

| V <sub>OH</sub>  | Output himb vallege parts 4, 0, 9,3                                                                                                           | $V_{CC} = 2.7 \text{ V}$ $I_{OH} = -20 \mu\text{A}$                                                         | V <sub>CC</sub> - 0.7    |                  |                          | V                    |

|                  | Output high voltage, ports 1, 2, 3 <sup>3</sup>                                                                                               | V <sub>CC</sub> = 4.5 V<br>I <sub>OH</sub> = -30 μA                                                         | V <sub>CC</sub> - 0.7    |                  |                          | V                    |

| V <sub>OH1</sub> | Output high voltage (port 0 in external bus mode), ALE <sup>9</sup> , PSEN <sup>3</sup>                                                       | $V_{CC} = 2.7 \text{ V}$<br>$I_{OH} = -3.2 \text{ mA}$                                                      | V <sub>CC</sub> - 0.7    |                  |                          | V                    |

| I <sub>IL</sub>  | Logical 0 input current, ports 1, 2, 3                                                                                                        | V <sub>IN</sub> = 0.4 V                                                                                     | -1                       |                  | -50                      | μΑ                   |

| I <sub>TL</sub>  | Logical 1-to-0 transition current, ports 1, 2, 36                                                                                             | V <sub>IN</sub> = 2.0 V<br>See note 4                                                                       |                          |                  | -650                     | μА                   |

| I <sub>LI</sub>  | Input leakage current, port 0                                                                                                                 | $0.45 < V_{IN} < V_{CC} - 0.3$                                                                              |                          |                  | ±10                      | μΑ                   |

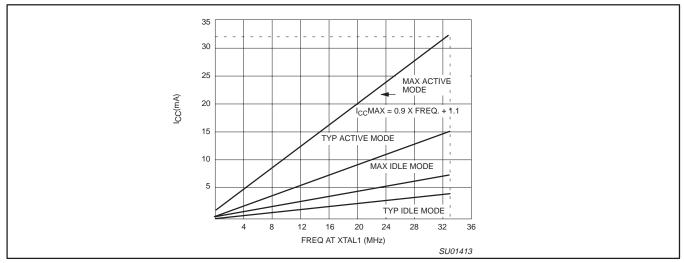

| Icc              | Power supply current (see Figure 21): Active mode @ 16 MHz Idle mode @ 16 MHz Power-down mode or clock stopped (see Figure 25 for conditions) | See note 5 $T_{amb} = 0^{\circ}C \text{ to } 70^{\circ}C$ $T_{amb} = -40^{\circ}C \text{ to } +85^{\circ}C$ |                          | 3                | 50<br>75                 | μΑ<br>μΑ<br>μΑ<br>μΑ |

| R <sub>RST</sub> | Internal reset pull-down resistor                                                                                                             |                                                                                                             | 40                       |                  | 225                      | kΩ                   |

| C <sub>IO</sub>  | Pin capacitance <sup>10</sup> (except <del>EA</del> )                                                                                         |                                                                                                             |                          |                  | 15                       | pF                   |

### NOTES:

- 1. Typical ratings are not guaranteed. The values listed are at room temperature, 5 V.

- Capacitive loading on ports 0 and 2 may cause spurious noise to be superimposed on the Vols of ALE and ports 1 and 3. The noise is due to external bus capacitance discharging into the port 0 and port 2 pins when these pins make 1-to-0 transitions during bus operations. In the worst cases (capacitive loading > 100 pF), the noise pulse on the ALE pin may exceed 0.8 V. In such cases, it may be desirable to qualify ALE with a Schmitt Trigger, or use an address latch with a Schmitt Trigger STROBE input. IoL can exceed these conditions provided that no single output sinks more than 5 mA and no more than two outputs exceed the test conditions

- 3. Capacitive loading on ports 0 and 2 may cause the  $V_{OH}$  on ALE and  $\overline{PSEN}$  to momentarily fall below the  $V_{CC}$ -0.7 specification when the address bits are stabilizing.

- Pins of ports 1, 2 and 3 source a transition current when they are being externally driven from 1 to 0. The transition current reaches its maximum value when V<sub>IN</sub> is approximately 2 V.

- See Figures 22 through 25 for I<sub>CC</sub> test conditions.

$I_{CC} = 0.9 \times FREQ. + 1.1 \text{ mA}$

- Idle mode:  $I_{CC} = 0.18 \times FREQ. +1.01$  mA; See Figure 21. 6. This value applies to  $T_{amb} = 0^{\circ}C$  to  $+70^{\circ}C$ . For  $T_{amb} = -40^{\circ}C$  to  $+85^{\circ}C$ ,  $I_{TL} = -750$   $\mu$ A.

- Load capacitance for port 0, ALE, and  $\overline{PSEN} = 100 \text{ pF}$ , load capacitance for all other outputs = 80 pF.

- 8. Under steady state (non-transient) conditions,  $I_{OL}$  must be externally limited as follows: Maximum I<sub>OL</sub> per port pin: 15 mA (\*NOTE: This is 85°C specification.)

Maximum I<sub>OL</sub> per 8-bit port: 26 mA Maximum total I<sub>OL</sub> for all outputs: 71 mA

If  $I_{OL}$  exceeds the test condition,  $V_{OL}$  may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

- ALE is tested to V<sub>OH1</sub>, except when ALE is off then V<sub>OH</sub> is the voltage specification.

- 10. Pin capacitance is characterized but not tested. Pin capacitance is less than 25 pF. Pin capacitance of ceramic package is less than 15 pF (except EA is 25 pF).

- 11. To improve noise rejection a nominal 100 ns glitch rejection circuitry has been added to the RST pin, and a nominal 15 ns glitch rejection circuitry has been added to the INTO and INTO pins. Previous devices provided only an inherent 5 ns of glitch rejection.

2000 Aug 07 22

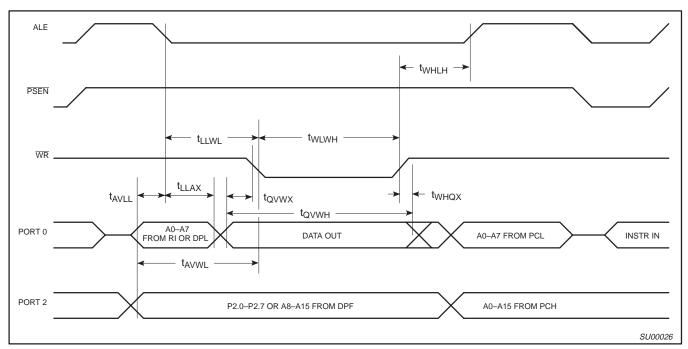

Figure 16. External Data Memory Write Cycle

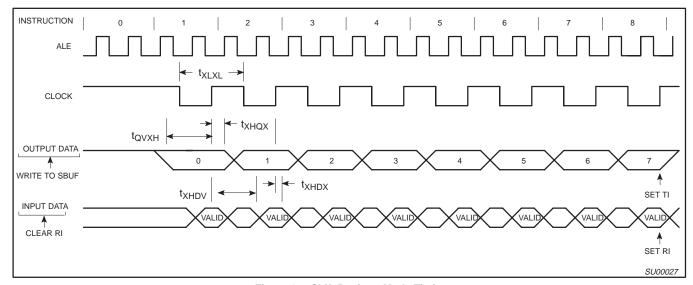

Figure 17. Shift Register Mode Timing

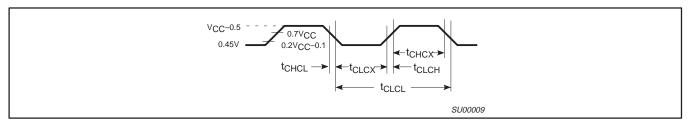

Figure 18. External Clock Drive

Philips Semiconductors Product specification

80C51 8-bit microcontroller family 4 K/8 K OTP/ROM low voltage (2.7 V-5.5 V), low power, high speed (33 MHz), 128/256 B RAM

# 80C51/87C51/80C52/87C52

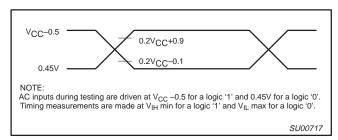

Figure 19. AC Testing Input/Output

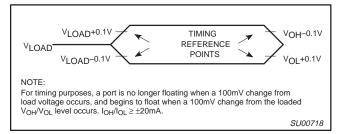

Figure 20. Float Waveform

$\label{eq:continuous} \mbox{Figure 21. I}_{\mbox{CC}} \mbox{ vs. FREQ} \\ \mbox{Valid only within frequency specifications of the device under test}$

80C51 8-bit microcontroller family 4 K/8 K OTP/ROM low voltage (2.7 V–5.5 V), low power, high speed (33 MHz), 128/256 B RAM

# 80C51/87C51/80C52/87C52

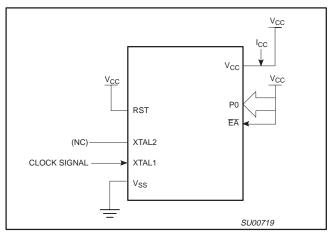

Figure 22. I<sub>CC</sub> Test Condition, Active Mode All other pins are disconnected

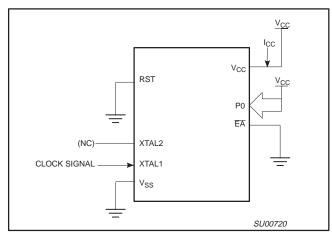

Figure 23. I<sub>CC</sub> Test Condition, Idle Mode All other pins are disconnected

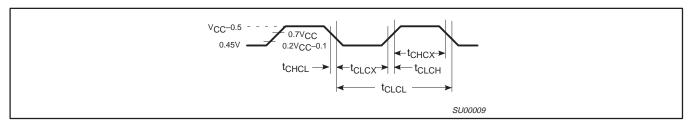

Figure 24. Clock Signal Waveform for  $I_{CC}$  Tests in Active and Idle Modes  $t_{CLCH}$  =  $t_{CHCL}$  = 5ns

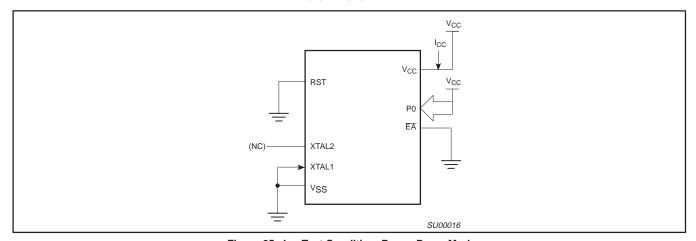

Figure 25.  $I_{CC}$  Test Condition, Power Down Mode All other pins are disconnected.  $V_{CC}$  = 2 V to 5.5 V

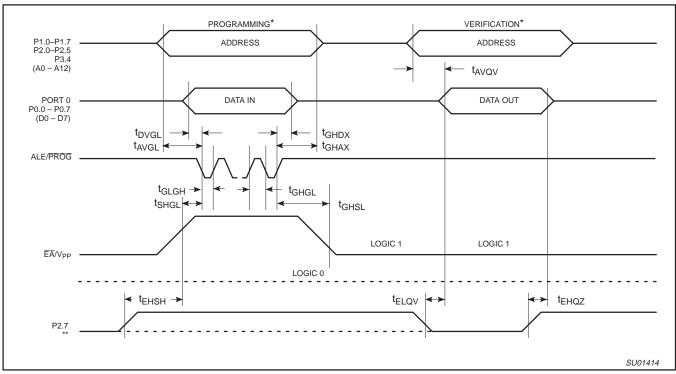

Figure 28. Program Verification

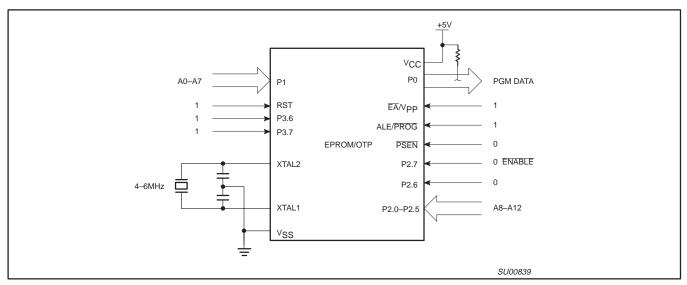

### **EPROM PROGRAMMING AND VERIFICATION CHARACTERISTICS**

$T_{amb} = 21$ °C to +27°C,  $V_{CC} = 5 \text{ V} \pm 10\%$ ,  $V_{SS} = 0 \text{ V (See Figure 29)}$

| SYMBOL              | PARAMETER                             | MIN                 | MAX                 | UNIT |

|---------------------|---------------------------------------|---------------------|---------------------|------|

| V <sub>PP</sub>     | Programming supply voltage            | 12.5                | 13.0                | V    |

| I <sub>PP</sub>     | Programming supply current            |                     | 50 <sup>1</sup>     | mA   |

| 1/t <sub>CLCL</sub> | Oscillator frequency                  | 4                   | 6                   | MHz  |

| t <sub>AVGL</sub>   | Address setup to PROG low             | 48t <sub>CLCL</sub> |                     |      |

| t <sub>GHAX</sub>   | Address hold after PROG               | 48t <sub>CLCL</sub> |                     |      |

| t <sub>DVGL</sub>   | Data setup to PROG low                | 48t <sub>CLCL</sub> |                     |      |

| t <sub>GHDX</sub>   | Data hold after PROG                  | 48t <sub>CLCL</sub> |                     |      |

| t <sub>EHSH</sub>   | P2.7 (ENABLE) high to V <sub>PP</sub> | 48t <sub>CLCL</sub> |                     |      |

| t <sub>SHGL</sub>   | V <sub>PP</sub> setup to PROG low     | 10                  |                     | μs   |

| t <sub>GHSL</sub>   | V <sub>PP</sub> hold after PROG       | 10                  |                     | μs   |

| t <sub>GLGH</sub>   | PROG width                            | 90                  | 110                 | μs   |

| t <sub>AVQV</sub>   | Address to data valid                 |                     | 48t <sub>CLCL</sub> |      |

| t <sub>ELQZ</sub>   | ENABLE low to data valid              |                     | 48t <sub>CLCL</sub> |      |

| t <sub>EHQZ</sub>   | Data float after ENABLE               | 0                   | 48t <sub>CLCL</sub> |      |

| t <sub>GHGL</sub>   | PROG high to PROG low                 | 10                  |                     | μs   |

### NOTE:

1. Not tested.

### NOTES:

- \* FOR PROGRAMMING CONFIGURATION SEE FIGURE 26 FOR VERIFICATION CONDITIONS SEE FIGURE 28.

- \*\* SEE TABLE 8.

Figure 29. EPROM Programming and Verification

### MASK ROM DEVICES

### **Security Bits**

With none of the security bits programmed the code in the program memory can be verified. If the encryption table is programmed, the code will be encrypted when verified. When only security bit 1 (see Table 10) is programmed, MOVC instructions executed from external program memory are disabled from fetching code bytes

from the internal memory,  $\overline{\text{EA}}$  is latched on Reset and all further programming of the EPROM is disabled. When security bits 1 and 2 are programmed, in addition to the above, verify mode is disabled.

### **Encryption Array**

64 bytes of encryption array are initially unprogrammed (all 1s).

**Table 10. Program Security Bits**

| PROGRAM LOCK BITS <sup>1, 2</sup> |     | BITS <sup>1, 2</sup> |                                                                                                                                                                                                                        |

|-----------------------------------|-----|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                   | SB1 | SB2                  | PROTECTION DESCRIPTION                                                                                                                                                                                                 |

| 1                                 | U   |                      | No Program Security features enabled.<br>(Code verify will still be encrypted by the Encryption Array if programmed.)                                                                                                  |

| 2                                 | Р   |                      | MOVC instructions executed from external program memory are disabled from fetching code bytes from internal memory, $\overline{EA}$ is sampled and latched on Reset, and further programming of the EPROM is disabled. |

#### NOTES:

- 1. P programmed. U unprogrammed.

- 2. Any other combination of the security bits is not defined.

Philips Semiconductors Product specification

80C51 8-bit microcontroller family 4 K/8 K OTP/ROM low voltage (2.7 V–5.5 V), low power, high speed (33 MHz), 128/256 B RAM

# 80C51/87C51/80C52/87C52

### 80C51 ROM CODE SUBMISSION

When submitting ROM code for the 80C51, the following must be specified:

- 1. 4k byte user ROM data

- 2. 64 byte ROM encryption key

- 3. ROM security bits.

| ADDRESS        | CONTENT | BIT(S) | COMMENT            |

|----------------|---------|--------|--------------------|

| 0000H to 0FFFH | DATA    | 7:0    | User ROM Data      |

| 1000H to 103FH | KEY     | 7:0    | ROM Encryption Key |

| 1040H          | SEC     | 0      | ROM Security Bit 1 |

| 1040H          | SEC     | 1      | ROM Security Bit 2 |

Security Bit 1: When programmed, this bit has two effects on masked ROM parts:

- 1. External MOVC is disabled, and

- 2. EA is latched on Reset.

Security Bit 2: When programmed, this bit inhibits Verify User ROM.

NOTE: Security Bit 2 cannot be enabled unless Security Bit 1 is enabled.

If the ROM Code file does not include the options, the following information must be included with the ROM code.

For each of the following, check the appropriate box, and send to Philips along with the code:

| Security Bit #1: | □ Enabled | ☐ Disable | ed                          |

|------------------|-----------|-----------|-----------------------------|

| Security Bit #2: | ☐ Enabled | ☐ Disable | ed                          |

| Encryption:      | □ No      | □ Yes     | If Yes, must send key file. |

### 80C52 ROM CODE SUBMISSION

When submitting ROM code for the 80C52, the following must be specified:

- 1. 8k byte user ROM data

- 2. 64 byte ROM encryption key

- 3. ROM security bits.

| ADDRESS        | CONTENT | BIT(S) | COMMENT            |

|----------------|---------|--------|--------------------|

| 0000H to 1FFFH | DATA    | 7:0    | User ROM Data      |

| 2000H to 203FH | KEY     | 7:0    | ROM Encryption Key |

| 2040H          | SEC     | 0      | ROM Security Bit 1 |

| 2040H          | SEC     | 1      | ROM Security Bit 2 |

Security Bit 1: When programmed, this bit has two effects on masked ROM parts:

- 1. External MOVC is disabled, and

- 2. EA is latched on Reset.

Security Bit 2: When programmed, this bit inhibits Verify User ROM.

NOTE: Security Bit 2 cannot be enabled unless Security Bit 1 is enabled.

If the ROM Code file does not include the options, the following information must be included with the ROM code.

For each of the following, check the appropriate box, and send to Philips along with the code:

| Security Bit #1: | ☐ Enabled | ☐ Disabled                       |

|------------------|-----------|----------------------------------|

| Security Bit #2: | ☐ Enabled | ☐ Disabled                       |

| Encryption:      | □ No      | ☐ Yes If Yes, must send key file |

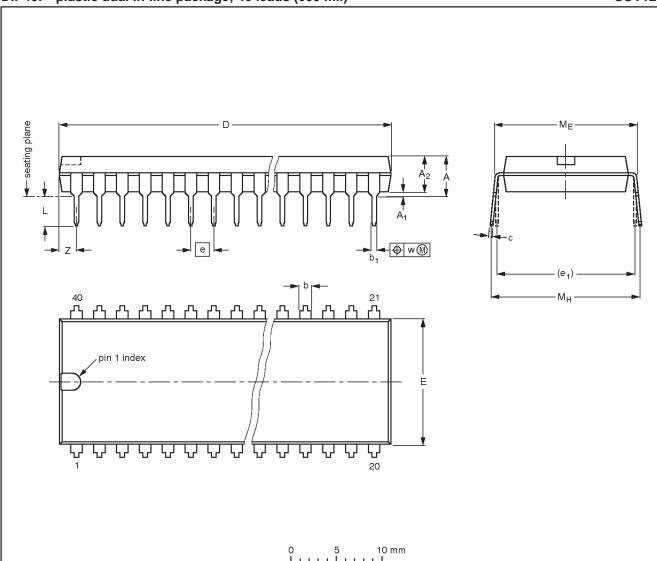

# DIP40: plastic dual in-line package; 40 leads (600 mil)

SOT129-1

# Scale

### DIMENSIONS (inch dimensions are derived from the original mm dimensions)

| UNIT   | A<br>max. | A <sub>1</sub><br>min. | A <sub>2</sub><br>max. | b              | b <sub>1</sub> | c              | D <sup>(1)</sup> | E <sup>(1)</sup> | е    | e <sub>1</sub> | L            | ME             | Мн             | w     | Z <sup>(1)</sup><br>max. |

|--------|-----------|------------------------|------------------------|----------------|----------------|----------------|------------------|------------------|------|----------------|--------------|----------------|----------------|-------|--------------------------|

| mm     | 4.7       | 0.51                   | 4.0                    | 1.70<br>1.14   | 0.53<br>0.38   | 0.36<br>0.23   | 52.50<br>51.50   | 14.1<br>13.7     | 2.54 | 15.24          | 3.60<br>3.05 | 15.80<br>15.24 | 17.42<br>15.90 | 0.254 | 2.25                     |

| inches | 0.19      | 0.020                  | 0.16                   | 0.067<br>0.045 | 0.021<br>0.015 | 0.014<br>0.009 | 2.067<br>2.028   | 0.56<br>0.54     | 0.10 | 0.60           | 0.14<br>0.12 | 0.62<br>0.60   | 0.69<br>0.63   | 0.01  | 0.089                    |

#### Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  |        | REFER  | RENCES    | EUROPEAN   | ISSUE DATE                      |

|----------|--------|--------|-----------|------------|---------------------------------|

| VERSION  | IEC    | JEDEC  | EIAJ      | PROJECTION | ISSUE DATE                      |

| SOT129-1 | 051G08 | MO-015 | SC-511-40 |            | <del>95-01-14</del><br>99-12-27 |

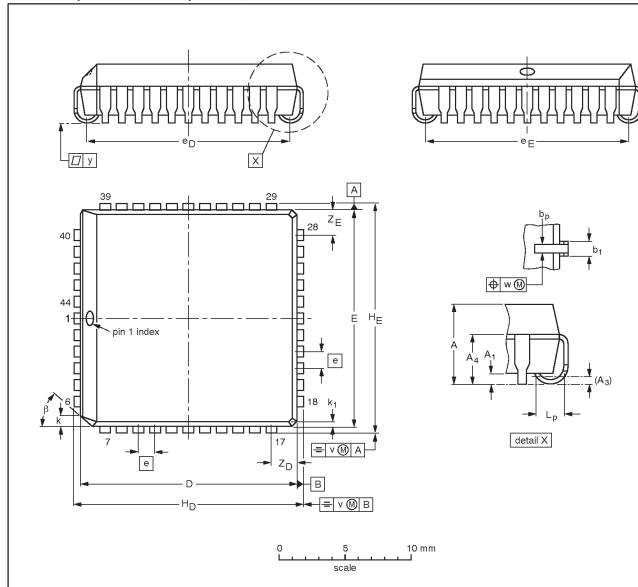

# PLCC44: plastic leaded chip carrier; 44 leads

SOT187-2

### DIMENSIONS (millimetre dimensions are derived from the original inch dimensions)

| UNIT   | Α              | A <sub>1</sub><br>min. | A <sub>3</sub> | A <sub>4</sub><br>max. | bp           | b <sub>1</sub> | D <sup>(1)</sup> | E <sup>(1)</sup> | е    | e <sub>D</sub> | еE             | H <sub>D</sub> | HE             | k              | k <sub>1</sub><br>max. | Lp             | v     | w     | у     |       | - 1   | β               |

|--------|----------------|------------------------|----------------|------------------------|--------------|----------------|------------------|------------------|------|----------------|----------------|----------------|----------------|----------------|------------------------|----------------|-------|-------|-------|-------|-------|-----------------|

| mm     | 4.57<br>4.19   | 0.51                   | 0.25           | 3.05                   | 0.53<br>0.33 |                |                  | 16.66<br>16.51   |      | 16.00<br>14.99 |                |                |                |                | 0.51                   | 1.44<br>1.02   | 0.18  | 0.18  | 0.10  | 2.16  | 2.16  | 45 <sup>0</sup> |

| inches | 0.180<br>0.165 | 0.020                  | 0.01           |                        |              | 0.032<br>0.026 |                  |                  | 0.05 | 0.630<br>0.590 | 0.630<br>0.590 | 0.695<br>0.685 | 0.695<br>0.685 | 0.048<br>0.042 | 0.020                  | 0.057<br>0.040 | 0.007 | 0.007 | 0.004 | 0.085 | 0.085 |                 |

#### Note

1. Plastic or metal protrusions of 0.01 inches maximum per side are not included.

| OUTLINE  |        | REFER  | RENCES | EUROPEAN   | ISSUE DATE                      |

|----------|--------|--------|--------|------------|---------------------------------|

| VERSION  | IEC    | JEDEC  | EIAJ   | PROJECTION | 1330E DATE                      |

| SOT187-2 | 112E10 | MO-047 |        |            | <del>97-12-16</del><br>99-12-27 |

80C51 8-bit microcontroller family 4 K/8 K OTP/ROM low voltage (2.7 V–5.5 V), low power, high speed (33 MHz), 128/256 B RAM

# 80C51/87C51/80C52/87C52

#### Data sheet status

| Data sheet status         | Product status | Definition [1]                                                                                                                                                                                                                                             |

|---------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective specification   | Development    | This data sheet contains the design target or goal specifications for product development. Specification may change in any manner without notice.                                                                                                          |

| Preliminary specification | Qualification  | This data sheet contains preliminary data, and supplementary data will be published at a later date. Philips Semiconductors reserves the right to make changes at any time without notice in order to improve design and supply the best possible product. |

| Product specification     | Production     | This data sheet contains final specifications. Philips Semiconductors reserves the right to make changes at any time without notice in order to improve design and supply the best possible product.                                                       |

<sup>[1]</sup> Please consult the most recently issued datasheet before initiating or completing a design.

#### **Definitions**

**Short-form specification** — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

**Application information** — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### **Disclaimers**

**Life support** — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

Philips Semiconductors 811 East Arques Avenue P.O. Box 3409 Sunnyvale, California 94088–3409 Telephone 800-234-7381 © Copyright Philips Electronics North America Corporation 2000 All rights reserved. Printed in U.S.A.

Date of release: 08-00

Document order number: 9397 750 07404

Let's make things better.

Philips Semiconductors