Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFl

| Details                    |                                                                                          |

|----------------------------|------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                   |

| Core Processor             | ARM® Cortex®-M0                                                                          |

| Core Size                  | 32-Bit Single-Core                                                                       |

| Speed                      | 32MHz                                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                             |

| Number of I/O              | 40                                                                                       |

| Program Memory Size        | 16KB (16K x 8)                                                                           |

| Program Memory Type        | FLASH                                                                                    |

| EEPROM Size                | -                                                                                        |

| RAM Size                   | 4K x 8                                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                              |

| Data Converters            | A/D 7x12b                                                                                |

| Oscillator Type            | Internal                                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                        |

| Mounting Type              | Surface Mount                                                                            |

| Package / Case             | 48-LQFP                                                                                  |

| Supplier Device Package    | 48-LQFP (7x7)                                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/nano102lb1an |

|                            |                                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **1 GENERAL DESCRIPTION**

The Nano112 series ultra-low-power 32-bit microcontroller embeded with ARM<sup>®</sup> Cortex<sup>™</sup>-M0 core operates at low voltage range from 1.8V to 3.6V and runs up to 32 MHz frequency with 16/32 Kbytes embedded Flash and 4/8 Kbytes embedded SRAM and 4 Kbytes Flash loader memory for In-System Programming (ISP). The Nano112 series integrates 4 COM x 36 SEG or 6 COM x 34 SEG LCD controller, RTC, 12-bit SAR ADC, comparators and provides high performance connectivity peripheral interfaces such as UART, SPI, I<sup>2</sup>C, GPIOs, and ISO-7816-3 for Smart card. The Nano112 series supports Brown-out Detector, Power-down mode with RTC turn on, RAM retention is less than 1.5 uA, Deep power down mode with RAM retention is less than 650 nA and fast wake-up via many peripheral interfaces.

The Nano112 series provides low voltage, low operating power consumption, low standby current, high integration peripherals, high-efficiency operation, fast wake-up function and the lowest cost 32-bit microcontrollers. The Nano112 series is suitable for a wide range of battery device applications such as:

- Wearable Device

- Smart Watch

- Wireless Gaming Control

- Hand-Held Medical Device

- RFID Reader

- Mobile Payment Smart Card Reader

- Security Alarm System

- Smart Home Appliance

- Wireless Thermostats

- Wireless Sensors Node Device (WSND)

- Wireless Auto Meter Reading (AMR)

- Portable Wireless Data Collector

- Smart Water, Gas, Heat Meters

The Nano112 series includes two product lines: Nano102 Base line and Nano112 LCD line.

The Nano102 Base line, an ultra-low-power 32-bit microcontroller embedded with ARM<sup>®</sup> Cortex<sup>™</sup>-M0 core, operates at low voltage range from 1.8V to 3.6V and runs up to 32 MHz frequency with 16/32 Kbytes embedded flash and 4/8 Kbytes embedded SRAM and 4 Kbytes Flash loader memory for In-System Programming (ISP). It integrates RTC, 8- channels 12-bit SAR ADC, 2xComparators and provides high performance connectivity peripheral interfaces such as 2 x Low Power UARTs, 2 x SPIs, 2 x I<sup>2</sup>Cs, GPIOs, and 2 x ISO-7816-3 for Smart card. The Nano102 Base line supports Brown-out Detector, Power-down mode with RAM retention and fast wake-up via many peripheral interfaces.

The Nano112 LCD line, an ultra-low-power 32-bit microcontroller embedded with ARM<sup>®</sup> Cortex<sup>TM</sup>-M0 core, operates at low voltage range from 1.8V to 3.6V and runs up to 32 MHz frequency with 16/32 Kbytes embedded flash and 4/8 Kbytes embedded SRAM and 4 Kbytes Flash loader memory for In-System Programming (ISP). It integrates 4 COM x 36 SEG or 6 COM x 34 SEG LCD controller, RTC, 8-channels 12-bit SAR ADC, 2 x Comparators and provides high performance connectivity peripheral interfaces such as 2 x Low Power UARTs, 2 x SPIs, 2 x I<sup>2</sup>Cs, GPIOs, and 2 x ISO-7816-3 for Smart card. The Nano112 LCD line supports Brown-out Detector, Power-down mode with RAM retention and fast wake-up via many peripheral interfaces.

#### 2 FEATURES

The equipped features are dependent on the product line and their sub products.

#### 2.1 Nano102 Features – Base Line

- Low Supply Voltage Range: 1.8 V to 3.6 V

- Ultra-Low Power Consumption

- Operation mode : 150 uA/MHz

- Power-down mode : 1.5 uA (RTC on, RAM retention)

- Deep power down mode : 650 nA (RAM retention)

- Fast Wake-Up From Standby Mode : Less than 6 μs

- Core

- ◆ ARM<sup>®</sup> Cortex<sup>™</sup>-M0 core running up to 32 MHz

- One 24-bit system timer

- Supports Low Power Sleep mode

- Single-cycle 32-bit hardware multiplier

- NVIC for the 32 interrupt inputs, each with 4-levels of priority

- Serial Wire Debug supports with 2 watchpoints/4 breakpoints

- Flash EPROM Memory

- Runs up to 32 MHz with zero wait state for discontinuous address read access

- 16/32 Kbytes application program memory (APROM)

- 4 KB in system programming (ISP) loader program memory (LDROM)

- Programmable data flash start address and memory size with 512 bytes page erase unit

- In System Program (ISP)/In Application Program (IAP) to update on-chip Flash EPROM

- SRAM Memory

- 4/8 Kbytes embedded SRAM

- Supports DMA mode

- DMA: Supports 5 channels: 4 PDMA channels and one CRC channel

- PDMA

- Peripheral-to-memory, memory-to-peripheral, and memory-to-memory transfer

- Supports word boundary address

- Supports word alignment transfer length in memory-to-memory mode

- Supports word/half-word/byte alignment transfer length in peripheral-tomemory and memory-to-peripheral mode

- Supports word/half-word/byte transfer data width from/to peripheral

- Supports address direction: increment, fixed, and wrap around

- CRC

- Up to two sets of SPI controllers

- Master up to 32 MHz, and Slave up to 16 MHz

- Supports SPI/MICROWIRE Master/Slave mode

- Full duplex synchronous serial data transfer

- Variable length of transfer data from 4 to 32 bits

- MSB or LSB first data transfer

- RX and TX on both rising or falling edge of serial clock independently

- Two slave/device select lines when SPI controller is used as the master, and 1 slave/device select line when SPI controller is used as the slave

- Supports byte suspend mode in 32-bit transmission

- Supports two channel PDMA requests, one for transmit and another for receive

- Supports three wire mode, no slave select signal, bi-direction interface

- Wake system up(SPI clock toggle) from Power-down mode

- I<sup>2</sup>C

- Up to two sets of I<sup>2</sup>C device

- Master/Slave up to 1 Mbit/s

- Bi-directional data transfer between masters and slaves

- Multi-master bus (no central master)

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus

- Serial clock synchronization allows devices with different bit rates to communicate via one serial bus

- Serial clock synchronization used as a handshake mechanism to suspend and resume serial transfer

- Built-in 14-bit time-out counter requesting the I<sup>2</sup>C interrupt if the I<sup>2</sup>C bus hangs up and timer-out counter overflows

- Programmable clocks allowing for versatile rate control

- Supports 7-bit addressing mode

- Supports multiple address recognition (four slave addresses with mask option)

- Wake system up(address match) from Power-down mode

- ADC

- 12-bit SAR ADC up to 1Msps conversion rate

- Up to 8-ch single-ended input from external pin (PA.0 ~ PA.7)

- Four internal channels from internal reference voltage (Int\_V<sub>REF</sub>), Temperature sensor, AV<sub>DD</sub>, and AV<sub>SS</sub>.

- Supports three reference voltage sources from V<sub>REF</sub> pin, internal reference voltage (Int\_V<sub>REF</sub>), and AV<sub>DD</sub>.

- Supports Single Scan, Single Cycle Scan, and Continuous Scan mode

- Each channel with individual result register

- Only scan on enabled channels

- Threshold voltage detection (comparator function)

- Conversion started by software programming or external input

- Supports PDMA mode

- Supports up to four timer time-out events (TMR0, TMR1, TMR2 and TMR3) to enable ADC

- SmartCard (SC)

- Compliant to ISO-7816-3 T=0, T=1

- Supports up to two ISO-7816-3 ports

- Separates receive/transmit 4 bytes entry FIFO for data payloads

- Programmable transmission clock frequency

- Programmable receiver buffer trigger level

- Programmable guard time selection (11 ETU ~ 267 ETU)

- A 24-bit and two 8-bit time-out counters for Answer to Request (ATR) and waiting times processing

- Supports auto inverse convention function

- Supports transmitter and receiver error retry and error limit function

- Supports hardware activation sequence process

- Supports hardware warm reset sequence process

- Supports hardware deactivation sequence process

- Supports hardware auto deactivation sequence when detect the card is removal

- Supports UART mode (full-duplex)

- ACMP

- Supports up to 2 analog comparators

- Analog input voltage range: 0 ~ AV<sub>DD</sub>

- Supports Hysteresis function

- Two analog comparators with optional internal reference voltage input at negative end

- Wake-up source

- Support RTC, WDT, I<sup>2</sup>C, Timer, UART, SPI, BOD, GPIO

- One built-in temperature sensor with 1 °C resolution

- Brown-out

- Built-in 2.5V/2.0V/1.7V BOD for wide operating voltage range operation

- 96-bit unique ID

- 128-bit unique customer ID

- Operating Temperature: -40°C~85°C

- Packages:

- All Green package (RoHS)

- LQFP 64-pin(7x7) / 48-pin(7x7) / QFN33-pin(5x5)

- Variable length of transfer data from 4 to 32 bits

- MSB or LSB first data transfer

- RX and TX on both rising or falling edge of serial clock independently

- Two slave/device select lines when SPI controller is as the master, and 1 slave/device select line when SPI controller is as the slave

- Supports byte suspend mode in 32-bit transmission

- Supports two channel PDMA requests, one for transmit and another for receive

- Supports three wire mode, no slave select signal, bi-direction interface

- Wake system up (SPI clock toggle) from Power-down mode

- I<sup>2</sup>C

- Up to two sets of I<sup>2</sup>C devices

- Master/Slave up to 1Mbit/s

- Bidirectional data transfer between masters and slaves

- Multi-master bus (no central master)

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus

- Serial clock synchronization allowing devices with different bit rates to communicate via one serial bus

- Serial clock synchronization used as a handshake mechanism to suspend and resume serial transfer

- Built-in 14-bit time-out counter requestING the I<sup>2</sup>C interrupt if the I<sup>2</sup>C bus hangs up and timer-out counter overflows

- Programmable clocks allow versatile rate control

- Supports 7-bit addressing mode

- Supports multiple address recognition (four slave address with mask option)

- Wake system up (address match) from Power-down mode

- ADC

- 12-bit SAR ADC up to 1Msps conversion rate

- Up to 7-ch single-ended input from external pin (PA.0 ~ PA.6)

- Four internal channels from internal reference voltage (Int\_V<sub>REF</sub>), Temperature sensor, AV<sub>DD</sub>, and AV<sub>SS</sub>

- Supports three reference voltage sources from V<sub>REF</sub> pin, internal reference voltage (Int\_V<sub>REF</sub>), and AV<sub>DD</sub>.

- Single scan/single cycle scan/continuous scan

- Each channel with individual result register

- Only scan on enabled channels

- Threshold voltage detection (comparator function)

- Conversion start by software programming or external input

- Supports PDMA mode

- Supports up to four timer time-out events (TMR0, TMR1, TMR2, and TMR3) to

Page **18** of 100

### **3 ABBREVIATIONS**

| Acronym | Description                                     |

|---------|-------------------------------------------------|

| ACMP    | Analog Comparator Controller                    |

| ADC     | Analog-to-Digital Converter                     |

| AES     | Advanced Encryption Standard                    |

| АРВ     | Advanced Peripheral Bus                         |

| АНВ     | Advanced High-Performance Bus                   |

| BOD     | Brown-out Detection                             |

| CAN     | Controller Area Network                         |

| DAP     | Debug Access Port                               |

| DES     | Data Encryption Standard                        |

| EBI     | External Bus Interface                          |

| EPWM    | Enhanced Pulse Width Modulation                 |

| FIFO    | First In, First Out                             |

| FMC     | Flash Memory Controller                         |

| FPU     | Floating-point Unit                             |

| GPIO    | General-Purpose Input/Output                    |

| HCLK    | The Clock of Advanced High-Performance Bus      |

| HIRC    | 12/16 MHz Internal High Speed RC Oscillator     |

| НХТ     | 4~24 MHz External High Speed Crystal Oscillator |

| IAP     | In Application Programming                      |

| ICP     | In Circuit Programming                          |

| ISP     | In System Programming                           |

| LDO     | Low Dropout Regulator                           |

| LIN     | Local Interconnect Network                      |

| LIRC    | 10 kHz internal low speed RC oscillator (LIRC)  |

| MPU     | Memory Protection Unit                          |

| NTC     | Negative Temperature Coefficient                |

| NVIC    | Nested Vectored Interrupt Controller            |

| PCLK    | The Clock of Advanced Peripheral Bus            |

| PDMA    | Peripheral Direct Memory Access                 |

| PLL     | Phase-Locked Loop                               |

| PTC     | Positive Temperature Coefficient                |

| PT1000  | Thermal Resistance                              |

| PWM     | Pulse Width Modulation                          |

### 4.2.2 NuMicro<sup>™</sup> Nano112 LCD Line Selection Guide

|                                                 |       |      | Data         | ISP |          | Timer    | C    | onnectivi | ty |      | PWM      | ADC |     | IRC<br>10KHz/ |      |            | ISO-   | ISP | <b>.</b> . | Maximum                      |

|-------------------------------------------------|-------|------|--------------|-----|----------|----------|------|-----------|----|------|----------|-----|-----|---------------|------|------------|--------|-----|------------|------------------------------|

| Part No.                                        | Flash | SRAM | Flash        | ROM | VO       | (32-bit) | UART | SPI       | ŕc | Comp | (16-bit) |     | RTC | 12MHz/        | PDMA | LCD        | 7816-3 | ЮР  | Package    | Operating Tem<br>Range (°C ) |

| NANO112LB1AN                                    | 16K   | 4K   | Configurable | 4K  | up to 40 | 4        | 4    | 2         | 2  | 2    | 4        | 7   | V   | 1             | 4    | 4x20, 6x18 | 2      | V   | LQFP48     | -40 to +85                   |

| NANO112LC2AN                                    | 32K   | 8K   | Configurable | 4K  | up to 40 | 4        | 4    | 2         | 2  | 2    | 4        | 7   | 1   | 1             | 4    | 4x20, 6x18 | 2      | V   | LQFP48     | -40 to +85                   |

| NANO112SB1AN                                    | 16K   | 4K   | Configurable | 4K  | up to 58 | 4        | 4    | 2         | 2  | 2    | 4        | 7   | V   | V             | 4    | 4x32, 6x30 | 2      | V   | LQFP64     | -40 to +85                   |

| NANO112SC2AN                                    | 32K   | 8K   | Configurable | 4K  | up to 58 | 4        | 4    | 2         | 2  | 2    | 4        | 7   | V   | 1             | 4    | 4x32, 6x30 | 2      | V   | LQFP64     | -40 to +85                   |

| NANO112RB1AN                                    | 16K   | 4K   | Configurable | 4K  | up to 58 | 4        | 4    | 2         | 2  | 2    | 4        | 7   | 1   | 1             | 4    | 4x32, 6x30 | 2      | V   | LQFP64*    | -40 to +85                   |

| NANO112RC2AN                                    | 32K   | 8K   | Configurable | 4K  | up to 58 | 4        | 4    | 2         | 2  | 2    | 4        | 7   | V   | 1             | 4    | 4x32, 6x30 | 2      | V   | LQFP64*    | -40 to +85                   |

| NANO112VC2AN                                    | 32K   | 8K   | Configurable | 4K  | up to 80 | 4        | 4    | 2         | 2  | 2    | 4        | 8   | V   | 1             | 4    | 4x36, 6x34 | 2      | V   | LQFP100    | -40 to +85                   |

| QFP48: 7x7mm<br>QFP64: 7x7mm<br>QFP64*: 10x10mm |       |      |              |     |          |          |      |           |    |      |          |     |     |               |      |            | - 20   |     |            |                              |

|                                                 |       |      |              |     |          |          |      |           |    |      |          |     |     |               |      |            |        |     |            |                              |

### 4.4 Pin Description

#### 4.4.1 NuMicro<sup>™</sup> Nano102 Pin Description

| Pin No. |        |        | Din Nome   | Din Ture | Description                                                                             |  |  |  |

|---------|--------|--------|------------|----------|-----------------------------------------------------------------------------------------|--|--|--|

| 64-pin  | 48-pin | 32-pin | Pin Name   | Pin Type | Description                                                                             |  |  |  |

|         |        |        | PB.10      | I/O      | General purpose digital I/O pin                                                         |  |  |  |

| 1       |        |        | UART1_RXD  | I        | UART1 Data receiver input pin                                                           |  |  |  |

|         |        |        | SPI0_MOSI1 | I/O      | SPI0 2 <sup>nd</sup> MOSI (Master Out, Slave In) pin                                    |  |  |  |

|         |        |        | PB.11      | I/O      | General purpose digital I/O pin                                                         |  |  |  |

|         |        |        | UART1_RTSn | 0        | UART1 Request to Send output pin                                                        |  |  |  |

| 2       |        |        | SPI0_MISO1 | I/O      | SPI0 2 <sup>rd</sup> MISO (Master In, Slave Out)<br>pin                                 |  |  |  |

|         |        |        | TM1        | I/O      | Timer1 external counter input or<br>Timer1 toggle out                                   |  |  |  |

|         |        |        | PB.12      | I/O      | General purpose digital I/O pin                                                         |  |  |  |

|         |        |        | UART0_RTSn | 0        | UART0 Request to Send output pin                                                        |  |  |  |

| 3       | 1      | 1      | SPI0_MOSI0 | I/O      | SPI0 1 <sup>st</sup> MOSI (Master Out, Slave In)<br>pin                                 |  |  |  |

|         |        |        | тмо        | I/O      | Timer0 external counter input or<br>Timer0 toggle out.                                  |  |  |  |

|         |        |        | FCLK0      | 0        | Frequency Divider0 output pin                                                           |  |  |  |

|         |        |        | PB.13      | I/O      | General purpose digital I/O pin                                                         |  |  |  |

| 4       | 2      | 2      | UART0_RXD  | I        | UART0 Data receiver input pin                                                           |  |  |  |

|         |        |        | SPI0_MISO0 | I/O      | SPI0 1 <sup>st</sup> MISO (Master In, Slave Out)<br>pin                                 |  |  |  |

|         |        |        | PB.14      | I/O      | General purpose digital I/O pin                                                         |  |  |  |

| 5       | 3      | 3      | UART0_TXD  | o        | UART0 Data transmitter output pin<br>(This pin could be modulated with<br>PWM0 output.) |  |  |  |

|         |        |        | SPI0_CLK   | I/O      | SPI0 serial clock pin                                                                   |  |  |  |

|         |        |        | PB.15      | I/O      | General purpose digital I/O pin                                                         |  |  |  |

| 6       | 4      | 4      | UART0_CTSn | I        | UART0 Clear to Send input pin                                                           |  |  |  |

|         |        |        | SPI0_SS0   | I/O      | SPI0 1 <sup>st</sup> slave select pin                                                   |  |  |  |

|         |        |        | PC.0       | I/O      | General purpose digital I/O pin                                                         |  |  |  |

| 7       | E      |        | SPI0_SS1   | I/O      | SPI0 2 <sup>nd</sup> slave select pin                                                   |  |  |  |

| '       | 5      |        | I2C0_SCL   | I/O      | I <sup>2</sup> C0 clock pin                                                             |  |  |  |

|         |        |        | PWM0_CH0   | I/O      | PWM0 Channel0 output                                                                    |  |  |  |

| 8       | 6      |        | PC.1       | I/O      | General purpose digital I/O pin                                                         |  |  |  |

| U       | 0      |        | I2C0_SDA   | I/O      | I <sup>2</sup> C0 data I/O pin                                                          |  |  |  |

| Pin No. |          |           | Pin Name        | Pin Type                        | Description                                                                           |

|---------|----------|-----------|-----------------|---------------------------------|---------------------------------------------------------------------------------------|

| 100-pin | 64-pin   | 48-pin    |                 | ТШТурс                          | Description                                                                           |

|         |          |           | LCD_SEG12       | 0                               | LCD segment output 12 at 64-pin                                                       |

|         |          |           | LCD_SEG5        | 0                               | LCD segment output 5 at 48-pin                                                        |

|         |          |           | UART1_RTSn      | 0                               | UART1 Request to Send output pin                                                      |

|         |          |           | SC0_DAT         | I/O                             | SmartCard0 DATA pin<br>(SC0_UART_RXD)                                                 |

|         |          |           | PC.7            | I/O                             | General purpose digital I/O pin                                                       |

|         |          |           | LCD_SEG15       | 0                               | LCD segment output 15 at 100-pin                                                      |

|         | 20 14 12 | LCD_SEG11 | 0               | LCD segment output 11 at 64-pin |                                                                                       |

| 20      |          | LCD_SEG4  | 0               | LCD segment output 4 at 48-pin  |                                                                                       |

|         |          | UART1_RXD | I               | UART1 Data receiver input pin   |                                                                                       |

|         |          |           | SC0_PWR         | 0                               | SmartCard0 Power pin                                                                  |

|         |          |           | PC.8            | I/O                             | General purpose digital I/O pin                                                       |

|         |          |           | LCD_SEG14       | 0                               | LCD segment output 14 at 100-pin                                                      |

| 21 15   |          | LCD_SEG10 | 0               | LCD segment output 10 at 64-pin |                                                                                       |

|         | 15       | 13        | LCD_SEG3        | 0                               | LCD segment output 3 at 48-pin                                                        |

|         |          |           | UART1_TXD       | o                               | UART1 Data transmitter output pin (Th<br>pin could be modulated with PWM0<br>output.) |

|         |          |           | SC0_RST         | 0                               | SmartCard0 RST pin                                                                    |

|         |          |           | PC.9            | I/O                             | General purpose digital I/O pin                                                       |

| 00      |          | 14        | LCD_SEG13       | 0                               | LCD segment output 13 at 100-pin                                                      |

| 22      | 16       |           | LCD_SEG9        | 0                               | LCD segment output 9 at 64-pin                                                        |

|         |          |           | LCD_SEG2        | 0                               | LCD segment output 2 at 48-pin                                                        |

| 23      |          |           | V <sub>DD</sub> | Р                               | Power supply for I/O ports and LDO source                                             |

| 24      |          |           | V <sub>SS</sub> | G                               | Ground for digital circuit                                                            |

| 25      |          |           | V <sub>SS</sub> | G                               | Ground for digital circuit                                                            |

|         |          |           | PC.10           | I/O                             | General purpose digital I/O pin                                                       |

| 26      |          |           | LCD_SEG12       | 0                               | LCD segment output 12 at 100-pin                                                      |

| 20      |          |           | I2C1_SCL        | I/O                             | I <sup>2</sup> C1 clock pin                                                           |

|         |          |           | SC1_CD          | I                               | SmartCard1 card detect pin                                                            |

|         |          |           | PC.11           | I/O                             | General purpose digital I/O pin                                                       |

| 07      |          |           | LCD_SEG11       | 0                               | LCD segment output 11 at 100-pin                                                      |

| 27      |          |           | I2C1_SDA        | I/O                             | I <sup>2</sup> C 1 data I/O pin                                                       |

|         |          | 1         | SC1_PWR         | 0                               | SmartCard1 PWR pin                                                                    |

| Pin No. |          |        |             |          |                                                                                         |

|---------|----------|--------|-------------|----------|-----------------------------------------------------------------------------------------|

| 100-pin | 64-pin   | 48-pin | -Pin Name   | Pin Type | Description                                                                             |

|         |          |        | PA.8        | I/O      | General purpose digital I/O pin                                                         |

| 84      |          |        | SC0_PWR     | 0        | SmartCard0 Power pin                                                                    |

|         |          |        | PA.9        | I/O      | General purpose digital I/O pin                                                         |

| 85      |          |        | SC0_RST     | 0        | SmartCard0 RST pin                                                                      |

|         |          |        | PA.10       | I/O      | General purpose digital I/O pin                                                         |

| 86      |          |        | SC0_CLK     | 0        | SmartCard0 clock pin<br>(SC0_UART_TXD)                                                  |

|         |          |        | PA.11       | I/O      | General purpose digital I/O pin                                                         |

| 87      |          |        | SC0_DAT     | I/O      | SmartCard0 DATA<br>pin(SC0_UART_RXD)                                                    |

|         |          |        | STADC       | I        | ADC external trigger input.                                                             |

|         |          |        | PA.12       | I/O      | General purpose digital I/O pin                                                         |

|         |          |        | LCD_SEG19   | 0        | LCD segment output 19 at 48-pin                                                         |

| 88      | 88 56 45 | 45     | UART0_TXD   | o        | UART0 Data transmitter output pin (This<br>pin could be modulated with PWM0<br>output.) |

|         |          |        | SPI1_MOSI0  | I/O      | SPI1 1 <sup>st</sup> MOSI (Master Out, Slave In) pir                                    |

|         |          |        | I2C0_SCL    | I/O      | I <sup>2</sup> C 0 clock pin                                                            |

|         |          |        | ACMP1_P     | AI       | Comparator1 P-end input                                                                 |

|         |          |        | PA.13       | I/O      | General purpose digital I/O pin                                                         |

|         |          |        | LCD_SEG18   | 0        | LCD segment output 18 at 48-pin                                                         |

|         | -7       | 40     | UART0_RXD   | I        | UART0 Data receiver input pin                                                           |

| 89      | 57       | 46     | SPI1_MISO0  | I/O      | SPI1 1 <sup>st</sup> MISO (Master In, Slave Out) pir                                    |

|         |          |        | I2C0_SDA    | I/O      | I <sup>2</sup> C0 data I/O pin                                                          |

|         |          |        | ACMP1_N     | AI       | Comparator1 N-end input                                                                 |

|         |          |        | PA.14       | I/O      | General purpose digital I/O pin                                                         |

|         |          |        | ACMP0_CHDIS | 0        | Comparator0 charge/discharge path                                                       |

| 00      | 50       | 47     | LCD_SEG31   | 0        | LCD segment output 31 at 64-pin                                                         |

| 90      | 58       | 47     | LCD_SEG17   | 0        | LCD segment output 17 at 48-pin                                                         |

|         |          |        | SPI1_CLK    | I/O      | SPI1 serial clock pin                                                                   |

|         |          |        | I2C1_SCL    | I/O      | I <sup>2</sup> C1 clock pin                                                             |

|         |          |        | PA.15       | I/O      | General purpose digital I/O pin                                                         |

| 01      | 50       | 40     | LCD_SEG30   | 0        | LCD segment output 30 at 64-pin                                                         |

| 91      | 59       | 48     | LCD_SEG16   | 0        | LCD segment output 16 at 48-pin                                                         |

|         |          |        | SPI1_SS0    | I/O      | SPI1 1 <sup>st</sup> slave select pin                                                   |

| Pin No. |        |           | Pin Name        | Pin Type                                                                                | Description                                          |

|---------|--------|-----------|-----------------|-----------------------------------------------------------------------------------------|------------------------------------------------------|

| 100-pin | 64-pin | 48-pin    |                 | Pin Type                                                                                | Description                                          |

|         |        |           | I2C1_SDA        | I/O                                                                                     | I <sup>2</sup> C1 data I/O pin                       |

|         |        |           | ACMP1_OUT       | 0                                                                                       | Comparator1 output                                   |

|         |        |           | TC3             | I                                                                                       | Timer3 capture input                                 |

|         |        |           | PB.0            | I/O                                                                                     | General purpose digital I/O pin                      |

|         |        |           | LCD_SEG29       | 0                                                                                       | LCD segment output 29 at 64-pin                      |

| 92      | 92 60  | UART0_TXD | ο               | UART0 Data transmitter output pin (This<br>pin could be modulated with PWM0<br>output.) |                                                      |

|         |        |           | FCLK1           | 0                                                                                       | Frequency Divider1 output pin                        |

|         |        |           | PB.1            | I/O                                                                                     | General purpose digital I/O pin                      |

|         |        |           | LCD_SEG28       | 0                                                                                       | LCD segment output 28 at 64-pin                      |

| 93      | 61     |           | UART0_RXD       | I                                                                                       | UART0 Data receiver input pin                        |

|         |        |           | TC2             | I                                                                                       | Timer 2 capture input                                |

|         |        |           | INT1            | I                                                                                       | External interrupt1 input pin                        |

|         |        |           | PB.2            | I/O                                                                                     | General purpose digital I/O pin                      |

|         |        |           | LCD_SEG27       | 0                                                                                       | LCD segment output 27 at 64-pin                      |

|         |        |           | UART0_RTSn      | 0                                                                                       | UART0 Request to Send output pin                     |

| 94      | 62     |           | SPI1_MOSI1      | I/O                                                                                     | SPI1 2 <sup>nd</sup> MOSI (Master Out, Slave In) pin |

|         |        |           | I2C0_SCL        | 0                                                                                       | I <sup>2</sup> C0 clock pin                          |

|         |        |           | TM3             | I/O                                                                                     | Timer3 external counter input or Timer3 toggle out.  |

|         |        |           | PB.3            | I/O                                                                                     | General purpose digital I/O pin                      |

|         |        |           | LCD_SEG26       | 0                                                                                       | LCD segment output 26 at 64-pin                      |

|         |        |           | UART0_CTSn      | I                                                                                       | UART0 Clear to Send input pin                        |

| 95      | 63     |           | SPI1_MISO1      | I/O                                                                                     | SPI1 2 <sup>nd</sup> MISO (Master In, Slave Out) pin |

|         |        |           | I2C0_SDA        | I/O                                                                                     | I <sup>2</sup> C0 data I/O pin                       |

|         |        |           | TM2             | I/O                                                                                     | Timer2 external counter input or Timer2 toggle out.  |

| 96      |        |           | V <sub>DD</sub> | Р                                                                                       | Power supply for I/O ports and LDO source            |

| 97      |        |           | V <sub>SS</sub> | G                                                                                       | Ground for digital circuit                           |

|         |        |           | PB.4            | I/O                                                                                     | General purpose digital I/O pin                      |

| 98      |        |           | UART1_RTSn      | 0                                                                                       | UART1 Request to Send output pin                     |

|         |        |           | SPI1_MISO1      | I/O                                                                                     | SPI1 2 <sup>nd</sup> MISO (Master In, Slave Out) pin |

| 99      |        |           | PB.5            | I/O                                                                                     | General purpose digital I/O pin                      |

| 33      |        |           | LCD_SEG35       | 0                                                                                       | LCD segment output 35 at 100-pin                     |

- NVIC:

- 32 external interrupt inputs, each with four levels of priority

- Dedicated Non-maskable Interrupt (NMI) input

- Supports for both level-sensitive and pulse-sensitive interrupt lines

- Supports Wake-up Interrupt Controller (WIC) and, providing Ultra-low Power Sleep mode

- Debug support:

- Four hardware breakpoints

- Two watchpoints

- Program Counter Sampling Register (PCSR) for non-intrusive code profiling

- Single step and vector catch capabilities

- Bus interfaces:

- Single 32-bit AMBA-3 AHB-Lite system interface that provides simple integration to all system peripherals and memory

- Single 32-bit slave port that supports the DAP (Debug Access Port)

#### 6.5 Clock Controller

#### 6.5.1 Overview

The clock controller generates clocks for the whole chip, lincluding system clocks (CPU clock, HCLKx, and PCLKx) and all peripheral module clocks. HCLKx means AHB bus clock for peripherals on AHB bus. PCLKx means APB bus clock for peripherals on APB bus. PCLKx can be the same as HCLKx or devided from HCLKx. The clock controller also implements the power control function with the individually clock ON/OFF control, clock source selection and a 4-bit clock divider. The chip will not enter power-down mode until CPU sets the power down enable bit PD\_EN(PWRCTL[6]) and executes the WFI instruction. In the Power-down mode, clock controller turns off the external high frequency crystal, internal high frequency oscillator, and system clocks (CPU clock, HCLKx, and PCLKx) to reduce the power consumption.

The clock controller consists of 5 sources as listed below:

- 32768Hz external low speed crystal oscillator (LXT)

- 4~ 24 MHz external high speed crystal oscillator (HXT)

- 12/16 MHz internal high speed RC oscillator (HIRC)

- One programmable PLL FOUT (PLL source can be selected from HXT or HIRC)

- 10 kHz internal low speed RC oscillator (LIRC)

#### 6.5.2 Features

- Generates clocks for system clocks and all peripheral module clocks.

- Each peripheral module clock can be turned on/off.

- High frequency crystal, internal high frequency oscillator, and system clocks will be turned off when chip is in Power-down mode.

#### 6.10.2 Features

6.10.2.1 PWM Function:

- PWM controllers has 4 independent PWM outputs, CH0~CH3, or as 2 complementary PWM pairs, (CH0, CH1), (CH2, CH3) with 2 programmable dead-zone generators

- Up to 4 PWM channels or 2 PWM paired channels

- Up to 16 bits PWM counter width

- PWM Interrupt request synchronous with PWM period

- Single-shot or Continuous mode

- Two Dead-Zone generators

#### 6.10.2.2 Capture Function:

- Timing control logic shared with PWM timer.

- 4 Capture input channels shared with 4 PWM output channels.

- Each channel supports one rising latch register CRL (PWM\_CRL0[15:0]), one falling latch register CFL (PWM\_CFL0[15:0]) and Capture interrupt flag CAPIF0 (PWM\_CAPINTSTS[0]).

- Four 16-bit counters for four capture channels or two 32-bit counter for two capture channels when cascade is enabled: when CH01CASKEN (PWM\_CAPCTL[13]) is set, the original 16-bit counter of channel 1 will combine with channel 0's 16 bit counter for channel 0 input capture counting and so does CH23CASKEN(PWM\_CAPCTL[29]) for channel 2, 3

- Supports PDMA transfer function for PWM channel 0, 2

- Supports multiple address recognition (Two slave addresses with mask option)

- Supports Power-down wake-up function

- Supports two-Level FIFO

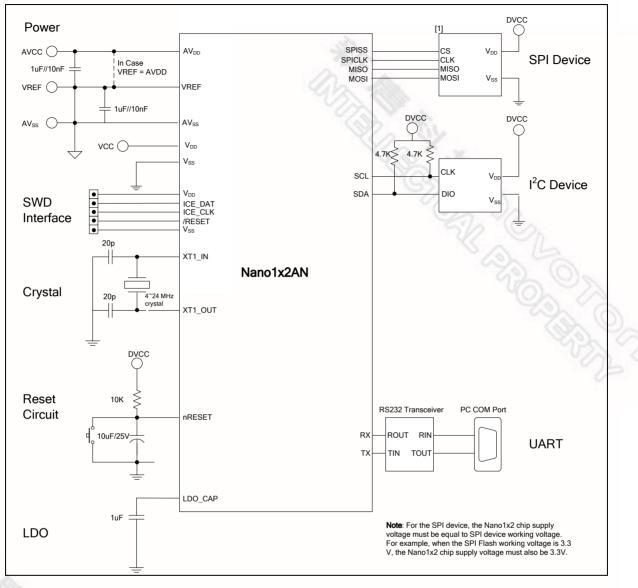

### 7 APPLICATION CIRCUIT

#### 9.2 Nano102/Nano112 DC Electrical Characteristics

(VDD-VSS=3.3V, TA = 25°C, FOSC = 32 MHz unless otherwise specified.)

| PARAMETER                              | SYM.                                | SI   | PECIFIC         | CATION | S    |                                    | TES                              |          |           | IC                 |  |

|----------------------------------------|-------------------------------------|------|-----------------|--------|------|------------------------------------|----------------------------------|----------|-----------|--------------------|--|

|                                        | 5 T WI.                             | MIN. | TYP.            | MAX.   | UNIT |                                    |                                  |          |           | 10                 |  |

| Operation voltage                      | V <sub>DD</sub>                     | 1.8  | -               | 3.6    | v    | V <sub>DD</sub> =1.8V up to 32 MHz |                                  |          |           |                    |  |

| Power Ground                           | V <sub>SS</sub><br>AV <sub>SS</sub> | -0.3 | -               |        | v    | 0                                  | XX                               | N.       |           |                    |  |

|                                        | V <sub>LDO1</sub>                   | 1.62 | 1.8             | 1.98   | V    | мси                                | operatin                         | g in Rui | n or Idle | mode               |  |

|                                        | V LDO1                              | 1.44 | 1.6             | 1.76   | V    | Set L                              | DO_LEV                           | EL(LDC   | D_CTL[3   | :2]) = 0x1         |  |

| LDO Output Voltage                     | V <sub>LDO2</sub>                   | 1.49 | 1.66            | 1.83   | V    | мси                                | MCU operating in Power-down mode |          |           |                    |  |

|                                        | C <sub>LDO</sub>                    |      | 1               |        | uF   | Conn                               | Connect to LDO_CAP pin           |          |           |                    |  |

| Analog Operating<br>Voltage            | AV <sub>DD</sub>                    |      | V <sub>DD</sub> |        | V    |                                    |                                  |          |           | Ų                  |  |

| Operating Current                      | I <sub>DD5</sub>                    |      | 11.7            |        | mA   | V <sub>DD</sub>                    | НХТ                              | HIRC     | PLL       | All digital module |  |

| Normal Run Mode                        |                                     |      |                 |        |      | 3.3 V                              | 12 MHz                           | Х        | V         | V                  |  |

| HCLK =32 MHz<br>wkhile(1){}executed    | I <sub>DD6</sub>                    |      | 5.8             |        | mA   | 3.3 V                              | 12 MHz                           | х        | V         | х                  |  |

| from flash<br>V <sub>LDO1</sub> =1.8 V | I <sub>DD7</sub>                    |      | 10.9            |        | mA   | 1.8 V                              | 12 MHz                           | х        | V         | V                  |  |

|                                        | I <sub>DD8</sub>                    |      | 5.6             |        | mA   | 1.8 V                              | 12 MHz                           | х        | V         | х                  |  |

| Operating Current                      | I <sub>DD9</sub>                    |      | 3.9             |        | mA   | 3.3 V                              | 12 MHz                           | х        | х         | V                  |  |

| Normal Run Mode<br>HCLK =32 MHz        | I <sub>DD10</sub>                   |      | 1.9             |        | mA   | 3.3 V                              | 12 MHz                           | х        | х         | х                  |  |

| while(1){}executed<br>from flash       | I <sub>DD11</sub>                   |      | 3.8             |        | mA   | 1.8 V                              | 12 MHz                           | х        | х         | V                  |  |

| V <sub>LDO1</sub> =1.6 V               | I <sub>DD12</sub>                   |      | 1.9             |        | mA   | 1.8 V                              | 12 MHz                           |          |           |                    |  |

#### 9.3.4 Internal 12 MHz Oscillator

| PARAMETER                                   | SYM.               | S     | PECIFI | CATION                                                             | IS   | TEST CONDITION                     |

|---------------------------------------------|--------------------|-------|--------|--------------------------------------------------------------------|------|------------------------------------|

|                                             | 511.               |       |        | MAX.                                                               | UNIT | TEST CONDITION                     |

| Supply voltage[1]                           | V <sub>HRC</sub>   |       | 1.8    | The                                                                | V    |                                    |

|                                             |                    | 11.88 | 12     | 12.12                                                              | MHz  | 25°C, VDD = 3.3V                   |

|                                             | F <sub>HRC</sub>   | 11.76 | 12     | 12.24                                                              | MHz  | -40°C ~ +85°C,<br>VDD = 1.8V~3.6V  |

| Calibrated Internal<br>Oscillator Frequency |                    |       |        |                                                                    |      | -40°C ~ +85 °C,<br>VDD = 1.8V~3.6V |

|                                             | 11.88 12 12.12 MHz |       | MHz    | Enable 32.768K crystal<br>oscillator and set<br>TRIM_SEL[1:0]="10" |      |                                    |

| Operating current                           | I <sub>HRC</sub>   |       | 250    |                                                                    | μA   | 76,00                              |

Note: Internal oscillator operation voltage comes from LDO.

#### 9.3.5 Internal 10 kHz Oscillator

| PARAMETER         | SYM.             | S    | PECIFI |      | IS   | TEST CONDITION                    |

|-------------------|------------------|------|--------|------|------|-----------------------------------|

|                   | <b>0</b> m.      | MIN. | TYP.   | MAX. | UNIT |                                   |

| Supply voltage[1] | $V_{LRC}$        |      | 1.8    |      | V    |                                   |

|                   |                  | 7    | 10     | 13   | kHz  | 25°C, VDD = 3V                    |

| Center Frequency  | F <sub>LRC</sub> | 5    | 10     | 15   | kHz  | -40°C ~+85 °C,<br>VDD = 1.8V~3.6V |

| Operating current | I <sub>LRC</sub> |      | 0.3    |      | μΑ   | VDD = 3V                          |

Note: Internal oscillator operation voltage comes from LDO.

### 9.4 Analog Characteristics

#### 9.4.1 12-bit ADC

| PARAMETER                                                                      | SYM.               | SF   | PECIFIC | ATIONS | 6    | TEST CONDITION                                                                      |  |

|--------------------------------------------------------------------------------|--------------------|------|---------|--------|------|-------------------------------------------------------------------------------------|--|

|                                                                                | 011.               | MIN. | TYP.    | MAX.   | UNIT |                                                                                     |  |

| Operating voltage                                                              | AV <sub>DD</sub>   | 1.8  |         | 3.6    | V    | $AV_{DD} = V_{DD}$                                                                  |  |

| Operating current (AV <sub>DD</sub><br>current)<br>(Enable ADC and disable all | I <sub>ADC32</sub> |      | 120     |        | μΑ   | $AV_{DD} = V_{DD} = 3.0V$<br>ADC_VREF = AV <sub>DD</sub><br>ADC Clock Rate = 32 MHz |  |

## nuvoTon

| PARAMETER                      | SYM.              | SF   | PECIFIC   | ATIONS           | S     | TEST CONDITION                                                              |

|--------------------------------|-------------------|------|-----------|------------------|-------|-----------------------------------------------------------------------------|

| FARAWETER                      | 5111.             | MIN. | TYP.      | MAX.             | UNIT  |                                                                             |

| other analog modules)          | I <sub>ADC2</sub> |      | 30        | ある               | μA    | $AV_{DD} = V_{DD} = 3.0V$<br>ADC_VREF = $AV_{DD}$<br>ADC Clock Rate = 2 MHz |

| Resolution                     | R <sub>ADC</sub>  |      |           | 12               | Bit   | -3-                                                                         |

| Reference voltage              | $V_{REF}$         | 1.8  |           | A <sub>VDD</sub> | V     | NY IN                                                                       |

| Reference input current (Avg.) | I <sub>REF</sub>  |      |           | 1                | μA    | 6 8 8                                                                       |

| ADC input voltage              | V <sub>IN</sub>   | 0    |           | V <sub>REF</sub> | V     | STA STA                                                                     |

| Conversion time                | T <sub>CONV</sub> | 1    |           |                  | μS    |                                                                             |

| Conversion Rate                | F <sub>SPS</sub>  |      |           | 1.5M             | Hz    | V <sub>DD</sub> = 3V                                                        |

| Integral Non-Linearity Error   | INL               |      | ±1        |                  | LSB   | V <sub>REF</sub> is external Vref pin                                       |

| Differential Non-Linearity     | DNL               |      | ±0.8      |                  | LSB   | V <sub>REF</sub> is external Vref pin                                       |

| Gain error                     | E <sub>G</sub>    |      | ±2        |                  | LSB   | V <sub>REF</sub> is external Vref pin                                       |

| Offset error                   | EOFFSET           |      | ±1.5      |                  | LSB   | V <sub>REF</sub> is external Vref pin                                       |

| Absolute error                 | E <sub>ABS</sub>  |      | -         | ±6               | LSB   | V <sub>REF</sub> is external Vref pin                                       |

| ADC Clock frequency            | F <sub>ADC</sub>  | 0.25 |           | 32               | MHz   |                                                                             |

| Clock cycle                    | AD <sub>CYC</sub> | 20   |           |                  | Cycle |                                                                             |

| Internal Capacitance           | C <sub>IN</sub>   | -    | 5         | -                | pF    |                                                                             |

| Monotonic                      | -                 | G    | Guarantee | ed               | -     |                                                                             |

#### 9.4.2 Brown-out Detector

| Symbol           | Parameter                | Min | Тур | Мах | Unit | Test Condition |

|------------------|--------------------------|-----|-----|-----|------|----------------|

| AV <sub>DD</sub> | Supply Voltage           | 0   | -   | 3.6 | V    | -              |

| TA               | Temperature              | -40 | 25  | 85  | °C   | -              |

| I <sub>BOD</sub> | Quiescent Current        | -   | 1   |     | μA   | $AV_{DD} = 3V$ |

| V <sub>BOD</sub> | Brown-out Voltage<br>25℃ | 2.4 | 2.5 | 2.6 | V    | BODCTL[2] = 1  |

|                  |                          | 1.9 | 2.0 | 2.1 | V    | BODCTL[1] = 1  |

|                  |                          | 1.6 | 1.7 | 1.8 | V    | BODCTL[0] = 1  |

#### **Important Notice**

Nuvoton Products are neither intended nor warranted for usage in systems or equipment, any malfunction or failure of which may cause loss of human life, bodily injury or severe property damage. Such applications are deemed, "Insecure Usage".

Insecure usage includes, but is not limited to: equipment for surgical implementation, atomic energy control instruments, airplane or spaceship instruments, the control or operation of dynamic, brake or safety systems designed for vehicular use, traffic signal instruments, all types of safety devices, and other applications intended to support or sustain life.

All Insecure Usage shall be made at customer's risk, and in the event that third parties lay claims to Nuvoton as a result of customer's Insecure Usage, customer shall indemnify the damages and liabilities thus incurred by Nuvoton.

Please note that all data and specifications are subject to change without notice. All the trademarks of products and companies mentioned in this datasheet belong to their respective owners.