Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

ENSE

| Details                    |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status A           | Active                                                       |

| Core Processor A           | ARM® Cortex®-M0                                              |

| Core Size 3                | 32-Bit Single-Core                                           |

| Speed 3                    | 32MHz                                                        |

| Connectivity               | <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART     |

| Peripherals E              | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT |

| Number of I/O              | 40                                                           |

| Program Memory Size        | 32KB (32K x 8)                                               |

| Program Memory Type F      | FLASH                                                        |

| EEPROM Size -              | -                                                            |

| RAM Size                   | 8K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                  |

| Data Converters A          | A/D 7x12b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature -    | -40°C ~ 85°C (TA)                                            |

| Mounting Type              | Surface Mount                                                |

| Package / Case 4           | 48-LQFP                                                      |

| Supplier Device Package    | 48-LQFP (7x7)                                                |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 6.18   | LCD Display Driver                            |

|--------|-----------------------------------------------|

| 6.18.1 | Overview                                      |

| 6.18.2 |                                               |

| 6.19   | Analog to Digital Converter (ADC)75           |

| 6.19.1 | Overview                                      |

| 6.19.2 |                                               |

| 6.20   | Analog Comparator Controller (ACMP)76         |

| 6.20.1 | Overview                                      |

| 6.20.2 |                                               |

| 7 App  | blication Circuit                             |

| 8 PO   | WER COMSUMPTION                               |

| 9 ELE  | ECTRICAL CHARACTERISTIC                       |

|        | Absolute Maximum Ratings                      |

| 9.2    | Nano102/Nano112 DC Electrical Characteristics |

| 9.3    | AC Electrical Characteristics                 |

| 9.3.1  | External Input Clock                          |

| 9.3.2  | External 4~24 MHz XTAL Oscillator             |

| 9.3.3  | External 32.768 kHz Crystal                   |

| 9.3.4  | Internal 12 MHz Oscillator                    |

| 9.3.5  | Internal 10 kHz Oscillator                    |

| 9.4    | Analog Characteristics                        |

| 9.4.1  | 12-bit ADC                                    |

| 9.4.2  | Brown-out Detector                            |

| 9.4.3  | Power-on Reset                                |

| 9.4.4  | Temperature Sensor                            |

| 9.4.5  | LCD                                           |

| 9.4.6  | Internal Voltage Reference                    |

| 9.4.7  | Comparator                                    |

| 10 PA  | CKAGE DIMENSIONS92                            |

| 10.1   | 100L LQFP (14x14x1.4 mm footprint 2.0 mm)92   |

| 10.2   | 64R LQFP(10x10x1.4 mm footprint 2.0 mm)93     |

| 10.3   | 64S LQFP (7x7x1.4 mm footprint 2.0 mm)94      |

| 10.4   | 48L LQFP (7x7x1.4 mm footprint 2.0 mm)96      |

| 10.5   | 33L QFN (5x5x1.4 mm footprint 2.0 mm)97       |

- Supports four common polynomials CRC-CCITT, CRC-8, CRC-16, and CRC-32

- CRC-CCITT:  $X^{16} + X^{12} + X^5 + 1$

- CRC-8:  $X^8 + X^2 + X + 1$

- CRC-16:  $X^{16} + X^{15} + X^2 + 1$

- CRC-32:  $X^{32} + X^{26} + X^{23} + X^{22} + X^{16} + X^{12} + X^{11} + X^{10} + X^8 + X^7 + X^5 + X^4 + X^2 + X + 1$

- Clock Control

- Flexible selection for different applications

- Built-in 12/16 MHz OSC, can be trimmed to 1 % deviation within all temperature range when turning on auto-trim function (system must have external 32.768 kHz crystal input) otherwise 12/16 MHz OSC has 2 % deviation within all temperature range.

- Low power 10 kHz OSC for watchdog and low power system operation

- Supports one PLL, up to 32 MHz, for high performance system operation External 4~24 MHz crystal input for precise timing operation

- External 32.768 kHz crystal input for RTC function and low power system operation

- GPIO

- Three I/O modes:

- Push-Pull output

- Open-Drain output

- Input only with high impendence

- All inputs with Schmitt trigger

- I/O pin configured as interrupt source with edge/level setting

- Supports High Driver and High Sink I/O mode

- Supports input 5V tolerance, except PA.0 ~ PA.7, PA.12, PA.13, PF.0(X32I), PF.1(X32O).

- Timer

- Supports 4 sets of 32-bit timers, each with 24-bit up-counting timer and one 8-bit pre-scale counter

- Independent Clock Source for each timer

- Provides one-shot, periodic, output toggle and continuous operation modes

- Internal trigger event to ADC and PDMA

- Supports PDMA mode

- Wake system up from Power-down mode

- Watchdog Timer

- Clock Source from LIRC (Internal 10 kHz Low Speed Oscillator Clock)

- Selectable time-out period from 1.6 ms ~ 26 sec (depending on clock source)

- Interrupt or reset selectable when watchdog time-out

### 2.2 Nano112 Features – LCD Line

- Low Supply Voltage Range: 1.8 V to 3.6 V

- Ultra-Low Power Consumption

- Operation mode : 150 uA/MHz

- Power-down mode : 1.5 uA (RTC on, RAM retention)

- Deep power down mode : 650 nA (RAM retention)

- Fast Wake-Up From Standby Mode : Less than 6 µs

- Core

- ARM<sup>®</sup> Cortex<sup>™</sup>-M0 core running up to 32 MHz

- One 24-bit system timer

- Supports Low Power Sleep mode

- Single-cycle 32-bit hardware multiplier

- NVIC for the 32 interrupt inputs, each with 4-levels of priority

- Serial Wire Debug supports with 2 watchpoints/4 breakpoints

- Flash EPROM Memory

- Runs up to 32 MHz with zero wait state for discontinuous address read access.

- 16/32 Kbytes application program memory (APROM)

- ◆ 4 Kbytes In System Programming (ISP) loader program memory (LDROM)

- Programmable data flash start address and memory size with 512 bytes page erase unit

- In System Program (ISP)/In Application Program (IAP) to update on chip Flash EPROM

- SRAM Memory

- ♦ 4/8 Kbytes embedded SRAM

- Supports DMA mode

- DMA : Supports 5 channels: 4 PDMA channels, and one CRC channel

- PDMA

- Peripheral-to-memory, memory-to-peripheral, and memory-to-memory transfer

- Supports word boundary address

- Supports word alignment transfer length in memory-to-memory mode

- Supports word/half-word/byte alignment transfer length in peripheral-tomemory and memory-to-peripheral mode

- Supports word/half-word/byte transfer data width from/to peripheral

- Supports address direction: increment, fixed, and wrap around

- ♦ CRC

- Supports four common polynomials CRC-CCITT, CRC-8, CRC-16, and CRC-32

- CRC-CCITT: X<sup>16</sup> + X<sup>12</sup> + X<sup>5</sup> + 1

- Brown-out

- Built-in 2.5V/2.0V/1.7V BOD for wide operating voltage range operation

- 96-bit unique ID

- 128-bit unique customer ID

- Operating Temperature: -40°C~85°C

- Packages:

- All Green package (RoHS)

- LQFP 100-pin(14x14) / 64-pin(10x10) / 64-pin(7x7) / 48-pin(7x7)

### **3 ABBREVIATIONS**

| Acronym | Description                                     |  |  |  |  |  |  |  |  |

|---------|-------------------------------------------------|--|--|--|--|--|--|--|--|

| ACMP    | Analog Comparator Controller                    |  |  |  |  |  |  |  |  |

| ADC     | Analog-to-Digital Converter                     |  |  |  |  |  |  |  |  |

| AES     | Advanced Encryption Standard                    |  |  |  |  |  |  |  |  |

| АРВ     | Advanced Peripheral Bus                         |  |  |  |  |  |  |  |  |

| АНВ     | Advanced High-Performance Bus                   |  |  |  |  |  |  |  |  |

| BOD     | Brown-out Detection                             |  |  |  |  |  |  |  |  |

| CAN     | Controller Area Network                         |  |  |  |  |  |  |  |  |

| DAP     | Debug Access Port                               |  |  |  |  |  |  |  |  |

| DES     | Data Encryption Standard                        |  |  |  |  |  |  |  |  |

| EBI     | External Bus Interface                          |  |  |  |  |  |  |  |  |

| EPWM    | Enhanced Pulse Width Modulation                 |  |  |  |  |  |  |  |  |

| FIFO    | First In, First Out                             |  |  |  |  |  |  |  |  |

| FMC     | Flash Memory Controller                         |  |  |  |  |  |  |  |  |

| FPU     | Floating-point Unit                             |  |  |  |  |  |  |  |  |

| GPIO    | General-Purpose Input/Output                    |  |  |  |  |  |  |  |  |

| HCLK    | The Clock of Advanced High-Performance Bus      |  |  |  |  |  |  |  |  |

| HIRC    | 12/16 MHz Internal High Speed RC Oscillator     |  |  |  |  |  |  |  |  |

| НХТ     | 4~24 MHz External High Speed Crystal Oscillator |  |  |  |  |  |  |  |  |

| IAP     | In Application Programming                      |  |  |  |  |  |  |  |  |

| ICP     | In Circuit Programming                          |  |  |  |  |  |  |  |  |

| ISP     | In System Programming                           |  |  |  |  |  |  |  |  |

| LDO     | Low Dropout Regulator                           |  |  |  |  |  |  |  |  |

| LIN     | Local Interconnect Network                      |  |  |  |  |  |  |  |  |

| LIRC    | 10 kHz internal low speed RC oscillator (LIRC)  |  |  |  |  |  |  |  |  |

| MPU     | Memory Protection Unit                          |  |  |  |  |  |  |  |  |

| NTC     | Negative Temperature Coefficient                |  |  |  |  |  |  |  |  |

| NVIC    | Nested Vectored Interrupt Controller            |  |  |  |  |  |  |  |  |

| PCLK    | The Clock of Advanced Peripheral Bus            |  |  |  |  |  |  |  |  |

| PDMA    | Peripheral Direct Memory Access                 |  |  |  |  |  |  |  |  |

| PLL     | Phase-Locked Loop                               |  |  |  |  |  |  |  |  |

| PTC     | Positive Temperature Coefficient                |  |  |  |  |  |  |  |  |

| PT1000  | Thermal Resistance                              |  |  |  |  |  |  |  |  |

| PWM     | Pulse Width Modulation                          |  |  |  |  |  |  |  |  |

# nuvoTon

| QEI  | Quadrature Encoder Interface                |

|------|---------------------------------------------|

| SDIO | Secure Digital Input/Output                 |

| SPI  | Serial Peripheral Interface                 |

| SPS  | Samples per Second                          |

| TDES | Triple Data Encryption Standard             |

| TMR  | Timer Controller                            |

| UART | Universal Asynchronous Receiver/Transmitter |

| UCID | Unique Customer ID                          |

| USB  | Universal Serial Bus                        |

| WDT  | Watchdog Timer                              |

| WWDT | Window Watchdog Timer                       |

Table 3-1 List of Abbreviations

# nuvoTon

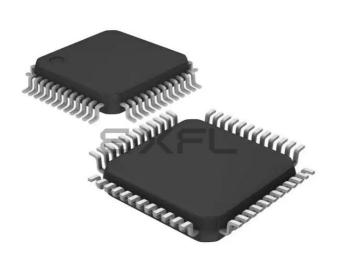

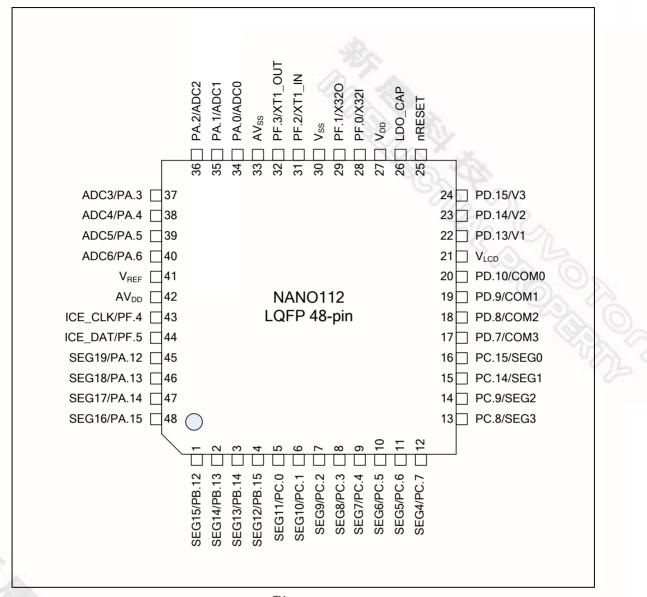

#### Figure 4-7 NuMicro<sup>™</sup> Nano112 LQFP 48-pin Diagram

| Pin No.               |   |        | -Pin Name             | Pin Type | Description                                                                           |

|-----------------------|---|--------|-----------------------|----------|---------------------------------------------------------------------------------------|

| 100-pin 64-pin 48-pin |   | 48-pin |                       | гштуре   | Description                                                                           |

|                       |   |        | LCD_SEG26             | 0        | LCD segment output 26 at 100-pin                                                      |

|                       |   |        | LCD_SEG22             | 0        | LCD segment output 22 at 64-pin                                                       |

|                       |   |        | LCD_SEG15             | 0        | LCD segment output 15 at 48-pin                                                       |

|                       |   |        | UART0_RTSn            | 0        | UART0 Request to Send output pin                                                      |

|                       |   |        | SPI0_MOSI0            | I/O      | SPI0 1 <sup>st</sup> MOSI (Master Out, Slave In) p                                    |

|                       |   |        | тмо                   | I/O      | Timer0 external counter input or Timer<br>toggle out.                                 |

|                       |   |        | FCLK0                 | 0        | Frequency Divider0 output pin                                                         |

|                       |   |        | PB.13                 | I/O      | General purpose digital I/O pin                                                       |

|                       |   |        | LCD_SEG25             | 0        | LCD segment output 25 at 100-pin                                                      |

|                       |   |        | LCD_SEG21             | 0        | LCD segment output 21 at 64-pin                                                       |

| 9                     | 4 | 2      | LCD_SEG14 O LCD segme |          | LCD segment output 14 at 48-pin                                                       |

|                       |   |        | UART0_RXD             | I        | UART0 Data receiver input pin                                                         |

|                       |   |        | SPI0_MISO0            | I/O      | SPI0 1 <sup>st</sup> MISO (Master In, Slave Out) p                                    |

|                       |   |        | PB.14                 | I/O      | General purpose digital I/O pin                                                       |

|                       |   |        | LCD_SEG24             | 0        | LCD segment output 24 at 100-pin                                                      |

|                       |   |        | LCD_SEG20             | 0        | LCD segment output 20 at 64-pin                                                       |

| 10                    | 5 | 3      | LCD_SEG13             | 0        | LCD segment output 13 at 48-pin                                                       |

|                       |   |        | UART0_TXD             | o        | UART0 Data transmitter output pin (Th<br>pin could be modulated with PWM0<br>output.) |

|                       |   |        | SPI0_CLK              | I/O      | SPI0 serial clock pin                                                                 |

| 11                    |   |        | NC                    |          |                                                                                       |

|                       |   |        | PB.15                 | I/O      | General purpose digital I/O pin                                                       |

|                       |   |        | LCD_SEG23             | 0        | LCD segment output 23 at 100-pin                                                      |

| 40                    |   | 4      | LCD_SEG19             | 0        | LCD segment output 19 at 64-pin                                                       |

| 12                    | 6 | 4      | LCD_SEG12             | 0        | LCD segment output 12 at 48-pin                                                       |

|                       |   |        | UART0_CTSn            | I        | UART0 Clear to Send input pin                                                         |

|                       |   |        | SPI0_SS0              | I/O      | SPI0 1 <sup>st</sup> slave select pin                                                 |

|                       |   |        | PC.0                  | I/O      | General purpose digital I/O pin                                                       |

|                       |   |        | LCD_SEG22             | 0        | LCD segment output 24 at 100-pin                                                      |

| 40                    | _ | _      | LCD_SEG18             | 0        | LCD segment output 18 at 64-pin                                                       |

| 13                    | 7 | 5      | LCD_SEG11             | 0        | LCD segment output 11 at 48-pin                                                       |

|                       |   |        | SPI0_SS1              | I/O      | SPI0 2 <sup>nd</sup> slave select pin                                                 |

|                       |   |        | I2C0_SCL              | I/O      | I <sup>2</sup> C0 clock pin                                                           |

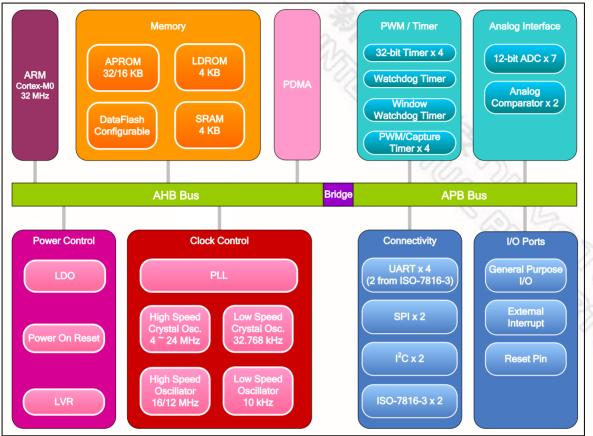

### 5 BLOCK DIAGRAM

### 5.1 Nano102 Block Diagram

Figure 5-1 NuMicro<sup>™</sup> Nano102 Block Diagram

### **6 FUNCTIONAL DESCRIPTION**

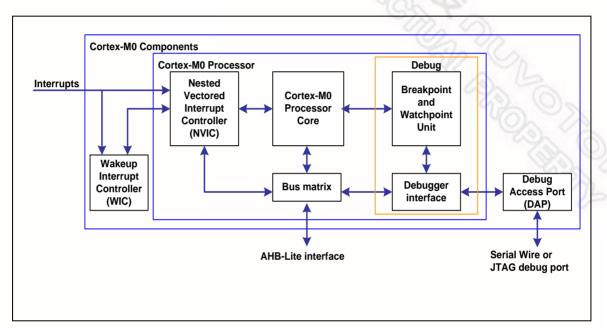

#### 6.1 ARM® Cortex<sup>™</sup>-M0 Core

The Cortex<sup>™</sup>-M0 processor is a configurable, multistage, 32-bit RISC processor, which has an AMBA AHB-Lite interface and includes an NVIC component. It also has optional hardware debug functionality. The processor can execute Thumb code and is compatible with other Cortex<sup>™</sup>-M profile processor. The profile supports two modes –Thread mode and Handler mode. Handler mode is entered as a result of an exception. An exception return can only be issued in Handler mode. Thread mode is entered on Reset, and can be entered as a result of an exception return. The following figure shows the functional controller of processor.

Figure 6-1 Functional Block Diagram

The implemented device provides:

- A low gate count processor:

- ARMv6-M Thumb® instruction set

- Thumb-2 technology

- ARMv6-M compliant 24-bit SysTick timer

- A 32-bit hardware multiplier

- System interface supported with little-endian data accesses

- Ability to have deterministic, fixed-latency, interrupt handling

- Load/store-multiples and multicycle-multiplies that can be abandoned and restarted to facilitate rapid interrupt handling

- C Application Binary Interface compliant exception model. This is the ARMv6-M, C Application Binary Interface (C-ABI) compliant exception model that enables the use of pure C functions as interrupt handlers

- Low Power Sleep mode entry using the Wait For Interrupt (WFI), Wait For Event (WFE) instructions, or return from interrupt sleep-on-exit feature

#### 6.2 Memory Organization

#### 6.2.1 Overview

The Nano112 provides 4G-byte addressing space. The memory locations assigned to each onchip modules are shown in following. The detailed register definition, memory space, and programming detailed will be described in the following sections for each on-chip module. The Nano112 series only supports little-endian data format.

### 6.11 Watchdog Timer Controller

#### 6.11.1 Overview

The purpose of Watchdog Timer is to perform a system reset after the software running into a problem. This prevents system from hanging for an infinite period of time. Besides, this Watchdog Timer supports the function to wake-up CPU from power-down mode. The watchdog timer includes an 18-bit free running counter with programmable time-out intervals.

#### 6.11.2 Features

- 18-bit free running WDT counter for Watchdog timer time-out interval.

- Selectable time-out interval (2<sup>4</sup> ~ 2<sup>18</sup>) and the time-out interval is 104 ms ~ 26.316 s (if WDT\_CLK = 10 kHz).

- Reset period = (1 / 10 kHz) \* 63, if WDT\_CLK = 10 kHz.

#### 6.12 Window Watchdog Timer Controller

#### 6.12.1 Overview

The purpose of Window Watchdog Timer is to perform a system reset within a specified window period to prevent software run to uncontrollable status by any unpredictable condition.

#### 6.12.2 Features

- 6-bit down counter and 6-bit compare value to make the window period flexible

- Selectable WWDT clock pre-scale counter to make WWDT time-out interval variable

### 6.16 I<sup>2</sup>C

#### 6.16.1 Overview

$I^2C$  is a two-wire, bi-directional serial bus that provides a simple and efficient method of data exchange between devices. The  $I^2C$  standard is a true multi-master bus including collision detection and arbitration that prevents data corruption if two or more masters attempt to control the bus simultaneously. Serial, 8-bit oriented bi-directional data transfers can be made up to 1 Mbps.

Data is transferred between a Master and a Slave synchronously to SCL on the SDA line on a byte-by-byte basis. Each data byte is 8-bit long. There is one SCL clock pulse for each data bit with the MSB being transmitted first. An acknowledge bit follows each transferred byte.

A transition on the SDA line while SCL is high is interpreted as a command (START or STOP). Each bit is sampled during the high period of SCL; therefore, the SDA line may be changed only during the low period of SCL and must be held stable during the high period of SCL.

The controller's on-chip  $I^2C$  logic provides the serial interface that meets the  $I^2C$  bus standard mode specification. The  $I^2C$  controller handles byte transfers autonomously. Pull up resistor is needed for  $I^2C$  operation as these are open drain pins.

The  $l^2C$  controller is equipped with two slave address registers. The contents of the registers are irrelevant when  $l^2C$  is in Master mode. In the Slave mode, the seven most significant bits must be loaded with the user's own slave address. The  $l^2C$  hardware will react if the contents of I2CADDR are matched with the received slave address.

This controller supports the "General Call (GC)" function. If the GCALL (I2CSADDR[0]) bit is set this controller will respond to General Call address (00H). Clear GC bit to disable general call function. When GCALL bit is set and the  $I^2C$  is in Slave mode, it can receive the general call address which is equal to 00H after master sends general call address to the  $I^2C$  bus, then it will follow status of GC mode. If it is in Master mode, the ACK bit must be cleared when it sends general call address of 00H to the  $I^2C$  bus.

The  $I^2C$ -bus controller supports multiple address recognition with two address mask register. When the bit in the address mask register is set to one, it means the received corresponding address bit is don't-care. If the bit is set to 0, that means the received corresponding register bit should be exact the same as address register.

#### 6.16.2 Features

- Supports two I2C channels and both of them can acts as Master or Slave mode

- Bidirectional data transfer between masters and slaves

- Multi-master bus (no central master)

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus

- Serial clock synchronization allows devices with different bit rates to communicate via one serial bus

- Serial clock synchronization can be used as a handshake mechanism to suspend and resume serial transfer

- One built-in 14-bit time-out counter requesting the I<sup>2</sup>C interrupt if the I<sup>2</sup>C bus hangs up and timer-out counter overflows.

- Programmable clock divider allows versatile rate control

- Supports 7-bit addressing mode

### 6.19 Analog to Digital Converter (ADC)

#### 6.19.1 Overview

The Nano112 series contains one 12-bit successive approximation analog-to-digital converter (SAR A/D converter) with 8 external input channels and 4 internal channels. The A/D converter supports three operation modes: Single, Single-cycle Scan and Continuous Scan mode, and can be started by software, external STADC(PA.11) pin, timer event start and PWM trigger.

Note that the I/O pins used as ADC analog input pins must configure the Pin Function (PA\_L\_MFP) to ADC input and off digital function (GPIOA\_OFFD) should be turned on before ADC function is enabled.

#### 6.19.2 Features

- Analog input voltage range: 0~V<sub>REF</sub> (Max to AV<sub>DD</sub>)

- Selectable 12-bits, 10-bits, 8-bits and 6-bits resolution

- Supports sampling time settings for channel 0~7 individually (ADCCHSAMP0 register) and channel 14~17 share the same one sampling time setting (ADCCHSAMP1 register)

- Supports two power-down modes:

- Power-down mode

- Standby mode

- Up to 8 external analog input channels (channel0 ~ channel7), and 4 internal channels (channel14~channel17) converting four voltage sources (internal band-gap voltage, internal temperature sensor output, AV<sub>DD</sub>, and AV<sub>SS</sub>).

- Maximum ADC clock frequency is 32 MHz and each conversion is 19 clocks+ sampling time depending on the input resistance (Rin).

- Three operating modes:

- Single mode: A/D conversion is performed one time on a specified channel.

- Single-cycle Scan mode: A/D conversion is performed one cycle on all specified channels with the sequence from the lowest numbered channel to the highest numbered channel.

- Continuous Scan mode: A/D converter continuously performs Single-cycle scan mode until software stops A/D conversion.

- An A/D conversion can be started by:

- Software write 1 to ADST bit

- External pin STADC

- PWM trigger

- Selects one from four timer events (TMR0, TMR1, TMR2 and TMR3) that enable ADC and transfer AD results by PDMA

- Conversion results held in data registers for each channel

- Supports digital comparator: Conversion result can be compared with a specified value and user can select whether to generate an interrupt when conversion result is equal to the compare register setting.

- Supports Calibration and load Calibration words capability.

### 6.20 Analog Comparator Controller (ACMP)

#### 6.20.1 Overview

The Nano112 series contains two comparators. The comparator output is logic 1 when positive input is greater than negative input; otherwise, the output is 0. Each comparator can be configured to generate an interrupt when the comparator output value changes. The comparator ACMP0 can be used as normal comparator or it can emulate ADC function. The comparator ACMP1 can be used as normal comparator only.

#### 6.20.2 Features

- Analog input voltage range: 0 ~ AV<sub>DD</sub>

- Supports hysteresis function

- Supports wake-up function

- Comparator ACMP0 supports

- 4 positive sources(ACMP0\_Px)

- PA.1, PA.2, PA.3, or PA.4

- 4 negative sources

- PA.5 (ACMP0\_N)

- Comparator Reference Voltage (CRV)

- Int\_V<sub>REF</sub>

- AGND

- Comparator ACMP1 supports

- 1 positive source

- PA.12(ACMP1\_P)

- ♦ 4 negative sources

- PA.13(ACMP1\_N)

- Comparator Reference Voltage (CRV)

- Int\_V<sub>REF</sub>

- AGND

- Comparator ACMP0 supports three operation modes:

- Normal Comparator mode

- Single Slope ADC mode: Resistance measurement (e.g. PTC, NTC, PT1000)

- Supports to measure 7 channels resistor

- Sigma-Delta ADC mode

- Supports up to 4 channel voltage input from ACMP0\_Px

| Operating Current<br>Idle Mode<br>HCLK =12 MHz<br>V <sub>LDO1</sub> =1.6 V | I <sub>IDLE9</sub>  | 2.8 |   | mA | 3.3 V | 12 MHz | х | х | V |

|----------------------------------------------------------------------------|---------------------|-----|---|----|-------|--------|---|---|---|

|                                                                            | I <sub>IDLE10</sub> | 0.8 |   | mA | 3.3 V | 12 MHz | х | х | Х |

|                                                                            | I <sub>IDLE11</sub> | 2.8 | 1 | mA | 1.8 V | 12 MHz | х | х | V |

|                                                                            | I <sub>IDLE12</sub> | 0.8 | 0 | mA | 1.8 V | 12 MHz | х | х | х |

#### 9.3.4 Internal 12 MHz Oscillator

| PARAMETER                                   | SYM.             | S     | PECIFI | CATION | IS   | TEST CONDITION                                                     |  |

|---------------------------------------------|------------------|-------|--------|--------|------|--------------------------------------------------------------------|--|

|                                             | <b>3</b> T WI.   | MIN.  | TYP.   | MAX.   | UNIT | TEST CONDITION                                                     |  |

| Supply voltage[1]                           | V <sub>HRC</sub> |       | 1.8    | The    | V    |                                                                    |  |

| Calibrated Internal<br>Oscillator Frequency |                  | 11.88 | 12     | 12.12  | MHz  | 25°C, VDD = 3.3V                                                   |  |

|                                             | F <sub>HRC</sub> | 11.76 | 12     | 12.24  | MHz  | -40°C ~ +85°C,<br>VDD = 1.8V~3.6V                                  |  |

|                                             |                  | 11.88 | 12     | 12.12  |      | -40°C ~ +85 °C,<br>VDD = 1.8V~3.6V                                 |  |

|                                             |                  |       |        |        | MHz  | Enable 32.768K crystal<br>oscillator and set<br>TRIM_SEL[1:0]="10" |  |

| Operating current                           | I <sub>HRC</sub> |       | 250    |        | μA   | 76,00                                                              |  |

Note: Internal oscillator operation voltage comes from LDO.

### 9.3.5 Internal 10 kHz Oscillator

| PARAMETER         | SYM.             | S    | PECIFI |      | IS   | TEST CONDITION                    |  |

|-------------------|------------------|------|--------|------|------|-----------------------------------|--|

|                   | <b>0</b> m.      | MIN. | TYP.   | MAX. | UNIT |                                   |  |

| Supply voltage[1] | $V_{LRC}$        |      | 1.8    |      | V    |                                   |  |

|                   |                  | 7    | 10     | 13   | kHz  | 25°C, VDD = 3V                    |  |

| Center Frequency  | F <sub>LRC</sub> | 5    | 10     | 15   | kHz  | -40°C ~+85 °C,<br>VDD = 1.8V~3.6V |  |

| Operating current | I <sub>LRC</sub> |      | 0.3    |      | μA   | VDD = 3V                          |  |

Note: Internal oscillator operation voltage comes from LDO.

### 9.4 Analog Characteristics

#### 9.4.1 12-bit ADC

| PARAMETER                                                                      | SYM.               | SF   | PECIFIC | ATIONS | 6    | TEST CONDITION                                                                      |  |

|--------------------------------------------------------------------------------|--------------------|------|---------|--------|------|-------------------------------------------------------------------------------------|--|

|                                                                                | <b>0</b> m.        | MIN. | TYP.    | MAX.   | UNIT |                                                                                     |  |

| Operating voltage                                                              | AV <sub>DD</sub>   | 1.8  |         | 3.6    | V    | $AV_{DD} = V_{DD}$                                                                  |  |

| Operating current (AV <sub>DD</sub><br>current)<br>(Enable ADC and disable all | I <sub>ADC32</sub> |      | 120     |        | μΑ   | $AV_{DD} = V_{DD} = 3.0V$<br>ADC_VREF = AV <sub>DD</sub><br>ADC Clock Rate = 32 MHz |  |

| PARAMETER | SYM.                 | S    | PECIFI |      | TEST CONDITION |                                                                                                                         |

|-----------|----------------------|------|--------|------|----------------|-------------------------------------------------------------------------------------------------------------------------|

|           | <b>0</b> m.          | MIN. | TYP.   | MAX. | UNIT           |                                                                                                                         |

|           |                      |      | 8.3    | もい   | μΑ             | $V_{DD}$ = 3V, frame rate = 64Hz<br>Without<br>loading (internal R type with<br>internal 200K $\Omega$ resistor ladder) |

|           | I <sub>LCDintR</sub> |      | 6.4    | 0    | μΑ             | $V_{DD}$ = 3V, frame rate = 64Hz<br>Without<br>loading (internal R type with<br>internal 300K $\Omega$ resistor ladder) |

|           |                      |      | 5.5    |      | μΑ             | $V_{DD}$ = 3V, frame rate = 64Hz<br>Without<br>loading (internal R type with<br>internal 400K $\Omega$ resistor ladder) |

|           | I <sub>LCDextR</sub> |      | 3.7    |      | μΑ             | $V_{DD}$ = 3V, frame rate = 64Hz<br>Without loading (external R type<br>with external 1M $\Omega$ resistor ladder)      |

### 9.4.6 Internal Voltage Reference

| PARAMETER              | SYM.                | SI   | PECIFI | CATION | TEST CONDITION |                                       |

|------------------------|---------------------|------|--------|--------|----------------|---------------------------------------|

|                        | 01111.              | MIN. | TYP.   | MAX.   | UNIT           |                                       |

| Operating voltage      | AV <sub>DD</sub>    | 1.8  | -      | 3.6    | V              |                                       |

| 1.5V voltage reference | V <sub>REF1</sub>   | 1.44 | 1.5    | 1.56   | V              | AV <sub>DD</sub> ≥ 1.8V (-40°C ~85°C) |

| 1.8V voltage reference | $V_{REF2}$          | 1.69 | 1.8    | 1.87   | V              | AV <sub>DD</sub> ≥ 2.0V (-40°C ~85°C) |

| 2.5V voltage reference | $V_{\text{REF3}}$   | 2.35 | 2.5    | 2.60   | V              | AV <sub>DD</sub> ≥ 2.8V (-40°C ~85°C) |

| Stable Time            | T <sub>REFTAB</sub> | -    | 1      | -      | ms             |                                       |

| Operating current      | I <sub>VREF</sub>   | -    | 30     | -      | μA             | $AV_{DD} = 3V$                        |

### 9.4.7 Comparator

| Symbol           | Parameter            | Min | Тур | Max                    | Unit | Test Condition         |

|------------------|----------------------|-----|-----|------------------------|------|------------------------|

| V <sub>CMP</sub> | Supply Voltage       | 1.8 |     | 3.6                    | V    |                        |

| T <sub>A</sub>   | Temperature          | -40 | 25  | 85                     | °C   | -                      |

| I <sub>CMP</sub> | Operation Current    | -   | 40  |                        | μA   | AV <sub>DD</sub> = 3 V |

| V <sub>OFF</sub> | Input Offset Voltage |     | 10  | 20                     | mV   | -                      |

| V <sub>SW</sub>  | Output Swing         | 0.1 | -   | AV <sub>DD</sub> - 0.1 | V    | -                      |

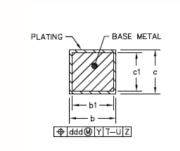

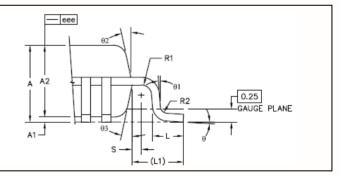

|                        |   | SYMBOL | MIN     | NOM   | MAX  |

|------------------------|---|--------|---------|-------|------|

| TOTAL THICKNESS        |   | Α      |         |       | 1.6  |

| STAND OFF              |   | A1     | 0.05    |       | 0.15 |

| MOLD THICKNESS         |   | A2     | 1.35    | 1.4   | 1.45 |

| LEAD WIDTH(PLATING)    |   | ь      | 0.13    | 0.18  | 0.23 |

| LEAD WIDTH             |   | b1     | 0.13    | 0.16  | 0.19 |

| L/F THICKNESS(PLATING) |   | с      | 0.09    |       | 0.2  |

| L/F THICKNESS          |   | c1     | 0.09    |       | 0.16 |

|                        | х | D      |         | 9 BSC |      |

|                        | Y | E      |         | 9 BSC |      |

| BODY SIZE              | х | D1     | 7 BSC   |       |      |

|                        | Y | E1     | 7 BSC   |       |      |

| LEAD PITCH             |   | е      | 0.4 BSC |       |      |

|                        |   | L      | 0.45    | 0.6   | 0.75 |

| FOOTPRINT              |   | L1     | 1 REF   |       |      |

|                        |   | θ      | 0.      | 3.5   | 7.   |

|                        |   | 01     | 0.      |       |      |

|                        |   | θ2     | 11.     | 12    | 13   |

|                        |   | 03     | 11'     | 12*   | 13   |

|                        |   | R1     | 0.08    |       |      |

|                        |   | R2     | 0.08    |       | 0.2  |

|                        |   | S      | 0.2     |       |      |

| PACKAGE EDGE TOLERANCE |   |        | 0.2     |       |      |

| LEAD EDGE TOLERANCE    |   | bbb    | 0.2     |       |      |

| COPLANARITY            |   | ccc    | 0.08    |       |      |

| LEAD OFFSET            |   | ddd    | 0.07    |       |      |

| MOLD FLATNESS          |   | eee    | 0.05    |       |      |