Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Detano                     |                                                                                          |

|----------------------------|------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                   |

| Core Processor             | ARM® Cortex®-M0                                                                          |

| Core Size                  | 32-Bit Single-Core                                                                       |

| Speed                      | 32MHz                                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                        |

| Number of I/O              | 58                                                                                       |

| Program Memory Size        | 32KB (32K x 8)                                                                           |

| Program Memory Type        | FLASH                                                                                    |

| EEPROM Size                | -                                                                                        |

| RAM Size                   | 8K x 8                                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                              |

| Data Converters            | A/D 7x12b                                                                                |

| Oscillator Type            | Internal                                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                        |

| Mounting Type              | Surface Mount                                                                            |

| Package / Case             | 64-LQFP                                                                                  |

| Supplier Device Package    | 64-LQFP (7x7)                                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/nano112sc2an |

|                            |                                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2 FEATURES

The equipped features are dependent on the product line and their sub products.

### 2.1 Nano102 Features – Base Line

- Low Supply Voltage Range: 1.8 V to 3.6 V

- Ultra-Low Power Consumption

- Operation mode : 150 uA/MHz

- Power-down mode : 1.5 uA (RTC on, RAM retention)

- Deep power down mode : 650 nA (RAM retention)

- Fast Wake-Up From Standby Mode : Less than 6 μs

- Core

- ◆ ARM<sup>®</sup> Cortex<sup>™</sup>-M0 core running up to 32 MHz

- One 24-bit system timer

- Supports Low Power Sleep mode

- Single-cycle 32-bit hardware multiplier

- NVIC for the 32 interrupt inputs, each with 4-levels of priority

- Serial Wire Debug supports with 2 watchpoints/4 breakpoints

- Flash EPROM Memory

- Runs up to 32 MHz with zero wait state for discontinuous address read access

- 16/32 Kbytes application program memory (APROM)

- 4 KB in system programming (ISP) loader program memory (LDROM)

- Programmable data flash start address and memory size with 512 bytes page erase unit

- In System Program (ISP)/In Application Program (IAP) to update on-chip Flash EPROM

- SRAM Memory

- 4/8 Kbytes embedded SRAM

- Supports DMA mode

- DMA: Supports 5 channels: 4 PDMA channels and one CRC channel

- PDMA

- Peripheral-to-memory, memory-to-peripheral, and memory-to-memory transfer

- Supports word boundary address

- Supports word alignment transfer length in memory-to-memory mode

- Supports word/half-word/byte alignment transfer length in peripheral-tomemory and memory-to-peripheral mode

- Supports word/half-word/byte transfer data width from/to peripheral

- Supports address direction: increment, fixed, and wrap around

- CRC

### enable ADC

- SmartCard (SC)

- Compliant to ISO-7816-3 T=0, T=1

- Supports up to two ISO-7816-3 ports

- Separates receive / transmit 4 bytes entry FIFO for data payloads

- Programmable transmission clock frequency

- Programmable receiver buffer trigger level

- Programmable guard time selection (11 ETU ~ 267 ETU)

- A 24-bit and two 8-bit time-out counter for Answer to Request (ATR) and waiting times processing

- Supports auto inverse convention function

- Supports transmitter and receiver error retry and error limit function

- Supports hardware activation sequence process

- Supports hardware warm reset sequence process

- Supports hardware deactivation sequence process

- Supports hardware auto deactivation sequence when detect the card is removal

- Supports UART mode (full-duplex)

- ACMP

- Suuports up to 2 analog comparators

- Analog input voltage range: 0 ~ AV<sub>DD</sub>

- Supports Hysteresis function

- Two analog comparators with optional internal reference voltage input at negative end

- Wake-up source

- Support RTC, WDT, I<sup>2</sup>C, Timer, UART, SPI, BOD, GPIO

- LCD

- LCD driver for up to 4 COM x 36 SEG or 6 COM x 34 SEG

- Supports Static, 1/2 bias and 1/3 bias voltage

- Six display modes; Static, 1/2 duty, 1/3 duty, 1/4 duty, 1/5 duty and 1/6 duty.

- Selectable LCD frequency by frequency divider

- Configurable frame frequency

- Internal Charge pump, adjustable contrast adjustment

- Configurable Charge pump frequency

- Blinking capability

- Supports R-type/C-type/External C-type method

- Configurable internal R-ladder resistor value (200K/300K/400K)

- ♦ LCD frame interrupt

- One built-in temperature sensor with 1°C resolution

Page 19 of 100

### 4.2.2 NuMicro<sup>™</sup> Nano112 LCD Line Selection Guide

|                                                 |       |      | Data         | ISP |          | Timer    | C                                                                            | onnectivi | ty  |        | PWM | ADC     |                              | IRC<br>10KHz/ |   |            | ISO- | ISP | <b>.</b> . | Maximum    |

|-------------------------------------------------|-------|------|--------------|-----|----------|----------|------------------------------------------------------------------------------|-----------|-----|--------|-----|---------|------------------------------|---------------|---|------------|------|-----|------------|------------|

| Part No.                                        | Flash | SRAM | Flash        | ROM | VO       | (32-bit) | UART SPI <sup>2</sup> C Comp (16-bit) (12-bit) RTC 12MHz/<br>12MHz/<br>16MHz | PDMA      | LCD | 7816-3 | ЮР  | Package | Operating Tem<br>Range (°C ) |               |   |            |      |     |            |            |

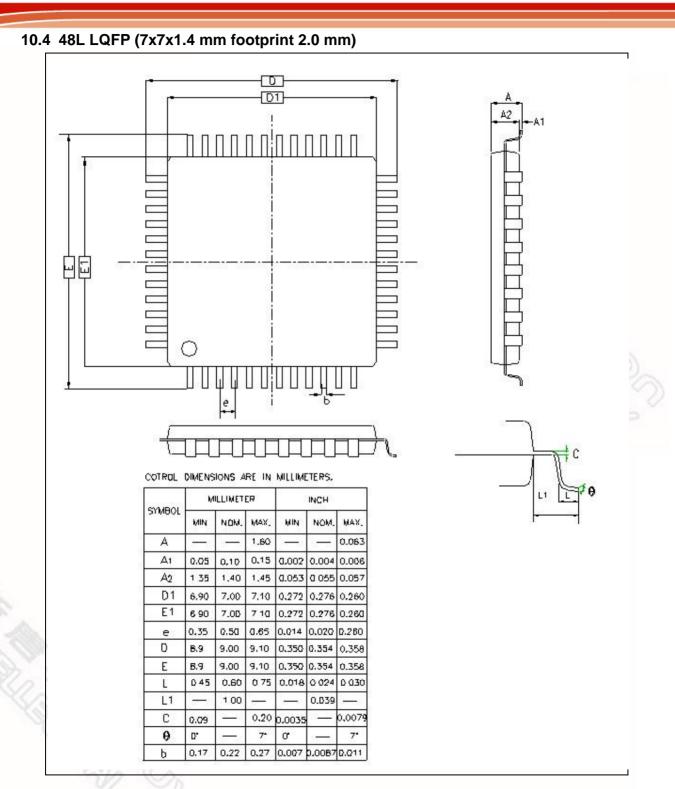

| NANO112LB1AN                                    | 16K   | 4K   | Configurable | 4K  | up to 40 | 4        | 4                                                                            | 2         | 2   | 2      | 4   | 7       | V                            | 1             | 4 | 4x20, 6x18 | 2    | V   | LQFP48     | -40 to +85 |

| NANO112LC2AN                                    | 32K   | 8K   | Configurable | 4K  | up to 40 | 4        | 4                                                                            | 2         | 2   | 2      | 4   | 7       | 1                            | 1             | 4 | 4x20, 6x18 | 2    | V   | LQFP48     | -40 to +85 |

| NANO112SB1AN                                    | 16K   | 4K   | Configurable | 4K  | up to 58 | 4        | 4                                                                            | 2         | 2   | 2      | 4   | 7       | V                            | V             | 4 | 4x32, 6x30 | 2    | V   | LQFP64     | -40 to +85 |

| NANO112SC2AN                                    | 32K   | 8K   | Configurable | 4K  | up to 58 | 4        | 4                                                                            | 2         | 2   | 2      | 4   | 7       | V                            | 1             | 4 | 4x32, 6x30 | 2    | V   | LQFP64     | -40 to +85 |

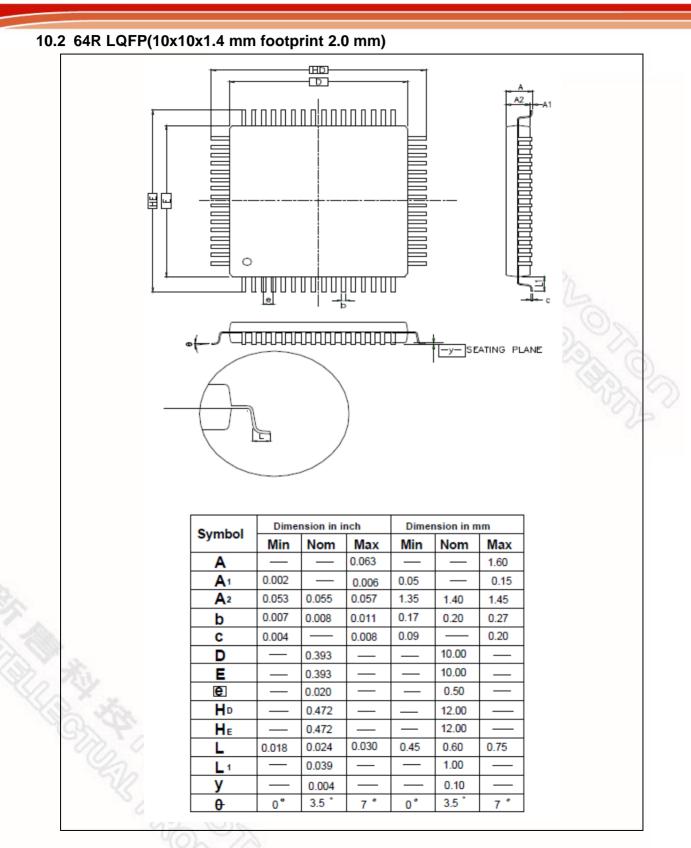

| NANO112RB1AN                                    | 16K   | 4K   | Configurable | 4K  | up to 58 | 4        | 4                                                                            | 2         | 2   | 2      | 4   | 7       | 1                            | 1             | 4 | 4x32, 6x30 | 2    | V   | LQFP64*    | -40 to +85 |

| NANO112RC2AN                                    | 32K   | 8K   | Configurable | 4K  | up to 58 | 4        | 4                                                                            | 2         | 2   | 2      | 4   | 7       | V                            | 1             | 4 | 4x32, 6x30 | 2    | V   | LQFP64*    | -40 to +85 |

| NANO112VC2AN                                    | 32K   | 8K   | Configurable | 4K  | up to 80 | 4        | 4                                                                            | 2         | 2   | 2      | 4   | 8       | V                            | 1             | 4 | 4x36, 6x34 | 2    | V   | LQFP100    | -40 to +85 |

| QFP48: 7x7mm<br>QFP64: 7x7mm<br>QFP64*: 10x10mm |       |      |              |     |          |          |                                                                              |           |     |        |     |         |                              |               |   |            | - 20 |     |            |            |

|                                                 |       |      |              |     |          |          |                                                                              |           |     |        |     |         |                              |               |   |            |      |     |            |            |

| Pin No | D      |        | Pin Name    | Pin Type  | Description                            |

|--------|--------|--------|-------------|-----------|----------------------------------------|

| 64-pin | 48-pin | 32-pin |             | Fill Type | Description                            |

|        |        |        | AD0         | AI        | ADC analog input0                      |

|        |        |        | PA.1        | I/O       | General purpose digital I/O pin        |

| 10     | 0.5    |        | AD1         | AI        | ADC analog input1                      |

| 46     | 35     |        | ACMP0_P3    | AI        | Comparator0 P-end input3               |

|        |        |        | ACMP0_CHDIS | 0         | Comparator0 charge/discharge pa        |

|        |        |        | PA.2        | I/O       | General purpose digital I/O pin        |

|        |        |        | SC0_CLK     | 0         | SmartCard0 clock pin<br>(SC0_UART_TXD) |

| 47     | 36     |        | INT0        | I         | External interrupt0 input pin          |

|        |        |        | AD2         | AI        | ADC analog input2                      |

|        |        |        | ACMP0_P2    | AI        | Comparator0 P-end input2               |

|        |        |        | ACMP0_CHDIS | 0         | Comparator0 charge/discharge pa        |

|        |        |        | PA.3        | I/O       | General purpose digital I/O pin        |

|        |        |        | SC0_DAT     | I/O       | SmartCard0 DATA<br>pin(SC0_UART_RXD)   |

| 48     | 37     |        | INT1        | I         | External interrupt 1                   |

|        |        |        | AD3         | AI        | ADC analog input3                      |

|        |        |        | ACMP0_P1    | AI        | Comparator0 P-end input1               |

|        |        |        | ACMP0_CHDIS | 0         | Comparator0 charge/discharge pa        |

|        |        |        | PA.4        | I/O       | General purpose digital I/O pin        |

|        |        |        | SC0_CD      | I         | SmartCard0 card detect pin             |

| 49     | 38     | 25     | AD4         | AI        | ADC analog input4                      |

| 2      |        |        | ACMP0_P0    | AI        | Comparator0 P-end input0               |

| 1      |        |        | ACMP0_CHDIS | 0         | Comparator0 charge/discharge pa        |

| 3      |        |        | PA.5        | I/O       | General purpose digital I/O pin        |

| 2      |        |        | SPI1_SS0    | I/O       | SPI1 1 <sup>st</sup> slave select pin  |

| 2      |        |        | I2C1_SDA    | I/O       | I <sup>2</sup> C1 data I/O pin         |

| 50     | 39     | 26     | SC0_PWR     | 0         | SmartCard0 Power pin                   |

|        |        |        | AD5         | AI        | ADC analog input5                      |

|        |        |        | ACMP0_N     | AI        | Comparator0 N-end input0               |

|        |        |        | ACMP0_CHDIS | 0         | Comparator0 charge/discharge pa        |

|        |        |        | PA.6        | I/O       | General purpose digital I/O pin        |

| 51     | 40     |        | ACMP0_CHDIS | 0         | Comparator0 charge/discharge pa        |

|        |        |        | SC0_RST     | 0         | SmartCard0 RST pin                     |

| Pin No. |        |        | Pin Name         | Die Tree | Description                                                                                        |

|---------|--------|--------|------------------|----------|----------------------------------------------------------------------------------------------------|

| 100-pin | 64-pin | 48-pin |                  | Pin Type | Description                                                                                        |

|         |        |        | LCD_DH2          | о        | LCD external capacitor pin of charge<br>pump circuit at 64-pin                                     |

|         |        |        | PWM0_CH1         | I/O      | PWM0 Channel1 output                                                                               |

|         |        |        | тсо              | I        | Timer0 capture input                                                                               |

|         |        |        | PD.12            | I/O      | General purpose digital I/O pin                                                                    |

|         |        |        | CLK_Hz           | 0        | 1, 1/2, 1/4, 1/8, 1/16 Hz clock output                                                             |

|         |        |        | LCD_DH1          | о        | LCD external capacitor pin of charge<br>pump circuit at 100-pin                                    |

| 44      | 31     |        | LCD_DH1          | 0        | LCD external capacitor pin of charge<br>pump circuit at 64-pin                                     |

|         |        |        | PWM0_CH0         | I/O      | PWM0 Channel0 output                                                                               |

|         |        |        | TM1              | I/O      | Timer1 external counter input<br>Frequency Divider0 output pin<br>NC<br>LCD power supply pin<br>NC |

|         |        |        | FCLK0            | 0        | Frequency Divider0 output pin                                                                      |

| 45      |        |        |                  |          | NC                                                                                                 |

| 46      | 32     | 21     | V <sub>LCD</sub> | Р        | LCD power supply pin                                                                               |

| 47      |        |        |                  |          | NC                                                                                                 |

|         |        |        | PD.13            | I/O      | General purpose digital I/O pin                                                                    |

|         |        |        | LCD_V1           | I        | Input pin of the 1 <sup>st</sup> most positive LCD<br>level at 100-pin                             |

| 48      | 33     | 22     | LCD_V1           | I        | Input pin of the 1 <sup>st</sup> most positive LCD<br>level at 64-pin                              |

|         |        |        | LCD_V1           | I        | Input pin of the 1 <sup>st</sup> most positive LCD<br>level at 48-pin                              |

|         |        |        | INT1             | I        | External interrupt 1 input pin                                                                     |

|         |        |        | PD.14            | I/O      | General purpose digital I/O pin                                                                    |

|         |        |        | LCD_V2           | I        | Input pin of the 2 <sup>nd</sup> most positive LCD<br>level at 100-pin                             |

| 49      | 34     | 23     | LCD_V2           | I        | Input pin of the 2 <sup>nd</sup> most positive LCD<br>level at 64-pin                              |

|         |        |        | LCD_V2           | I        | Input pin of the 2 <sup>nd</sup> most positive LCD<br>level at 48-pin                              |

|         |        |        | PD.15            | I/O      | General purpose digital I/O pin                                                                    |

|         |        |        | LCD_V3           | I        | Input pin of the 3 <sup>rd</sup> most positive LCD<br>level at 100-pin                             |

| 50      | 35     | 24     | LCD_V3           | I        | Input pin of the 3 <sup>rd</sup> most positive LCD<br>level at 64-pin                              |

|         |        |        | LCD_V3           | I        | Input pin of the 3 <sup>rd</sup> most positive LCD<br>level at 48-pin                              |

| Pin No. |                            |                                 |             |                                 |                                                                                         |

|---------|----------------------------|---------------------------------|-------------|---------------------------------|-----------------------------------------------------------------------------------------|

| 100-pin | 64-pin                     | 48-pin                          | -Pin Name   | Pin Type                        | Description                                                                             |

|         |                            |                                 | PA.8        | I/O                             | General purpose digital I/O pin                                                         |

| 84      |                            |                                 | SC0_PWR     | 0                               | SmartCard0 Power pin                                                                    |

|         |                            |                                 | PA.9        | I/O                             | General purpose digital I/O pin                                                         |

| 85      |                            |                                 | SC0_RST     | 0                               | SmartCard0 RST pin                                                                      |

|         |                            |                                 | PA.10       | I/O                             | General purpose digital I/O pin                                                         |

| 86      |                            |                                 | SC0_CLK     | 0                               | SmartCard0 clock pin<br>(SC0_UART_TXD)                                                  |

|         |                            |                                 | PA.11       | I/O                             | General purpose digital I/O pin                                                         |

| 87      | 87                         |                                 | SC0_DAT     | I/O                             | SmartCard0 DATA<br>pin(SC0_UART_RXD)                                                    |

|         |                            |                                 | STADC       | I                               | ADC external trigger input.                                                             |

|         |                            |                                 | PA.12       | I/O                             | General purpose digital I/O pin                                                         |

|         | 56 45                      | LCD_SEG19                       | 0           | LCD segment output 19 at 48-pin |                                                                                         |

| 88      |                            | 45                              | UART0_TXD   | o                               | UART0 Data transmitter output pin (This<br>pin could be modulated with PWM0<br>output.) |

|         |                            |                                 | SPI1_MOSI0  | I/O                             | SPI1 1 <sup>st</sup> MOSI (Master Out, Slave In) pir                                    |

|         |                            |                                 | I2C0_SCL    | I/O                             | I <sup>2</sup> C 0 clock pin                                                            |

|         |                            |                                 | ACMP1_P     | AI                              | Comparator1 P-end input                                                                 |

|         |                            |                                 | PA.13       | I/O                             | General purpose digital I/O pin                                                         |

|         |                            |                                 | LCD_SEG18   | 0                               | LCD segment output 18 at 48-pin                                                         |

|         | -7                         | 40                              | UART0_RXD   | I                               | UART0 Data receiver input pin                                                           |

| 89      | 57                         | 46                              | SPI1_MISO0  | I/O                             | SPI1 1 <sup>st</sup> MISO (Master In, Slave Out) pir                                    |

|         | 12C0.                      | I2C0_SDA                        | I/O         | I <sup>2</sup> C0 data I/O pin  |                                                                                         |

|         |                            |                                 | ACMP1_N     | AI                              | Comparator1 N-end input                                                                 |

|         |                            |                                 | PA.14       | I/O                             | General purpose digital I/O pin                                                         |

|         |                            |                                 | ACMP0_CHDIS | 0                               | Comparator0 charge/discharge path                                                       |

| 00      | 50                         | 47                              | LCD_SEG31   | 0                               | LCD segment output 31 at 64-pin                                                         |

| 90      | 58                         | 47                              | LCD_SEG17   | 0                               | LCD segment output 17 at 48-pin                                                         |

|         |                            |                                 | SPI1_CLK    | I/O                             | SPI1 serial clock pin                                                                   |

|         |                            |                                 | I2C1_SCL    | I/O                             | I <sup>2</sup> C1 clock pin                                                             |

|         |                            |                                 | PA.15       | I/O                             | General purpose digital I/O pin                                                         |

| 01      | 50                         | 40                              | LCD_SEG30   | 0                               | LCD segment output 30 at 64-pin                                                         |

| 91      | 59 48 LCD_SEG16 <b>O</b> L | LCD segment output 16 at 48-pin |             |                                 |                                                                                         |

|         |                            |                                 | SPI1_SS0    | I/O                             | SPI1 1 <sup>st</sup> slave select pin                                                   |

| Pin No. |        |        | Pin Name        | Pin Type                      | Description                                                                             |

|---------|--------|--------|-----------------|-------------------------------|-----------------------------------------------------------------------------------------|

| 100-pin | 64-pin | 48-pin |                 | Pin Type                      | Description                                                                             |

|         |        |        | I2C1_SDA        | I/O                           | I <sup>2</sup> C1 data I/O pin                                                          |

|         |        |        | ACMP1_OUT       | 0                             | Comparator1 output                                                                      |

|         |        |        | TC3             | I                             | Timer3 capture input                                                                    |

|         |        |        | PB.0            | I/O                           | General purpose digital I/O pin                                                         |

|         |        |        | LCD_SEG29       | 0                             | LCD segment output 29 at 64-pin                                                         |

| 92      | 2 60   |        | UART0_TXD       | ο                             | UART0 Data transmitter output pin (This<br>pin could be modulated with PWM0<br>output.) |

|         |        | FCLK1  | 0               | Frequency Divider1 output pin |                                                                                         |

|         |        |        | PB.1            | I/O                           | General purpose digital I/O pin                                                         |

|         |        |        | LCD_SEG28       | 0                             | LCD segment output 28 at 64-pin                                                         |

| 93      | 61     |        | UART0_RXD       | I                             | UART0 Data receiver input pin                                                           |

|         |        |        | TC2             | I                             | Timer 2 capture input                                                                   |

|         |        |        | INT1            | I                             | External interrupt1 input pin                                                           |

|         |        |        | PB.2            | I/O                           | General purpose digital I/O pin                                                         |

|         |        |        | LCD_SEG27       | 0                             | LCD segment output 27 at 64-pin                                                         |

|         |        |        | UART0_RTSn      | 0                             | UART0 Request to Send output pin                                                        |

| 94      | 62     |        | SPI1_MOSI1      | I/O                           | SPI1 2 <sup>nd</sup> MOSI (Master Out, Slave In) pin                                    |

|         |        |        | I2C0_SCL        | 0                             | I <sup>2</sup> C0 clock pin                                                             |

|         |        |        | TM3             | I/O                           | Timer3 external counter input or Timer3 toggle out.                                     |

|         |        |        | PB.3            | I/O                           | General purpose digital I/O pin                                                         |

|         |        |        | LCD_SEG26       | 0                             | LCD segment output 26 at 64-pin                                                         |

|         |        |        | UART0_CTSn      | I                             | UART0 Clear to Send input pin                                                           |

| 95      | 63     |        | SPI1_MISO1      | I/O                           | SPI1 2 <sup>nd</sup> MISO (Master In, Slave Out) pin                                    |

|         |        |        | I2C0_SDA        | I/O                           | I <sup>2</sup> C0 data I/O pin                                                          |

|         |        |        | TM2             | I/O                           | Timer2 external counter input or Timer2 toggle out.                                     |

| 96      |        |        | V <sub>DD</sub> | Р                             | Power supply for I/O ports and LDO source                                               |

| 97      |        |        | V <sub>SS</sub> | G                             | Ground for digital circuit                                                              |

|         |        |        | PB.4            | I/O                           | General purpose digital I/O pin                                                         |

| 98      |        |        | UART1_RTSn      | 0                             | UART1 Request to Send output pin                                                        |

|         |        |        | SPI1_MISO1      | I/O                           | SPI1 2 <sup>nd</sup> MISO (Master In, Slave Out) pin                                    |

| 99      |        |        | PB.5            | I/O                           | General purpose digital I/O pin                                                         |

| 33      |        |        | LCD_SEG35       | 0                             | LCD segment output 35 at 100-pin                                                        |

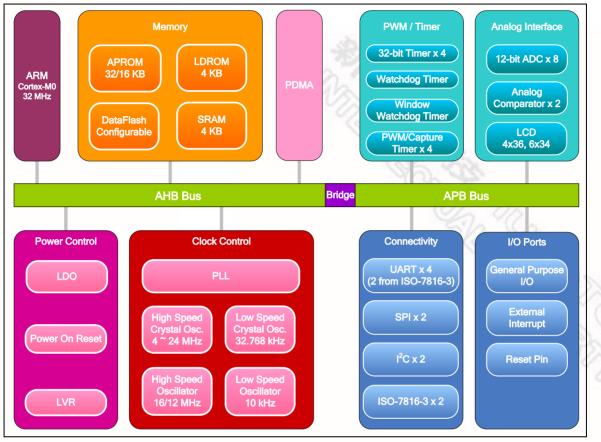

### 5.2 Nano112 Block Diagram

### Figure 5-2 NuMicro<sup>™</sup> Nano112 Block Diagram

### 6.3 Nested Vectored Interrupt Controller (NVIC)

#### 6.3.1 Overview

The Cortex-M0 provides an interrupt controller as an integral part of the exception mode, named as "Nested Vectored Interrupt Controller (NVIC)". It is closely coupled to the processor kernel and provides following features:

#### 6.3.2 Features

- Nested and Vectored interrupt support

- Automatic processor state saving and restoration

- Dynamic priority changing

- Reduced and deterministic interrupt latency

The NVIC prioritizes and handles all supported exceptions. All exceptions are handled in "Handler Mode". This NVIC architecture supports 32 (IRQ[31:0]) discrete interrupts with 4 levels of priority. All of the interrupts and most of the system exceptions can be configured to different priority levels. When an interrupt occurs, the NVIC will compare the priority of the new interrupt to the current running one's priority. If the priority of the new interrupt is higher than the current one, the new interrupt handler will override the current handler.

When any interrupts is accepted, the starting address of the interrupt service routine (ISR) is fetched from a vector table in memory. There is no need to determine which interrupt is accepted and branch to the starting address of the correlated ISR by software. While the starting address is fetched, NVIC will also automatically save processor state including the registers "PC, PSR, LR, R0~R3, R12" to the stack. At the end of the ISR, the NVIC will restore the mentioned registers from stack and resume the normal execution. Thus it will take less and deterministic time to process the interrupt request.

The NVIC supports "Tail Chaining" which handles back-to-back interrupts efficiently without the overhead of states saving and restoration and therefore reduces delay time in switching to pending ISR at the end of current ISR. The NVIC also supports "Late Arrival" which improves the efficiency of concurrent ISRs. When a higher priority interrupt request occurs before the current ISR starts to execute (at the stage of state saving and starting address fetching), the NVIC will give priority to the higher one without delay penalty. Thus it advances the real-time capability.

For more detailed information, please refer to the "ARM<sup>®</sup> Cortex<sup>™</sup>-M0 Technical Reference Manual" and "ARM<sup>®</sup> v6-M Architecture Reference Manual".

### 6.8.2 Features

- Supports four PDMA channels (CH1 ~ CH4) and one CRC channel. Each PDMA channel can support a unidirectional transfer

- AMBA AHB master/slave interface compatible, for data transfer and register read/write

- Hardware round robin priority scheme. DMA channel 1 has the highest priority and channel 4 has the lowest priority

- PDMA

- Peripheral-to-memory, memory-to-peripheral, and memory-to-memory transfer

- Supports word boundary address

- Supports word alignment transfer length in memory-to-memory mode

- Supports word/half-word/byte alignment transfer length in peripheral-to-memory and memory-to-peripheral mode

- Supports word/half-word/byte transfer data width from/to peripheral

- Supports address direction: increment, fixed, and wrap around

- Supports time-out function in all channel

- Cyclic Redundancy Check (CRC)

- Supports four common polynomials CRC-CCITT, CRC-8, CRC-16, and CRC-32

- CRC-CCITT: X16 + X12 + X5 + 1

- CRC-8: X8 + X2 + X + 1

- CRC-16: X16 + X15 + X2 + 1

- CRC-32: X32 + X26 + X23 + X22 + X16 + X12 + X11 + X10 + X8 + X7 + X5 + X4 + X2 + X + 1

- Programmable seed value

- Supports programmable order reverse setting for input data and CRC checksum

- Supports programmable 1's complement setting for input data and CRC checksum

- Supports CPU mode or DMA transfer mode

- Supports 8/16/32-bit of data width in CRC CPU mode

- 8-bit write mode: 1-AHB clock cycle operation

- 16-bit write mode: 2-AHB clock cycle operation

- 32-bit write mode: 4-AHB clock cycle operation

- Supports byte alignment transfer length in CRC DMA mode

### 6.9 Timer Controller

#### 6.9.1 Overview

This chip is equipped with four timer modules including TIMER0, TIMER1, TIMER2 and TIMER3, which allow user to easily implement a counting scheme or timing control for applications. The timer can perform functions like frequency measurement, event counting, interval measurement, clock generation, delay timing, and so on. The timer can generate an interrupt signal upon timeout, or provide the current value of count during operation.

#### 6.9.2 Features

- Independent Clock Source for each Timer (TMRx\_CLK, x= 0, 1,2,3)

- Time-out period = (Period of timer clock input) \* (8-bit pre-scale counter + 1) \* (24-bit TCMP)

- Counting cycle time = (1 / TMRx\_CLK) \* (2^8) \* (2^24)

- Internal 8-bit pre-scale counter

- Internal 24-bit up counter is readable through TDR (Timer Data Register)

- Supports One-shot, Periodic, Output Toggle and Continuous Counting Operation mode

- Supports external pin capture for interval measurement

- Supports external pin capture for timer counter reset

- Supports Inter-Timer trigger

- Supports event generator in TIMER 0 and TIMER 2 to generate event to TIMER1 and TIMER3, respectively.

- Supports Internal trigger event to ADC and PDMA

### 6.10.2 Features

6.10.2.1 PWM Function:

- PWM controllers has 4 independent PWM outputs, CH0~CH3, or as 2 complementary PWM pairs, (CH0, CH1), (CH2, CH3) with 2 programmable dead-zone generators

- Up to 4 PWM channels or 2 PWM paired channels

- Up to 16 bits PWM counter width

- PWM Interrupt request synchronous with PWM period

- Single-shot or Continuous mode

- Two Dead-Zone generators

#### 6.10.2.2 Capture Function:

- Timing control logic shared with PWM timer.

- 4 Capture input channels shared with 4 PWM output channels.

- Each channel supports one rising latch register CRL (PWM\_CRL0[15:0]), one falling latch register CFL (PWM\_CFL0[15:0]) and Capture interrupt flag CAPIF0 (PWM\_CAPINTSTS[0]).

- Four 16-bit counters for four capture channels or two 32-bit counter for two capture channels when cascade is enabled: when CH01CASKEN (PWM\_CAPCTL[13]) is set, the original 16-bit counter of channel 1 will combine with channel 0's 16 bit counter for channel 0 input capture counting and so does CH23CASKEN(PWM\_CAPCTL[29]) for channel 2, 3

- Supports PDMA transfer function for PWM channel 0, 2

### 6.16 I<sup>2</sup>C

### 6.16.1 Overview

$I^2C$  is a two-wire, bi-directional serial bus that provides a simple and efficient method of data exchange between devices. The  $I^2C$  standard is a true multi-master bus including collision detection and arbitration that prevents data corruption if two or more masters attempt to control the bus simultaneously. Serial, 8-bit oriented bi-directional data transfers can be made up to 1 Mbps.

Data is transferred between a Master and a Slave synchronously to SCL on the SDA line on a byte-by-byte basis. Each data byte is 8-bit long. There is one SCL clock pulse for each data bit with the MSB being transmitted first. An acknowledge bit follows each transferred byte.

A transition on the SDA line while SCL is high is interpreted as a command (START or STOP). Each bit is sampled during the high period of SCL; therefore, the SDA line may be changed only during the low period of SCL and must be held stable during the high period of SCL.

The controller's on-chip  $I^2C$  logic provides the serial interface that meets the  $I^2C$  bus standard mode specification. The  $I^2C$  controller handles byte transfers autonomously. Pull up resistor is needed for  $I^2C$  operation as these are open drain pins.

The  $l^2C$  controller is equipped with two slave address registers. The contents of the registers are irrelevant when  $l^2C$  is in Master mode. In the Slave mode, the seven most significant bits must be loaded with the user's own slave address. The  $l^2C$  hardware will react if the contents of I2CADDR are matched with the received slave address.

This controller supports the "General Call (GC)" function. If the GCALL (I2CSADDR[0]) bit is set this controller will respond to General Call address (00H). Clear GC bit to disable general call function. When GCALL bit is set and the  $I^2C$  is in Slave mode, it can receive the general call address which is equal to 00H after master sends general call address to the  $I^2C$  bus, then it will follow status of GC mode. If it is in Master mode, the ACK bit must be cleared when it sends general call address of 00H to the  $I^2C$  bus.

The  $I^2C$ -bus controller supports multiple address recognition with two address mask register. When the bit in the address mask register is set to one, it means the received corresponding address bit is don't-care. If the bit is set to 0, that means the received corresponding register bit should be exact the same as address register.

### 6.16.2 Features

- Supports two I2C channels and both of them can acts as Master or Slave mode

- Bidirectional data transfer between masters and slaves

- Multi-master bus (no central master)

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus

- Serial clock synchronization allows devices with different bit rates to communicate via one serial bus

- Serial clock synchronization can be used as a handshake mechanism to suspend and resume serial transfer

- One built-in 14-bit time-out counter requesting the I<sup>2</sup>C interrupt if the I<sup>2</sup>C bus hangs up and timer-out counter overflows.

- Programmable clock divider allows versatile rate control

- Supports 7-bit addressing mode

### 6.20 Analog Comparator Controller (ACMP)

#### 6.20.1 Overview

The Nano112 series contains two comparators. The comparator output is logic 1 when positive input is greater than negative input; otherwise, the output is 0. Each comparator can be configured to generate an interrupt when the comparator output value changes. The comparator ACMP0 can be used as normal comparator or it can emulate ADC function. The comparator ACMP1 can be used as normal comparator only.

### 6.20.2 Features

- Analog input voltage range: 0 ~ AV<sub>DD</sub>

- Supports hysteresis function

- Supports wake-up function

- Comparator ACMP0 supports

- 4 positive sources(ACMP0\_Px)

- PA.1, PA.2, PA.3, or PA.4

- 4 negative sources

- PA.5 (ACMP0\_N)

- Comparator Reference Voltage (CRV)

- Int\_V<sub>REF</sub>

- AGND

- Comparator ACMP1 supports

- 1 positive source

- PA.12(ACMP1\_P)

- ♦ 4 negative sources

- PA.13(ACMP1\_N)

- Comparator Reference Voltage (CRV)

- Int\_V<sub>REF</sub>

- AGND

- Comparator ACMP0 supports three operation modes:

- Normal Comparator mode

- Single Slope ADC mode: Resistance measurement (e.g. PTC, NTC, PT1000)

- Supports to measure 7 channels resistor

- Sigma-Delta ADC mode

- Supports up to 4 channel voltage input from ACMP0\_Px

| Operating Current                           | I <sub>IDLE131</sub> | 4.2  | mA | 3.3 V           | х               | 16 MHz        | х   | V                  |

|---------------------------------------------|----------------------|------|----|-----------------|-----------------|---------------|-----|--------------------|

| Idle Mode                                   | I <sub>IDLE141</sub> | 0.7  | mA | 3.3 V           | х               | 16 MHz        | Х   | х                  |

| HCLK =16 MHz<br>V <sub>LDO1</sub> =1.6 V    | I <sub>IDLE151</sub> | 4.1  | mA | 1.8 V           | х               | 16 MHz        | Х   | V                  |

| V <sub>LDO1</sub> -1.0 V                    | I <sub>IDLE161</sub> | 0.7  | mA | 1.8 V           | х               | 16 MHz        | Х   | х                  |

| Operating Current                           | I <sub>IDLE132</sub> | 2.9  | mA | 3.3 V           | х               | 12 MHz        | Х   | V                  |

| Idle Mode                                   | I <sub>IDLE142</sub> | 0.6  | mA | 3.3 V           | x               | 12 MHz        | Х   | х                  |

| HCLK =12 MHz<br>V <sub>LDO1</sub> =1.6 V    | I <sub>IDLE152</sub> | 2.9  | mA | 1.8 V           | x               | 12 MHz        | Х   | V                  |

| V <sub>LDO1</sub> =1.0 V                    | I <sub>IDLE162</sub> | 0.6  | mA | 1.8 V           | x               | 12 MHz        | Х   | х                  |

| Operating Current                           | I <sub>IDLE13</sub>  | 2.8  | mA | 3.3 V           | 12 MHz          | x             | x   | V                  |

| Idle Mode                                   | I <sub>IDLE14</sub>  | 0.8  | mA | 3.3 V           | 12 MHz          | x             | x   | х                  |

| HCLK =12 MHz                                | I <sub>IDLE15</sub>  | 2.8  | mA | 1.8 V           | 12 MHz          | x             | х   | V                  |

| V <sub>LDO1</sub> =1.6 V                    | I <sub>IDLE16</sub>  | 0.8  | mA | 1.8 V           | 12 MHz          | х             | х   | x                  |

| Operating Current                           | I <sub>IDLE17</sub>  | 1.0  | mA | 3.3 V           | 4 MHz           | х             | х   | v                  |

| Idle Mode                                   | I <sub>IDLE18</sub>  | 0.3  | mA | 3.3 V           | 4 MHz           | х             | х   | x                  |

| HCLK =4 MHz                                 | I <sub>IDLE19</sub>  | 1.0  | mA | 1.8 V           | 4 MHz           | х             | х   | v                  |

| V <sub>LDO1</sub> =1.6 V                    | I <sub>IDLE20</sub>  | 0.3  | mA | 1.8 V           | 4 MHz           | х             | Х   | x                  |

| On and the a Quantum t                      | I <sub>IDLE21</sub>  | 96   | uA | V <sub>DD</sub> | LXT (kHz)       | HIRC          | PLL | All digital module |

| Operating Current<br>Idle Mode              |                      |      |    | 3.3 V           | 32.768          | Х             | Х   | V                  |

| HCLK =32.768 kHz                            | I <sub>IDLE22</sub>  | 90   | uA | 3.3 V           | 32.768          | х             | Х   | х                  |

| V <sub>LDO1</sub> =1.6 V                    | I <sub>IDLE23</sub>  | 92   | uA | 1.8 V           | 32.768          | х             | Х   | V                  |

|                                             | I <sub>IDLE24</sub>  | 86   | uA | 1.8 V           | 32.768          | х             | Х   | х                  |

|                                             | I <sub>IDLE25</sub>  | 90   | uA | V <sub>DD</sub> | HXT/LXT         | LIRC<br>(kHz) | PLL | All digital module |

| Operating Current<br>Idle Mode              |                      |      |    | 3.3 V           | Х               | 10            | Х   | V                  |

| HCLK =10 kHz                                | I <sub>IDLE26</sub>  | 89   | uA | 3.3 V           | х               | 10            | Х   | Х                  |

| V <sub>LDO1</sub> =1.6 V                    | I <sub>IDLE27</sub>  | 86   | uA | 1.8 V           | х               | 10            | Х   | V                  |

|                                             | I <sub>IDLE28</sub>  | 84   | uA | 1.8 V           | х               | 10            | Х   | х                  |

| N.                                          | I <sub>PWD1</sub>    | 0.65 | uA | V <sub>DD</sub> | HXT/HIRC<br>PLL | LXT<br>(kHz)  | RTC | RAM retensi        |

| Standby Current                             |                      |      |    | 3.3 V           | Х               | Х             | Х   | V                  |

| Power-down Mode<br>V <sub>LD01</sub> =1.6 V | I PWD2               | 0.65 | uA | 1.8 V           | х               | х             | х   | V                  |

| 52250                                       | I <sub>PWD3</sub>    | 1.5  | uA | 3.3 V           | х               | 32.768        | V   | V                  |

| " (Da Da                                    | I <sub>PWD4</sub>    | 1.5  | uA | 1.8 V           | Х               | 32.768        | V   | V                  |

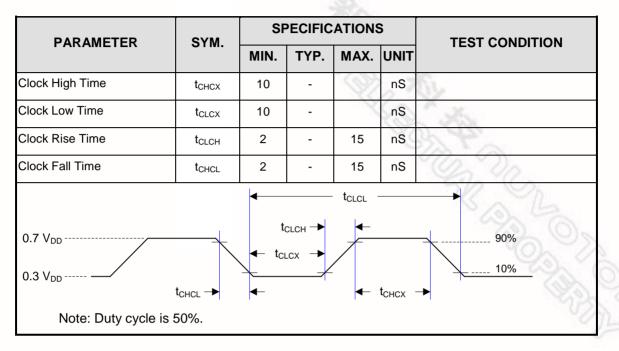

### 9.3 AC Electrical Characteristics

### 9.3.1 External Input Clock

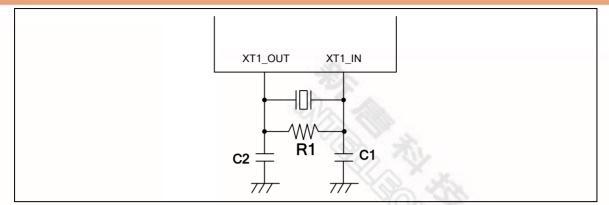

### 9.3.2 External 4~24 MHz XTAL Oscillator

| PARAMETER            | SYM.             | SF   | PECIFIC | ATIONS | 6    | TEST CONDITION    |  |

|----------------------|------------------|------|---------|--------|------|-------------------|--|

|                      | 5 T WI.          | MIN. | TYP.    | MAX.   | UNIT |                   |  |

| Oscillator frequency | f <sub>HXT</sub> | 4    | 12      | 24     | MHz  | VDD = 1.8V ~ 3.6V |  |

| Temperature          | T <sub>HXT</sub> | -40  | -       | +85    | °C   |                   |  |

| Operating current    | I <sub>HXT</sub> |      | 0.3     |        | mA   | VDD = 3.0V        |  |

### 9.3.2.1 Typical Crystal Application Circuits

| CRYSTAL       | C1   | C2   | R1      |

|---------------|------|------|---------|

| 4MHz ~ 24 MHz | 20pF | 20pF | without |

| C D           |      | L    |         |

|               |      |      |         |

|               |      |      |         |

|               |      |      |         |

|               |      |      |         |

|               |      |      |         |

Figure 9-1 Typical Crystal Application Circuit

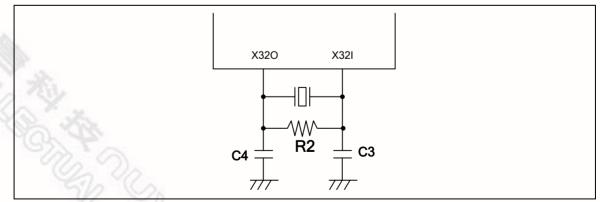

### 9.3.3 External 32.768 kHz Crystal

| PARAMETER            | SPECIFICATIONS   |      |        |      |      | TEST CONDITION    |

|----------------------|------------------|------|--------|------|------|-------------------|

|                      |                  | MIN. | TYP.   | MAX. | UNIT |                   |

| Oscillator frequency | f <sub>LXT</sub> |      | 32.768 |      | kHz  | VDD = 1.8V ~ 3.6V |

| Temperature          | T <sub>LXT</sub> | -40  | -      | +85  | °C   | 10                |

| Operating current    | I <sub>LXT</sub> |      | 1      |      | μΑ   | VDD = 3.0V        |

### 9.3.3.1 Typical Crystal Application Circuits

| CRYSTAL    | C3   | C4   | R2      |

|------------|------|------|---------|

| 32.768 kHz | 20pF | 20pF | without |

Figure 9-2 Typical Crystal Application Circuit

### **11 REVISION HISTORY**

| Date       | Revision | Description                                                                                                                                                                                                                                                                                                                                                                   |

|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2014.03.28 | 1.00     | 1. Initial release                                                                                                                                                                                                                                                                                                                                                            |

| 2014.05.08 | 1.01     | 1. Modified some typos and format.                                                                                                                                                                                                                                                                                                                                            |

| 2014.09.02 | 1.02     | <ol> <li>Modified the pin description for LCD_Vx in section 4.4.</li> <li>Modified all PWM1 group to PWM0 group in section 6.10.</li> <li>Modified "PWM1 channel 2 and 3" to "PWM0 channel 2 and 3" in section 6.10.</li> <li>Modified some typos and format.</li> </ol>                                                                                                      |

| 2015.01.15 | 1.03     | <ol> <li>Updated ADC channel number in NANO102 feature list in Chapter 2.</li> <li>Corrected typo in NANO102 64-pin sequence in section 4.4.</li> <li>Updated all power related pins from "VDD, VSS, AVDD, AVSS, VTEMP and VLCD" to<br/>"V<sub>DD</sub>, V<sub>SS</sub>, AV<sub>DD</sub>, AV<sub>SS</sub>, V<sub>TEMP</sub> and V<sub>LCD</sub>" in the Datashhet.</li> </ol> |