#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                   |

|----------------------------|------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                                          |

| Core Size                  | 32-Bit Single-Core                                                                       |

| Speed                      | 32MHz                                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                        |

| Number of I/O              | 80                                                                                       |

| Program Memory Size        | 32KB (32K x 8)                                                                           |

| Program Memory Type        | FLASH                                                                                    |

| EEPROM Size                | -                                                                                        |

| RAM Size                   | 8K x 8                                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                              |

| Data Converters            | A/D 8x12b                                                                                |

| Oscillator Type            | Internal                                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                        |

| Mounting Type              | Surface Mount                                                                            |

| Package / Case             | 100-LQFP                                                                                 |

| Supplier Device Package    | 100-LQFP (14x14)                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/nano112vc2an |

|                            |                                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Table of Contents

|       | NERAL DESCRIPTION                             |

|-------|-----------------------------------------------|

| 2 FE  | ATURES                                        |

| 2.1   | Nano102 Features – Base Line10                |

| 2.2   | Nano112 Features – LCD Line15                 |

| 3 AB  | BREVIATIONS                                   |

| 4 PA  | RTS INFORMATION LIST AND PIN CONFIGURATION    |

| 4.1   | NuMicro™ Nano102/112 Series Selection Code23  |

| 4.2   | NuMicro™ Nano112 Products Selection Guide23   |

| 4.2.1 | NuMicro™ Nano102 Base Line Selection Guide    |

| 4.2.2 | NuMicro™ Nano112 LCD Line Selection Guide24   |

| 4.3   | Pin Configuration25                           |

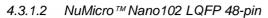

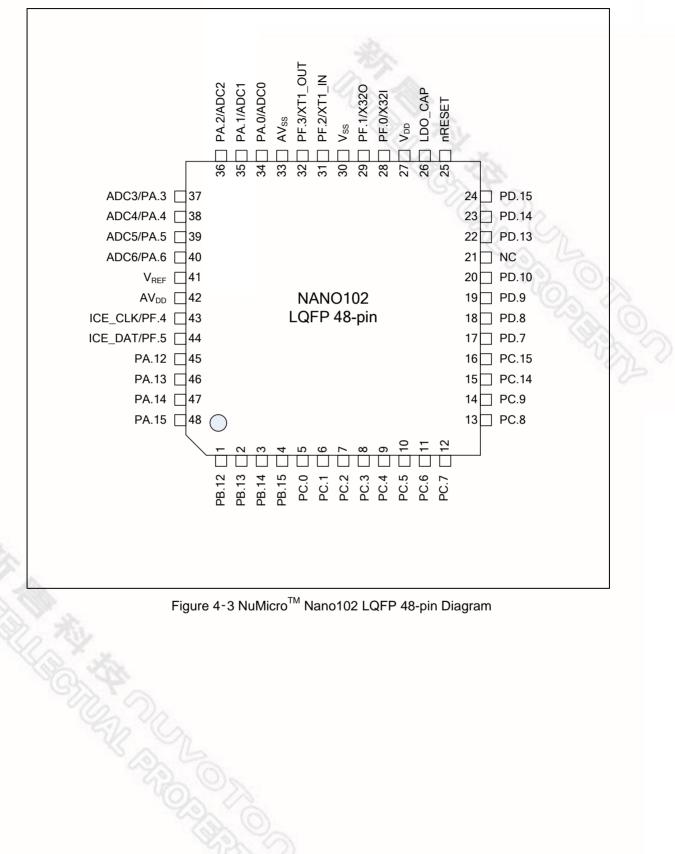

| 4.3.1 | NuMicro™ Nano102 Pin Diagrams                 |

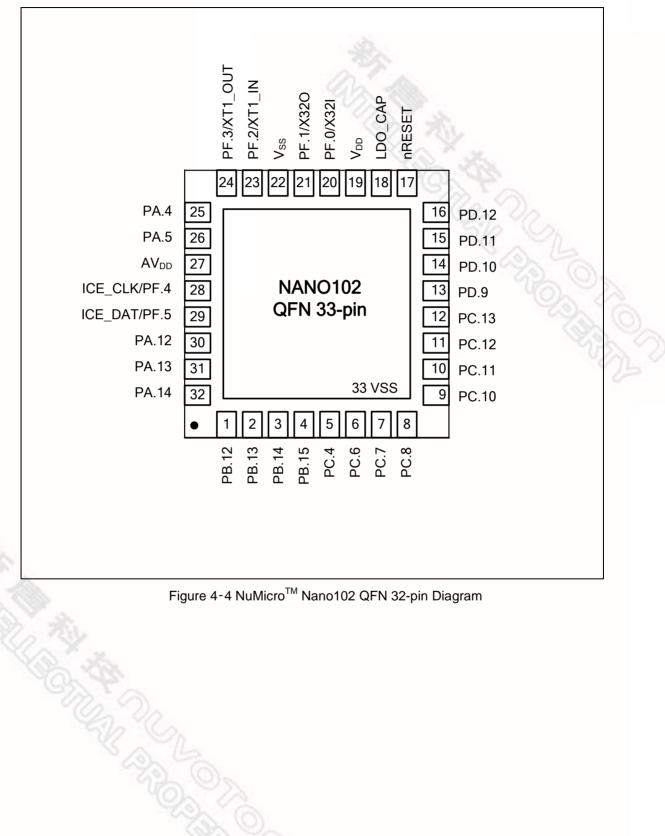

| 4.3.2 | NuMicro™ Nano112 Pin Diagrams                 |

| 4.4   | Pin Description                               |

| 4.4.1 | NuMicro™ Nano102 Pin Description              |

| 4.4.2 | NuMicro™ Nano112 Pin Description              |

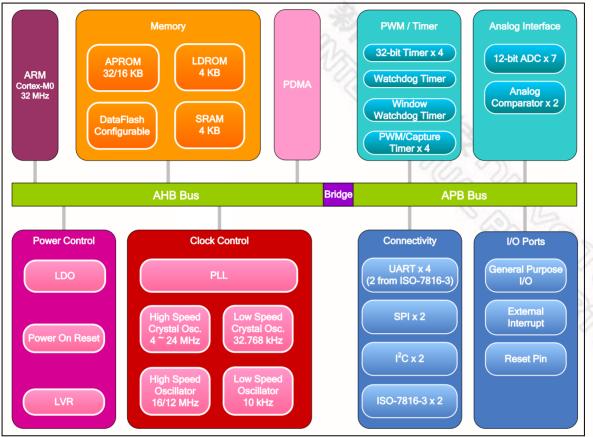

| 5 BL  | OCK DIAGRAM                                   |

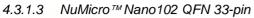

| 5.1   | Nano102 Block Diagram51                       |

| 5.2   | Nano112 Block Diagram52                       |

| 6 FU  | NCTIONAL DESCRIPTION                          |

| 6.1   | ARM® Cortex™-M0 Core53                        |

| 6.2   | Memory Organization                           |

| 6.2.1 | Overview                                      |

| 6.3   | Nested Vectored Interrupt Controller (NVIC)56 |

| 6.3.1 | Overview                                      |

| 6.3.2 | Features                                      |

| 6.4   | System Manager                                |

| 6.4.1 | Overview                                      |

| 6.4.2 | Features                                      |

| 6.5   | Clock Controller                              |

| 6.5.1 | Overview                                      |

| 6.5.2 | Features                                      |

| 6.6   | Flash Memory Controller (FMC)                 |

|       |                                               |

### 2.2 Nano112 Features – LCD Line

- Low Supply Voltage Range: 1.8 V to 3.6 V

- Ultra-Low Power Consumption

- Operation mode : 150 uA/MHz

- Power-down mode : 1.5 uA (RTC on, RAM retention)

- Deep power down mode : 650 nA (RAM retention)

- Fast Wake-Up From Standby Mode : Less than 6 µs

- Core

- ARM<sup>®</sup> Cortex<sup>™</sup>-M0 core running up to 32 MHz

- One 24-bit system timer

- Supports Low Power Sleep mode

- Single-cycle 32-bit hardware multiplier

- NVIC for the 32 interrupt inputs, each with 4-levels of priority

- Serial Wire Debug supports with 2 watchpoints/4 breakpoints

- Flash EPROM Memory

- Runs up to 32 MHz with zero wait state for discontinuous address read access.

- 16/32 Kbytes application program memory (APROM)

- ◆ 4 Kbytes In System Programming (ISP) loader program memory (LDROM)

- Programmable data flash start address and memory size with 512 bytes page erase unit

- In System Program (ISP)/In Application Program (IAP) to update on chip Flash EPROM

- SRAM Memory

- ♦ 4/8 Kbytes embedded SRAM

- Supports DMA mode

- DMA : Supports 5 channels: 4 PDMA channels, and one CRC channel

- PDMA

- Peripheral-to-memory, memory-to-peripheral, and memory-to-memory transfer

- Supports word boundary address

- Supports word alignment transfer length in memory-to-memory mode

- Supports word/half-word/byte alignment transfer length in peripheral-tomemory and memory-to-peripheral mode

- Supports word/half-word/byte transfer data width from/to peripheral

- Supports address direction: increment, fixed, and wrap around

- ♦ CRC

- Supports four common polynomials CRC-CCITT, CRC-8, CRC-16, and CRC-32

- CRC-CCITT: X<sup>16</sup> + X<sup>12</sup> + X<sup>5</sup> + 1

- CRC-8: X<sup>8</sup> + X<sup>2</sup> + X + 1

- CRC-16: X<sup>16</sup> + X<sup>15</sup> + X<sup>2</sup> + 1

- CRC-32:  $X^{32} + X^{26} + X^{23} + X^{22} + X^{16} + X^{12} + X^{11} + X^{10} + X^8 + X^7 + X^5 + X^4 + X^2 + X + 1$

- Clock Control

- Flexible selection for different applications

- Built-in 12/16 MHz OSC, can be trimmed to 1 % deviation within all temperature range when turning on auto-trim function (system must have external 32.768 kHz crystal input) otherwise 12/16 MHz OSC has 2 % deviation within all temperature range.

- Low power 10 kHz OSC for watchdog and low power system operation

- Supports one PLL, up to 32 MHz, for high performance system operation

- External 4~24 MHz crystal input for precise timing operation

- External 32.768 kHz crystal input for RTC function and low power system operation

- GPIO

- Three I/O modes:

- Push-Pull output

- Open-Drain output

- Input only with high impendence

- All inputs with Schmitt trigger

- I/O pin configured as interrupt source with edge/level setting

- Supports High Driver and High Sink I/O mode

- Supports input 5V tolerance, except PA.0 ~ PA.7, PA.12, PA.13, P.0(X32I), PF.1(X32O)

- Timer

- Supports 4 sets of 32-bit timers, each with 24-bit up-timer and one 8-bit prescale counter

- Independent Clock Source for each timer

- Provides one-shot, periodic, output toggle and continuous operation modes

- Internal trigger event to ADC and PDMA

- Supports PDMA mode

- Wake system up from Power-down mode

- Watchdog Timer

- Clock Source from LIRC (Internal 10 kHz Low Speed Oscillator Clock)

- Selectable time-out period from 1.6 ms ~ 26 sec (depending on clock source)

- ♦ Interrupt or reset selectable when watchdog time-out

- Wake system up from Power-down mode

- Window Watchdog Timer(WWDT)

- 6-bit down counter and 6-bit compare value to make the window period flexible

Page 16 of 100

- Selectable WWDT clock pre-scale counter to make WWDT time-out interval variable.

- RTC

- Supports software compensation by setting frequency compensate register (FCR)

- Supports RTC counter (second, minute, hour) and calendar counter (day, month, year)

- Supports Alarm registers (second, minute, hour, day, month, year)

- Selectable 12-hour or 24-hour mode

- Automatic leap year recognition

- Supports periodic time tick interrupt with 8 periodic options 1/128, 1/64, 1/32, 1/16, 1/8, 1/4, 1/2 and 1 second

- Wake system up from Power-down mode

- Supports 80 bytes spare registers and a snoop pin to clear the content of these spare registers

- Supports 1, 1/2, 1/4, 1/8, 1/16 Hz clock output

- PWM/Capture

- Supports 1 PWM module with two 16-bit PWM generators

- Provides four PWM outputs or two complementary paired PWM outputs

- Each PWM generator equipped with one clock divider, one 8-bit prescaler, two clock selectors, and one Dead-zone generator for complementary paired PWM

- (Shared with PWM timers) with four 16-bit digital capture timers provides four rising/ falling/both capture inputs.

- Supports Capture interrupt

- UART

- Up to 1 Mbit/s baud rate and support 9600 baud rate @ 32kHz, low power mode

- Up to two 16-byte FIFO UART controllers

- UART ports with flow control (TX, RX, CTSn and RTSn)

- Supports IrDA (SIR) function

- Supports LIN function

- Supports RS-485 9 bit mode and direction control (Low Density Only)

- Programmable baud rate generator

- Supports PDMA mode

- Wake system up (CTS, received data or RS-485 address matched) from Powerdown mode

- SPI

- Up to two sets of SPI controller

- Master up to 32 MHz, and Slave up to 16 MHz

- Supports SPI/MICROWIRE Master/Slave mode

- Full duplex synchronous serial data transfer

### enable ADC

- SmartCard (SC)

- Compliant to ISO-7816-3 T=0, T=1

- Supports up to two ISO-7816-3 ports

- Separates receive / transmit 4 bytes entry FIFO for data payloads

- Programmable transmission clock frequency

- Programmable receiver buffer trigger level

- Programmable guard time selection (11 ETU ~ 267 ETU)

- A 24-bit and two 8-bit time-out counter for Answer to Request (ATR) and waiting times processing

- Supports auto inverse convention function

- Supports transmitter and receiver error retry and error limit function

- Supports hardware activation sequence process

- Supports hardware warm reset sequence process

- Supports hardware deactivation sequence process

- Supports hardware auto deactivation sequence when detect the card is removal

- Supports UART mode (full-duplex)

- ACMP

- Suuports up to 2 analog comparators

- Analog input voltage range: 0 ~ AV<sub>DD</sub>

- Supports Hysteresis function

- Two analog comparators with optional internal reference voltage input at negative end

- Wake-up source

- Support RTC, WDT, I<sup>2</sup>C, Timer, UART, SPI, BOD, GPIO

- LCD

- LCD driver for up to 4 COM x 36 SEG or 6 COM x 34 SEG

- Supports Static, 1/2 bias and 1/3 bias voltage

- Six display modes; Static, 1/2 duty, 1/3 duty, 1/4 duty, 1/5 duty and 1/6 duty.

- Selectable LCD frequency by frequency divider

- Configurable frame frequency

- Internal Charge pump, adjustable contrast adjustment

- Configurable Charge pump frequency

- Blinking capability

- Supports R-type/C-type/External C-type method

- Configurable internal R-ladder resistor value (200K/300K/400K)

- ♦ LCD frame interrupt

- One built-in temperature sensor with 1 °C resolution

Page 19 of 100

- Brown-out

- Built-in 2.5V/2.0V/1.7V BOD for wide operating voltage range operation

- 96-bit unique ID

- 128-bit unique customer ID

- Operating Temperature: -40°C~85°C

- Packages:

- All Green package (RoHS)

- LQFP 100-pin(14x14) / 64-pin(10x10) / 64-pin(7x7) / 48-pin(7x7)

### 4.2.2 NuMicro<sup>™</sup> Nano112 LCD Line Selection Guide

|                                                 |       | 00444 | Data         | ISP |          | Timer    | C    | onnectivi |    |      | PWM      | ADC |     | IRC<br>10KHz/    |      |            | ISO-   | ISP |         | Maximum                      |

|-------------------------------------------------|-------|-------|--------------|-----|----------|----------|------|-----------|----|------|----------|-----|-----|------------------|------|------------|--------|-----|---------|------------------------------|

| Part No.                                        | Flash | SRAM  | Flash        | ROM | VO       | (32-bit) | UART | SPI       | ŕc | Comp | (16-bit) |     | RTC | 12MHz /<br>16MHz | PDMA | LCD        | 7816-3 | ЮР  | Package | Operating Tem<br>Range (°C ) |

| NANO112LB1AN                                    | 16K   | 4K    | Configurable | 4K  | up to 40 | 4        | 4    | 2         | 2  | 2    | 4        | 7   | V   | V                | 4    | 4x20, 6x18 | 2      | V   | LQFP48  | -40 to +85                   |

| NANO112LC2AN                                    | 32K   | 8K    | Configurable | 4K  | up to 40 | 4        | 4    | 2         | 2  | 2    | 4        | 7   | 1   | 1                | 4    | 4x20, 6x18 | 2      | V   | LQFP48  | -40 to +85                   |

| NANO112SB1AN                                    | 16K   | 4K    | Configurable | 4K  | up to 58 | 4        | 4    | 2         | 2  | 2    | 4        | 7   | V   | V                | 4    | 4x32, 6x30 | 2      | V   | LQFP64  | -40 to +85                   |

| NANO112SC2AN                                    | 32K   | 8K    | Configurable | 4K  | up to 58 | 4        | 4    | 2         | 2  | 2    | 4        | 7   | V   | ~ 1              | 4    | 4x32, 6x30 | 2      | V   | LQFP64  | -40 to +85                   |

| NANO112RB1AN                                    | 16K   | 4K    | Configurable | 4K  | up to 58 | 4        | 4    | 2         | 2  | 2    | 4        | 7   | V   | 1                | 4    | 4x32, 6x30 | 2      | V   | LQFP64* | -40 to +85                   |

| NANO112RC2AN                                    | 32K   | 8K    | Configurable | 4K  | up to 58 | 4        | 4    | 2         | 2  | 2    | 4        | 7   | V   | $\leq 1$         | 4    | 4x32, 6x30 | 2      | V   | LQFP64* | -40 to +85                   |

| NANO112VC2AN                                    | 32K   | 8K    | Configurable | 4K  | up to 80 | 4        | 4    | 2         | 2  | 2    | 4        | 8   | V   | V                | 4    | 4x36, 6x34 | 2      | V   | LQFP100 | -40 to +85                   |

| QFP48: 7x7mm<br>QFP64: 7x7mm<br>QFP64*: 10x10mm |       |       |              |     |          |          |      |           |    |      |          |     |     |                  |      |            |        |     |         |                              |

|                                                 |       |       |              |     |          |          |      |           |    |      |          |     |     |                  |      |            |        |     |         |                              |

| Pin No. |        |        | Dia Mana   | Dia Tanà | Description                                                                             |

|---------|--------|--------|------------|----------|-----------------------------------------------------------------------------------------|

| 64-pin  | 48-pin | 32-pin | – Pin Name | Pin Type | Description                                                                             |

|         |        |        | PWM0_CH1   | I/O      | PWM0 Channel1 output                                                                    |

|         |        |        | PC.2       | I/O      | General purpose digital I/O pin                                                         |

| 9       | 7      |        | I2C1_SCL   | 0        | l <sup>2</sup> C1 clock pin                                                             |

|         |        |        | PWM0_CH2   | I/O      | PWM0 Channel2 output                                                                    |

|         |        |        | PC.3       | I/O      | General purpose digital I/O pin                                                         |

| 10      | 8      |        | I2C1_SDA   | I/O      | I <sup>2</sup> C1 data I/O pin                                                          |

|         |        |        | PWM0_CH3   | I/O      | PWM0 Channel3 output                                                                    |

|         |        |        | PC.4       | I/O      | General purpose digital I/O pin                                                         |

|         |        |        | UART1_CTSn | I        | UART1 Clear to Send input pin                                                           |

| 11      | 9      | 5      | SC0_CLK    | ο        | SmartCard0 clock pin<br>(SC0_UART_TXD)                                                  |

|         |        |        | INT0       | I        | External interrupt0 input pin                                                           |

| 10      | 10     |        | PC.5       | I/O      | General purpose digital I/O pin                                                         |

| 12      | 10     |        | SC0_CD     | I        | SmartCard0 card detect pin                                                              |

|         |        |        | PC.6       | I/O      | General purpose digital I/O pin                                                         |

| 13      | 11     | 6      | UART1_RTSn | 0        | UART1 Request to Send output pin                                                        |

|         |        |        | SC0_DAT    | I/O      | SmartCard0 DATA pin<br>(SC0_UART_RXD)                                                   |

|         |        |        | PC.7       | I/O      | General purpose digital I/O pin                                                         |

| 14      | 12     | 7      | UART1_RXD  | I        | UART1 Data receiver input pin                                                           |

|         |        |        | SC0_PWR    | 0        | SmartCard0 Power pin                                                                    |

|         |        |        | PC.8       | I/O      | General purpose digital I/O pin                                                         |

| 15      | 13     | 8      | UART1_TXD  | ο        | UART1 Data transmitter output pin<br>(This pin could be modulated with<br>PWM0 output.) |

|         |        |        | SC0_RST    | 0        | SmartCard0 RST pin                                                                      |

| 16      | 14     |        | PC.9       | I/O      | General purpose digital I/O pin                                                         |

|         |        |        | PC.10      | I/O      | General purpose digital I/O pin                                                         |

|         |        | 9      | I2C1_SCL   | I/O      | I <sup>2</sup> C1 clock pin                                                             |

|         |        |        | SC1_CD     | I        | SmartCard1 card detect                                                                  |

|         |        |        | PC.11      | I/O      | General purpose digital I/O pin                                                         |

|         |        | 10     | I2C1_SDA   | I/O      | I <sup>2</sup> C 1 data I/O pin                                                         |

|         |        |        | SC1_PWR    | 0        | SmartCard1 PWR pin                                                                      |

|         |        |        | PC.12      | I/O      | General purpose digital I/O pin                                                         |

|         |        | 11     | SC1_CLK    | о        | SmartCard1 clock pin<br>(SC1_UART_TXD)                                                  |

| Pin No. |        |        | Pin Name        | Pin Type | Description                                                                             |

|---------|--------|--------|-----------------|----------|-----------------------------------------------------------------------------------------|

| 100-pin | 64-pin | 48-pin |                 | Pin Type | Description                                                                             |

|         |        |        | I2C1_SDA        | I/O      | I <sup>2</sup> C1 data I/O pin                                                          |

|         |        |        | ACMP1_OUT       | 0        | Comparator1 output                                                                      |

|         |        |        | тсз             | I        | Timer3 capture input                                                                    |

|         |        |        | PB.0            | I/O      | General purpose digital I/O pin                                                         |

|         |        |        | LCD_SEG29       | 0        | LCD segment output 29 at 64-pin                                                         |

| 92      | 60     |        | UART0_TXD       | ο        | UART0 Data transmitter output pin (This<br>pin could be modulated with PWM0<br>output.) |

|         |        |        | FCLK1           | 0        | Frequency Divider1 output pin                                                           |

|         |        |        | PB.1            | I/O      | General purpose digital I/O pin                                                         |

|         |        |        | LCD_SEG28       | 0        | LCD segment output 28 at 64-pin                                                         |

| 93      | 61     |        | UART0_RXD       | I        | UART0 Data receiver input pin                                                           |

|         |        |        | TC2             | I        | Timer 2 capture input                                                                   |

|         |        |        | INT1            | I        | External interrupt1 input pin                                                           |

|         |        |        | PB.2            | I/O      | General purpose digital I/O pin                                                         |

|         |        |        | LCD_SEG27       | 0        | LCD segment output 27 at 64-pin                                                         |

|         |        |        | UART0_RTSn      | 0        | UART0 Request to Send output pin                                                        |

| 94      | 62     |        | SPI1_MOSI1      | I/O      | SPI1 2 <sup>nd</sup> MOSI (Master Out, Slave In) pin                                    |

|         |        |        | I2C0_SCL        | 0        | I <sup>2</sup> C0 clock pin                                                             |

|         |        |        | ТМЗ             | I/O      | Timer3 external counter input or Timer3 toggle out.                                     |

|         |        |        | PB.3            | I/O      | General purpose digital I/O pin                                                         |

|         |        |        | LCD_SEG26       | 0        | LCD segment output 26 at 64-pin                                                         |

|         |        |        | UART0_CTSn      | I        | UART0 Clear to Send input pin                                                           |

| 95      | 63     |        | SPI1_MISO1      | I/O      | SPI1 2 <sup>nd</sup> MISO (Master In, Slave Out) pin                                    |

|         |        |        | I2C0_SDA        | I/O      | I²C0 data I/O pin                                                                       |

|         |        |        | TM2             | I/O      | Timer2 external counter input or Timer2 toggle out.                                     |

| 96      |        |        | V <sub>DD</sub> | Р        | Power supply for I/O ports and LDO source                                               |

| 97      |        |        | V <sub>ss</sub> | G        | Ground for digital circuit                                                              |

|         |        |        | PB.4            | I/O      | General purpose digital I/O pin                                                         |

| 98      |        |        | UART1_RTSn      | 0        | UART1 Request to Send output pin                                                        |

|         |        |        | SPI1_MISO1      | I/O      | SPI1 2 <sup>nd</sup> MISO (Master In, Slave Out) pin                                    |

| 99      |        |        | PB.5            | I/O      | General purpose digital I/O pin                                                         |

| 39      |        |        | LCD_SEG35       | 0        | LCD segment output 35 at 100-pin                                                        |

### 5 BLOCK DIAGRAM

### 5.1 Nano102 Block Diagram

Figure 5-1 NuMicro<sup>™</sup> Nano102 Block Diagram

### 6.5 Clock Controller

#### 6.5.1 Overview

The clock controller generates clocks for the whole chip, lincluding system clocks (CPU clock, HCLKx, and PCLKx) and all peripheral module clocks. HCLKx means AHB bus clock for peripherals on AHB bus. PCLKx means APB bus clock for peripherals on APB bus. PCLKx can be the same as HCLKx or devided from HCLKx. The clock controller also implements the power control function with the individually clock ON/OFF control, clock source selection and a 4-bit clock divider. The chip will not enter power-down mode until CPU sets the power down enable bit PD\_EN(PWRCTL[6]) and executes the WFI instruction. In the Power-down mode, clock controller turns off the external high frequency crystal, internal high frequency oscillator, and system clocks (CPU clock, HCLKx, and PCLKx) to reduce the power consumption.

The clock controller consists of 5 sources as listed below:

- 32768Hz external low speed crystal oscillator (LXT)

- 4~ 24 MHz external high speed crystal oscillator (HXT)

- 12/16 MHz internal high speed RC oscillator (HIRC)

- One programmable PLL FOUT (PLL source can be selected from HXT or HIRC)

- 10 kHz internal low speed RC oscillator (LIRC)

#### 6.5.2 Features

- Generates clocks for system clocks and all peripheral module clocks.

- Each peripheral module clock can be turned on/off.

- High frequency crystal, internal high frequency oscillator, and system clocks will be turned off when chip is in Power-down mode.

### 6.10 Pulse Width Modulation (PWM)

#### 6.10.1 Overview

This chip has one PWM controller, which includes 4 independent PWM outputs, CH0~CH3, or as 2 complementary PWM pairs, (CH0, CH1), (CH2, CH3) with 2 programmable dead-zone generators.

Each of the two PWM outputs, (CH0, CH1), (CH2, CH3), share the same 8-bit prescaler, clock divider providing 5 divided frequencies (1, 1/2, 1/4, 1/8, 1/16). Each PWM output has independent 16-bit PWM counter which has two counting modes for PWM period control. The PWM counter operates as down counting in edge-aligned mode and up-down counting in center-aligned mode only. Each PWM output also has a 16-bit comparator for PWM duty control. Each dead-zone generator has two outputs. The first dead-zone generator output is CH0 and CH1, and for the second dead-zone generator, the output is CH2 and CH3. The PWM controller total provide four independent PWM interrupt flags which are set by hardware when the corresponding PWM period down counter in edge-aligned mode (or up-down counter in center-aligned mode) reaches 0. PWM interrupt will be asserted when both PWM interrupt source and its corresponding enable bit are active. Each PWM output can be configured as one-shot mode to produce only one PWM cycle signal or continuous mode to output PWM waveform continuously.

When DZEN01(PWM\_CTL[4]) is set, CH0 and CH1 perform complementary PWM paired function; the paired PWM timing, period, duty and dead-time are determined by PWM channel 0 timer and Dead-zone generator 0. Similarly, When DZEN23(PWM\_CTL[5]) is set the complementary PWM pair of (CH2, CH3) is controlled by PWM channel 2.

To prevent PWM driving output pin with unsteady waveform, the 16-bit period down counter and 16-bit comparator are implemented with double buffer. When user writes data to counter/comparator buffer registers the updated value will be loaded into the 16-bit down counter/ comparator at the time down counter reaching 0. The double buffering feature avoids glitch at PWM outputs.

When the 16-bit period down counter reaches 0, the interrupt request is generated. If PWM output is set as continuous mode, when the down counter reaches 0, it is reloaded with CN of PWM\_DUTYy(y=0~3) Register automatically then start decreases, repeatedly. If the PWM output is set as one-shot mode, the down counter will stop and generate one interrupt request when it reaches 0.

The value of PWM counter comparator is used for pulse width modulation. The counter control logic changes the output level when down-counter value matches the value of compare register.

The alternate feature of the PWM is digital input capture function. If capture function is enabled the PWM output pin is switched as capture input pin. The capture channel 0 and PWM CH0 share one timer; and the capture channel 1 and PWM CH1 share one timer, and etc. Therefore user must set up the PWM timer before enabling capture feature. After capture feature of channel 0 is enabled, the capture always latches PWM CH0 timer value to Capture Rising Latch Register CRL (PWM\_CRL0[15:0]) when input channel has a rising transition and latches PWM CH0 timer value to Capture Falling Latch Register CFL (PWM\_CFL0[15:0]) when input channel has a falling transition. Capture channel 0 interrupt is programmable by setting CRL\_IE0(PWM\_CAPINTEN[0]) for rising transition or CFL\_IE0 (PWM\_CAPINTEN[1]) for falling transition. Whenever Capture rising event latched for channel 0, the PWM CH0 timer will be reload at this moment if the corresponding reload enable bit CAPRELOADREN0 (PWM\_CAPCTL[6]) is set.

The maximum captured frequency that PWM can capture is dominated by the capture interrupt latency. When capture interrupt occurs, software will do at least three steps, they are: Read PWMINTSTS to tell it from interrupt source and Read PWM\_CRLy/PWM\_CFLy(y=0~3) to get capture value and finally write 1 to clear PWM\_INTSTS. If interrupt latency will take time T0 to finish, the capture signal mustn't transient during this interval. In this case, the maximum capture frequency will be 1/T0.

#### 6.14 UART Controller

#### 6.14.1 Overview

The UART Controller provides up to two channels of Universal Asynchronous Receiver/Transmitter (UART) modules and performs Normal Speed UART, and supports flow control function. The Universal Asynchronous Receiver/Transmitter (UART) performs a serial-to-parallel conversion on data received from the peripheral, and a parallel-to-serial conversion on data transmitted from the CPU.

The UART controller also supports IrDA (SIR), LIN Master/Slave and RS-485 function modes.

There are four conditions to wake-up the system and it also supports PWM channel source selection to modulate the PWM and the UART transmitter.

#### 6.14.2 Features

- Full duplex, asynchronous communications.

- Separate receiving / transmitting 16 bytes entry FIFO for data payloads.

- Supports hardware auto-flow control/flow control function (CTSn, RTSn) and programmable (CTSn, RTSn) flow control trigger level.

- Supports programmable baud rate generator.

- Supports auto-baud rate detect and baud rate compensation function.

- Supports programmable receiver buffer trigger level.

- Supports incoming data or CTSn or received FIFO is equal to the RFITL or RS-485 AAD mode address matched to wake-up function.

- Supports 9 bit receiver buffer time-out detection function.

- All UART Controller can be served by the PDMA.

- Programmable transmitting data delay time between the last stop bit leaving the TX-FIFO and the de-assertion by setting DLY (UART\_TMCTL[23:16]) register.

- Supports IrDA SIR function mode

- Supports LIN function mode.

- Supports RS-485 function mode.

- Supports PWM modulation

- Supports multiple address recognition (Two slave addresses with mask option)

- Supports Power-down wake-up function

- Supports two-Level FIFO

## nuvoTon

| Input Pull Up Resistor<br>PA, PB, PC, PD, PE,                   | P                 |                    | 43          |                         | KΩ | $V_{DD} = 3.3V$                                                          |

|-----------------------------------------------------------------|-------------------|--------------------|-------------|-------------------------|----|--------------------------------------------------------------------------|

| PA, FB, FC, FD, FE,<br>PF                                       | R <sub>IN</sub>   |                    | 108         |                         | KΩ | V <sub>DD</sub> = 1.8V                                                   |

| Input Leakage Current<br>PA, PB, PC, PD, PE,<br>PF              | I <sub>LK</sub>   | -0.1               | -           | +0.1                    | μΑ | V <sub>DD</sub> = 3.3V, 0 <v<sub>IN<v<sub>DD</v<sub></v<sub>             |

| Input Low Voltage PA,<br>PB, PC, PD, PE, PF<br>(Schmitt input)  | V <sub>IL1</sub>  |                    | -           | 0.4V <sub>DD</sub>      | v  | N.                                                                       |

| Input High Voltage PA,<br>PB, PC, PD, PE, PF<br>(Schmitt input) | V <sub>IH1</sub>  | 0.6V <sub>DD</sub> |             | 5.5                     | V  | ADC and DAC shared pins without Input<br>5V tolerance.                   |

| Hysteresis voltage of<br>PA~PF (Schmitt input)                  | V <sub>HY</sub>   |                    | $0.2V_{DD}$ |                         | V  | Sk Ch                                                                    |

| Input Low Voltage<br>XT1 <sup>[*2]</sup>                        | V <sub>IL2</sub>  | 0                  | -           | 0.4                     |    | V <sub>DD</sub> = 3.3V                                                   |

| Input High Voltage<br>XT1 <sup>[*2]</sup>                       | V <sub>IH2</sub>  | 1.5                | -           | V <sub>DD</sub><br>+0.2 | V  | V <sub>DD</sub> = 3.3V                                                   |

| Input Low Voltage<br>X32I <sup>[*2]</sup>                       | V <sub>IL4</sub>  | 0                  | -           | 0.3                     | V  | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~                                   |

| Input High Voltage<br>X32I <sup>[*2]</sup>                      | V <sub>IH4</sub>  | 1.5                | -           | 1.98                    | V  | 0                                                                        |

| Negative going<br>threshold<br>(Schmitt input),<br>/RESET       | V <sub>ILS</sub>  | 1.03               | 1.08        | 1.13                    | V  | V <sub>DD</sub> = 3.3V                                                   |

| Positive going<br>threshold<br>(SchmittIput), /RESET            | V <sub>IHS</sub>  | 1.75               | 2.01        | 2.25                    | V  | V <sub>DD</sub> = 3.3V                                                   |

| Source Current PA,<br>PB, PC, PD, PE, PF                        | I <sub>SR21</sub> | -10                | -14         | -                       | mA | $V_{\text{DD}} = 3.3 \text{V},$ $V_{\text{S}} = \text{Vdd-}0.7 \text{V}$ |

| (Push-pull Mode)                                                | I <sub>SR22</sub> | -3                 | -5          | -                       | mA | $V_{DD} = 1.8V,$<br>$V_{S} = Vdd-0.45V$                                  |

| Sink Current PA, PB,<br>PC, PD, PE, PF                          | I <sub>SK21</sub> | 10                 | 15          | -                       | mA | $V_{DD} = 3.3V,$<br>$V_{S} = 0.7V$                                       |

| (Push-pull Mode)                                                | I <sub>SK22</sub> | 3                  | 6           | -                       | mA | $V_{DD} = 1.8V,$<br>$V_{S} = 0.45V$                                      |

#### Note:

1. /RESET pin is a Schmitt trigger input.

2. Crystal Input is a CMOS input.

3. It is recommended that a 10uF or higher capacitor and a 100nF bypass capacitor are connected between VDD and the closest VSS pin of the device.

4. For ensuring power stability, a 1uF or higher capacitor must be connected between LDO pin and the closest VSS pin of the device. Also a 100nF bypass capacitor between LDO and VSS help suppressing output noise.

5. All peripherals' clock source is from HXT (12 MHz), except SPI from HCLK.

| V <sub>COM</sub> | Input Common Mode Range | 0.1 | -   | AV <sub>DD</sub> – 0.1 | V  | -                         |

|------------------|-------------------------|-----|-----|------------------------|----|---------------------------|

| -                | DC Gain                 | 40  | 70  | -                      | dB | -                         |

| T <sub>PGD</sub> | Propagation Delay       | -   | 200 | -                      | ns | V <sub>DIFF</sub> = 100mV |

| V <sub>HYS</sub> | Hysteresis              | - 2 | ±10 | <u></u>                | mV |                           |

| Т <sub>STB</sub> | Stable time             | -   | VXX |                        | μs |                           |

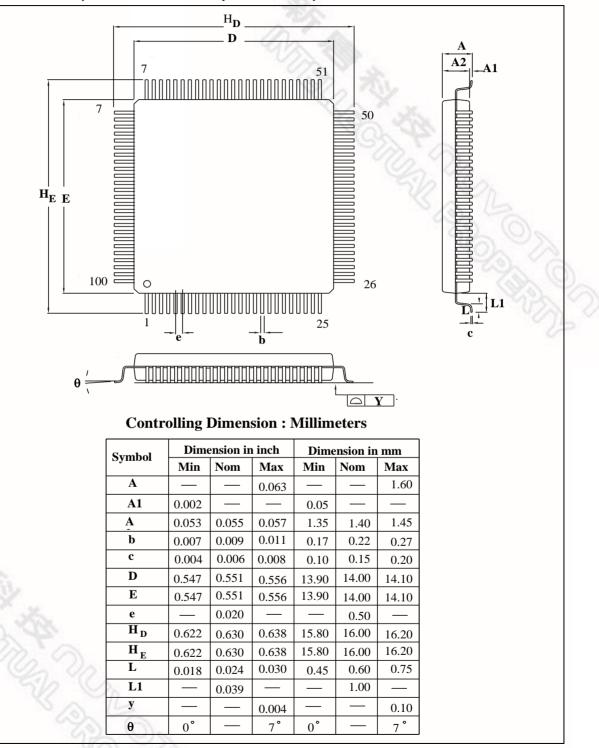

### **10 PACKAGE DIMENSIONS**

### 10.1 100L LQFP (14x14x1.4 mm footprint 2.0 mm)

|                   |       | SYMBOL      | MIN     | NOM       | MAX  |  |  |

|-------------------|-------|-------------|---------|-----------|------|--|--|

| TOTAL THICKNESS   |       | Α           | 0.7     | 0.75      | 0.8  |  |  |

| STAND OFF         |       | A1          | 0       | 0.035     | 0.05 |  |  |

| MOLD THICKNESS    |       | A2          |         | 0.55      | 0.57 |  |  |

| L/F THICKNESS     |       | A3          |         | 0.203 REF |      |  |  |

| LEAD WIDTH        |       | b           | 0.2     | 0.25      | 0.3  |  |  |

| BODY SIZE         | Х     | D           | 5 BSC   |           |      |  |  |

| BODT SIZE         | Y     | Y E 5       |         |           |      |  |  |

| LEAD PITCH        |       | е           | 0.5 BSC |           |      |  |  |

| EP SIZE           | Х     | J           | 3.4     | 3.5       | 3.6  |  |  |

| EF SIZE           | Y     | к           | 3.4     | 3.5       | 3.6  |  |  |

| LEAD LENGTH       |       | L           | 0.35    | 0.4       | 0.45 |  |  |

| PACKAGE EDGE TOLE | RANCE | aaa         | 0.1     |           |      |  |  |

| MOLD FLATNESS     | bbb   | 0.1<br>0.08 |         |           |      |  |  |

| COPLANARITY       | ccc   |             |         |           |      |  |  |

| LEAD OFFSET       |       | ddd         | 0.1     |           |      |  |  |

| EXPOSED PAD OFFSE | Т     | eee         |         | 0.1       |      |  |  |