#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                               |

|----------------------------|--------------------------------------------------------|

| Core Processor             | Z8                                                     |

| Core Size                  | 8-Bit                                                  |

| Speed                      | 20MHz                                                  |

| Connectivity               | EBI/EMI, UART/USART                                    |

| Peripherals                | -                                                      |

| Number of I/O              | 52                                                     |

| Program Memory Size        | -                                                      |

| Program Memory Type        | ROMIess                                                |

| EEPROM Size                | -                                                      |

| RAM Size                   | 236 x 8                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                              |

| Data Converters            | -                                                      |

| Oscillator Type            | Internal                                               |

| Operating Temperature      | 0°C ~ 70°C (TA)                                        |

| Mounting Type              | Surface Mount                                          |

| Package / Case             | 68-LCC (J-Lead)                                        |

| Supplier Device Package    | -                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z86c9620vsc |

|                            |                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### PIN DESCRIPTION

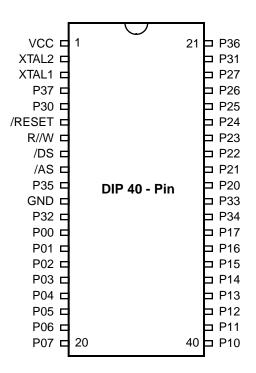

### Figure 4. Z86C61 40-Pin DIP Pin Assignments

### Table 1. Z86C61 40-Pin DIP Pin Identification

| Pin # | Symbol          | Function                        | Direction |  |  |

|-------|-----------------|---------------------------------|-----------|--|--|

| 1     | V <sub>CC</sub> | Power Supply                    | Input     |  |  |

| 2     | XTAL2           | Crystal, Oscillator<br>Clock    | Output    |  |  |

| 3     | XTAL1           | Crystal, Oscillator<br>Clock    | Input     |  |  |

| 4     | P37             | Port 3, Pin 7                   | Output    |  |  |

| 5     | P30             | Port 3, Pin 0                   | Input     |  |  |

| 6     | /RESET          | Reset                           | Input     |  |  |

| 7     | R//W            | Read/Write                      | Output    |  |  |

| 8     | /DS             | Data Strobe                     | Output    |  |  |

| 9     | /AS             | Address Strobe                  | Output    |  |  |

| 10    | P35             | Port 3, Pin 5                   | Output    |  |  |

| 11    | GND             | Ground                          | Input     |  |  |

| 12    | P32             | Port 3, Pin 2                   | Input     |  |  |

| 13-20 | P07-P00         | Port 0, Pins<br>0,1,2,3,4,5,6,7 | In/Output |  |  |

| 21-28 | P17-P10         | Port 1, Pins<br>0,1,2,3,4,5,6,7 | In/Output |  |  |

| 29    | P34             | Port 3, Pin 4                   | Output    |  |  |

| 30    | P33             | Port 3, Pin 3                   | Input     |  |  |

| 31-38 | P27-P20         | Port 2, Pins<br>0,1,2,3,4,5,6,7 | In/Output |  |  |

| 39    | P31             | Port 3, Pin 1                   | Input     |  |  |

| 40    | P36             | Port 3, Pin 6                   | Output    |  |  |

### PIN DESCRIPTION (Continued)

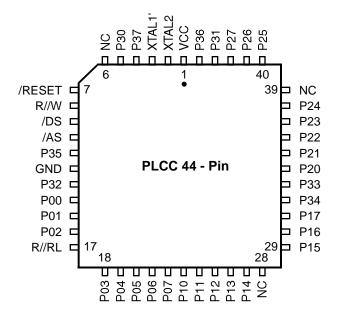

Figure 5. Z86C61 44-Pin PLCC Pin Assignments

### Table 2. Z86C61 44-Pin PLCC Pin Assignments

Pin # Symbol Function Direction 1 V<sub>CC</sub> **Power Supply** Input 2 XTAL2 Crystal, Oscillator Clock Output 3 XTAL1 Crystal, Oscillator Clock Input P37 Port 3, Pin 7 4 Output P30 Port 3, Pin 0 5 Input N/C Not Connected 6 Input 7 /RESET Reset Input 8 R//W Read/Write Output 9 /DS Data Strobe Output /AS 10 Address Strobe Output 11 P35 Port 3, Pin 5 Output 12 GND Ground Input P32 Port 3, Pin 2 13 Input 14-16 P02-P00 Port 0, Pins 0,1,2 In/Output R//RL **ROM/ROMIess** control 17 Input 18-22 P07-P03 Port 0, Pins 3,4,5,6,7 In/Output

#### Table 2. Z86C61 44-Pin PLCC Pin Assignments

| Pin # | Symbol  | Function               | Direction |

|-------|---------|------------------------|-----------|

| 23-27 | P14-P10 | Port 1, Pins 0,1,2,3,4 | In/Output |

| 28    | N/C     | Not Connected          | Input     |

| 29-31 | P17-P15 | Port 1, Pins 5,6,7     | In/Output |

| 32    | P34     | Port 3, Pin 4          | Output    |

| 33    | P33     | Port 3, Pin 3          | Input     |

| 34-38 | P24-P20 | Port 2, Pins 0,1,2,3,4 | In/Output |

| 39    | N/C     | Not Connected          | Input     |

| 40-42 | P25-P27 | Port 2, Pins 5,6,7     | In/Output |

| 43    | P31     | Port 3, Pin 1          | Input     |

| 44    | P36     | Port 3, Pin 6          | Output    |

DS97Z8X1600

| Pin # | Symbol          | Function                     | Direction |

|-------|-----------------|------------------------------|-----------|

| 1-2   | P44-P43         | Port 4, Pins 3,4             | In/Output |

| 3     | V <sub>CC</sub> | Power Supply                 | Input     |

| 4     | P45             | Port 4, Pin 5                | In/Output |

| 5     | XTAL2           | Crystal, Oscillator Clock    | Output    |

| 6     | XTAL1           | Crystal, Oscillator Clock    | Input     |

| 7     | P37             | Port 3, Pin 7                | Output    |

| 8     | P30             | Port 3, Pin 0                | Input     |

| 9     | /RESET          | Reset                        | Input     |

| 10    | R//W            | Read/Write                   | Output    |

| 11    | /P0DS           | Port 0 Data Strobe           | Output    |

| 12    | /DS             | Data Strobe                  | Output    |

| 13-14 | P47-P46         | Port 4, Pins 6,7             | In/Output |

| 15    | /P1DS           | Port 1, Data Strobe          | Output    |

| 16    | /AS             | Address Strobe               | Output    |

| 17    | /DTIMER         | DTIMER                       | Input     |

| 18    | P35             | Port 3, Pin 5                | Output    |

| 19    | R//RL           | ROM/ROMIess control          | Input     |

| 20    | GND             | Ground                       | Input     |

| 21    | P32             | Port 3, Pin 2                | Input     |

| 22-23 | P51-P50         | Port 5, Pins 0,1             | In/Output |

| 24-31 | P07-P00         | Port 0, Pins 0,1,2,3,4,5,6,7 | In/Output |

| 32    | V <sub>CC</sub> | Power Supply                 | Input     |

| 33-36 | P55-P52         | Port 5, Pins 2,3,4,5         | In/Output |

| 37-38 | P11-P10         | Port 1, Pins 0,1             | In/Output |

| 39-40 | P56-P57         | Port 5, Pins 6,7             | In/Output |

| 41-46 | P17-P12         | Port 1, Pins2,3,4,5,6,7      | In/Output |

| 47-48 | P63-P62         | Port 6, Pins 3,2             | In/Output |

| 49    | P34             | Port 3, Pin 4                | Output    |

| 50    | P33             | Port 3, Pin 3                | Input     |

| 51    | GND             | Ground                       | Input     |

| 52    | /SYNC           | Synchronization              | Output    |

| 53    | SCLK            | System Clock                 | Output    |

| 54-55 | P21-P20         | Port 2, Pins 0,1             | In/Output |

| 56-57 | P60-P61         | Port 6, Pins 1,0             | In/Output |

| 58-63 | P27-P22         | Port 2, Pins 2,3,4,5,6,7     | In/Output |

| 64-65 | P41-P40         | Port 4, Pins 0,1             | In/Output |

| 66    | P31             | Port 3, Pin 1                | Input     |

| 67    | P36             | Port 3, Pin 6                | Output    |

| 68    | P42             | Port 4, Pin 2                | In/Output |

#### Table 4. Z86C62/C96 68-Pin PLCC Pin Identification

## DC ELECTRICAL CHARACTERISTICS (Continued)

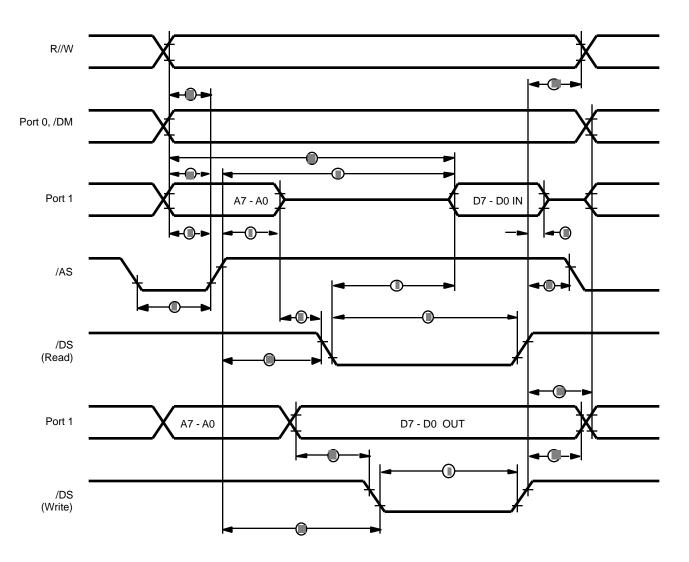

Figure 9. External I/O or Memory Read/Write

PRELIMINARY PS003501-0301

External I/O or Memory Read and Write Timing Z86C61/62/96 (20 MHz)

|    |           |                                               | $T_A = 0^{\circ}C$ | to +70°C | T <sub>A</sub> = -40°C | to +105°C |       |       |

|----|-----------|-----------------------------------------------|--------------------|----------|------------------------|-----------|-------|-------|

|    |           |                                               |                    | 20 MHz   |                        | 20 MHz    |       |       |

| No | Sym       | Parameter                                     | Min                | Max      | Min                    | Max       | Units | Notes |

| 1  | TdA(AS)   | Address Valid to /AS rise<br>Delay            | 15                 |          | 25                     |           | ns    | 2,3   |

| 2  | TdAS(A)   | /AS rise to Address Float<br>Delay            | 25                 |          | 35                     |           | ns    | 2,3   |

| 3  | TdAS(DR)  | /AS rise to Read Data<br>Req'd Valid          |                    | 120      |                        | 120       | ns    | 1,2,3 |

| 4  | TwAS      | /AS Low Width                                 | 30                 |          | 30                     |           | ns    | 2,3   |

| 5  | TdAZ(DS)  | Address Float to /DS fall                     | 0                  |          | 0                      |           | ns    |       |

| 6  | TwDSR     | /DS (Read) Low Width                          |                    | 105      |                        | 105       | ns    | 1,2,3 |

| 7  | TwDSW     | /DS (Write) Low Width                         | 65                 |          | 65                     |           | ns    | 1,2,3 |

| 8  | TdDSR(DR) | /DS fall to Read Data<br>Req'd Valid          | 55                 |          | 55                     |           | ns    | 1,2,3 |

| 9  | ThDR(DS)  | Read Data to /DS rise Hold<br>Time            | 0                  |          | 0                      |           | ns    | 2,3   |

| 10 | TdDS(A)   | /DS rise to Address Active<br>Delay           | 40                 |          | 40                     |           | ns    | 2,3   |

| 11 | TdDS(AS)  | /DS rise to /AS fall Delay                    | 25                 |          | 25                     |           | ns    | 2,3   |

| 12 | TdR/W(AS) | R//W Valid to /AS rise<br>Delay               | 20                 |          | 20                     |           | ns    | 2,3   |

| 13 | TdDS(R/W) | /DS rise to R//W Not Valid                    | 25                 |          | 25                     |           | ns    | 2,3   |

| 14 | TdDW(DSW) | Write Data Valid to /DS fall<br>(Write) Delay | 20                 |          | 20                     |           | ns    | 2,3   |

| 15 | TdDS(DW)  | /DS rise to Write Data Not<br>Valid Delay     | 25                 |          | 25                     |           | ns    | 2,3   |

| 16 | TdA(DR)   | Address Valid to Read<br>Data Req'd Valid     |                    | 150      |                        | 150       | ns    | 1,2,3 |

| 17 | TdAS(DS)  | /AS rise to /DS fall Delay                    | 35                 |          | 35                     |           | ns    | 2,3   |

| 18 | TdDM(AS)  | /DM Valid to /AS rise Delay                   | 15                 |          | 15                     |           | ns    | 2,3   |

#### Notes:

1. When using extended memory timing add 2 TpC.

2. Timing numbers given are for minimum TpC.

3. See clock cycle dependent characteristics table.

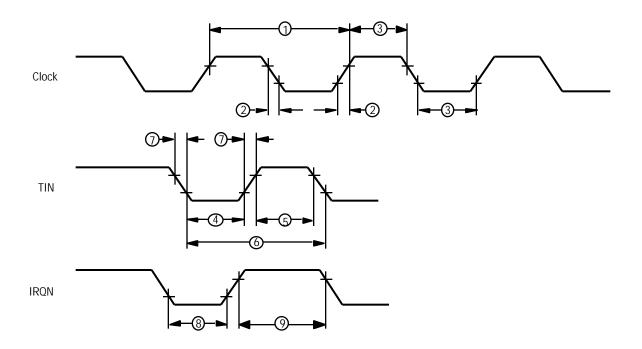

Additional Timing Diagram

Figure 10. Additional Timing

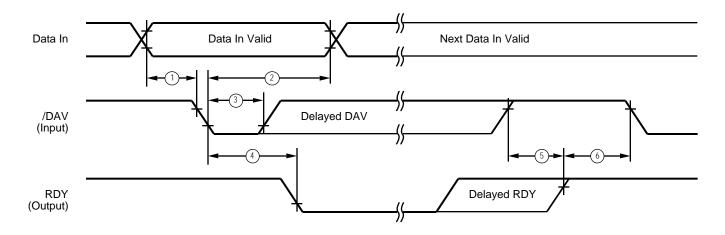

Handshake Timing Diagrams

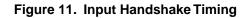

Figure 12. Output Handshake Timing

Handshake Timing Table Z86C61/62/96

|    |              |                            |      | C to +70°C | T <sub>A</sub> = −40°C to<br>+105°C |     |           |

|----|--------------|----------------------------|------|------------|-------------------------------------|-----|-----------|

|    |              |                            | 20/1 | 6 MHz      | 20/16                               | MHZ | Data      |

| No | Symbol       | Parameter                  | Min  | Max        | Min                                 | Max | Direction |

| 1  | TsDI(DAV)    | Data In Setup Time         | 0    |            | 0                                   |     | IN        |

| 2  | ThDI(DAV)    | Data In Hold Time          | 145  |            | 145                                 |     | IN        |

| 3  | TwDAV        | Data Available Width       | 110  |            | 110                                 |     | IN        |

| 4  | TdDAVI(RDY)  | DAV fall to RDY fall Delay | 115  |            | 115                                 |     | IN        |

| 5  | TdDAVId(RDY) | DAV rise to RDY rise Delay | 115  |            | 115                                 |     | IN        |

| 6  | TdRDY0(DAV)  | RDY rise to DAV fall Delay | 0    |            | 0                                   |     | IN        |

| 7  | TdDO(DAV)    | Data Out to DAV fall Delay | ТрС  |            | ТрС                                 |     | OUT       |

| 8  | TdDAV0(RDY)  | DAV fall to RDY fall Delay | 0    |            | 0                                   |     | OUT       |

| 9  | TdRDY0(DAV)  | RDY fall to DAV rise Delay | 115  |            | 115                                 |     | OUT       |

| 10 | TwRDY        | RDY Width                  | 110  |            | 110                                 |     | OUT       |

| 11 | TdRDY0d(DAV) | RDY rise to DAV fall Delay | 115  |            | 115                                 |     | OUT       |

## PIN FUNCTIONS (Continued)

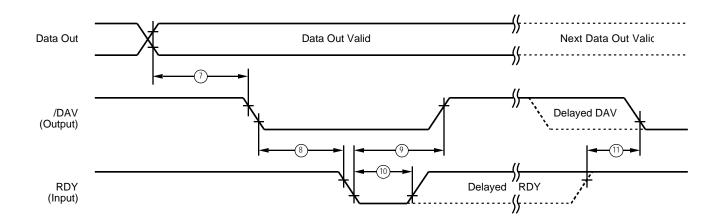

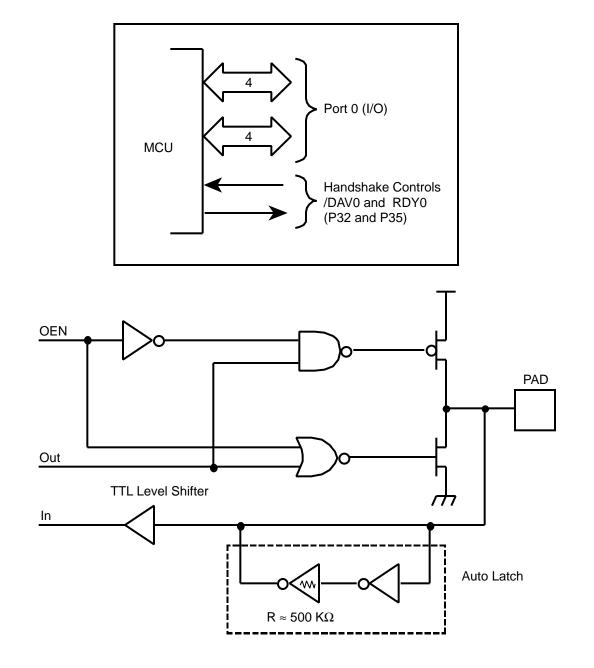

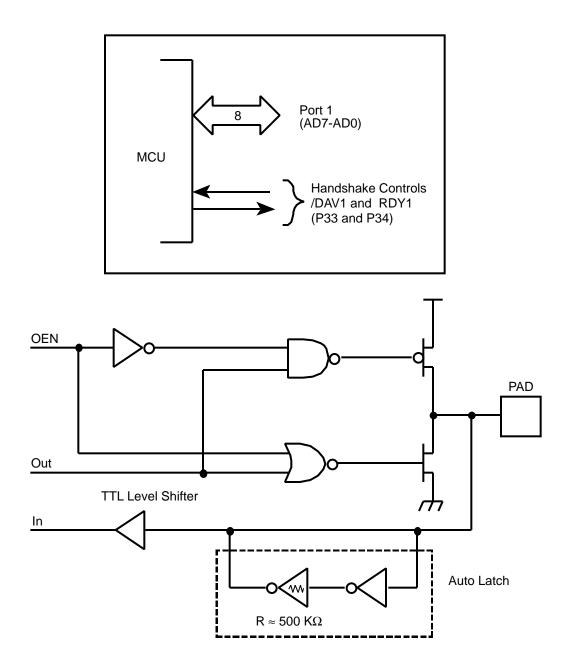

Figure 13. Port 0 Configuration

**Port 1** (P17-P10). Port 1 is an 8-bit, byte programmable, bidirectional, TTL compatible port. It has multiplexed Address (A7-A0) and Data (D7-D0) ports. For Z86C61/62/96, these eight I/O lines can be programmed as Input or Output lines or can be configured under software control as an address/data port for interfacing external memory. When used as an I/O port, Port 1 may be placed under handshake control. In this configuration, Port 3 line P33 and P34 are used as the handshake controls RDY1 and /DAV1.

Memory locations greater than 16,384 are referenced through Port 1. To interface external memory, Port 1 must be programmed for the multiplexed Address/Data mode. If more than 256 external locations are required, Port 0 must output the additional lines.

Port 1 can be placed in high-impedance state along with Port 0, /AS, /DS, and R//W, allowing the microcontroller to share common resources in multiprocessor and DMA applications. Data transfers can be controlled by assigning P33 as a Bus Acknowledge input, and P34 as a Bus request output (Figure 14).

Figure 14. Port 1 Configuration

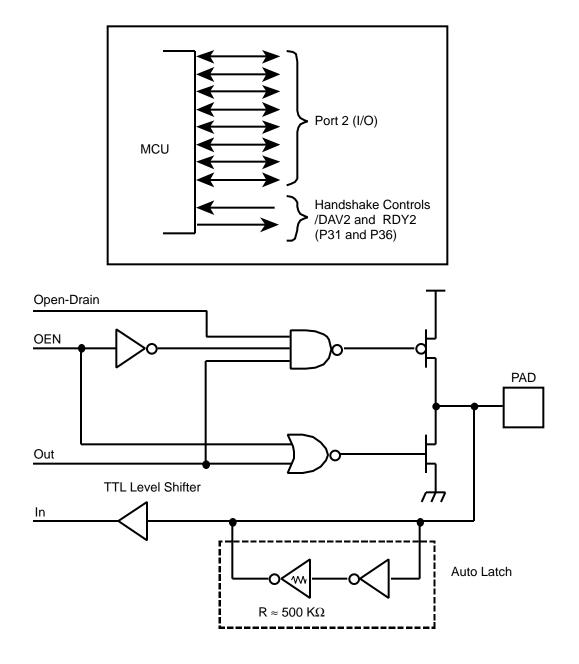

**Port 2** (P27-P20). Port 2 is an 8-bit, bit programmable, bidirectional, CMOS-compatible port. Each of these eight I/O lines can be independently programmed as an input or output or globally as an open-drain output. Port 2 is always available for I/O operation. When used as an I/O port, Port 2 may be placed under handshake control. In this configuration, Port 3 lines P31 and P36 are used as the handshake control lines /DAV2 and RDY2. The handshake signal assignment for Port 3 lines P31 and P36 is dictated by the direction (input or output) assigned to P27 (Figure 15).

Figure 15. Port 2 Configuration

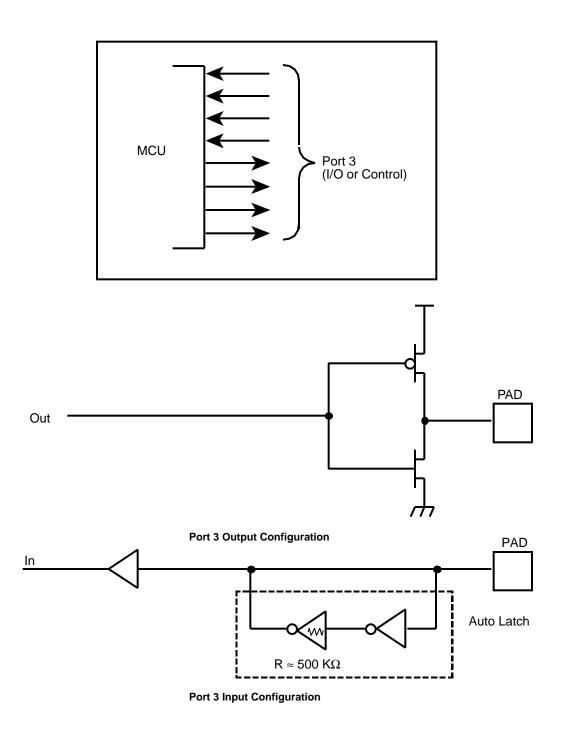

**Port 3** (P37-P30). Port 3 is an 8-bit, CMOS-compatible four-fixed input and four-fixed output port. These eight I/O lines have four-fixed (P33-P30) input and four-fixed (P37-

P34) output ports. Port 3, when used as serial I/O, are programmed as serial in and serial out, respectively (Figure 16).

Figure 16. Port 3 Configuration

## PIN FUNCTIONS (Continued)

Port 3 can be configured under software control to provide the following control functions: handshake for Ports 0 and 2 (/DAV and RDY); four external interrupt request signals (IRQ3-IRQ0); timer input and output signals (T<sub>IN</sub> and T<sub>OUT</sub>), and Data Memory Select (/DM).

| Pin | I/O | CTC1             | Int. | P0 HS | P1 HS | P2 HS | UART       | Ext |

|-----|-----|------------------|------|-------|-------|-------|------------|-----|

| P30 | IN  |                  | IRQ3 |       |       |       | Serial In  |     |

| P31 | IN  | T <sub>IN</sub>  | IRQ2 |       |       | D/R   |            |     |

| P32 | IN  |                  | IRQ0 | D/R   |       |       |            |     |

| P33 | IN  |                  | IRQ1 |       | D/R   |       |            |     |

| P34 | OUT |                  |      |       | R/D   |       |            | DM  |

| P35 | OUT |                  |      | R/D   |       |       |            |     |

| P36 | OUT | T <sub>OUT</sub> |      |       |       | R/D   |            |     |

| P37 | OUT |                  |      |       |       |       | Serial Out |     |

| T0  |     |                  | IRQ4 |       |       |       |            |     |

| T1  |     |                  | IRQ5 |       |       |       |            |     |

#### Table 6. Port 3 Pin Assignments

Notes:

HS = Handshake Signals

D = Data Available

R = Ready

### Uart Operation

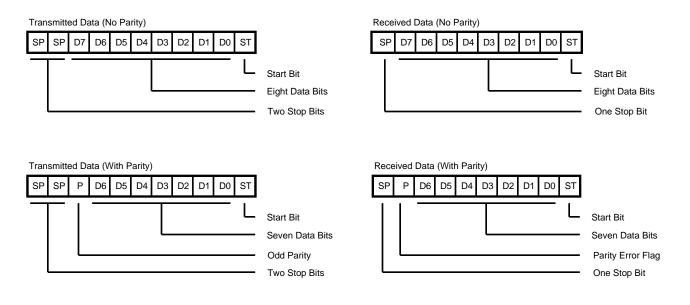

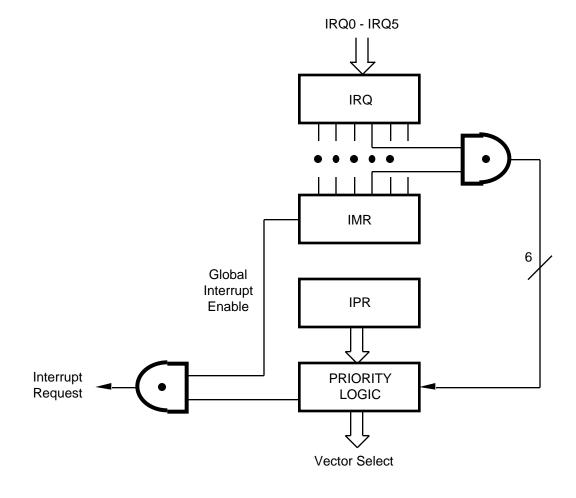

Port 3 lines P30 and P37, can be programmed as serial I/O lines for full-duplex serial asynchronous receiver/transmitter operation. The bit rate is controlled by the Counter/Timer0.

The Z86C61/62/96 automatically adds a start bit and two stop bits to transmitted data (Figure 17). Odd parity is also available as an option. Eight data bits are always transmitted, regardless of parity selection. If parity is enabled, the eighth bit is the odd parity bit. An interrupt request (IRQ4) is generated on all transmitted characters. Received data must have a start bit, eight data bits and at least one stop bit. If parity is on, bit 7 of the received data is replaced by a parity error flag. Received characters generate the IRQ3 interrupt request.

**Note:** UART function is only available in standard timing mode (i.e., P01M D5 = 0).

## PIN FUNCTIONS (Continued)

**Port 4** (P47-P40). Port 4 is an 8-bit, bit programmable, bidirectional, CMOS-compatible port. Each of these eight I/O lines can be independently programmed as an input or output or globally as an open-drain output. Port 4 is always available for I/O operation (Figure 18). Port address (F)02.

Port 5 (P57-P50). Same as Port 4. Port address (F)04.

**Open-Drain**

OEN

Out

In

MCU

TTL Level Shifter

**Port 6** (P63-P60). Same as Port 4. (Note: this is a 4-bit port, bits D3-D0.) Port address (F)07.

**Auto Latch.** The Auto Latch puts valid CMOS levels on all CMOS inputs that are not externally driven. This reduces excessive supply current flow in the input buffer when it is not being driven by any source.

PAD

Auto Latch

Port 4 (I/O)

$R \approx 500 \text{ K}\Omega$

Figure 18. Port 4 Configuration

## FUNCTIONAL DESCRIPTION (Continued)

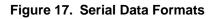

Figure 25. Counter/Timer Block Diagram

### Zilog

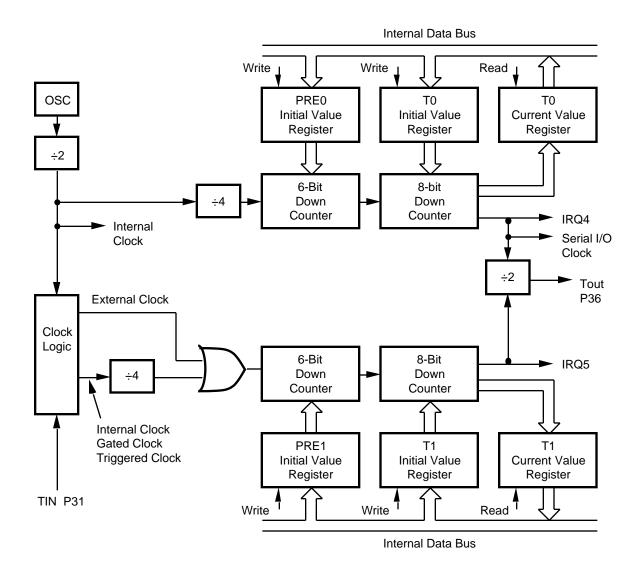

Interrupts. The Z86C61/62/96 has six different interrupts from eight different sources. The interrupts are maskable and prioritized. The eight sources are divided as follows: four sources are claimed by Port 3 lines P33-P30, one in Serial Out, one is Serial In, and two in the counter/timers (Figure 26). The Interrupt Mask Register globally or individually enables or disables the six interrupt requests. When more than one interrupt is pending, priorities are resolved by a programmable priority encoder that is controlled by the Interrupt Priority register. All Z86C61/62/96 interrupts are vectored through locations in the program memory. When an interrupt machine cycle is activated, an interrupt request is granted. Thus, this disables all of the subsequent interrupts, saves the Program Counter and Status Flags, and then branches to the program memory vector location reserved for that interrupt. This memory location and the next byte contain the 16-bit address of the interrupt service routine for that particular interrupt request.

To accommodate polled interrupt systems, interrupt inputs are masked and the Interrupt Request register is polled to determine which of the interrupt requests need service. Software initialed interrupts are supported by setting the appropriate bit in the Interrupt Request Register (IRQ).

Internal interrupt requests are sampled on the falling edge of the last cycle of every instruction. The interrupt request must be valid 5TpC before the falling edge of the last clock cycle of the currently executing instruction.

For the ROMless mode, when the device samples a valid interrupt request, the next 48 (external) clock cycles are used to prioritize the interrupt, and push the two PC bytes and the FLAG register onto the stack. The following nine cycles are used to fetch the interrupt vector from external memory. The first byte of the interrupt service routine is fetched beginning on the 58th TpC cycle following the internal sample point, which corresponds to the 63rd TpC cycle following the external interrupt sample point.

Figure 26. Interrupt Block Diagram

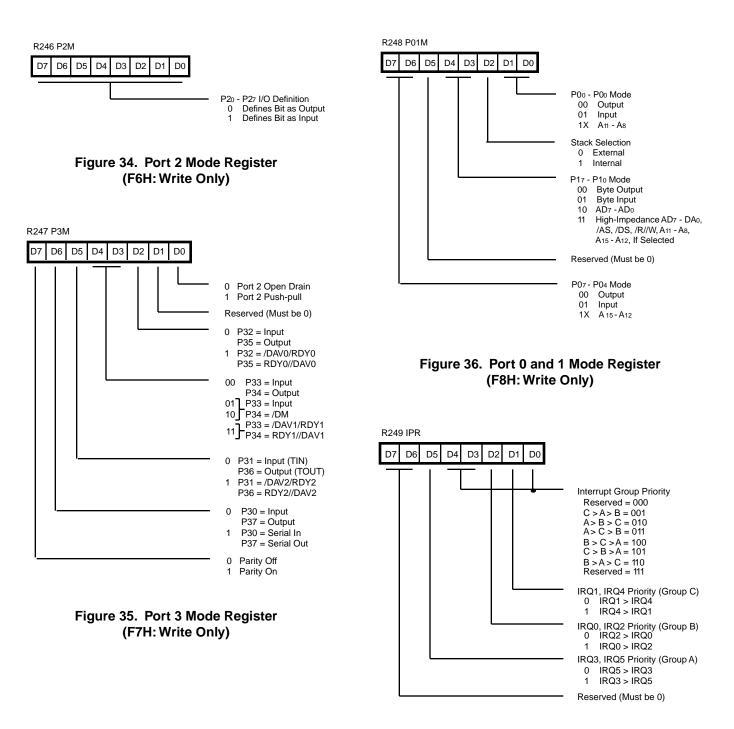

### **Z8 CONTROL REGISTER DIAGRAMS**

(F2H: Read/Write)

Figure 37. Interrupt Priority Register (F9H: Write Only)

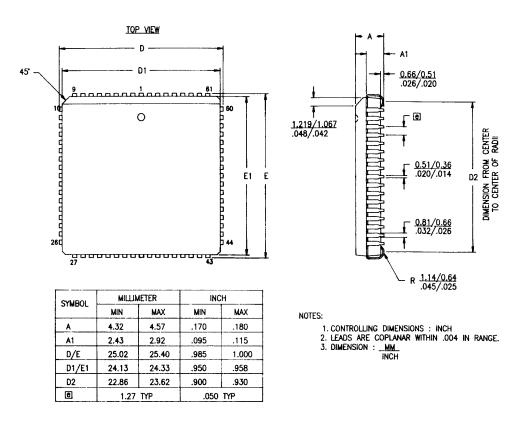

Figure 55. 68-Pin PLCC Package Diagram