# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 12                                                                       |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 64 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 16-VQFN Exposed Pad                                                      |

| Supplier Device Package    | 16-QFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f630-e-ml |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral functions for controlling the desired operation of the device (see Table 2-1). These registers are static RAM.

The special registers can be classified into two sets: core and peripheral. The Special Function Registers associated with the "core" are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

### FIGURE 2-2: DATA MEMORY MAP OF THE PIC16F630/676

|                                                                                  | THEF            | PIC16F630/676                 |                |

|----------------------------------------------------------------------------------|-----------------|-------------------------------|----------------|

|                                                                                  | File<br>Address | A                             | File<br>ddress |

| Indirect addr. <sup>(1)</sup>                                                    | 00h             | Indirect addr. <sup>(1)</sup> | 80h            |

| TMR0                                                                             | 01h             | OPTION_REG                    | 81h            |

| PCL                                                                              | 02h             | PCL                           | 82h            |

| STATUS                                                                           | 03h             | STATUS                        | 83h            |

| FSR                                                                              | 04h             | FSR                           | 84h            |

| PORTA                                                                            | 05h             | TRISA                         | 85h            |

|                                                                                  | 06h             | -                             | 86h            |

| PORTC                                                                            | 07h             | TRISC                         | 87h            |

|                                                                                  | 08h             | -                             | 88h            |

|                                                                                  | 09h             |                               | 89h            |

| PCLATH                                                                           | 0Ah             | PCLATH                        | 8Ah            |

| INTCON                                                                           | 0Bh             | INTCON                        | 8Bh            |

| PIR1                                                                             | 0Ch             | PIE1                          | 8Ch            |

|                                                                                  | 0Dh             |                               | 8Dh            |

| TMR1L                                                                            | 0Eh             | PCON                          | 8Eh            |

| TMR1H                                                                            | 0Fh             |                               | 8Fh            |

| T1CON                                                                            | 10h             | OSCCAL                        | 90h            |

| TICON                                                                            | 11h             | ANSEL <sup>(2)</sup>          | 91h            |

|                                                                                  | 12h             | THOLE                         | 92h            |

|                                                                                  | 13h             | -                             | 93h            |

|                                                                                  | 14h             |                               | 94h            |

|                                                                                  | 15h             | WPUA                          | 95h            |

|                                                                                  | 16h             | IOCA                          | 96h            |

|                                                                                  | 17h             | IOCA                          | 97h            |

|                                                                                  | 18h             |                               | 98h            |

| CMCON                                                                            | 19h             | VRCON                         | 99h            |

| CINCON                                                                           | 1Ah             | EEDAT                         | 9Ah            |

|                                                                                  | 1Bh             | EEADR                         | 9Bh            |

|                                                                                  | 1Ch             | EECON1                        | 9Ch            |

|                                                                                  | 1Dh             | EECON2 <sup>(1)</sup>         | 9Dh            |

| ADRESH <sup>(2)</sup>                                                            | 1Eh             | ADRESL <sup>(2)</sup>         | 9Eh            |

| ADCON0 <sup>(2)</sup>                                                            | 1Fh             | ADCON1 <sup>(2)</sup>         | 9Fh            |

| ADCONU                                                                           | 20h             | ADCONT                        | A0h            |

| General<br>Purpose<br>Registers<br>64 Bytes                                      | 2011            | accesses<br>20h-5Fh           |                |

|                                                                                  | 5Fh             |                               | DFh            |

|                                                                                  | 60h             |                               | E0h            |

|                                                                                  | 001             |                               | Lon            |

|                                                                                  |                 |                               |                |

|                                                                                  |                 |                               |                |

|                                                                                  | 7Fh             | _                             | FFh            |

| Bank 0                                                                           |                 | Bank 1                        |                |

| <ul><li>Unimplemente</li><li>1: Not a physical</li><li>2: PIC16F676 on</li></ul> | register.       | mory locations, rea           | d as '0'.      |

## 2.2.2.2 OPTION Register

The OPTION register is a readable and writable register, which contains various control bits to configure:

- TMR0/WDT prescaler

- External RA2/INT interrupt

- TMR0

- Weak pull-ups on PORTA

### REGISTER 2-2: OPTION\_REG — OPTION REGISTER (ADDRESS: 81h)

|         | R/W-1                         | R/W-1         | R/W-1                         | R/W-1         | R/W-1       | R/W-1  | R/W-1 | R/W-1 |  |

|---------|-------------------------------|---------------|-------------------------------|---------------|-------------|--------|-------|-------|--|

|         | RAPU                          | INTEDG        | TOCS                          | T0SE          | PSA         | PS2    | PS1   | PS0   |  |

|         | bit 7                         |               |                               |               |             |        |       | bit 0 |  |

|         |                               |               |                               |               |             |        |       |       |  |

| bit 7   |                               |               | ip Enable bit                 |               |             |        |       |       |  |

|         |                               |               | are disabled<br>are enabled l | oy individual | PORT latch  | values |       |       |  |

| bit 6   |                               | · ·           | lge Select bi                 | •             |             | Valueo |       |       |  |

| Site    |                               |               | edge of RA                    |               |             |        |       |       |  |

|         | 0 = Interru                   | pt on falling | g edge of RA                  | 2/INT pin     |             |        |       |       |  |

| bit 5   |                               |               | Source Selec                  | t bit         |             |        |       |       |  |

|         |                               |               | 2/T0CKI pin<br>n cycle clock  |               |             |        |       |       |  |

| bit 4   |                               |               | Edge Select                   | · ,           |             |        |       |       |  |

|         |                               |               |                               | sition on RA2 | 2/T0CKI pin |        |       |       |  |

|         | 0 = Increm                    | nent on low   | -to-high trans                | sition on RA2 | 2/T0CKI pin |        |       |       |  |

| bit 3   |                               | scaler Assig  |                               |               |             |        |       |       |  |

|         |                               |               | ned to the V<br>aned to the T | imer0 modul   | e           |        |       |       |  |

| bit 2-0 |                               |               | Rate Select I                 |               | -           |        |       |       |  |

|         |                               | Bit Value     | TMR0 Rate                     | WDT Rate      |             |        |       |       |  |

|         |                               | 000           | 1:2                           | 1:1           |             |        |       |       |  |

|         |                               | 001           | 1:4                           | 1:2           |             |        |       |       |  |

|         |                               | 010           | 1:8                           | 1:4           |             |        |       |       |  |

|         | 011 1:16 1:8<br>100 1:32 1:16 |               |                               |               |             |        |       |       |  |

|         | 101 1:64 1:32                 |               |                               |               |             |        |       |       |  |

|         | 110 <b>1:128 1:64</b>         |               |                               |               |             |        |       |       |  |

|         | 111 <b>1:256 1:128</b>        |               |                               |               |             |        |       |       |  |

|         |                               |               |                               |               |             |        |       |       |  |

|         | · ·                           |               |                               |               |             |        |       | ]     |  |

|         | Legend:                       |               |                               |               |             |        |       |       |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

Note: To achieve a 1:1 prescaler assignment for TMR0, assign the prescaler to the WDT by setting PSA bit to '1' (OPTION<3>). See Section 4.4 "Prescaler".

### 2.2.2.5 PIR1 Register

bit

bit

bit bit

bit bit

The PIR1 register contains the interrupt flag bits, as shown in Register 2-5.

- n = Value at POR

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### REGISTER 2-5: PIR1 — PERIPHERAL INTERRUPT REGISTER 1 (ADDRESS: 0Ch)

|       | R/W-0                                                                                                         | R/W-0                                                                                                                                                                                                                                                                                                                                  | U-0             | U-0          | R/W-0         | U-0       | U-0            | R/W-0  |  |  |  |

|-------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------|---------------|-----------|----------------|--------|--|--|--|

|       | EEIF                                                                                                          | ADIF                                                                                                                                                                                                                                                                                                                                   |                 | _            | CMIF          | _         | _              | TMR1IF |  |  |  |

|       | bit 7                                                                                                         |                                                                                                                                                                                                                                                                                                                                        |                 |              |               |           |                | bit 0  |  |  |  |

| t 7   | 1 = The wr                                                                                                    | ROM Write (<br>ite operation<br>ite operation                                                                                                                                                                                                                                                                                          | completed       | (must be cle | eared in soft | ,         |                |        |  |  |  |

| t 6   | 1 = The A/                                                                                                    | ADIF: A/D Converter Interrupt Flag bit (PIC16F676 only)<br>1 = The A/D conversion is complete (must be cleared in software)<br>0 = The A/D conversion is not complete                                                                                                                                                                  |                 |              |               |           |                |        |  |  |  |

| t 5-4 | Unimplem                                                                                                      | ented: Read                                                                                                                                                                                                                                                                                                                            | <b>l as</b> '0' |              |               |           |                |        |  |  |  |

| t 3   | <b>CMIF</b> : Comparator Interrupt Flag bit<br>1 = Comparator input has changed (must be cleared in software) |                                                                                                                                                                                                                                                                                                                                        |                 |              |               |           |                |        |  |  |  |

| t 2-1 | Unimplem                                                                                                      | ented: Read                                                                                                                                                                                                                                                                                                                            | <b>l as</b> '0' |              |               |           |                |        |  |  |  |

| t 0   | 1 = TMR1                                                                                                      | <ul> <li>1 = Comparator input has changed (must be cleared in software)</li> <li>0 = Comparator input has not changed</li> <li>Unimplemented: Read as '0'</li> <li>TMR1IF: TMR1 Overflow Interrupt Flag bit</li> <li>1 = TMR1 register overflowed (must be cleared in software)</li> <li>0 = TMR1 register did not overflow</li> </ul> |                 |              |               |           |                |        |  |  |  |

|       | Legend:                                                                                                       |                                                                                                                                                                                                                                                                                                                                        |                 |              |               |           |                |        |  |  |  |

|       | R = Reada                                                                                                     | ble bit                                                                                                                                                                                                                                                                                                                                | W = W           | /ritable bit | U = Unim      | plemented | bit, read as ' | 0'     |  |  |  |

'0' = Bit is cleared

'1' = Bit is set

x = Bit is unknown

# 2.2.2.6 PCON Register

The Power Control (PCON) register contains flag bits to differentiate between a:

- · Power-on Reset (POR)

- Brown-out Detect (BOD)

- Watchdog Timer Reset (WDT)

- External MCLR Reset

The PCON Register bits are shown in Register 2-6.

### REGISTER 2-6: PCON — POWER CONTROL REGISTER (ADDRESS: 8Eh)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-x |

|-------|-----|-----|-----|-----|-----|-------|-------|

| _     | _   | _   | —   | _   | -   | POR   | BOD   |

| bit 7 |     |     |     |     |     |       | bit 0 |

bit 7-2 Unimplemented: Read as '0'

bit 1 **POR:** Power-on Reset Status bit

1 = No Power-on Reset occurred

0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

bit 0 BOD: Brown-out Detect Status bit

- 1 = No Brown-out Detect occurred

- 0 = A Brown-out Detect occurred (must be set in software after a Brown-out Detect occurs)

| Legend:            |                  |                                    |                    |  |  |

|--------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit   | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

## 2.2.2.7 OSCCAL Register

bit 7-2

bit 1-0

The Oscillator Calibration register (OSCCAL) is used to calibrate the internal 4 MHz oscillator. It contains 6 bits to adjust the frequency up or down to achieve 4 MHz.

The OSCCAL register bits are shown in Register 2-7.

### REGISTER 2-7: OSCCAL—INTERNALOSCILLATOR CALIBRATION REGISTER (ADDRESS: 90h)

|             |                                            |          |             |             |            |                | -      |

|-------------|--------------------------------------------|----------|-------------|-------------|------------|----------------|--------|

| R/W-1       | R/W-0                                      | R/W-0    | R/W-0       | R/W-0       | R/W-0      | U-0            | U-0    |

| CAL5        | CAL4                                       | CAL3     | CAL2        | CAL1        | CAL0       | _              | _      |

| bit 7       |                                            |          |             |             |            |                | bit    |

| 100000 = 0  | Maximum fro<br>Center frequ<br>Minimum fre | iency    |             |             |            |                |        |

| Unimplem    | ented: Read                                | d as '0' |             |             |            |                |        |

| Legend:     |                                            |          |             |             |            |                |        |

| R = Reada   | ble bit                                    | W = W    | ritable bit | U = Unin    | nplemented | bit, read as ' | ʻ0'    |

| - n = Value | at POR                                     | '1' = B  | it is set   | '0' = Bit i | s cleared  | x = Bit is u   | nknown |

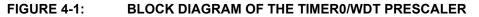

# 4.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- · Interrupt on overflow from FFh to 00h

- Edge select for external clock

Figure 4-1 is a block diagram of the Timer0 module and the prescaler shared with the WDT.

| Note: | Additional                                            | information | on | the | Timer0 |  |  |

|-------|-------------------------------------------------------|-------------|----|-----|--------|--|--|

|       | module is available in the PIC <sup>®</sup> Mid-Range |             |    |     |        |  |  |

|       | Reference Manual, (DS33023).                          |             |    |     |        |  |  |

### 4.1 Timer0 Operation

Timer mode is selected by clearing the T0CS bit (OPTION\_REG<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If TMR0 is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting the T0CS bit (OPTION\_REG<5>). In this mode, the Timer0 module will increment either on every rising or falling edge of pin RA2/T0CKI. The incrementing edge is determined by the source edge (T0SE) control bit (OPTION\_REG<4>). Clearing the T0SE bit selects the rising edge.

| Note: | requirements.           | Additional | ic external clock<br>information on<br>lable in the PIC <sup>®</sup> |

|-------|-------------------------|------------|----------------------------------------------------------------------|

|       | Mid-Range<br>(DS33023). | Reference  | ce Manual,                                                           |

# 4.2 Timer0 Interrupt

A Timer0 interrupt is generated when the TMR0 register timer/counter overflows from FFh to 00h. This overflow sets the T0IF bit. The interrupt can be masked by clearing the T0IE bit (INTCON<5>). The T0IF bit (INTCON<2>) must be cleared in software by the Timer0 module Interrupt Service Routine before reenabling this interrupt. The Timer0 interrupt cannot wake the processor from Sleep since the timer is shut-off during Sleep.

# 5.1 Timer1 Modes of Operation

Timer1 can operate in one of three modes:

- 16-bit timer with prescaler

- 16-bit synchronous counter

- · 16-bit asynchronous counter

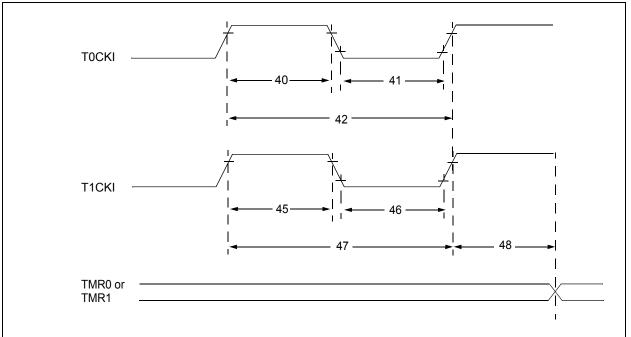

FIGURE 5-2:

In Timer mode, Timer1 is incremented on every instruction cycle. In Counter mode, Timer1 is incremented on the rising edge of the external clock input T1CKI. In addition, the Counter mode clock can be synchronized to the microcontroller system clock or run asynchronously.

In counter and timer modules, the counter/timer clock can be gated by the  $\overline{T1G}$  input.

If an external clock oscillator is needed (and the microcontroller is using the INTOSC w/o CLKOUT), Timer1 can use the LP oscillator as a clock source.

| Note: | In Counter mode, a falling edge must be      |  |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|--|

|       | registered by the counter prior to the first |  |  |  |  |  |

|       | incrementing rising edge.                    |  |  |  |  |  |

TIMER1 INCREMENTING EDGE

# 5.2 Timer1 Interrupt

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit (PIR1<0>) is set. To enable the interrupt on rollover, you must set these bits:

- Timer1 interrupt Enable bit (PIE1<0>)

- PEIE bit (INTCON<6>)

- GIE bit (INTCON<7>).

The interrupt is cleared by clearing the TMR1IF in the Interrupt Service Routine.

Note: The TMR1H:TTMR1L register pair and the TMR1IF bit should be cleared before enabling interrupts.

# 5.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4, or 8 divisions of the clock input. The T1CKPS bits (T1CON<5:4>) control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

# T1CKI = 1 when TMR1 Enabled T1CKI = 0 when TMR1 Enabled Note 1: Arrows indicate counter increments. 2: In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge of the clock.

| SISTER 5-1: T1CON — TIMER1 CONTROL REGISTER (ADDRESS: 10h) |                                                            |                                                                                                 |             |                |                |           |              |         |  |  |

|------------------------------------------------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------|----------------|----------------|-----------|--------------|---------|--|--|

|                                                            | U-0                                                        | R/W-0                                                                                           | R/W-0       | R/W-0          | R/W-0          | R/W-0     | R/W-0        | R/W-0   |  |  |

|                                                            | —                                                          | TMR1GE                                                                                          | T1CKPS1     | T1CKPS0        | T1OSCEN        | T1SYNC    | TMR1CS       | TMR10N  |  |  |

|                                                            | bit 7                                                      |                                                                                                 |             |                |                |           |              | bit 0   |  |  |

| bit 7                                                      | Unimplem                                                   | ented: Read                                                                                     | as '0'      |                |                |           |              |         |  |  |

| bit 6                                                      | -                                                          | Timer1 Gate                                                                                     |             |                |                |           |              |         |  |  |

|                                                            | If TMR10                                                   |                                                                                                 |             |                |                |           |              |         |  |  |

|                                                            | This bit is i<br>If TMR10N                                 |                                                                                                 |             |                |                |           |              |         |  |  |

|                                                            |                                                            | is on if T1G                                                                                    | pin is low  |                |                |           |              |         |  |  |

|                                                            | 0 = Timer1                                                 |                                                                                                 |             |                |                |           |              |         |  |  |

| bit 5-4                                                    |                                                            | :T1CKPS0: T                                                                                     | •           | t Clock Pres   | scale Select I | oits      |              |         |  |  |

|                                                            | -                                                          | rescale Value<br>rescale Value                                                                  |             |                |                |           |              |         |  |  |

|                                                            |                                                            | rescale Value                                                                                   |             |                |                |           |              |         |  |  |

|                                                            | 00 <b>= 1:1 P</b>                                          | rescale Value                                                                                   | 9           |                |                |           |              |         |  |  |

| bit 3                                                      |                                                            | : LP Oscillato                                                                                  |             |                |                |           |              |         |  |  |

|                                                            |                                                            | If INTOSC without CLKOUT oscillator is active:<br>1 = LP oscillator is enabled for Timer1 clock |             |                |                |           |              |         |  |  |

|                                                            |                                                            | illator is off                                                                                  |             |                |                |           |              |         |  |  |

|                                                            | <u>Else:</u><br>This hit is i                              | aparad                                                                                          |             |                |                |           |              |         |  |  |

| bit 2                                                      | This bit is i                                              | gnored<br>Timer1 Exteri                                                                         | aal Clock I | nnut Synchr    | onization Co   | atrol bit |              |         |  |  |

| DIL Z                                                      | TMR1CS =                                                   |                                                                                                 |             | iiput Synchii  |                |           |              |         |  |  |

|                                                            | 1 = Do not synchronize external clock input                |                                                                                                 |             |                |                |           |              |         |  |  |

|                                                            | 0 = Synchronize external clock input<br><u>TMR1CS = 0:</u> |                                                                                                 |             |                |                |           |              |         |  |  |

|                                                            |                                                            | <u>gnored</u> . Time                                                                            | er1 uses th | e internal clo | ock.           |           |              |         |  |  |

| bit 1                                                      | TMR1CS:                                                    | Timer1 Clock                                                                                    | Source S    | elect bit      |                |           |              |         |  |  |

|                                                            |                                                            | al clock from                                                                                   |             | 1CKI pin (on   | the rising ed  | lge)      |              |         |  |  |

| h# 0                                                       |                                                            | al clock (Fosc                                                                                  | -           |                |                |           |              |         |  |  |

| bit 0                                                      | 1 = Enable                                                 | Timer1 On b<br>s Timer1                                                                         | IL          |                |                |           |              |         |  |  |

|                                                            | 0 = Stops                                                  | Timer1                                                                                          |             |                |                |           |              |         |  |  |

|                                                            | Legend:                                                    |                                                                                                 |             |                |                |           |              |         |  |  |

|                                                            | R = Reada                                                  | able bit                                                                                        | VV = V      | Vritable bit   | U = Unim       | plemented | bit, read as | '0'     |  |  |

|                                                            | - n = Value                                                | e at POR                                                                                        | '1' = E     | Bit is set     | '0' = Bit is   | s cleared | x = Bit is u | Inknown |  |  |

# REGISTER 5-1: T1CON — TIMER1 CONTROL REGISTER (ADDRESS: 10h)

|                    | R/W-0                                                                                                                                                                   | R/W-0                                                                                                                                          | U-0                                                                              | R/W-0                                                                      | R/W-0                                       | R/W-0                     | R/W-0                              | R/W-0             |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------|---------------------------|------------------------------------|-------------------|

|                    | ADFM                                                                                                                                                                    | VCFG                                                                                                                                           | _                                                                                | CHS2                                                                       | CHS1                                        | CHS0                      | GO/DONE                            | ADON              |

|                    | bit 7                                                                                                                                                                   |                                                                                                                                                |                                                                                  |                                                                            |                                             |                           |                                    | bit 0             |

|                    |                                                                                                                                                                         |                                                                                                                                                |                                                                                  |                                                                            |                                             |                           |                                    |                   |

| bit 7              | <b>ADFM:</b> A/E<br>1 = Right ju<br>0 = Left jus                                                                                                                        |                                                                                                                                                | med Select                                                                       | bit                                                                        |                                             |                           |                                    |                   |

| bit 6              |                                                                                                                                                                         | VCFG: Voltage Reference bit<br>1 = VREF pin                                                                                                    |                                                                                  |                                                                            |                                             |                           |                                    |                   |

| bit 5              | Unimplem                                                                                                                                                                | ented: Rea                                                                                                                                     | d as zero                                                                        |                                                                            |                                             |                           |                                    |                   |

| bit 4-2            | 000 = Cha<br>001 = Cha<br>010 = Cha<br>011 = Cha<br>100 = Cha<br>101 = Cha<br>110 = Cha                                                                                 | 60: Analog (<br>annel 00 (AN<br>annel 01 (AN<br>annel 02 (AN<br>annel 03 (AN<br>annel 04 (AN<br>annel 05 (AN<br>annel 06 (AN<br>annel 07 (AN   | NO)<br>N1)<br>N2)<br>N3)<br>N4)<br>N5)<br>N6)                                    | ect bits                                                                   |                                             |                           |                                    |                   |

| bit 1              | GO/DONE<br>1 = A/D co<br>This bit                                                                                                                                       | A/D Conve                                                                                                                                      | rsion Status<br>cle in progre<br>cally cleared                                   | ss. Setting f<br>d by hardwa                                               |                                             |                           | nversion cycle<br>rsion has com    |                   |

| bit 0              | 1 = A/D co                                                                                                                                                              | D Conversio<br>nverter mod<br>nverter is sh                                                                                                    | ule is opera                                                                     | -                                                                          | o operating o                               | current                   |                                    |                   |

|                    | Logond                                                                                                                                                                  |                                                                                                                                                |                                                                                  |                                                                            |                                             |                           |                                    |                   |

|                    | Legend:                                                                                                                                                                 | blo bit                                                                                                                                        | ۱۵/ – ۱۸                                                                         | <i>I</i> ritabla bit                                                       |                                             | nnlomontor                | hit road as '(                     | )'                |

|                    | R = Reada                                                                                                                                                               |                                                                                                                                                |                                                                                  | /ritable bit                                                               |                                             | •                         | l bit, read as '(                  |                   |

|                    | -                                                                                                                                                                       |                                                                                                                                                |                                                                                  | /ritable bit<br>it is set                                                  |                                             | nplemented<br>is cleared  | l bit, read as '(<br>x = Bit is ur |                   |

| REGISTER 7-2:      | R = Reada<br>- n = Value                                                                                                                                                | at POR                                                                                                                                         | '1' = B                                                                          | it is set                                                                  | '0' = Bit                                   | is cleared                |                                    |                   |

| REGISTER 7-2:      | R = Reada<br>- n = Value<br>ADCON1 ·                                                                                                                                    | at POR<br>— <b>A/D CO</b>                                                                                                                      | '1' = B                                                                          | it is set<br>EGISTER 1                                                     | '0' = Bit                                   | is cleared                | x = Bit is ur                      | iknown            |

| REGISTER 7-2:      | R = Reada<br>- n = Value                                                                                                                                                | at POR<br>— <b>A/D CO</b><br>R/W-0                                                                                                             | '1' = B<br>NTROL RE<br>R/W-0                                                     | it is set<br>EGISTER 1<br>R/W-0                                            | '0' = Bit                                   | is cleared                |                                    |                   |

| REGISTER 7-2:      | R = Reada<br>- n = Value<br>ADCON1 -<br>U-0<br>—                                                                                                                        | at POR<br>— A/D CO                                                                                                                             | '1' = B                                                                          | it is set<br>EGISTER 1                                                     | '0' = Bit                                   | is cleared                | x = Bit is ur                      | U-0               |

| REGISTER 7-2:      | R = Reada<br>- n = Value<br>ADCON1 ·                                                                                                                                    | at POR<br>— <b>A/D CO</b><br>R/W-0                                                                                                             | '1' = B<br>NTROL RE<br>R/W-0                                                     | it is set<br>EGISTER 1<br>R/W-0                                            | '0' = Bit                                   | is cleared                | x = Bit is ur                      | iknown            |

|                    | R = Reada<br>- n = Value<br>ADCON1 -<br>U-0<br>bit 7                                                                                                                    | at POR<br>— A/D CO<br>R/W-0<br>ADCS2                                                                                                           | '1' = B<br>NTROL RE<br>R/W-0<br>ADCS1                                            | it is set<br>EGISTER 1<br>R/W-0                                            | '0' = Bit                                   | is cleared                | x = Bit is ur                      | U-0               |

| bit 7:             | R = Reada<br>- n = Value<br>ADCON1 -<br>U-0<br>bit 7<br>Unimplem                                                                                                        | at POR<br>– A/D CO<br>R/W-0<br>ADCS2<br>ented: Rea                                                                                             | '1' = B<br>NTROL RI<br>R/W-0<br>ADCS1<br>d as '0'                                | it is set<br>EGISTER 1<br>R/W-0<br>ADCS0                                   | '0' = Bit i<br>I <b>(ADRESS</b><br>U-0<br>— | is cleared                | x = Bit is ur                      | U-0               |

|                    | R = Reada<br>- n = Value<br>ADCON1 -<br>U-0<br>bit 7<br>Unimplem<br>ADCS<2:0                                                                                            | at POR<br>— A/D CO<br>R/W-0<br>ADCS2<br>ented: Read                                                                                            | '1' = B<br>NTROL RI<br>R/W-0<br>ADCS1<br>d as '0'                                | it is set<br>EGISTER 1<br>R/W-0<br>ADCS0                                   | '0' = Bit i<br>I <b>(ADRESS</b><br>U-0<br>— | is cleared                | x = Bit is ur                      | U-0               |

| bit 7:             | R = Reada<br>- n = Value<br>ADCON1 -<br>U-0<br>bit 7<br>Unimplem                                                                                                        | at POR<br>— A/D CO<br>R/W-0<br>ADCS2<br>ented: Read<br>>: A/D Conv<br>c/2<br>c/8                                                               | '1' = B<br>NTROL RI<br>R/W-0<br>ADCS1<br>d as '0'                                | it is set<br>EGISTER 1<br>R/W-0<br>ADCS0                                   | '0' = Bit i<br>I <b>(ADRESS</b><br>U-0<br>— | is cleared                | x = Bit is ur                      | U-0               |

| bit 7:             | R = Reada<br>- n = Value<br>ADCON1 -<br>U-0<br>bit 7<br>Unimplem<br>ADCS<2:0<br>000 = Fos<br>001 = Fos<br>010 = Fos<br>x11 = FRC<br>100 = Fos                           | at POR<br>— A/D CO<br>R/W-0<br>ADCS2<br>ented: Read<br>>: A/D Conv<br>c/2<br>c/8<br>c/32<br>(clock derive<br>c/4<br>c/16                       | '1' = B<br>NTROL RI<br>R/W-0<br>ADCS1<br>d as '0'<br>version Cloc                | it is set<br>EGISTER 1<br>R/W-0<br>ADCS0                                   | '0' = Bit i<br>I <b>(ADRESS</b><br>U-0<br>— | 6: 9Fh)<br>U-0            | x = Bit is ur<br>U-0               | U-0               |

| bit 7:<br>bit 6-4: | R = Reada<br>- n = Value<br>ADCON1 -<br>U-0<br>bit 7<br>Unimplem<br>ADCS<2:0<br>000 = Fos<br>001 = Fos<br>010 = Fos<br>100 = Fos<br>101 = Fos                           | at POR<br>— A/D CO<br>R/W-0<br>ADCS2<br>ented: Read<br>>: A/D Conv<br>c/2<br>c/8<br>c/32<br>(clock deriv<br>c/4<br>c/16<br>c/64                | '1' = B<br>NTROL RI<br>R/W-0<br>ADCS1<br>d as '0'<br>version Cloc<br>ed from a d | it is set<br>EGISTER 1<br>R/W-0<br>ADCS0                                   | '0' = Bit i<br>I <b>(ADRESS</b><br>U-0<br>— | 6: 9Fh)<br>U-0            | x = Bit is ur<br>U-0               | U-0               |

| bit 7:             | R = Reada<br>- n = Value<br>ADCON1 -<br>U-0<br>bit 7<br>Unimplem<br>ADCS<2:0<br>000 = Fos<br>001 = Fos<br>010 = Fos<br>100 = Fos<br>101 = Fos                           | at POR<br>— A/D CO<br>R/W-0<br>ADCS2<br>ented: Read<br>>: A/D Conv<br>c/2<br>c/8<br>c/32<br>(clock derive<br>c/4<br>c/16                       | '1' = B<br>NTROL RI<br>R/W-0<br>ADCS1<br>d as '0'<br>version Cloc<br>ed from a d | it is set<br>EGISTER 1<br>R/W-0<br>ADCS0                                   | '0' = Bit i<br>I <b>(ADRESS</b><br>U-0<br>— | 6: 9Fh)<br>U-0            | x = Bit is ur<br>U-0               | U-0               |

| bit 7:<br>bit 6-4: | R = Reada<br>- n = Value<br>ADCON1 -<br>U-0<br>bit 7<br>Unimplem<br>ADCS<2:0<br>000 = Fos<br>010 = Fos<br>010 = Fos<br>110 = Fos<br>101 = Fos<br>110 = Fos              | at POR<br>— A/D CO<br>R/W-0<br>ADCS2<br>ented: Read<br>>: A/D Conv<br>c/2<br>c/8<br>c/32<br>(clock deriv<br>c/4<br>c/16<br>c/64                | '1' = B<br>NTROL RI<br>R/W-0<br>ADCS1<br>d as '0'<br>version Cloc<br>ed from a d | it is set<br>EGISTER 1<br>R/W-0<br>ADCS0                                   | '0' = Bit i<br>I <b>(ADRESS</b><br>U-0<br>— | 6: 9Fh)<br>U-0            | x = Bit is ur<br>U-0               | U-0               |

| bit 7:<br>bit 6-4: | R = Reada<br>- n = Value<br>ADCON1 -<br>U-0<br>bit 7<br>Unimplem<br>ADCS<2:0<br>000 = Fos<br>001 = Fos<br>010 = Fos<br>100 = Fos<br>101 = Fos<br>101 = Fos<br>101 = Fos | at POR<br>— A/D CO<br>R/W-0<br>ADCS2<br>ented: Read<br>>: A/D Conv<br>C/2<br>C/8<br>C/32<br>(clock deriv<br>C/4<br>C/16<br>C/64<br>ented: Read | '1' = B<br>NTROL RI<br>R/W-0<br>ADCS1<br>d as '0'<br>version Cloc<br>ed from a d | it is set<br>EGISTER 1<br>R/W-0<br>ADCS0                                   | '0' = Bit i<br>I (ADRESS<br>U-0<br>—        | s: 9Fh)<br>U-0            | x = Bit is ur<br>U-0<br>           | U-0               |

| bit 7:<br>bit 6-4: | R = Reada<br>- n = Value<br>ADCON1 -<br>U-0<br>bit 7<br>Unimplem<br>ADCS<2:0<br>000 = Fos<br>010 = Fos<br>010 = Fos<br>110 = Fos<br>101 = Fos<br>110 = Fos              | at POR<br>— A/D CO<br>R/W-0<br>ADCS2<br>ented: Read<br>>: A/D Conv<br>C/2<br>C/8<br>C/32<br>(clock deriv<br>C/4<br>C/16<br>C/64<br>ented: Read | '1' = B<br>NTROL RI<br>R/W-0<br>ADCS1<br>d as '0'<br>version Cloc<br>ed from a d | it is set<br>EGISTER 1<br>R/W-0<br>ADCS0<br>k Select bits<br>edicated inte | '0' = Bit i<br>I (ADRESS<br>U-0<br>—        | s: <b>9Fh)</b><br>U-0<br> | x = Bit is ur<br>U-0               | U-0<br>—<br>bit 0 |

# REGISTER 7-1: ADCON0 — A/D CONTROL REGISTER (ADDRESS: 1Fh)

# 7.3 A/D Operation During Sleep

The A/D converter module can operate during Sleep. This requires the A/D clock source to be set to the internal oscillator. When the RC clock source is selected, the A/D waits one instruction before starting the conversion. This allows the SLEEP instruction to be executed, thus eliminating much of the switching noise from the conversion. When the conversion is complete, the GO/DONE bit is cleared, and the result is loaded into the ADRESH:ADRESL registers. If the A/D interrupt is enabled, the device awakens from Sleep. If the A/D interrupt is not enabled, the A/D module is turned off, although the ADON bit remains set. When the A/D clock source is something other than RC, a SLEEP instruction causes the present conversion to be aborted, and the A/D module is turned off. The ADON bit remains set.

# 7.4 Effects of Reset

A device Reset forces all registers to their Reset state. Thus, the A/D module is turned off and any pending conversion is aborted. The ADRESH:ADRESL registers are unchanged.

| IADLL    |        |            |                | DIVEOR        |             |               |               |               |           |                      |                                 |

|----------|--------|------------|----------------|---------------|-------------|---------------|---------------|---------------|-----------|----------------------|---------------------------------|

| Address  | Name   | Bit 7      | Bit 6          | Bit 5         | Bit 4       | Bit 3         | Bit 2         | Bit 1         | Bit 0     | Value on<br>POR, BOD | Value on<br>all other<br>Resets |

| 05h      | PORTA  | —          | —              | PORTA5        | PORTA4      | PORTA3        | PORTA2        | PORTA1        | PORTA0    | xx xxxx              | uu uuuu                         |

| 07h      | PORTC  | —          | _              | PORTC5        | PORTC4      | PORTC3        | PORTC2        | PORTC1        | PORTC0    | xx xxxx              | uu uuuu                         |

| 0Bh, 8Bh | INTCON | GIE        | PEIE           | T0IE          | INTE        | RAIE          | T0IF          | INTF          | RAIF      | 0000 0000            | 0000 000u                       |

| 0Ch      | PIR1   | EEIF       | ADIF           | —             | _           | CMIF          | —             | _             | TMR1IF    | 00 00                | 00 00                           |

| 1Eh      | ADRESH | Most Signi | ficant 8 bits  | of the Left   | Shifted A/D | result or 2 l | bits of the R | light Shifted | Result    | XXXX XXXX            | uuuu uuuu                       |

| 1Fh      | ADCON0 | ADFM       | VCFG           | —             | CHS2        | CHS1          | CHS0          | GO            | ADON      | 00-0 0000            | 00-0 0000                       |

| 85h      | TRISA  | —          | _              | TRISA5        | TRISA4      | TRISA3        | TRISA2        | TRISA1        | TRISA0    | 11 1111              | 11 1111                         |

| 87h      | TRISC  | —          | _              | TRISC5        | TRISC4      | TRISC3        | TRISC2        | TRISC1        | TRISC0    | 11 1111              | 11 1111                         |

| 8Ch      | PIE1   | EEIE       | ADIE           | —             | _           | CMIE          | —             | _             | TMR1IE    | 00 00                | 00 00                           |

| 91h      | ANSEL  | ANS7       | ANS6           | ANS5          | ANS4        | ANS3          | ANS2          | ANS1          | ANS0      | 1111 1111            | 1111 1111                       |

| 9Eh      | ADRESL | Least Sign | ificant 2 bits | s of the Left | Shifted A/D | Result or 8   | 3 bits of the | Right Shifte  | ed Result | XXXX XXXX            | uuuu uuuu                       |

| 9Fh      | ADCON1 |            | ADCS2          | ADCS1         | ADCS0       | _             | —             | _             | —         | -000                 | -000                            |

TABLE 7-2: SUMMARY OF A/D REGISTERS

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for A/D converter module.

# 9.0 SPECIAL FEATURES OF THE CPU

Certain special circuits that deal with the needs of real time applications are what sets a microcontroller apart from other processors. The PIC16F630/676 family has a host of such features intended to:

- maximize system reliability

- minimize cost through elimination of external components

- provide power-saving operating modes and offer code protection

These features are:

- Oscillator selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Detect (BOD)

- Interrupts

- Watchdog Timer (WDT)

- Sleep

- Code protection

- · ID Locations

- In-Circuit Serial Programming<sup>™</sup>

The PIC16F630/676 has a Watchdog Timer that is controlled by Configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in Reset while the power supply stabilizes. There is also circuitry to reset the device if a brown-out occurs, which can provide at least a 72 ms Reset. With these three functions on-chip, most applications need no external Reset circuitry.

The Sleep mode is designed to offer a very low current Power-down mode. The user can wake-up from Sleep through:

- · External Reset

- · Watchdog Timer wake-up

- An interrupt

Several oscillator options are also made available to allow the part to fit the application. The INTOSC option saves system cost while the LP crystal option saves power. A set of Configuration bits are used to select various options (see Register 9-1).

# 9.2 Oscillator Configurations

### 9.2.1 OSCILLATOR TYPES

The PIC16F630/676 can be operated in eight different Oscillator Option modes. The user can program three Configuration bits (FOSC2 through FOSC0) to select one of these eight modes:

- LP Low-Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC External Resistor/Capacitor (2 modes)

- · INTOSC Internal Oscillator (2 modes)

- EC External Clock In

| Note: | Additional information on oscillator config-<br>urations is available in the PIC <sup>®</sup> Mid-Range |

|-------|---------------------------------------------------------------------------------------------------------|

|       | Reference Manual, (DS33023).                                                                            |

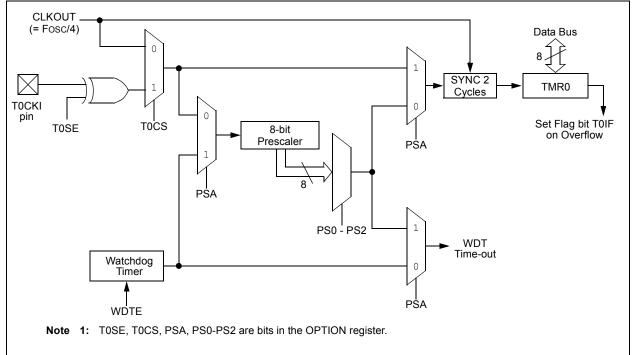

# 9.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

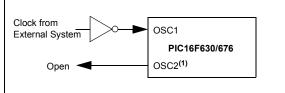

In XT, LP or HS modes a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation (see Figure 9-1). The PIC16F630/676 oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may yield a frequency outside of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1 pin (see Figure 9-2).

### FIGURE 9-1: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (HS, XT OR LP OSC CONFIGURATION)

### EXTERNAL CLOCK INPUT OPERATION (HS, XT, EC, OR LP OSC CONFIGURATION)

Note 1: Functions as RA4 in EC Osc mode.

# TABLE 9-1:CAPACITOR SELECTION FOR<br/>CERAMIC RESONATORS

| Ranges Characterized:                                                                                                                                                                                                                                                                                     |                               |                                   |                                   |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------------------|-----------------------------------|--|

| Mode                                                                                                                                                                                                                                                                                                      | Freq                          | OSC1(C1)                          | OSC2(C2)                          |  |

| ХТ                                                                                                                                                                                                                                                                                                        | 455 kHz<br>2.0 MHz<br>4.0 MHz | 68-100 pF<br>15-68 pF<br>15-68 pF | 68-100 pF<br>15-68 pF<br>15-68 pF |  |

| HS                                                                                                                                                                                                                                                                                                        | 8.0 MHz<br>16.0 MHz           | 10-68 pF<br>10-22 pF              | 10-68 pF<br>10-22 pF              |  |

| Note 1: Higher capacitance increases the stability of the oscillator but also increases the start-up time. These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components. |                               |                                   |                                   |  |

### TABLE 9-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR

| Mode                                               | Freq                      | OSC1(C1)                          | OSC2(C2)                           |

|----------------------------------------------------|---------------------------|-----------------------------------|------------------------------------|

| LP                                                 | 32 kHz                    | 68-100 pF                         | 68-100 pF                          |

| ХТ                                                 | 100 kHz<br>2 MHz<br>4 MHz | 68-150 pF<br>15-30 pF<br>15-30 pF | 150-200 pF<br>15-30 pF<br>15-30 pF |

| HS                                                 | 8 MHz<br>10 MHz<br>20 MHz | 15-30 pF<br>15-30 pF<br>15-30 pF  | 15-30 pF<br>15-30 pF<br>15-30 pF   |

| Note 1: Higher capacitance increases the stability |                           |                                   |                                    |

of the oscillator but also increases the start-up time. These values are for design guidance only. Rs may be required in HS mode as well as XT mode to avoid overdriving crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

# 9.8 Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

**Note:** The entire data EEPROM and Flash program memory will be erased when the code protection is turned off. The INTOSC calibration data is also erased. See PIC16F630/676 Programming Specification for more information.

# 9.9 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution but are readable and writable during Program/Verify. Only the Least Significant 7 bits of the ID locations are used.

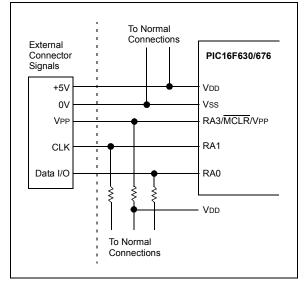

### 9.10 In-Circuit Serial Programming

The PIC16F630/676 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for:

- power

- ground

- programming voltage

This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a Program/Verify mode by holding the RA0 and RA1 pins low, while raising the MCLR (VPP) pin from VIL to VIHH (see Programming Specification). RA0 becomes the programming data and RA1 becomes the programming clock. Both RA0 and RA1 are Schmitt Trigger inputs in this mode.

After Reset, to place the device into Programming/Verify mode, the program counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14 bits of program data are then supplied to or from the device, depending on whether the command was a load or a read. For complete details of serial programming, please refer to the PIC16F630/676 Programming Specification.

A typical In-Circuit Serial Programming connection is shown in Figure 9-14.

#### FIGURE 9-14:

### TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

# 9.11 In-Circuit Debugger

Since in-circuit debugging requires the loss of clock, data and MCLR pins, MPLAB<sup>®</sup> ICD 2 development with an 14-pin device is not practical. A special 20-pin PIC16F676-ICD device is used with MPLAB ICD 2 to provide separate clock, data and MCLR pins and frees all normally available pins to the user.

This special ICD device is mounted on the top of the header and its signals are routed to the MPLAB ICD 2 connector. On the bottom of the header is an 14-pin socket that plugs into the user's target via the 14-pin stand-off connector.

When the ICD pin on the PIC16F676-ICD device is held low, the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB ICD 2. When the microcontroller has this feature enabled, some of the resources are not available for general use. Table 9-10 shows which features are consumed by the background debugger:

### TABLE 9-10: DEBUGGER RESOURCES

| I/O pins       | ICDCLK, ICDDATA                     |

|----------------|-------------------------------------|

| Stack          | 1 level                             |

| Program Memory | Address 0h must be NOP<br>300h-3FEh |

For more information, see 14-Pin MPLAB ICD 2 Header Information Sheet (DS51292) available on Microchip's web site (www.microchip.com).

| MOVF             | Move f                                                                                                                                                                                                                                                                            |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                         |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                       |

| Operation:       | (f) $\rightarrow$ (destination)                                                                                                                                                                                                                                                   |

| Status Affected: | Z                                                                                                                                                                                                                                                                                 |

| Description:     | The contents of register f are<br>moved to a destination dependant<br>upon the status of d. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register f itself.<br>d = 1 is useful to test a file register,<br>since status flag Z is affected. |

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| MOVLW            | Move Literal to W                                                                                |

|------------------|--------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                         |

| Operands:        | $0 \leq k \leq 255$                                                                              |

| Operation:       | $k \rightarrow (W)$                                                                              |

| Status Affected: | None                                                                                             |

| Description:     | The eight-bit literal 'k' is loaded<br>into W register. The don't cares<br>will assemble as 0's. |

| RETFIE           | Return from Interrupt                        |

|------------------|----------------------------------------------|

| Syntax:          | [label] RETFIE                               |

| Operands:        | None                                         |

| Operation:       | TOS $\rightarrow$ PC,<br>1 $\rightarrow$ GIE |

| Status Affected: | None                                         |

| MOVWF            | Move W to f                                |

|------------------|--------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVWF f                   |