Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 12                                                                       |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 64 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                           |

| Supplier Device Package    | 14-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f630-e-sl |

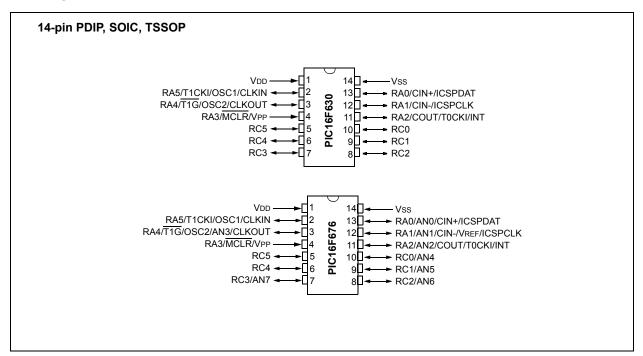

#### **Pin Diagrams**

#### **Table of Contents**

| 1.0                             | Device Overview                                           | 7   |  |  |  |  |

|---------------------------------|-----------------------------------------------------------|-----|--|--|--|--|

| 2.0                             | Memory Organization                                       |     |  |  |  |  |

| 3.0                             | Ports A and C                                             | 21  |  |  |  |  |

| 4.0 Timer0 Module               |                                                           |     |  |  |  |  |

| 5.0                             | Timer1 Module with Gate Control                           | 34  |  |  |  |  |

| 6.0                             | Comparator Module                                         | 39  |  |  |  |  |

| 7.0                             | Analog-to-Digital Converter (A/D) Module (PIC16F676 only) | 45  |  |  |  |  |

| 8.0                             | Data EEPROM Memory                                        | 51  |  |  |  |  |

| 9.0 Special Features of the CPU |                                                           |     |  |  |  |  |

| 10.0 Instruction Set Summary    |                                                           |     |  |  |  |  |

| 11.0 Development Support        |                                                           |     |  |  |  |  |

| 12.0 Electrical Specifications  |                                                           |     |  |  |  |  |

| 13.0                            | DC and AC Characteristics Graphs and Tables               | 107 |  |  |  |  |

| 14.0                            | Packaging Information                                     | 117 |  |  |  |  |

| Appe                            | ndix A: Data Sheet Revision History                       | 123 |  |  |  |  |

| Appe                            | ndix B: Device Differences                                | 123 |  |  |  |  |

| Appe                            | ndix C: Device Migrations                                 | 124 |  |  |  |  |

| Appe                            | ndix D: Migrating from other PIC <sup>®</sup> Devices     | 124 |  |  |  |  |

| Index                           | · · · · · · · · · · · · · · · · · · ·                     | 125 |  |  |  |  |

| On-Line Support                 |                                                           |     |  |  |  |  |

| Syste                           | ems Information and Upgrade Hot Line                      | 129 |  |  |  |  |

| Read                            | er Response                                               | 130 |  |  |  |  |

| Produ                           | uct Identification System                                 | 131 |  |  |  |  |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

#### 2.2.2.1 STATUS Register

The STATUS register, shown in Register 2-1, contains:

- · the arithmetic status of the ALU

- · the Reset status

- · the bank select bits for data memory (SRAM)

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits, see **Section 10.0 "Instruction Set Summary"**.

- Note 1: Bits IRP and RP1 (STATUS<7:6>) are not used by the PIC16F630/676 and should be maintained as clear. Use of these bits is not recommended, since this may affect upward compatibility with future products.

- 2: The C and DC bits operate as a Borrow and Digit Borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

#### REGISTER 2-1: STATUS — STATUS REGISTER (ADDRESS: 03h OR 83h)

| Reserved | Reserved | R/W-0 | R-1 | R-1 | R/W-x | R/W-x | R/W-x |

|----------|----------|-------|-----|-----|-------|-------|-------|

| IRP      | RP1      | RP0   | TO  | PD  | Z     | DC    | С     |

| bit 7    |          |       |     |     |       |       | bit 0 |

| hit 7 IRP: This hit is reserved and should be maintained as '0' |       |           |              |                |                      |

|-----------------------------------------------------------------|-------|-----------|--------------|----------------|----------------------|

|                                                                 | hit 7 | IDD: Thic | hit in rooms | d and should l | ha maintainad aa '∩' |

bit 6 **RP1:** This bit is reserved and should be maintained as '0'

bit 5 **RP0:** Register Bank Select bit (used for direct addressing)

1 = Bank 1 (80h-FFh)

0 = Bank 0 (00h-7Fh)

bit 4 **TO:** Time-out bit

1 = After power-up, CLRWDT instruction, or SLEEP instruction

0 = A WDT time-out occurred

bit 3 **PD**: Power-Down bit

1 = After power-up or by the CLRWDT instruction

0 = By execution of the SLEEP instruction

bit 2 **Z**: Zero bit

1 = The result of an arithmetic or logic operation is zero

0 = The result of an arithmetic or logic operation is not zero

bit 1 DC: Digit carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)

For borrow, the polarity is reversed.

${\tt 1}$  = A carry-out from the 4th low order bit of the result occurred

0 = No carry-out from the 4th low order bit of the result

bit 0 C: Carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)

1 = A carry-out from the Most Significant bit of the result occurred

$_{0}$  = No carry-out from the Most Significant bit of the result occurred

**Note:** For borrow the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high or low order bit of the source register.

| _ | _ | _                     | - | ᆈ |   |

|---|---|-----------------------|---|---|---|

| μ | a | $\boldsymbol{\omega}$ | п | а | п |

|   |   |                       |   |   |   |

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

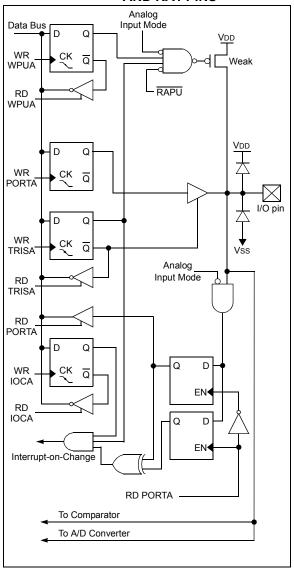

### 3.2.3 PIN DESCRIPTIONS AND DIAGRAMS

Each PORTA pin is multiplexed with other functions. The pins and their combined functions are briefly described here. For specific information about individual functions such as the comparator or the A/D, refer to the appropriate section in this Data Sheet.

#### 3.2.3.1 RA0/AN0/CIN+

Figure 3-1 shows the diagram for this pin. The RA0 pin is configurable to function as one of the following:

- · a general purpose I/O

- an analog input for the A/D (PIC16F676 only)

- · an analog input to the comparator

#### 3.2.3.2 RA1/AN1/CIN-/VREF

Figure 3-1 shows the diagram for this pin. The RA1 pin is configurable to function as one of the following:

- · as a general purpose I/O

- an analog input for the A/D (PIC16F676 only)

- · an analog input to the comparator

- a voltage reference input for the A/D (PIC16F676 only)

FIGURE 3-1: BLOCK DIAGRAM OF RA0

AND RA1 PINS

TABLE 7-1: TAD vs. DEVICE OPERATING FREQUENCIES

| A/D Clock | Source (TAD) | Device Frequency          |                           |                           |                           |  |  |  |

|-----------|--------------|---------------------------|---------------------------|---------------------------|---------------------------|--|--|--|

| Operation | ADCS2:ADCS0  | 20 MHz                    | 5 MHz                     | 4 MHz                     | 1.25 MHz                  |  |  |  |

| 2 Tosc    | 000          | 100 ns <sup>(2)</sup>     | 400 ns <sup>(2)</sup>     | 500 ns <sup>(2)</sup>     | 1.6 μs                    |  |  |  |

| 4 Tosc    | 100          | 200 ns <sup>(2)</sup>     | 800 ns <sup>(2)</sup>     | 1.0 μs <sup>(2)</sup>     | 3.2 μs                    |  |  |  |

| 8 Tosc    | 001          | 400 ns <sup>(2)</sup>     | 1.6 μs                    | 2.0 μs                    | 6.4 μs                    |  |  |  |

| 16 Tosc   | 101          | 800 ns <sup>(2)</sup>     | 3.2 μs                    | 4.0 μs                    | 12.8 μs <sup>(3)</sup>    |  |  |  |

| 32 Tosc   | 010          | 1.6 μs                    | 6.4 μs                    | 8.0 μs <sup>(3)</sup>     | 25.6 μs <sup>(3)</sup>    |  |  |  |

| 64 Tosc   | 110          | 3.2 μs                    | 12.8 μs <sup>(3)</sup>    | 16.0 μs <sup>(3)</sup>    | 51.2 μs <sup>(3)</sup>    |  |  |  |

| A/D RC    | x11          | 2 - 6 μs <sup>(1,4)</sup> |  |  |  |

Legend: Shaded cells are outside of recommended range.

- **Note 1:** The A/D RC source has a typical TAD time of 4  $\mu$ s for VDD > 3.0V.

- 2: These values violate the minimum required TAD time.

- 3: For faster conversion times, the selection of another clock source is recommended.

- **4:** When the device frequency is greater than 1 MHz, the A/D RC clock source is only recommended if the conversion will be performed during Sleep.

#### 7.1.5 STARTING A CONVERSION

The A/D conversion is initiated by setting the GO/DONE bit (ADCON0<1>). When the conversion is complete, the A/D module:

- Clears the GO/DONE bit

- Sets the ADIF flag (PIR1<6>)

- · Generates an interrupt (if enabled)

If the conversion must be aborted, the GO/DONE bit can be cleared in software. The ADRESH:ADRESL registers will not be updated with the partially complete A/D conversion sample. Instead, the ADRESH:ADRESL registers will retain the value of the

previous conversion. After an aborted conversion, a 2 TAD delay is required before another acquisition can be initiated. Following the delay, an input acquisition is automatically started on the selected channel.

**Note:** The GO/DONE bit should not be set in the same instruction that turns on the A/D.

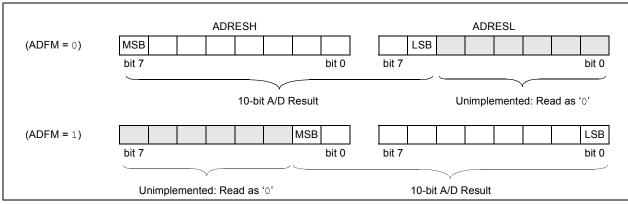

#### 7.1.6 CONVERSION OUTPUT

The A/D conversion can be supplied in two formats: left or right shifted. The ADFM bit (ADCON0<7>) controls the output format. Figure 7-2 shows the output formats.

FIGURE 7-2: 10-BIT A/D RESULT FORMAT

#### REGISTER 7-1: ADCON0 — A/D CONTROL REGISTER (ADDRESS: 1Fh)

| R/W-0 | R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 |

|-------|-------|-----|-------|-------|-------|---------|-------|

| ADFM  | VCFG  | _   | CHS2  | CHS1  | CHS0  | GO/DONE | ADON  |

| hit 7 |       |     |       |       |       |         | hit 0 |

bit 7 ADFM: A/D Result Formed Select bit

1 = Right justified0 = Left justified

bit 6 VCFG: Voltage Reference bit

1 = VREF pin 0 = VDD

bit 5 **Unimplemented:** Read as zero

bit 4-2 CHS2:CHS0: Analog Channel Select bits

000 = Channel 00 (AN0) 001 = Channel 01 (AN1) 010 = Channel 02 (AN2) 011 = Channel 03 (AN3) 100 = Channel 04 (AN4) 101 = Channel 05 (AN5) 110 = Channel 06 (AN6) 111 = Channel 07 (AN7)

bit 1 GO/DONE: A/D Conversion Status bit

1 = A/D conversion cycle in progress. Setting this bit starts an A/D conversion cycle. This bit is automatically cleared by hardware when the A/D conversion has completed.

0 = A/D conversion completed/not in progress

bit 0 ADON: A/D Conversion Status bit

1 = A/D converter module is operating

0 = A/D converter is shut-off and consumes no operating current

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### REGISTER 7-2: ADCON1 — A/D CONTROL REGISTER 1 (ADRESS: 9Fh)

| U-0   | R/W-0 | R/W-0 | R/W-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-------|-------|-----|-----|-----|-------|

| _     | ADCS2 | ADCS1 | ADCS0 | _   | _   | _   | _     |

| hit 7 |       |       |       |     |     |     | hit 0 |

bit 7: **Unimplemented:** Read as '0'

bit 6-4: ADCS<2:0>: A/D Conversion Clock Select bits

000 = Fosc/2 001 = Fosc/8

010 = Fosc/32

x11 = FRC (clock derived from a dedicated internal oscillator = 500 kHz max)

100 = Fosc/4 101 = Fosc/16 110 = Fosc/64

bit 3-0: Unimplemented: Read as '0'

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### 8.1 EEADR

The EEADR register can address up to a maximum of 128 bytes of data EEPROM. Only seven of the eight bits in the register (EEADR<6:0>) are required. The MSb (bit 7) is ignored.

The upper bit should always be '0' to remain upward compatible with devices that have more data EEPROM memory.

### 8.2 EECON1 AND EECON2 REGISTERS

EECON1 is the control register with four low order bits physically implemented. The upper four bits are non-implemented and read as '0's.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared in hardware at completion

of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a MCLR Reset, or a WDT Time-out Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit, clear it, and rewrite the location. The data and address will be cleared, therefore, the EEDATA and EEADR registers will need to be re-initialized.

The Interrupt flag bit EEIF in the PIR1 register is set when the write is complete. This bit must be cleared in software.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the data EEPROM write sequence.

#### REGISTER 8-3: EECON1 — EEPROM CONTROL REGISTER (ADDRESS: 9Ch)

| U-0   | U-0 | U-0 | U-0 | R/W-x | R/W-0 | R/S-0 | R/S-0 |

|-------|-----|-----|-----|-------|-------|-------|-------|

| _     | _   | _   | _   | WRERR | WREN  | WR    | RD    |

| bit 7 |     |     |     |       |       |       | bit 0 |

#### bit 7-4 Unimplemented: Read as '0'

#### bit 3 WRERR: EEPROM Error Flag bit

- 1 = A write operation is prematurely terminated (any MCLR Reset, any WDT Reset during normal operation or BOD detect)

- 0 = The write operation completed

#### bit 2 WREN: EEPROM Write Enable bit

- 1 = Allows write cycles

- 0 = Inhibits write to the data EEPROM

#### bit 1 WR: Write Control bit

- 1 = Initiates a write cycle (The bit is cleared by hardware once write is complete. The WR bit can only be set, not cleared, in software.)

- 0 = Write cycle to the data EEPROM is complete

#### bit 0 RD: Read Control bit

- 1 = Initiates an EEPROM read (Read takes one cycle. RD is cleared in hardware. The RD bit can only be set, not cleared, in software.)

- 0 = Does not initiate an EEPROM read

#### Legend:

S = Bit can only be set

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### 9.3.5 BROWN-OUT DETECT (BOD)

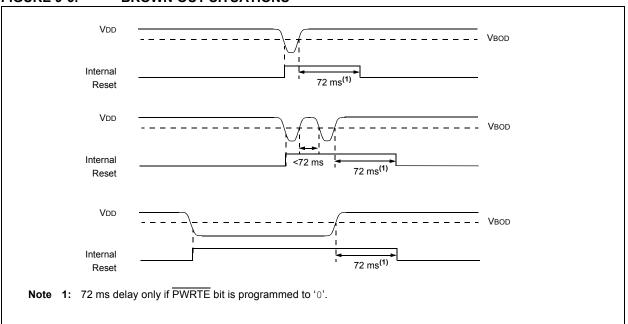

The PIC16F630/676 members have on-chip Brown-out Detect circuitry. A Configuration bit, BODEN, can disable (if clear/programmed) or enable (if set) the Brown-out Detect circuitry. If VDD falls below VBOD for greater than parameter (TBOD) in Table 12-4 (see Section 12.0 "Electrical Specifications"), the Brown-out situation will reset the device. This will occur regardless of VDD slew-rate. A Reset is not guaranteed to occur if VDD falls below VBOD for less than parameter (TBOD).

On any Reset (Power-on, Brown-out Detect, Watchdog, etc.), the chip will remain in Reset until VDD rises above BVDD (see Figure 9-6). The Power-up Timer will now be invoked, if enabled, and will keep the chip in Reset an additional 72 ms.

Note: A Brown-out Detect does not enable the Power-up Timer if the PWRTE bit in the Configuration Word is set.

If VDD drops below BVDD while the Power-up Timer is running, the chip will go back into a Brown-out Detect and the Power-up Timer will be re-initialized. Once VDD rises above BVDD, the Power-up Timer will execute a 72 ms Reset.

#### 9.3.6 TIME-OUT SEQUENCE

On power-up, the time-out sequence is as follows: first, PWRT time-out is invoked after POR has expired. Then, OST is activated. The total time-out will vary based on oscillator configuration and PWRTE bit status. For example, in EC mode with PWRTE bit erased (PWRT disabled), there will be no time-out at all. Figure 9-7, Figure 9-8 and Figure 9-9 depict time-out sequences.

Since the time-outs occur from the POR pulse, if MCLR is kept low long enough, the time-outs will expire. Then bringing MCLR high will begin execution immediately (see Figure 9-8). This is useful for testing purposes or to synchronize more than one PIC16F630/676 device operating in parallel.

Table 9-6 shows the Reset conditions for some special registers, while Table 9-7 shows the Reset conditions for all the registers.

### 9.3.7 POWER CONTROL (PCON) STATUS REGISTER

The power CONTROL/STATUS register, PCON (address 8Eh) has two bits.

Bit 0 is  $\overline{\text{BOD}}$  (Brown-out).  $\overline{\text{BOD}}$  is unknown on Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if  $\overline{\text{BOD}} = 0$ , indicating that a brown-out has occurred. The  $\overline{\text{BOD}}$  Status bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (by setting  $\overline{\text{BODEN}}$  bit = 0 in the Configuration Word).

Bit 1 is  $\overline{\mathsf{POR}}$  (Power-on Reset). It is a '0' on Power-on Reset and unaffected otherwise. The user must write a '1' to this bit following a Power-on Reset. On a subsequent Reset, if  $\overline{\mathsf{POR}}$  is '0', it will indicate that a Power-on Reset must have occurred (i.e., VDD may have gone too low).

#### 9.4 Interrupts

The PIC16F630/676 has 7 sources of interrupt:

- · External Interrupt RA2/INT

- · TMR0 Overflow Interrupt

- PORTA Change Interrupts

- Comparator Interrupt

- A/D Interrupt (PIC16F676 only)

- · TMR1 Overflow Interrupt

- · EEPROM Data Write Interrupt

The Interrupt Control register (INTCON) and Peripheral Interrupt register (PIR) record individual interrupt requests in flag bits. The INTCON register also has individual and Global Interrupt Enable bits.

A Global Interrupt Enable bit, GIE (INTCON<7>) enables (if set) all unmasked interrupts, or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in INTCON register and PIE register. GIE is cleared on Reset.

The return from interrupt instruction, RETFIE, exits interrupt routine, as well as sets the GIE bit, which reenables unmasked interrupts.

The following interrupt flags are contained in the INTCON register:

- · INT pin interrupt

- · PORTA change interrupt

- · TMR0 overflow interrupt

The peripheral interrupt flags are contained in the special register PIR1. The corresponding interrupt enable bit is contained in Special Register PIE1.

The following interrupt flags are contained in the PIR register:

- · EEPROM data write interrupt

- A/D interrupt

- · Comparator interrupt

- Timer1 overflow interrupt

When an interrupt is serviced:

- The GIE is cleared to disable any further interrupt

- · The return address is pushed onto the stack

- · The PC is loaded with 0004h

Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid RA2/INT recursive interrupts.

For external interrupt events, such as the INT pin, or PORTA change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends upon when the interrupt event occurs (see Figure 9-11). The latency is the same for one or two-cycle instructions. Once in the Interrupt Service Routine, the source(s) of the interrupt can be

determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests.

- Note 1: Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit or the GIE bit.

- 2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The interrupts which were ignored are still pending to be serviced when the GIE bit is set again.

**FIGURE 9-10: INTERRUPT LOGIC** IOCA-RA0 -IOCA-RA1 \_ IOCA1 \_ IOCA-RA2 \_ IOCA2 \_ IOCA-RA3 | IOCA-RA4 – IOCA4 – IOCA-RA5 – IOCA5 – TOIF -Wake-up (If in Sleep mode) INTF \_ Interrupt to CPU TMR1IF -TMR1IE -**RAIF** RAIE -**CMIF** CMIE PEIE ADIF -GIE EEIF -Note 1: PIC16F676 only.

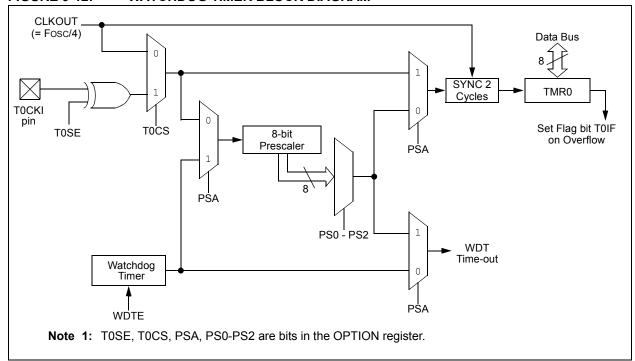

#### FIGURE 9-12: WATCHDOG TIMER BLOCK DIAGRAM

TABLE 9-9: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address | Name         | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOD | Value on all<br>other<br>Resets |

|---------|--------------|-------|--------|-------|-------|-------|-------|-------|-------|----------------------|---------------------------------|

| 81h     | OPTION_REG   | RAPU  | INTEDG | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111            | 1111 1111                       |

| 2007h   | Config. bits | CP    | BODEN  | MCLRE | PWRTE | WDTE  | F0SC2 | F0SC1 | F0SC0 | uuuu uuuu            | uuuu uuuu                       |

**Legend:** u = Unchanged, shaded cells are not used by the Watchdog Timer.

# 11.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit™ 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows® programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit™ 2 enables in-circuit debugging on most PIC® microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

#### 11.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

# 11.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>TM</sup> and dsPICDEM<sup>TM</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, Keeloq® security ICs, CAN, IrDA®, PowerSmart battery management, Seevallation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

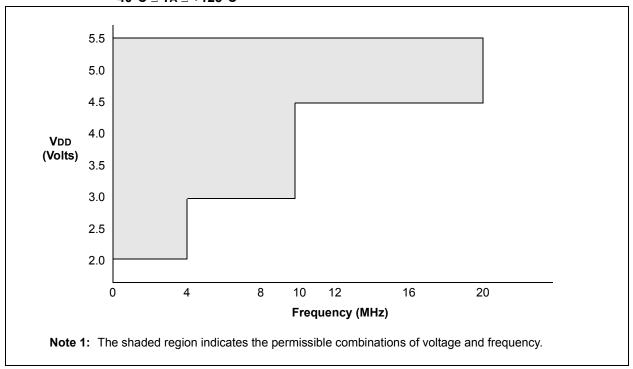

FIGURE 12-1: PIC16F630/676 WITH A/D DISABLED VOLTAGE-FREQUENCY GRAPH,  $-40^{\circ}C \le Ta \le +125^{\circ}C$

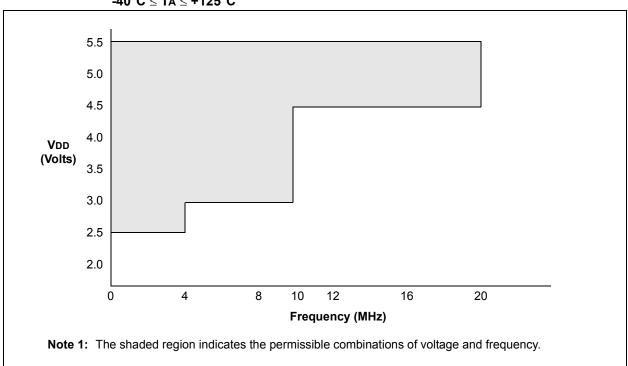

FIGURE 12-2: PIC16F676 WITH A/D ENABLED VOLTAGE-FREQUENCY GRAPH,  $-40^{\circ}C \le T_A \le +125^{\circ}C$

#### 12.8 TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

io

Т

| F      | Frequency                             | Т   | Time     |

|--------|---------------------------------------|-----|----------|

| Lowerd | case letters (pp) and their meanings: |     |          |

| рр     |                                       |     |          |

| СС     | CCP1                                  | osc | OSC1     |

| ck     | CLKOUT                                | rd  | RD       |

| cs     | <del>CS</del>                         | rw  | RD or WR |

| di     | SDI                                   | sc  | SCK      |

| do     | SDO                                   | SS  | SS       |

| dt     | Data in                               | t0  | T0CKI    |

Uppercase letters and their meanings:

I/O port

MCLR

| S |                          |   |                |

|---|--------------------------|---|----------------|

| F | Fall                     | Р | Period         |

| Н | High                     | R | Rise           |

| 1 | Invalid (High-impedance) | V | Valid          |

| L | Low                      | Z | High-impedance |

t1

wr

T1CKI

$\overline{\text{WR}}$

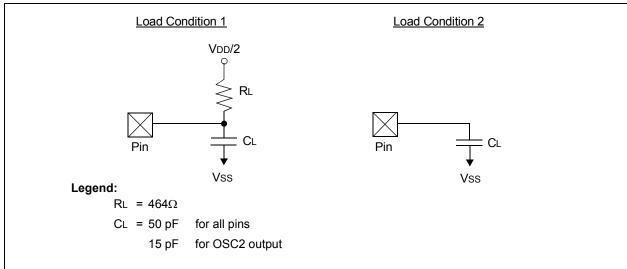

#### FIGURE 12-4: LOAD CONDITIONS

NOTES:

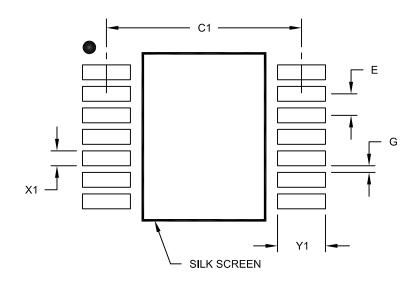

#### 14-Lead Plastic Thin Shrink Small Outline (ST) - 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### RECOMMENDED LAND PATTERN

|                          | Units  | N    | <b>IILLIMETER</b> | S    |

|--------------------------|--------|------|-------------------|------|

| Dimension                | Limits | MIN  | NOM               | MAX  |

| Contact Pitch            | E      |      | 0.65 BSC          |      |

| Contact Pad Spacing      | C1     |      | 5.90              |      |

| Contact Pad Width (X14)  | X1     |      |                   | 0.45 |

| Contact Pad Length (X14) | Y1     |      |                   | 1.45 |

| Distance Between Pads    | G      | 0.20 |                   |      |

#### Notes

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2087A

## APPENDIX A: DATA SHEET REVISION HISTORY

#### **Revision A**

This is a new data sheet.

#### **Revision B**

Added characterization graphs.

Updated specifications.

Added notes to indicate Microchip programmers maintain all calibration bits to factory settings and the PIC16F676 ANSEL register must be initialized to configure pins as digital I/O.

#### **Revision C**

#### **Revision D**

Updated Package Drawings; Replaced PICmicro with PIC:

#### **Revision E (03/2007)**

Replaced Package Drawings (Rev. AM); Replaced Development Support Section.

#### **Revision F (05/2010)**

Replaced Package Drawings (Rev. BD); Replaced Development Support Section.

## APPENDIX B: DEVICE DIFFERENCES

The differences between the PIC16F630/676 devices listed in this data sheet are shown in Table B-1.

#### TABLE B-1: DEVICE DIFFERENCES

| Feature | PIC16F630 | PIC16F676 |

|---------|-----------|-----------|

| A/D     | No        | Yes       |

| INDEX                                       |     | Output                                                 | 42  |

|---------------------------------------------|-----|--------------------------------------------------------|-----|

| A                                           |     | Reference                                              |     |

| A/D                                         | 45  | Response Time                                          |     |

| Acquisition Requirements                    |     | Comparator Specifications                              |     |

| Block Diagram                               |     | Comparator Voltage Reference Specifications            |     |

| Calculating Acquisition Time                |     | Configuration Bits                                     |     |

| Configuration and Operation                 |     | Configuring the Voltage Reference<br>Crystal Operation |     |

| Effects of a Reset                          |     | Customer Change Notification Service                   |     |

| Internal Sampling Switch (Rss) Impedance    |     | Customer Notification Service                          |     |

| Operation During Sleep                      |     | Customer Support                                       |     |

| PIC16F675 Converter Characteristics         | 103 | _                                                      | 120 |

| Source Impedance                            | 49  | D                                                      |     |

| Summary of Registers                        | 50  | Data EEPROM Memory                                     |     |

| Absolute Maximum Ratings                    | 85  | Associated Registers/Bits                              |     |

| AC Characteristics                          |     | Code Protection                                        |     |

| Industrial and Extended                     |     | EEADR Register                                         |     |

| Analog Input Connection Considerations      | 42  | EECONI Register                                        |     |

| Analog-to-Digital Converter. See A/D        |     | EECON2 Register                                        |     |

| Assembler                                   |     | EEDATA Register                                        |     |

| MPASM Assembler                             | 82  | Data Memory Organization  DC Characteristics           | 9   |

| В                                           |     | Extended and Industrial                                | 03  |

| Block Diagram                               |     | Industrial                                             |     |

| TMR0/WDT Prescaler                          | 31  | Debugger                                               |     |

| Block Diagrams                              |     | Development Support                                    |     |

| Analog Input Mode                           | 42  | Device Differences                                     |     |

| Analog Input Model                          | 49  | Device Migrations                                      |     |

| Comparator Output                           |     | Device Overview                                        |     |

| Comparator Voltage Reference                | 43  | E                                                      |     |

| On-Chip Reset Circuit                       | 59  |                                                        |     |

| RA0 and RA1 Pins                            | 24  | EEPROM Data Memory                                     | 50  |

| RA2                                         | 25  | Reading                                                |     |

| RA3                                         |     | Spurious Write                                         |     |

| RA4                                         |     | Write Verify                                           |     |

| RA5                                         |     | Writing                                                |     |

| RC Oscillator Mode                          |     | Electrical Specifications                              |     |

| RC0/RC1/RC2/RC3 Pins                        |     |                                                        | 3   |

| RC4 AND RC5 Pins                            |     | F                                                      |     |

| Timer1                                      |     | Firmware Instructions                                  | 73  |

| Watchdog Timer                              | 69  | G                                                      |     |

| Brown-out Associated Registers              | 62  | General Purpose Register File                          | 9   |

| Brown-out Detect (BOD)                      |     | I                                                      |     |

| Brown-out Detect Timing and Characteristics |     | I                                                      |     |

| C                                           |     | ID Locations                                           |     |

| C                                           |     | In-Circuit Serial Programming                          |     |

| C Compilers                                 |     | Indirect Addressing, INDF and FSR Registers            |     |

| MPLAB C18                                   |     | Instruction FormatInstruction Set                      |     |

| Calibrated Internal RC Frequencies          |     | ADDLW                                                  |     |

| CLKOUT                                      | 58  | ADDWF                                                  |     |

| Code Examples                               | 00  | ANDLW                                                  |     |

| Changing Prescaler                          |     | ANDWF                                                  |     |

| Data EEPROM Read<br>Data EEPROM Write       |     | BCF                                                    |     |

|                                             |     | BSF                                                    |     |

| Initializing PORTAInitializing PORTC        |     | BTFSC                                                  |     |

| Saving STATUS and W Registers in RAM        |     | BTFSS                                                  |     |

| Write Verify                                |     | CALL                                                   | 76  |

| Code Protection                             |     | CLRF                                                   |     |

| Comparator                                  |     | CLRW                                                   | 76  |

| Associated Registers                        |     | CLRWDT                                                 | 76  |

| Configuration                               |     | COMF                                                   | 76  |

| Effects of a Reset                          |     | DECF                                                   | 76  |

| I/O Operating Modes                         |     | DECFSZ                                                 | 77  |

| Interrupts                                  |     | GOTO                                                   | 77  |

| Operation                                   |     | INCF                                                   |     |

| Operation During Sleep                      |     | INCFSZ                                                 | 77  |

| IORLW                                                     | 77       | Power-on Reset (POR)                         | 60  |

|-----------------------------------------------------------|----------|----------------------------------------------|-----|

| IORWF                                                     | 77       | Power-up Timer (PWRT)                        | 60  |

| MOVF                                                      | 78       | Prescaler                                    | 33  |

| MOVLW                                                     | 78       | Switching Prescaler Assignment               |     |

| MOVWF                                                     | 78       | Program Memory Organization                  | 9   |

| NOP                                                       |          | Programming, Device Instructions             | 73  |

| RETFIE                                                    | 78       | R                                            |     |

| RETLW                                                     | 78       | RC Oscillator                                | 58  |

| RETURN                                                    | 79       | Reader Response                              |     |

| RLF                                                       | 79       | READ-MODIFY-WRITE OPERATIONS                 |     |

| RRF                                                       | 79       | Registers                                    | / C |

| SLEEP                                                     |          | ADCON0 (A/D Control)                         | 47  |

| SUBLW                                                     | 79       | ADCON1                                       |     |

| SUBWF                                                     |          | CMCON (Comparator Control)                   |     |

| SWAPF                                                     |          | CONFIG (Configuration Word)                  |     |

| XORLW                                                     |          | EEADR (EEPROM Address)                       |     |

| XORWF                                                     |          | EECON1 (EEPROM Control)                      |     |

| Summary Table                                             |          | EEDAT (EEPROM Data)                          |     |

| Internal 4 MHz Oscillator                                 |          | INTCON (Interrupt Control)                   |     |

| Internal Sampling Switch (Rss) Impedance                  |          | IOCA (Interrupt-on-Change PORTA)             |     |

| Internet Address                                          |          | Maps                                         |     |

| Interrupts                                                |          | PIC16F630                                    | 10  |

| A/D Converter                                             |          | PIC16F676                                    |     |

| Comparator                                                |          | OPTION_REG (Option)                          |     |

| Context Saving                                            |          | OSCCAL (Oscillator Calibration)              |     |

| PORTA                                                     |          | PCON (Power Control)                         |     |

| RA2/INT                                                   |          | PIE1 (Peripheral Interrupt Enable 1)         |     |

| Summary of Registers                                      |          | PIR1 (Peripheral Interrupt 1)                |     |

| TMR0                                                      | 67       | PORTC                                        |     |

| M                                                         |          | STATUS                                       | 13  |

| MCLR                                                      | 60       | T1CON (Timer1 Control)                       |     |

| Memory Organization                                       |          | TRISC                                        |     |

| Data EEPROM Memory                                        | 51       | VRCON (Voltage Reference Control)            | 44  |

| Microchip Internet Web Site                               |          | WPUA (Weak Pull-up PORTA)                    |     |

| Migrating from other PICmicro Devices                     |          | RESET                                        |     |

| MPLAB ASM30 Assembler, Linker, Librarian                  | 82       | Revision History                             | 123 |

| MPLAB Integrated Development Environment Softwa           | are 81   | S                                            |     |

| MPLAB PM3 Device Programmer                               | 84       | Software Simulator (MPLAB SIM)               | Q:  |

| MPLAB REAL ICE In-Circuit Emulator System                 | 83       | Special Features of the CPU                  |     |

| MPLINK Object Linker/MPLIB Object Librarian               | 82       | Special Function Registers                   |     |

| 0                                                         |          | <b>T</b>                                     |     |

| OPCODE Field Descriptions                                 | 73       | ı                                            |     |

| Oscillator Configurations                                 |          | Time-out Sequence                            |     |

| Oscillator Start-up Timer (OST)                           |          | Timer0                                       |     |

| B                                                         |          | Associated Registers                         |     |

| <b>r</b><br>                                              |          | External Clock                               |     |

| Packaging                                                 |          | Interrupt                                    |     |

| Details                                                   |          | Operation                                    |     |

| Marking                                                   |          | T0CKI                                        | 32  |

| PCL and PCLATH                                            |          | Timer1                                       | 0-  |

| Computed GOTO                                             |          | Associated Registers                         |     |

| Stack                                                     | 19       | Asynchronous Counter Mode                    | 31  |

| Pinout Descriptions                                       | 0        | Reading and Writing                          |     |

| PIC16F630                                                 |          | Interrupt                                    |     |

| PIC16F676                                                 | 8        | Modes of Operations                          |     |

| PORTA                                                     | 04       | Operation During SLEEP                       |     |

| Additional Pin Functions                                  |          | Oscillator                                   |     |

| Interrupt-on-Change                                       |          | Prescaler                                    |     |

| Weak Pull-up                                              |          | Timer1 Module with Gate Control              | 34  |

| Associated Registers                                      |          | Timing Diagrams                              | 01  |

| Pin Descriptions and Diagrams                             |          | CLKOUT and I/O                               |     |

| PORTA and TRISIO Registers                                |          | External Clock                               |     |

| PORTCAssociated Registers                                 |          | INT Pin Interrupt                            |     |

| Associated Registers Power Control/Status Register (PCON) |          | PIC16F675 A/D Conversion (Normal Mode)       |     |

| Power Control/Status Register (PCON)                      | 01<br>70 | PIC16F675 A/D Conversion Timing (Sleep Mode) | 100 |

#### PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.           | <u>x /xx xxx</u>                                                      | Exa | mples:                                                                       |

|--------------------|-----------------------------------------------------------------------|-----|------------------------------------------------------------------------------|

| Device Te          | emperature Package Pattern<br>Range                                   | a)  | PIC16F630 – E/P 301 = Extended Temp., PDIP package, 20 MHz, QTP pattern #301 |

|                    | ······································                                | b)  | PIC16F676 - I/SL = Industrial Temp., SOIC                                    |

| Device:            | : Standard VDD range<br>T: (Tape and Reel)                            |     | package, 20 MHz                                                              |

| Temperature Range: | I = -40°C to +85°C<br>E = -40°C to +125°C                             |     |                                                                              |

| Package:           | P = PDIP<br>SL = SOIC (Gull wing, 3.90 mm body)<br>ST = TSSOP(4.4 mm) |     |                                                                              |

| Pattern:           | 3-Digit Pattern Code for QTP (blank otherwise)                        |     |                                                                              |

<sup>\*</sup> JW Devices are UV erasable and can be programmed to any device configuration. JW Devices meet the electrical requirement of each oscillator type.