# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 12                                                                       |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 64 × 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 16-VQFN Exposed Pad                                                      |

| Supplier Device Package    | 16-QFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f630-i-ml |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

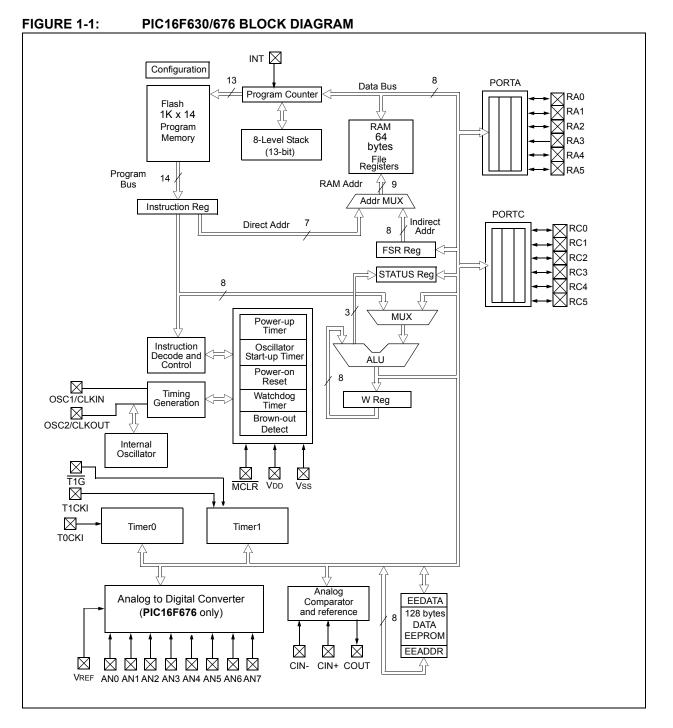

# 1.0 DEVICE OVERVIEW

This document contains device specific information for the PIC16F630/676. Additional information may be found in the PIC<sup>®</sup> Mid-Range Reference Manual (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip web site. The Reference Manual should be considered a complementary document to this Data Sheet and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

The PIC16F630 and PIC16F676 devices are covered by this Data Sheet. They are identical, except the PIC16F676 has a 10-bit A/D converter. They come in 14-pin PDIP, SOIC and TSSOP packages. Figure 1-1 shows a block diagram of the PIC16F630/676 devices. Table 1-1 shows the pinout description.

# 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral functions for controlling the desired operation of the device (see Table 2-1). These registers are static RAM.

The special registers can be classified into two sets: core and peripheral. The Special Function Registers associated with the "core" are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

#### FIGURE 2-2: DATA MEMORY MAP OF THE PIC16F630/676

|                                                                                  | THEF            | PIC16F630/676                 |                |

|----------------------------------------------------------------------------------|-----------------|-------------------------------|----------------|

|                                                                                  | File<br>Address | A                             | File<br>ddress |

| Indirect addr. <sup>(1)</sup>                                                    | 00h             | Indirect addr. <sup>(1)</sup> | 80h            |

| TMR0                                                                             | 01h             | OPTION_REG                    | 81h            |

| PCL                                                                              | 02h             | PCL                           | 82h            |

| STATUS                                                                           | 03h             | STATUS                        | 83h            |

| FSR                                                                              | 04h             | FSR                           | 84h            |

| PORTA                                                                            | 05h             | TRISA                         | 85h            |

|                                                                                  | 06h             | -                             | 86h            |

| PORTC                                                                            | 07h             | TRISC                         | 87h            |

|                                                                                  | 08h             | -                             | 88h            |

|                                                                                  | 09h             |                               | 89h            |

| PCLATH                                                                           | 0Ah             | PCLATH                        | 8Ah            |

| INTCON                                                                           | 0Bh             | INTCON                        | 8Bh            |

| PIR1                                                                             | 0Ch             | PIE1                          | 8Ch            |

|                                                                                  | 0Dh             |                               | 8Dh            |

| TMR1L                                                                            | 0Eh             | PCON                          | 8Eh            |

| TMR1H                                                                            | 0Fh             |                               | 8Fh            |

| T1CON                                                                            | 10h             | OSCCAL                        | 90h            |

| TICON                                                                            | 11h             | ANSEL <sup>(2)</sup>          | 91h            |

|                                                                                  | 12h             | THOLE                         | 92h            |

|                                                                                  | 13h             | -                             | 93h            |

|                                                                                  | 14h             |                               | 94h            |

|                                                                                  | 15h             | WPUA                          | 95h            |

|                                                                                  | 16h             | IOCA                          | 96h            |

|                                                                                  | 17h             | IOCA                          | 97h            |

|                                                                                  | 18h             |                               | 98h            |

| CMCON                                                                            | 19h             | VRCON                         | 99h            |

| CINCON                                                                           | 1Ah             | EEDAT                         | 9Ah            |

|                                                                                  | 1Bh             | EEADR                         | 9Bh            |

|                                                                                  | 1Ch             | EECON1                        | 9Ch            |

|                                                                                  | 1Dh             | EECON2 <sup>(1)</sup>         | 9Dh            |

| ADRESH <sup>(2)</sup>                                                            | 1Eh             | ADRESL <sup>(2)</sup>         | 9Eh            |

| ADCON0 <sup>(2)</sup>                                                            | 1Fh             | ADCON1 <sup>(2)</sup>         | 9Fh            |

| ADCONU                                                                           | 20h             | ADCONT                        | A0h            |

| General<br>Purpose<br>Registers<br>64 Bytes                                      | 2011            | accesses<br>20h-5Fh           |                |

|                                                                                  | 5Fh             |                               | DFh            |

|                                                                                  | 60h             |                               | E0h            |

|                                                                                  | 001             |                               | Lon            |

|                                                                                  |                 |                               |                |

|                                                                                  |                 |                               |                |

|                                                                                  | 7Fh             | _                             | FFh            |

| Bank 0                                                                           |                 | Bank 1                        |                |

| <ul><li>Unimplemente</li><li>1: Not a physical</li><li>2: PIC16F676 on</li></ul> | register.       | mory locations, rea           | d as '0'.      |

| TABLE 2-1: | PIC16F630/676 SPECIAL | REGISTERS SUMMARY BANK 0 |

|------------|-----------------------|--------------------------|

|            |                       |                          |

| Addr   | Name                  | Bit 7              | Bit 6                 | Bit 5             | Bit 4          | Bit 3            | Bit 2          | Bit 1         | Bit 0   | Value on<br>POR,<br>BOD | Page  |

|--------|-----------------------|--------------------|-----------------------|-------------------|----------------|------------------|----------------|---------------|---------|-------------------------|-------|

| Bank 0 |                       |                    |                       |                   |                |                  |                |               |         |                         |       |

| 00h    | INDF                  | Addressing         | this location         | uses content      | ts of FSR to a | address data     | memory (not    | a physical re | gister) | XXXX XXXX               | 20,63 |

| 01h    | TMR0                  | Timer0 Mod         | dule's Registe        | er                |                |                  |                |               |         | XXXX XXXX               | 31    |

| 02h    | PCL                   | Program Co         | ounter's (PC)         | ) Least Signifi   | icant Byte     |                  |                |               |         | 0000 0000               | 19    |

| 03h    | STATUS                | IRP <sup>(2)</sup> | RP1 <sup>(2)</sup>    | RP0               | TO             | PD               | Z              | DC            | С       | 0001 1xxx               | 13    |

| 04h    | FSR                   | Indirect dat       | a memory Ac           | dress Pointe      | r              |                  |                |               |         | xxxx xxxx               | 20    |

| 05h    | PORTA                 |                    | I/O Control Registers |                   |                |                  |                |               |         | xx xxxx                 | 21    |

| 06h    | _                     | Unimpleme          | nted                  |                   |                |                  |                |               |         | -                       | _     |

| 07h    | PORTC                 | _                  | _                     | I/O Control       | Registers      |                  |                |               |         | xx xxxx                 | 28    |

| 08h    | _                     | Unimpleme          | Unimplemented         |                   |                |                  |                |               | _       | -                       |       |

| 09h    | _                     | Unimplemented      |                       |                   |                |                  | -              | _             |         |                         |       |

| 0Ah    | PCLATH                | _                  | _                     | l —               | Write buffer   | for upper 5 b    | oits of progra | m counter     |         | 0 0000                  | 19    |

| 0Bh    | INTCON                | GIE                | PEIE                  | T0IE              | INTE           | RAIE             | T0IF           | INTF          | RAIF    | 0000 0000               | 15    |

| 0Ch    | PIR1                  | EEIF               | ADIF                  | _                 | _              | CMIF             | _              | —             | TMR1IF  | 00 00                   | 17    |

| 0Dh    | —                     | Unimpleme          | nted                  | ·                 | •              |                  | •              |               |         | -                       | -     |

| 0Eh    | TMR1L                 | Holding reg        | ister for the l       | _east Signific    | ant Byte of th | ie 16-bit TMR    | 1              |               |         | XXXX XXXX               | 34    |

| 0Fh    | TMR1H                 | Holding reg        | ister for the I       | Most Significa    | ant Byte of th | e 16-bit TMR     | 1              |               |         | XXXX XXXX               | 34    |

| 10h    | T1CON                 | _                  | T1GE                  | T1CKPS1           | T1CKPS0        | T10SCEN          | T1SYNC         | TMR1CS        | TMR10N  | -000 0000               | 36    |

| 11h    | —                     | Unimpleme          | nted                  |                   |                |                  |                |               |         | _                       | -     |

| 12h    | —                     | Unimpleme          | nted                  |                   |                |                  |                |               |         | -                       | -     |

| 13h    | —                     | Unimpleme          | nted                  |                   |                |                  |                |               |         | -                       | -     |

| 14h    | —                     | Unimpleme          | nted                  |                   |                |                  |                |               |         | -                       | -     |

| 15h    | —                     | Unimpleme          | nted                  |                   |                |                  |                |               |         | _                       | -     |

| 16h    | _                     | Unimpleme          | nted                  |                   |                |                  |                |               |         | _                       | -     |

| 17h    | _                     | Unimpleme          |                       |                   |                |                  |                |               |         | _                       | -     |

| 18h    |                       | Unimpleme          |                       |                   |                |                  | •              |               |         | -                       | -     |

| 19h    | CMCON                 | —                  | COUT                  | —                 | CINV           | CIS              | CM2            | CM1           | CM0     | -0-0 0000               | 39    |

| 1Ah    | —                     | Unimpleme          |                       |                   |                |                  |                |               |         | -                       | -     |

| 1Bh    | —                     | Unimpleme          |                       |                   |                |                  |                |               |         | -                       | -     |

| 1Ch    | -                     | Unimpleme          |                       |                   |                |                  |                |               |         | -                       | -     |

| 1Dh    |                       | Unimpleme          |                       |                   |                |                  |                |               |         | -                       | -     |

| 1Eh    | ADRESH <sup>(3)</sup> | -                  | 1                     | f the left shifte | ed A/D result  | or 2 bits of rig | ght shifted re | 1             |         | XXXX XXXX               | 46    |

| 1Fh    | ADCON0 <sup>(3)</sup> | ADFM               | VCFG                  | —                 | CHS2           | CHS1             | CHS0           | GO/DONE       | ADON    | 00-0 0000               | 47,63 |

– = Unimplemented locations read <u>as '0'</u>, <u>u</u> = unchanged, <u>x</u> = unknown, <u>q</u> = value depends on condition shaded = unimplemented

Other (non Power-up) Resets include MCLR Reset, Brown-out Detect and Watchdog Timer Reset during normal operation.

IRP and RP1 bits are reserved, always maintain these bits clear.

PIC16F676 only. Legend: Note 1:

2: 3:

| Addr                        | Name                  | Bit 7                         | Bit 6              | Bit 5            | Bit 4           | Bit 3                        | Bit 2                         | Bit 1                        | Bit 0                         | Value on<br>POR,<br>BOD     | Page  |

|-----------------------------|-----------------------|-------------------------------|--------------------|------------------|-----------------|------------------------------|-------------------------------|------------------------------|-------------------------------|-----------------------------|-------|

| Bank 1                      |                       |                               | •                  |                  | •               | •                            | •                             |                              | •                             |                             |       |

| 80h                         | INDF                  | Addressing                    | this location      | uses content     | ts of FSR to a  | address data                 | memory (not                   | a physical re                | egister)                      | xxxx xxxx                   | 20,63 |

| 81h                         | OPTION_REG            | RAPU                          | INTEDG             | TOCS             | T0SE            | PSA                          | PS2                           | PS1                          | PS0                           | 1111 1111                   | 14,32 |

| 82h                         | PCL                   | Program Co                    | ounter's (PC)      | Least Signif     | icant Byte      |                              |                               | 1                            |                               | 0000 0000                   | 19    |

| 83h                         | STATUS                | IRP <sup>(2)</sup>            | RP1 <sup>(2)</sup> | RP0              | TO              | PD                           | Z                             | DC                           | С                             | 0001 1xxx                   | 13    |

| 84h                         | FSR                   |                               | a memory Ad        | -                |                 |                              |                               | 50                           | , v                           | xxxx xxxx                   | 20    |

| 85h                         | TRISA                 | _                             | _                  | TRISA5           | TRISA4          | TRISA3                       | TRISA2                        | TRISA1                       | TRISA0                        | 11 1111                     | 21    |

| 86h                         | _                     | Unimpleme                     | nted               |                  |                 |                              | •                             | •                            |                               | _                           | _     |

| 87h                         | TRISC                 |                               | _                  | TRISC5           | TRISC4          | TRISC3                       | TRISC2                        | TRISC1                       | TRISC0                        | 11 1111                     | _     |

| 88h                         | _                     | Unimpleme                     | nted               | •                |                 | •                            | •                             | •                            |                               | -                           | _     |

| 89h                         | _                     | Unimpleme                     | nted               |                  |                 |                              |                               |                              |                               | -                           | -     |

| 8Ah                         | PCLATH                | _                             | _                  | _                | Write buffer    | for upper 5 l                | oits of progra                | m counter                    |                               | 0 0000                      | 19    |

| 8Bh                         | INTCON                | GIE                           | PEIE               | T0IE             | INTE            | RAIE                         | T0IF                          | INTF                         | RAIF                          | 0000 0000                   | 15    |

| 8Ch                         | PIE1                  | EEIE                          | ADIE               |                  | —               | CMIE                         | —                             |                              | TMR1IE                        | 0000                        | 16    |

| 8Dh                         | —                     | Unimpleme                     | nted               |                  |                 |                              |                               |                              |                               | -                           | _     |

| 8Eh                         | PCON                  | _                             | _                  |                  | _               | _                            | _                             | POR                          | BOD                           | dd                          | 18    |

| 8Fh                         | _                     |                               | •                  |                  | •               | •                            | •                             | •                            |                               | -                           |       |

| 90h                         | OSCCAL                | CAL5                          | CAL4               | CAL3             | CAL2            | CAL1                         | CAL0                          |                              | _                             | 1000 00                     | 18    |

| 91h                         | ANSEL <sup>(3)</sup>  | ANS7                          | ANS6               | ANS5             | ANS4            | ANS3                         | ANS2                          | ANS1                         | ANS0                          | 1111 1111                   | 48    |

| 92h                         | —                     | Unimpleme                     | nted               | •                |                 |                              | •                             | •                            |                               | -                           | -     |

| 93h                         | _                     | Unimpleme                     | nted               |                  |                 |                              |                               |                              |                               | _                           | l –   |

| 94h                         | _                     | Unimpleme                     | nted               |                  |                 |                              |                               |                              |                               | -                           | _     |

| 95h                         | WPUA                  | _                             | _                  | WPUA5            | WPUA4           | _                            | WPUA2                         | WPUA1                        | WPUA0                         | 11 -111                     | 22    |

| 96h                         | IOCA                  | _                             | _                  | IOCA5            | IOCA4           | IOCA3                        | IOCA2                         | IOCA1                        | IOCA0                         | 00 0000                     | 23    |

| 97h                         | _                     | Unimpleme                     | nted               |                  |                 |                              | •                             | •                            |                               | _                           | -     |

| 98h                         | _                     | Unimpleme                     | nted               |                  |                 |                              |                               |                              |                               | _                           | l –   |

| 99h                         | VRCON                 | VREN                          | _                  | VRR              | _               | VR3                          | VR2                           | VR1                          | VR0                           | 0-0- 0000                   | 44    |

| 9Ah                         | EEDAT                 | EEPROM d                      | lata register      |                  |                 |                              |                               |                              |                               | 0000 0000                   | 51    |

| 9Bh                         | EEADR                 | _                             | EEPROM a           | ddress regis     | ter             |                              |                               |                              |                               | 0000 0000                   | 51    |

| 9Ch                         | EECON1                | _                             | _                  | _                | _               | WRERR                        | WREN                          | WR                           | RD                            | x000                        | 52    |

| 9Dh                         | EECON2                | EEPROM c                      | ontrol registe     | r 2 (not a ph    | ysical registe  | r)                           |                               |                              |                               |                             | 51    |

| 9Eh                         | ADRESL <sup>(3)</sup> | Least Signi                   | ficant 2 bits o    | f the left shift | ted result or 8 | B bits of the ri             | ght shifted re                | sult                         |                               | xxxx xxxx                   | 46    |

| 9Fh                         | ADCON1 <sup>(3)</sup> | _                             | ADCS2              | ADCS1            | ADCS0           | —                            | _                             |                              | —                             | -000                        | 47,63 |

| Legend:<br>Note 1<br>2<br>3 | : Other (non Po       | ower-up) Res<br>bits are rese | sets include N     | ICLR Reset,      | Brown-out D     | = unknown, o<br>etect and Wa | g = value dep<br>atchdog Time | ends on con<br>r Reset durir | dition, shade<br>ng normal op | ed = unimplemer<br>eration. | ited  |

#### **TABLE 2-2:** PIC16F630/676 SPECIAL FUNCTION REGISTERS SUMMARY BANK 1

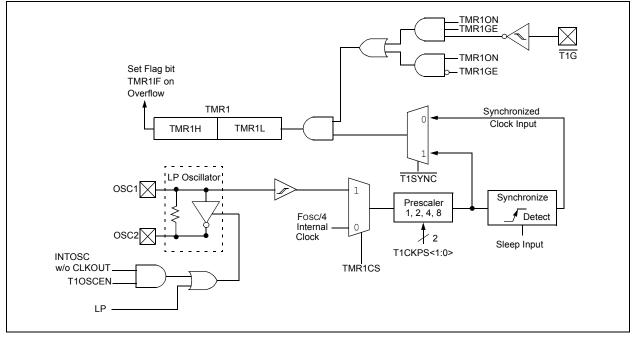

# 5.0 TIMER1 MODULE WITH GATE CONTROL

The PIC16F630/676 devices have a 16-bit timer. Figure 5-1 shows the basic block diagram of the Timer1 module. Timer1 has the following features:

- 16-bit timer/counter (TMR1H:TMR1L)

- · Readable and writable

- Internal or external clock selection

- Synchronous or asynchronous operation

- Interrupt on overflow from FFFFh to 0000h

- Wake-up upon overflow (Asynchronous mode)

- Optional external enable input  $(\overline{T1G})$

- · Optional LP oscillator

#### FIGURE 5-1: TIMER1 BLOCK DIAGRAM

The Timer1 Control register (T1CON), shown in Register 5-1, is used to enable/disable Timer1 and select the various features of the Timer1 module.

Note: Additional information on timer modules is available in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

### 5.4 Timer1 Operation in Asynchronous Counter Mode

If control bit  $\overline{T1SYNC}$  (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 5.4.1).

Note: The ANSEL (91h) and CMCON (19h) registers must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0'. The ANSEL register is defined for the PIC16F676.

# 5.4.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L, while the timer is running from an external asynchronous clock, will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Examples 12-2 and 12-3 in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023) show how to read and write Timer1 when it is running in Asynchronous mode.

# 5.5 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins OSC1 (input) and OSC2 (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator rated up to 32 kHz. It will continue to run during Sleep. It is primarily intended for a 32 kHz crystal. Table 9-2 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is shared with the system LP oscillator. Thus, Timer1 can use this mode only when the system clock is derived from the internal oscillator. As with the system LP oscillator, the user must provide a software time delay to ensure proper oscillator start-up.

TRISA5 and TRISA4 bits are set when the Timer1 oscillator is enabled. RA5 and RA4 read as '0' and TRISA5 and TRISA4 bits read as '1'.

Note: The oscillator requires a start-up and stabilization time before use. Thus, T1OSCEN should be set and a suitable delay observed prior to enabling Timer1.

# 5.6 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To setup the timer to wake the device:

- Timer1 must be on (T1CON<0>)

- TMR1IE bit (PIE1<0>) must be set

- PEIE bit (INTCON<6>) must be set

The device will wake-up on an overflow. If the GIE bit (INTCON<7>) is set, the device will wake-up and jump to the Interrupt Service Routine on an overflow.

| Address | Name   | Bit 7   | Bit 6                                                                      | Bit 5        | Bit 4       | Bit 3       | Bit 2     | Bit 1      | Bit 0  | Value<br>POR, |      |      | e on<br>other<br>sets |

|---------|--------|---------|----------------------------------------------------------------------------|--------------|-------------|-------------|-----------|------------|--------|---------------|------|------|-----------------------|

| 0Bh/8Bh | INTCON | GIE     | PEIE                                                                       | T0IE         | INTE        | RAIE        | T0IF      | INTF       | RAIF   | 0000          | 0000 | 0000 | 000u                  |

| 0Ch     | PIR1   | EEIF    | ADIF                                                                       |              | _           | CMIF        | —         | -          | TMR1IF | 00            | 00   | 00   | 00                    |

| 0Eh     | TMR1L  | Holding | g Register f                                                               | or the Least | Significant | Byte of the | 16-bit TM | R1 Registe | r      | XXXX          | XXXX | uuuu | uuuu                  |

| 0Fh     | TMR1H  | Holding | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register |              |             |             |           |            |        | XXXX          | XXXX | uuuu | uuuu                  |

| 10h     | T1CON  | _       | TMR1GE                                                                     | T1CKPS1      | T1CKPS0     | T10SCEN     | T1SYNC    | TMR1CS     | TMR10N | -000          | 0000 | -uuu | uuuu                  |

| 8Ch     | PIE1   | EEIE    | ADIE                                                                       | _            | _           | CMIE        | _         | _          | TMR1IE | 00            | 00   | 00   | 00                    |

TABLE 5-1:

REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

NOTES:

#### 6.0 **COMPARATOR MODULE**

The PIC16F630/676 devices have one analog comparator. The inputs to the comparator are multiplexed with the RA0 and RA1 pins. There is an on-chip Comparator Voltage Reference that can also be applied to an input of the comparator. In addition, RA2 can be configured as the comparator output. The Comparator Control Register (CMCON), shown in Register 6-1, contains the bits to control the comparator.

#### **REGISTER 6-1:** CMCON — COMPARATOR CONTROL REGISTER (ADDRESS: 19h)

|         | U-0                          | R-0                                      | U-0                     | R/W-0        | R/W-0     | R/W-0       | R/W-0       | R/W-0     |  |  |  |

|---------|------------------------------|------------------------------------------|-------------------------|--------------|-----------|-------------|-------------|-----------|--|--|--|

|         | —                            | COUT                                     | _                       | CINV         | CIS       | CM2         | CM1         | CM0       |  |  |  |

|         | bit 7                        |                                          |                         |              |           |             |             | bit 0     |  |  |  |

|         |                              |                                          |                         |              |           |             |             |           |  |  |  |

| bit 7   | Unimplem                     | ented: Rea                               | <b>d as</b> '0'         |              |           |             |             |           |  |  |  |

| bit 6   | COUT: Con                    | <b>COUT</b> : Comparator Output bit      |                         |              |           |             |             |           |  |  |  |

|         | When CIN\                    |                                          |                         |              |           |             |             |           |  |  |  |

|         | 1 = VIN+ > '<br>0 = VIN+ < ' |                                          |                         |              |           |             |             |           |  |  |  |

|         |                              |                                          |                         |              |           |             |             |           |  |  |  |

|         |                              | <u>When CINV = 1:</u><br>1 = VIN+ < VIN- |                         |              |           |             |             |           |  |  |  |

|         | 0 = VIN+ > VIN-              |                                          |                         |              |           |             |             |           |  |  |  |

| bit 5   | Unimplem                     | ented: Rea                               | <b>d as</b> '0'         |              |           |             |             |           |  |  |  |

| bit 4   |                              |                                          | put Inversio            | n bit        |           |             |             |           |  |  |  |

|         | 1 = Output                   |                                          | ı                       |              |           |             |             |           |  |  |  |

| 1:10    | 0 = Output                   |                                          |                         |              |           |             |             |           |  |  |  |

| bit 3   | CIS: Compa<br>When CM2       |                                          |                         |              |           |             |             |           |  |  |  |

|         | 1 = VIN- COI                 |                                          |                         |              |           |             |             |           |  |  |  |

|         | 0 = VIN- coi                 | nnects to C                              | IN-                     |              |           |             |             |           |  |  |  |

| bit 2-0 | CM2:CM0:                     |                                          |                         |              |           |             |             |           |  |  |  |

|         | Figure 6-2                   | shows the C                              | Comparator              | modes and (  | CM2:CM0 b | it settings |             |           |  |  |  |

|         |                              |                                          |                         |              |           |             |             |           |  |  |  |

|         | Legend:                      |                                          |                         |              |           |             |             |           |  |  |  |

|         |                              | hla hit                                  | $\lambda A = \lambda A$ | /ritable bit |           | anlamantad  | hit road on | <u>o'</u> |  |  |  |

| Legenu.          |                     |                      |                    |

|------------------|---------------------|----------------------|--------------------|

| R = Readable bi  | t W = Writable bit  | U = Unimplemente     | d bit, read as '0' |

| - n = Value at P | OR '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

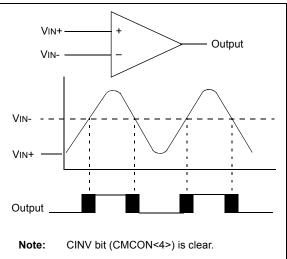

# 6.1 Comparator Operation

A single comparator is shown in Figure 6-1, along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 6-1 represent the uncertainty due to input offsets and response time.

| Note: | To use  | CIN+ and   | CIN-    | pins  | as ana   | alog  |

|-------|---------|------------|---------|-------|----------|-------|

|       | inputs, | the appro  | opriate | bits  | must     | be    |

|       | program | med in the | CMCO    | N (19 | h) regis | ster. |

The polarity of the comparator output can be inverted by setting the CINV bit (CMCON<4>). Clearing CINV results in a non-inverted output. A complete table showing the output state versus input conditions and the polarity bit is shown in Table 6-1.

#### TABLE 6-1: OUTPUT STATE VS. INPUT CONDITIONS

| Input Conditions | CINV | COUT |

|------------------|------|------|

| VIN- > VIN+      | 0    | 0    |

| VIN- < VIN+      | 0    | 1    |

| VIN- > VIN+      | 1    | 1    |

| VIN- < VIN+      | 1    | 0    |

#### SINGLE COMPARATOR

# 8.0 DATA EEPROM MEMORY

The EEPROM data memory is readable and writable during normal operation (full VDD range). This memory is not directly mapped in the register file space. Instead, it is indirectly addressed through the Special Function Registers. There are four SFRs used to read and write this memory:

- EECON1

- EECON2 (not a physically implemented register)

- EEDATA

- EEADR

EEDATA holds the 8-bit data for read/write, and EEADR holds the address of the EEPROM location being accessed. PIC16F630/676 devices have 128 bytes of data EEPROM with an address range from 0h to 7Fh. The EEPROM data memory allows byte read and write. A byte write automatically erases the location and writes the new data (erase before write). The EEPROM data memory is rated for high erase/write cycles. The write time is controlled by an on-chip timer. The write time will vary with voltage and temperature as well as from chip to chip. Please refer to AC Specifications for exact limits.

When the data memory is code-protected, the CPU may continue to read and write the data EEPROM memory. The device programmer can no longer access this memory.

Additional information on the data EEPROM is available in the  ${\rm PIC}^{\circledast}$  Mid-Range Reference Manual, (DS33023).

#### REGISTER 8-1: EEDAT — EEPROM DATA REGISTER (ADDRESS: 9Ah)

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| EEDAT7 | EEDAT6 | EEDAT5 | EEDAT4 | EEDAT3 | EEDAT2 | EEDAT1 | EEDAT0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

#### bit 7-0 **EEDATn**: Byte value to write to or read from data EEPROM

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### **REGISTER 8-2: EEADR — EEPROM ADDRESS REGISTER (ADDRESS: 9Bh)**

| U-0   | R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       | EADR6 | EADR5 | EADR4 | EADR3 | EADR2 | EADR1 | EADR0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

bit 7 Unimplemented: Should be set to '0'

bit 6-0 **EEADR**: Specifies one of 128 locations for EEPROM Read/Write Operation

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### 9.2 Oscillator Configurations

#### 9.2.1 OSCILLATOR TYPES

The PIC16F630/676 can be operated in eight different Oscillator Option modes. The user can program three Configuration bits (FOSC2 through FOSC0) to select one of these eight modes:

- LP Low-Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC External Resistor/Capacitor (2 modes)

- · INTOSC Internal Oscillator (2 modes)

- EC External Clock In

| Note: | Additional information on oscillator config-<br>urations is available in the PIC <sup>®</sup> Mid-Range |

|-------|---------------------------------------------------------------------------------------------------------|

|       | Reference Manual, (DS33023).                                                                            |

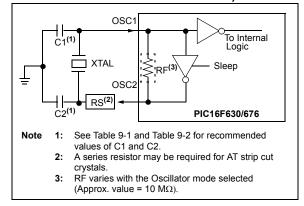

# 9.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

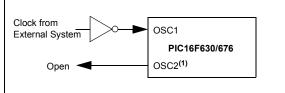

In XT, LP or HS modes a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation (see Figure 9-1). The PIC16F630/676 oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may yield a frequency outside of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1 pin (see Figure 9-2).

#### FIGURE 9-1: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (HS, XT OR LP OSC CONFIGURATION)

### EXTERNAL CLOCK INPUT OPERATION (HS, XT, EC, OR LP OSC CONFIGURATION)

Note 1: Functions as RA4 in EC Osc mode.

# TABLE 9-1:CAPACITOR SELECTION FOR<br/>CERAMIC RESONATORS

| Ranges Characterized:                                                                                                                                                                                                                                                                                                          |                               |                                   |                                   |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------------------|-----------------------------------|--|--|--|--|--|

| Mode                                                                                                                                                                                                                                                                                                                           | Freq                          | OSC1(C1)                          | OSC2(C2)                          |  |  |  |  |  |

| ХТ                                                                                                                                                                                                                                                                                                                             | 455 kHz<br>2.0 MHz<br>4.0 MHz | 68-100 pF<br>15-68 pF<br>15-68 pF | 68-100 pF<br>15-68 pF<br>15-68 pF |  |  |  |  |  |

| HS                                                                                                                                                                                                                                                                                                                             | 8.0 MHz<br>16.0 MHz           | 10-68 pF<br>10-22 pF              | 10-68 pF<br>10-22 pF              |  |  |  |  |  |

| Note 1: Higher capacitance increases the stability<br>of the oscillator but also increases the<br>start-up time. These values are for design<br>guidance only. Since each resonator has<br>its own characteristics, the user should<br>consult the resonator manufacturer for<br>appropriate values of external<br>components. |                               |                                   |                                   |  |  |  |  |  |

#### TABLE 9-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR

| Mode                                               | Freq                      | OSC1(C1)                          | OSC2(C2)                           |  |  |  |  |  |

|----------------------------------------------------|---------------------------|-----------------------------------|------------------------------------|--|--|--|--|--|

| LP                                                 | 32 kHz                    | 68-100 pF                         | 68-100 pF                          |  |  |  |  |  |

| ХТ                                                 | 100 kHz<br>2 MHz<br>4 MHz | 68-150 pF<br>15-30 pF<br>15-30 pF | 150-200 pF<br>15-30 pF<br>15-30 pF |  |  |  |  |  |

| HS                                                 | 8 MHz<br>10 MHz<br>20 MHz | 15-30 pF<br>15-30 pF<br>15-30 pF  | 15-30 pF<br>15-30 pF<br>15-30 pF   |  |  |  |  |  |

| Note 1: Higher capacitance increases the stability |                           |                                   |                                    |  |  |  |  |  |

of the oscillator but also increases the start-up time. These values are for design guidance only. Rs may be required in HS mode as well as XT mode to avoid overdriving crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

#### TABLE 10-2: PIC16F630/676 INSTRUCTION SET

| Mnemonic,      |       | Description                  | Cycles       |        | 14-Bit  | Opcode | Status | Natas    |       |

|----------------|-------|------------------------------|--------------|--------|---------|--------|--------|----------|-------|

| Ореі           | rands | Description                  |              | MSb    |         |        | LSb    | Affected | Notes |

|                |       | BYTE-ORIENTED FILE           | REGISTER OPE | RATIC  | NS      |        |        |          |       |

| ADDWF          | f, d  | Add W and f                  | 1            | 00     | 0111    | dfff   | ffff   | C,DC,Z   | 1,2   |

| ANDWF          | f, d  | AND W with f                 | 1            | 00     | 0101    | dfff   | ffff   | Z        | 1,2   |

| CLRF           | f     | Clear f                      | 1            | 00     | 0001    | lfff   | ffff   | Z        | 2     |

| CLRW           | -     | Clear W                      | 1            | 00     | 0001    | 0xxx   | XXXX   | Z        |       |

| COMF           | f, d  | Complement f                 | 1            | 00     | 1001    | dfff   | ffff   | Z        | 1,2   |

| DECF           | f, d  | Decrement f                  | 1            | 00     | 0011    | dfff   | ffff   | Z        | 1,2   |

| DECFSZ         | f, d  | Decrement f, Skip if 0       | 1(2)         | 00     | 1011    | dfff   | ffff   |          | 1,2,3 |

| INCF           | f, d  | Increment f                  | 1            | 00     | 1010    | dfff   | ffff   | Z        | 1,2   |

| INCFSZ         | f, d  | Increment f, Skip if 0       | 1(2)         | 00     | 1111    | dfff   | ffff   |          | 1,2,3 |

| IORWF          | f, d  | Inclusive OR W with f        | 1            | 00     | 0100    | dfff   | ffff   | Z        | 1,2   |

| MOVF           | f, d  | Move f                       | 1            | 00     | 1000    | dfff   | ffff   | Z        | 1,2   |

| MOVWF          | f     | Move W to f                  | 1            | 00     | 0000    | lfff   | ffff   |          |       |

| NOP            | -     | No Operation                 | 1            | 00     | 0000    | 0xx0   | 0000   |          |       |

| RLF            | f, d  | Rotate Left f through Carry  | 1            | 00     | 1101    | dfff   | ffff   | С        | 1,2   |

| RRF            | f, d  | Rotate Right f through Carry | 1            | 00     | 1100    | dfff   | ffff   | С        | 1,2   |

| SUBWF          | f, d  | Subtract W from f            | 1            | 00     | 0010    | dfff   | ffff   | C,DC,Z   | 1,2   |

| SWAPF          | f, d  | Swap nibbles in f            | 1            | 00     | 1110    | dfff   | ffff   |          | 1,2   |

| XORWF          | f, d  | Exclusive OR W with f        | 1            | 00     | 0110    | dfff   | ffff   | Z        | 1,2   |

|                |       | BIT-ORIENTED FILE            |              | RATION | NS      |        |        |          |       |

| BCF            | f, b  | Bit Clear f                  | 1            | 01     | 00bb    | bfff   | ffff   |          | 1,2   |

| BSF            | f, b  | Bit Set f                    | 1            | 01     | 01bb    | bfff   | ffff   |          | 1,2   |

| BTFSC          | f, b  | Bit Test f, Skip if Clear    | 1 (2)        | 01     | 10bb    | bfff   | ffff   |          | 3     |

| BTFSS          | f, b  | Bit Test f, Skip if Set      | 1 (2)        | 01     | 11bb    | bfff   | ffff   |          | 3     |

|                |       | LITERAL AND CO               | NTROL OPERAT | IONS   |         |        |        |          |       |

| ADDLW          | k     | Add literal and W            | 1            | 11     | 111x    | kkkk   | kkkk   | C,DC,Z   |       |

| ANDLW          | k     | AND literal with W           | 1            | 11     | 1001    | kkkk   | kkkk   | Z        |       |

| CALL           | k     | Call subroutine              | 2            | 10     | 0 k k k | kkkk   | kkkk   |          |       |

| CLRWDT         | -     | Clear Watchdog Timer         | 1            | 00     | 0000    | 0110   | 0100   | TO,PD    |       |

| GOTO           | k     | Go to address                | 2            | 10     | 1kkk    | kkkk   | kkkk   |          |       |

| IORLW          | k     | Inclusive OR literal with W  | 1            | 11     | 1000    | kkkk   | kkkk   | Z        |       |

| MOVLW          | k     | Move literal to W            | 1            | 11     | 00xx    | kkkk   | kkkk   |          |       |

| RETFIE         | -     | Return from interrupt        | 2            | 00     | 0000    | 0000   | 1001   |          |       |

| RETLW          | k     | Return with literal in W     | 2            | 11     | 01xx    | kkkk   | kkkk   |          |       |

| RETURN         | -     | Return from Subroutine       | 2            | 00     | 0000    | 0000   | 1000   |          |       |

|                | -     | Go into Standby mode         | 1            | 00     | 0000    | 0110   | 0011   | TO,PD    |       |

| SLEEP          |       | -                            |              |        |         |        |        | 0 0 0 7  |       |

| SLEEP<br>SUBLW | k     | Subtract W from literal      | 1            | 11     | 110x    | kkkk   | kkkk   | C,DC,Z   |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTA, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 module.

3: If Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

**Note:** Additional information on the mid-range instruction set is available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

## 11.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

# 11.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

# 11.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

## 11.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 11.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- · Rich directive set

- Flexible macro language

- · MPLAB IDE compatibility

# 11.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

### 11.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

### 11.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 11.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup>.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

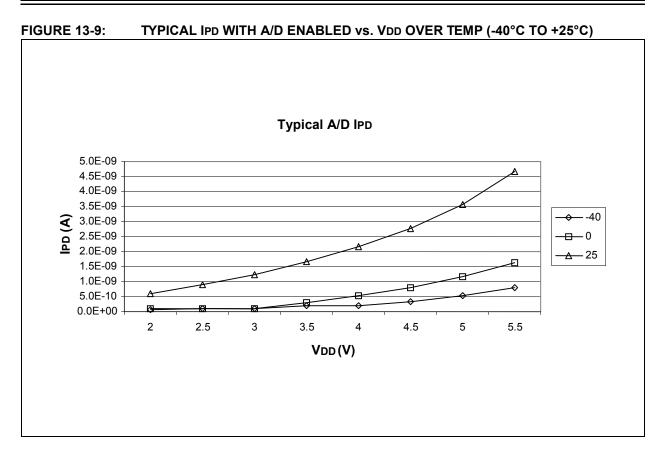

# 12.1 DC Characteristics: PIC16F630/676-I (Industrial), PIC16F630/676-E (Extended)

| DC CHARACTERISTICS                       |      |                                                                  | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \end{array}$ |      |                                        |                  |                                                                                                                                                            |  |

|------------------------------------------|------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No. Sym Characteristic          |      |                                                                  | Min                                                                                                                                                                                                                                                             | Тур† | Max                                    | Units            | Conditions                                                                                                                                                 |  |

| D001<br>D001A<br>D001B<br>D001C<br>D001D | Vdd  | Supply Voltage                                                   | 2.0<br>2.2<br>2.5<br>3.0<br>4.5                                                                                                                                                                                                                                 |      | 5.5<br>5.5<br>5.5<br>5.5<br>5.5<br>5.5 | V<br>V<br>V<br>V | Fosc < = 4 MHz:<br>PIC16F630/676 with A/D off<br>PIC16F676 with A/D on, 0°C to +125°C<br>PIC16F676 with A/D on, -40°C to +125°C<br>4 MHz < Fosc < = 10 MHz |  |

| D002                                     | Vdr  | RAM Data Retention<br>Voltage <sup>(1)</sup>                     | 1.5*                                                                                                                                                                                                                                                            | —    | -                                      | V                | Device in Sleep mode                                                                                                                                       |  |

| D003                                     | VPOR | VDD Start Voltage to<br>ensure internal Power-on<br>Reset signal | —                                                                                                                                                                                                                                                               | Vss  | _                                      | V                | See section on Power-on Reset for details                                                                                                                  |  |

| D004                                     | Svdd | Vod Rise Rate to ensure<br>internal Power-on Reset<br>signal     | 0.05*                                                                                                                                                                                                                                                           | —    | _                                      | V/ms             | See section on Power-on Reset for details                                                                                                                  |  |

| D005                                     | VBOD |                                                                  | _                                                                                                                                                                                                                                                               | 2.1  |                                        | V                |                                                                                                                                                            |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

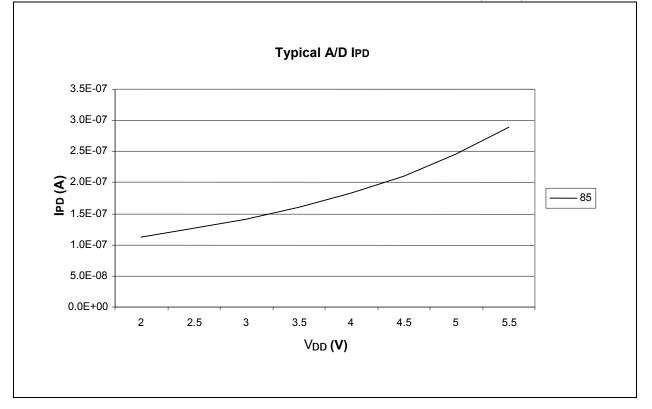

| Param<br>No. | Sym  | Characteristic                                          | Min        | Тур†                      | Мах           | Units | Conditions                                                          |

|--------------|------|---------------------------------------------------------|------------|---------------------------|---------------|-------|---------------------------------------------------------------------|

| A01          | NR   | Resolution                                              |            | _                         | 10 bits       | bit   |                                                                     |

| A02          | Eabs | Total Absolute<br>Error*                                | _          | —                         | ±1            | LSb   | VREF = 5.0V                                                         |

| A03          | EIL  | Integral Error                                          | _          | _                         | ±1            | LSb   | VREF = 5.0V                                                         |

| A04          | Edl  | Differential Error                                      | _          | _                         | ±1            | LSb   | No missing codes to 10 bits<br>VREF = 5.0V                          |

| A05          | Efs  | Full Scale Range                                        | 2.2*       | —                         | 5.5*          | V     |                                                                     |

| A06          | EOFF | Offset Error                                            | _          | —                         | ±1            | LSb   | VREF = 5.0V                                                         |

| A07          | Egn  | Gain Error                                              | _          | —                         | ±1            | LSb   | VREF = 5.0V                                                         |

| A10          | —    | Monotonicity                                            | _          | guaranteed <sup>(3)</sup> | _             | —     | $VSS \leq VAIN \leq VREF+$                                          |

| A20<br>A20A  | VREF | Reference Voltage                                       | 2.0<br>2.5 | _                         | <br>Vdd + 0.3 | V     | Absolute minimum to ensure 10-bit<br>accuracy                       |

| A21          | Vref | Reference V High<br>(VDD or VREF)                       | Vss        | —                         | Vdd           | V     |                                                                     |

| A25          | Vain | Analog Input<br>Voltage                                 | Vss        |                           | VREF          | V     |                                                                     |

| A30          | ZAIN | Recommended<br>Impedance of<br>Analog Voltage<br>Source | _          | _                         | 10            | kΩ    |                                                                     |

| A50          | IREF | VREF Input<br>Current <sup>(2)</sup>                    | 10         | —                         | 1000          | μA    | During VAIN acquisition.<br>Based on differential of VHOLD to VAIN. |

|              |      |                                                         |            | —                         | 10            | μA    | During A/D conversion cycle.                                        |

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: When A/D is off, it will not consume any current other than leakage current. The power-down current spec includes any such leakage from the A/D module.

2: VREF current is from External VREF or VDD pin, whichever is selected as reference input.

3: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

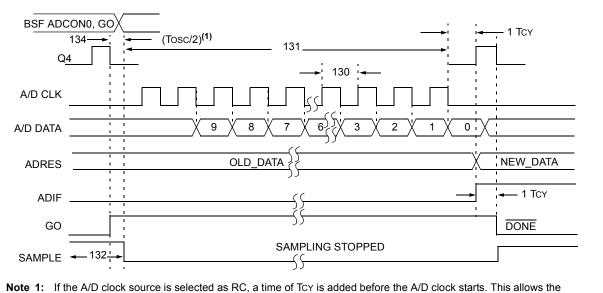

SLEEP instruction to be executed.

| Param<br>No. | Sym  | Characteristic                                                        | Min      | Тур†   | Мах  | Units | Conditions                                                                                                                                                                                                                   |

|--------------|------|-----------------------------------------------------------------------|----------|--------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | Tad  | A/D Clock Period                                                      | 1.6      | —      | _    | μS    | Tosc based, VREF $\geq$ 3.0V                                                                                                                                                                                                 |

|              |      |                                                                       | 3.0*     | _      | —    | μS    | Tosc based, VREF full range                                                                                                                                                                                                  |

| 130          | Tad  | A/D Internal RC<br>Oscillator Period                                  | 3.0*     | 6.0    | 9.0* | μs    | ADCS<1:0> = 11 (RC mode)<br>At VDD = 2.5V                                                                                                                                                                                    |

|              |      |                                                                       | 2.0*     | 4.0    | 6.0* | μS    | At VDD = 5.0V                                                                                                                                                                                                                |

| 131          | TCNV | Conversion Time<br>(not including<br>Acquisition Time) <sup>(1)</sup> | _        | 11     | —    | Tad   | Set GO bit to new data in A/D result register                                                                                                                                                                                |

| 132          | TACQ | Acquisition Time                                                      | (Note 2) | 11.5   | —    | μS    |                                                                                                                                                                                                                              |

|              |      |                                                                       | 5*       | _      | _    | μs    | The minimum time is the amplifier<br>settling time. This may be used if the<br>"new" input voltage has not changed<br>by more than 1 LSb (i.e., 4.1 mV @<br>4.096V) from the last sampled volt-<br>age (as stored on CHOLD). |

| 134          | TGO  | Q4 to A/D Clock<br>Start                                              | _        | Tosc/2 | —    | _     | If the A/D clock source is selected as RC, a time of TCY is added before the A/D clock starts. This allows the SLEEP instruction to be executed.                                                                             |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** ADRES register may be read on the following TCY cycle.

**2:** See Table 7-1 for minimum conditions.