Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | -                                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                        |

| Number of I/O              | 12                                                                      |

| Program Memory Size        | 1.75KB (1K x 14)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 128 x 8                                                                 |

| RAM Size                   | 64 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                               |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                 |

| Supplier Device Package    | 14-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f630-i-p |

TABLE 1-1: PIC16F630/676 PINOUT DESCRIPTION

| Name                          | Function | Input<br>Type | Output<br>Type | Description                                                        |  |  |

|-------------------------------|----------|---------------|----------------|--------------------------------------------------------------------|--|--|

| RA0/AN0/CIN+/ICSPDAT          | RA0      | TTL           | CMOS           | Bidirectional I/O w/ programmable pull-up and interrupt-on-change. |  |  |

|                               | AN0      | AN            | _              | A/D Channel 0 input.                                               |  |  |

|                               | CIN+     | AN            |                | Comparator input.                                                  |  |  |

|                               | ICSPDAT  | TTL           | CMOS           | Serial Programming Data I/O.                                       |  |  |

| RA1/AN1/CIN-/VREF/<br>ICSPCLK | RA1      | TTL           | CMOS           | Bidirectional I/O w/ programmable pull-up and interrupt-on-change. |  |  |

|                               | AN1      | AN            | _              | A/D Channel 1 input.                                               |  |  |

|                               | CIN-     | AN            | _              | Comparator input.                                                  |  |  |

|                               | VREF     | AN            | _              | External Voltage reference.                                        |  |  |

|                               | ICSPCLK  | ST            | _              | Serial Programming Clock.                                          |  |  |

| RA2/AN2/COUT/T0CKI/INT        | RA2      | ST            | CMOS           | Bidirectional I/O w/ programmable pull-up and interrupt-on-change. |  |  |

|                               | AN2      | AN            | _              | A/D Channel 2 input.                                               |  |  |

|                               | COUT     | _             | CMOS           | Comparator output.                                                 |  |  |

|                               | T0CKI    | ST            | _              | Timer0 clock input.                                                |  |  |

|                               | INT      | ST            | _              | External Interrupt.                                                |  |  |

| RA3/MCLR/VPP                  | RA3      | TTL           | _              | Input port with interrupt-on-change.                               |  |  |

|                               | MCLR     | ST            | _              | Master Clear.                                                      |  |  |

|                               | VPP      | HV            | _              | Programming voltage.                                               |  |  |

| RA4/T1G/AN3/OSC2/<br>CLKOUT   | RA4      | TTL           | CMOS           | Bidirectional I/O w/ programmable pull-up and interrupt-on-change. |  |  |

|                               | T1G      | ST            | _              | Timer1 gate.                                                       |  |  |

|                               | AN3      | AN3           | _              | A/D Channel 3 input.                                               |  |  |

|                               | OSC2     | _             | XTAL           | Crystal/Resonator.                                                 |  |  |

|                               | CLKOUT   | _             | CMOS           | Fosc/4 output.                                                     |  |  |

| RA5/T1CKI/OSC1/CLKIN          | RA5      | TTL           | CMOS           | Bidirectional I/O w/ programmable pull-up and interrupt-on-change. |  |  |

|                               | T1CKI    | ST            | _              | Timer1 clock.                                                      |  |  |

|                               | OSC1     | XTAL          | _              | Crystal/Resonator.                                                 |  |  |

|                               | CLKIN    | ST            | _              | External clock input/RC oscillator connection.                     |  |  |

| RC0/AN4                       | RC0      | TTL           | CMOS           | Bidirectional I/O.                                                 |  |  |

|                               | AN4      | AN4           | _              | A/D Channel 4 input.                                               |  |  |

| RC1/AN5                       | RC1      | TTL           | CMOS           | Bidirectional I/O.                                                 |  |  |

|                               | AN5      | AN5           | _              | A/D Channel 5 input.                                               |  |  |

| RC2/AN6                       | RC2      | TTL           | CMOS           | Bidirectional I/O.                                                 |  |  |

| -                             | AN6      | AN6           | _              | A/D Channel 6 input.                                               |  |  |

| RC3/AN7                       | RC3      | TTL           | CMOS           | Bidirectional I/O.                                                 |  |  |

|                               | AN7      | AN7           | _              | A/D Channel 7 input.                                               |  |  |

| RC4                           | RC4      | TTL           | CMOS           | Bidirectional I/O.                                                 |  |  |

| RC5                           | RC5      | TTL           | CMOS           | Bidirectional I/O.                                                 |  |  |

| Vss                           | Vss      | Power         | _              | Ground reference.                                                  |  |  |

| VDD                           | VDD      | Power         | _              | Positive supply.                                                   |  |  |

**Legend:** Shade = PIC16F676 only

TTL = TTL input buffer

ST = Schmitt Trigger input buffer

#### 2.2.2.2 OPTION Register

The OPTION register is a readable and writable register, which contains various control bits to configure:

- TMR0/WDT prescaler

- · External RA2/INT interrupt

- TMR0

- · Weak pull-ups on PORTA

To achieve a 1:1 prescaler assignment for TMR0, assign the prescaler to the WDT by setting PSA bit to '1' (OPTION<3>). See **Section 4.4 "Prescaler"**.

#### REGISTER 2-2: OPTION\_REG — OPTION REGISTER (ADDRESS: 81h)

|   | R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|---|-------|--------|-------|-------|-------|-------|-------|-------|

| F | RAPU  | INTEDG | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   |

| Ī | bit 7 |        |       |       |       |       |       | bit 0 |

Note:

bit 7 RAPU: PORTA Pull-up Enable bit

1 = PORTA pull-ups are disabled

0 = PORTA pull-ups are enabled by individual PORT latch values

bit 6 INTEDG: Interrupt Edge Select bit

1 = Interrupt on rising edge of RA2/INT pin

0 = Interrupt on falling edge of RA2/INT pin

bit 5 **TOCS**: TMR0 Clock Source Select bit

1 = Transition on RA2/T0CKI pin

0 = Internal instruction cycle clock (CLKOUT)

bit 4 T0SE: TMR0 Source Edge Select bit

1 = Increment on high-to-low transition on RA2/T0CKI pin

0 = Increment on low-to-high transition on RA2/T0CKI pin

bit 3 **PSA:** Prescaler Assignment bit

1 = Prescaler is assigned to the WDT

0 = Prescaler is assigned to the Timer0 module

bit 2-0 **PS2:PS0:** Prescaler Rate Select bits

| Bit Value | TMR0 Rate | WDT Rate |

|-----------|-----------|----------|

| 000       | 1:2       | 1:1      |

| 001       | 1:4       | 1:2      |

| 010       | 1:8       | 1:4      |

| 011       | 1:16      | 1:8      |

| 100       | 1:32      | 1:16     |

| 101       | 1:64      | 1:32     |

| 110       | 1:128     | 1:64     |

| 111       | 1:256     | 1 : 128  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented I  | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

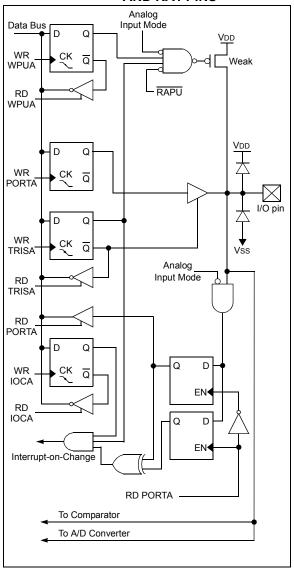

## 3.2.3 PIN DESCRIPTIONS AND DIAGRAMS

Each PORTA pin is multiplexed with other functions. The pins and their combined functions are briefly described here. For specific information about individual functions such as the comparator or the A/D, refer to the appropriate section in this Data Sheet.

#### 3.2.3.1 RA0/AN0/CIN+

Figure 3-1 shows the diagram for this pin. The RA0 pin is configurable to function as one of the following:

- · a general purpose I/O

- an analog input for the A/D (PIC16F676 only)

- · an analog input to the comparator

#### 3.2.3.2 RA1/AN1/CIN-/VREF

Figure 3-1 shows the diagram for this pin. The RA1 pin is configurable to function as one of the following:

- · as a general purpose I/O

- an analog input for the A/D (PIC16F676 only)

- · an analog input to the comparator

- a voltage reference input for the A/D (PIC16F676 only)

FIGURE 3-1: BLOCK DIAGRAM OF RA0

AND RA1 PINS

#### REGISTER 5-1: T1CON — TIMER1 CONTROL REGISTER (ADDRESS: 10h)

| U-0   | R/W-0  | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------|--------|---------|---------|---------|--------|--------|--------|

| _     | TMR1GE | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N |

| bit 7 |        |         |         |         |        |        | hit 0  |

bit 7 **Unimplemented:** Read as '0'

bit 6 TMR1GE: Timer1 Gate Enable bit

If TMR1ON = 0: This bit is ignored If TMR1ON = 1:

1 = Timer1 is on if  $\overline{11G}$  pin is low

0 = Timer1 is on

bit 5-4 T1CKPS1:T1CKPS0: Timer1 Input Clock Prescale Select bits

11 = 1:8 Prescale Value 10 = 1:4 Prescale Value 01 = 1:2 Prescale Value 00 = 1:1 Prescale Value

bit 3 T10SCEN: LP Oscillator Enable Control bit

If INTOSC without CLKOUT oscillator is active:

1 = LP oscillator is enabled for Timer1 clock

0 = LP oscillator is off

Else:

This bit is ignored

bit 2 T1SYNC: Timer1 External Clock Input Synchronization Control bit

**TMR1CS = 1**:

1 = Do not synchronize external clock input

0 = Synchronize external clock input

TMR1CS = 0:

This bit is ignored. Timer1 uses the internal clock.

bit 1 TMR1CS: Timer1 Clock Source Select bit

1 = External clock from T1OSO/T1CKI pin (on the rising edge)

0 = Internal clock (Fosc/4)

bit 0 TMR10N: Timer1 On bit

1 = Enables Timer10 = Stops Timer1

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

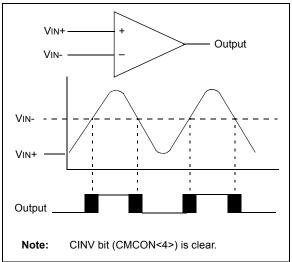

#### 6.1 Comparator Operation

A single comparator is shown in Figure 6-1, along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 6-1 represent the uncertainty due to input offsets and response time.

**Note:** To use CIN+ and CIN- pins as analog inputs, the appropriate bits must be programmed in the CMCON (19h) register.

The polarity of the comparator output can be inverted by setting the CINV bit (CMCON<4>). Clearing CINV results in a non-inverted output. A complete table showing the output state versus input conditions and the polarity bit is shown in Table 6-1.

TABLE 6-1: OUTPUT STATE VS. INPUT CONDITIONS

| Input Conditions | CINV | COUT |

|------------------|------|------|

| VIN- > VIN+      | 0    | 0    |

| VIN- < VIN+      | 0    | 1    |

| VIN- > VIN+      | 1    | 1    |

| VIN- < VIN+      | 1    | 0    |

FIGURE 6-1: SINGLE COMPARATOR

### REGISTER 7-3: ANSEL—ANALOG SELECT REGISTER (ADRESS: 91h) (PIC16F676 ONLY)

| R/W-1 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| ANS7  | ANS6  | ANS5  | ANS4  | ANS3  | ANS2  | ANS1  | ANS0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

bit 7-0: ANS<7:0>: Analog Select between analog or digital function on pins AN<7:0>, respectively.

- 1 = Analog input. Pin is assigned as analog input. (1)

- 0 = Digital I/O. Pin is assigned to port or special function.

**Note 1:** Setting a pin to an analog input automatically disables the digital input circuitry, weak pull-ups, and interrupt-on-change if available. The corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented I  | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 9.1 Configuration Bits

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1') to select various device configurations, as shown in Register 9-1. These bits are mapped in program memory location 2007h.

Address 2007h is beyond the user program memory space. It belongs to the special configuration memory space (2000h-3FFFh), which can be accessed only during programming. See PIC16F630/676 Programming Specification for more information.

#### REGISTER 9-1: CONFIG — CONFIGURATION WORD (ADDRESS: 2007h)

| R/P-1  | R/P-1 | U-0 | U-0 | U-0 | R/P-1 |

|--------|-------|-----|-----|-----|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| BG1    | BG0   | _   | _   | _   | CPD   | CP    | BODEN | MCLRE | PWRTE | WDTE  | F0SC2 | F0SC1 | F0SC0 |

| bit 13 |       |     |     |     |       |       |       |       |       |       |       |       | bit 0 |

Note:

bit 13-12 **BG1:BG0:** Bandgap Calibration bits for BOD and POR voltage<sup>(1)</sup>

00 = Lowest bandgap voltage

11 = Highest bandgap voltage

bit 11-9 **Unimplemented**: Read as '0'

bit 8 CPD: Data Code Protection bit<sup>(2)</sup>

1 = Data memory code protection is disabled

0 = Data memory code protection is disabled

bit 7 **CP**: Code Protection bit<sup>(3)</sup>

${\tt 1}$  = Program Memory code protection is disabled

0 = Program Memory code protection is enabled

bit 6 BODEN: Brown-out Detect Enable bit (4)

1 = BOD enabled 0 = BOD disabled

bit 5 MCLRE: RA3/MCLR pin function select bit (5)

1 = RA3/ $\overline{\text{MCLR}}$  pin function is  $\overline{\text{MCLR}}$

0 = RA3/MCLR pin function is digital I/O, MCLR internally tied to VDD

bit 4 **PWRTE**: Power-up Timer Enable bit

1 = PWRT disabled

0 = PWRT enabled

bit 3 WDTE: Watchdog Timer Enable bit

1 = WDT enabled 0 = WDT disabled

bit 2-0 FOSC2:FOSC0: Oscillator Selection bits

111 = RC oscillator: CLKOUT function on RA4/OSC2/CLKOUT pin, RC on RA5/OSC1/CLKIN

110 = RC oscillator: I/O function on RA4/OSC2/CLKOUT pin, RC on RA5/OSC1/CLKIN

101 = INTOSC oscillator: CLKOUT function on RA4/OSC2/CLKOUT pin, I/O function on RA5/OSC1/CLKIN

100 = INTOSC oscillator: I/O function on RA4/OSC2/CLKOUT pin, I/O function on RA5/OSC1/CLKIN

011 = EC: I/O function on RA4/OSC2/CLKOUT pin, CLKIN on RA5/OSC1/CLKIN

010 = HS oscillator: High speed crystal/resonator on RA4/OSC2/CLKOUT and RA5/OSC1/CLKIN

001 = XT oscillator: Crystal/resonator on RA4/OSC2/CLKOUT and RA5/OSC1/CLKIN

000 = LP oscillator: Low power crystal on RA4/OSC2/CLKOUT and RA5/OSC1/CLKIN

Note 1: The Bandgap Calibration bits are factory programmed and must be read and saved prior to erasing the device as specified in the PIC16F630/676 Programming Specification. These bits are reflected in an export of the Configuration Word. Microchip Development Tools maintain all calibration bits to factory settings.

2: The entire data EEPROM will be erased when the code protection is turned off.

**3:** The entire program memory will be erased, including OSCCAL value, when the code protection is turned off.

4: Enabling Brown-out Detect does not automatically enable Power-up Timer.

5: When MCLR is asserted in INTOSC or RC mode, the internal clock oscillator is disabled.

Legend:

P = Programmed using ICSP™

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR 1 = bit is set 0 = bit is cleared x = bit is unknown

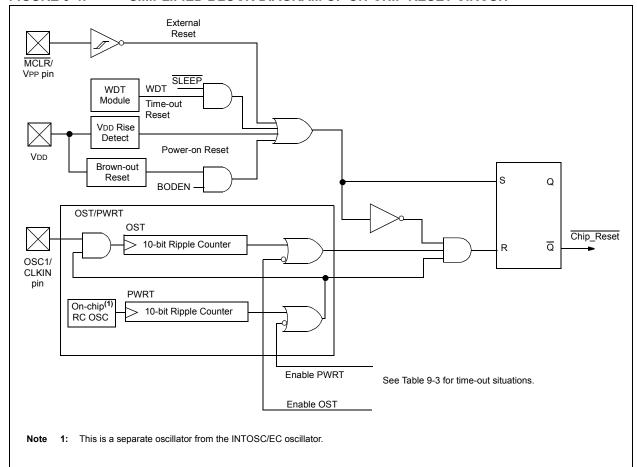

#### 9.3 Reset

The PIC16F630/676 differentiates between various kinds of Reset:

- a) Power-on Reset (POR)

- b) WDT Reset during normal operation

- c) WDT Reset during Sleep

- d) MCLR Reset during normal operation

- e) MCLR Reset during Sleep

- f) Brown-out Detect (BOD)

Some registers are not affected in any Reset condition; their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on:

- · Power-on Reset

- MCLR Reset

- WDT Reset

- · WDT Reset during Sleep

- Brown-out Detect (BOD)

They are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation.  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are set or cleared differently in different Reset situations as indicated in Table 9-4. These bits are used in software to determine the nature of the Reset. See Table 9-7 for a full description of Reset states of all registers.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 9-4.

The MCLR Reset path has a noise filter to detect and ignore small pulses. See Table 12-4 in Electrical Specifications Section for pulse-width specification.

#### FIGURE 9-4: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

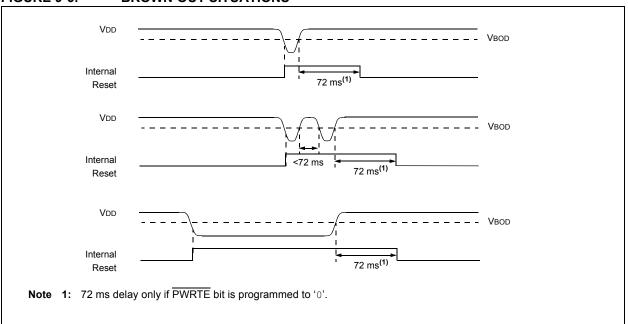

#### 9.3.5 BROWN-OUT DETECT (BOD)

The PIC16F630/676 members have on-chip Brown-out Detect circuitry. A Configuration bit, BODEN, can disable (if clear/programmed) or enable (if set) the Brown-out Detect circuitry. If VDD falls below VBOD for greater than parameter (TBOD) in Table 12-4 (see Section 12.0 "Electrical Specifications"), the Brown-out situation will reset the device. This will occur regardless of VDD slew-rate. A Reset is not guaranteed to occur if VDD falls below VBOD for less than parameter (TBOD).

On any Reset (Power-on, Brown-out Detect, Watchdog, etc.), the chip will remain in Reset until VDD rises above BVDD (see Figure 9-6). The Power-up Timer will now be invoked, if enabled, and will keep the chip in Reset an additional 72 ms.

Note: A Brown-out Detect does not enable the Power-up Timer if the PWRTE bit in the Configuration Word is set.

If VDD drops below BVDD while the Power-up Timer is running, the chip will go back into a Brown-out Detect and the Power-up Timer will be re-initialized. Once VDD rises above BVDD, the Power-up Timer will execute a 72 ms Reset.

#### 9.3.6 TIME-OUT SEQUENCE

On power-up, the time-out sequence is as follows: first, PWRT time-out is invoked after POR has expired. Then, OST is activated. The total time-out will vary based on oscillator configuration and PWRTE bit status. For example, in EC mode with PWRTE bit erased (PWRT disabled), there will be no time-out at all. Figure 9-7, Figure 9-8 and Figure 9-9 depict time-out sequences.

Since the time-outs occur from the POR pulse, if MCLR is kept low long enough, the time-outs will expire. Then bringing MCLR high will begin execution immediately (see Figure 9-8). This is useful for testing purposes or to synchronize more than one PIC16F630/676 device operating in parallel.

Table 9-6 shows the Reset conditions for some special registers, while Table 9-7 shows the Reset conditions for all the registers.

# 9.3.7 POWER CONTROL (PCON) STATUS REGISTER

The power CONTROL/STATUS register, PCON (address 8Eh) has two bits.

Bit 0 is  $\overline{\text{BOD}}$  (Brown-out).  $\overline{\text{BOD}}$  is unknown on Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if  $\overline{\text{BOD}} = 0$ , indicating that a brown-out has occurred. The  $\overline{\text{BOD}}$  Status bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (by setting  $\overline{\text{BODEN}}$  bit = 0 in the Configuration Word).

Bit 1 is  $\overline{\mathsf{POR}}$  (Power-on Reset). It is a '0' on Power-on Reset and unaffected otherwise. The user must write a '1' to this bit following a Power-on Reset. On a subsequent Reset, if  $\overline{\mathsf{POR}}$  is '0', it will indicate that a Power-on Reset must have occurred (i.e., VDD may have gone too low).

FIGURE 9-10: **INTERRUPT LOGIC** IOCA-RA0 -IOCA-RA1 \_ IOCA1 \_ IOCA-RA2 \_ IOCA2 \_ IOCA-RA3 | IOCA-RA4 – IOCA4 – IOCA-RA5 – IOCA5 – TOIF -Wake-up (If in Sleep mode) INTF \_ Interrupt to CPU TMR1IF -TMR1IE -**RAIF** RAIE -**CMIF** CMIE PEIE ADIF -GIE EEIF -Note 1: PIC16F676 only.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                 |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                     |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                     |  |  |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                             |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Description:     | The contents of register 'f' are decremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'.  If the result is 1, the next instruction is executed. If the result is 0, then a NOP is executed instead, making it a 2-cycle instruction. |  |  |  |  |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                       |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                           |

| Operands:        | $\begin{aligned} 0 &\leq f \leq 127 \\ d &\in [0,1] \end{aligned}$                                                                                                                                                                                                                                           |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                   |

| Status Affected: | None                                                                                                                                                                                                                                                                                                         |

| Description:     | The contents of register 'f' are incremented. If 'd' is $0$ , the result is placed in the W register. If 'd' is $1$ , the result is placed back in register 'f'. If the result is $1$ , the next instruction is executed. If the result is $0$ , a NOP is executed instead, making it a 2-cycle instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                              |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] GOTO k                                                                                                                                                                    |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                              |  |  |  |  |  |  |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                   |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                              |  |  |  |  |  |  |

| Description:     | GOTO is an unconditional branch. The eleven-bit immediate value is loaded into PC bits <10:0>. The upper bits of PC are loaded from PCLATH<4:3>. GOTO is a two-cycle instruction. |  |  |  |  |  |  |

| IORLW            | Inclusive OR Literal with W                                                                                      |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] IORLW k                                                                                                  |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                              |  |  |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow (W)$                                                                                     |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                |  |  |  |  |  |  |

| Description:     | The contents of the W register are OR'ed with the eight-bit literal 'k'. The result is placed in the W register. |  |  |  |  |  |  |

| Syntax:          | [label] INCF f,d                                                                                                                                           |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                         |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                        |

| Status Affected: | Z                                                                                                                                                          |

| Description:     | The contents of register 'f' are incremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'. |

Increment f

| IORWF            | Inclusive OR W with f                                                                                                                                       |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ label ] IORWF f,d                                                                                                                                         |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                          |  |  |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                    |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                           |  |  |  |  |  |  |

| Description:     | Inclusive OR the W register with register 'f'. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'. |  |  |  |  |  |  |

**INCF**

# 11.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit™ 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows® programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit™ 2 enables in-circuit debugging on most PIC® microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

### 11.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

# 11.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>TM</sup> and dsPICDEM<sup>TM</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, Keeloq® security ICs, CAN, IrDA®, PowerSmart battery management, Seevallation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

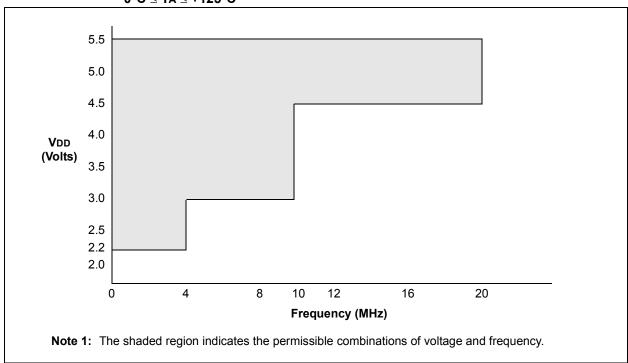

FIGURE 12-3: PIC16F676 WITH A/D ENABLED VOLTAGE-FREQUENCY GRAPH,  $0^{\circ}C \le T_A \le +125^{\circ}C$

## 12.1 DC Characteristics: PIC16F630/676-I (Industrial), PIC16F630/676-E (Extended)

| DC CHARACTERISTICS                       |      |                                                                  | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \leq \text{Ta} \leq +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \leq \text{Ta} \leq +125^{\circ}\text{C}$ for extended |     |                                 |      |                                                                                                                                                |  |

|------------------------------------------|------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No.                             | Sym  | Characteristic                                                   | Min Typ† Max Units Conditions                                                                                                                                                                                                          |     |                                 |      |                                                                                                                                                |  |

| D001<br>D001A<br>D001B<br>D001C<br>D001D | VDD  | Supply Voltage                                                   | 2.0<br>2.2<br>2.5<br>3.0<br>4.5                                                                                                                                                                                                        |     | 5.5<br>5.5<br>5.5<br>5.5<br>5.5 | >    | Fosc < = 4 MHz: PIC16F630/676 with A/D off PIC16F676 with A/D on, 0°C to +125°C PIC16F676 with A/D on, -40°C to +125°C 4 MHz < Fosc < = 10 MHz |  |

| D002                                     | VDR  | RAM Data Retention<br>Voltage <sup>(1)</sup>                     | 1.5*                                                                                                                                                                                                                                   | _   | _                               | V    | Device in Sleep mode                                                                                                                           |  |

| D003                                     | VPOR | VDD Start Voltage to<br>ensure internal Power-on<br>Reset signal | _                                                                                                                                                                                                                                      | Vss | _                               | V    | See section on Power-on Reset for details                                                                                                      |  |

| D004                                     | SVDD | VDD Rise Rate to ensure internal Power-on Reset signal           | 0.05*                                                                                                                                                                                                                                  | _   | _                               | V/ms | See section on Power-on Reset for details                                                                                                      |  |

| D005                                     | VBOD |                                                                  | _                                                                                                                                                                                                                                      | 2.1 | _                               | V    |                                                                                                                                                |  |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

<sup>†</sup> Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

TABLE 12-6: COMPARATOR SPECIFICATIONS

| Comparator Specifications |                                           | Standard<br>-40°C to +     |       |           |    |  |

|---------------------------|-------------------------------------------|----------------------------|-------|-----------|----|--|

| Sym                       | Characteristics                           | Min Typ Max Units Comments |       |           |    |  |

| Vos                       | Input Offset Voltage                      | _                          | ± 5.0 | ± 10      | mV |  |

| Vсм                       | Input Common Mode Voltage                 | 0                          | _     | VDD - 1.5 | V  |  |

| CMRR                      | Common Mode Rejection Ratio               | +55*                       | _     | _         | db |  |

| TRT                       | Response Time <sup>(1)</sup>              | _                          | 150   | 400*      | ns |  |

| TMC2COV                   | Comparator Mode Change to<br>Output Valid | _                          | _     | 10*       | μS |  |

<sup>\*</sup> These parameters are characterized but not tested.

**Note 1:** Response time measured with one comparator input at (VDD - 1.5)/2 while the other input transitions from Vss to VDD - 1.5V.

TABLE 12-7: COMPARATOR VOLTAGE REFERENCE SPECIFICATIONS

| Voltage I | Reference Specifications     | Standard Operating Conditions -40°C to +125°C (unless otherwise stated) |                   |                  |            |                                             |  |

|-----------|------------------------------|-------------------------------------------------------------------------|-------------------|------------------|------------|---------------------------------------------|--|

| Sym       | Characteristics              | Min                                                                     | Тур               | Max              | Units      | Comments                                    |  |

|           | Resolution                   | _                                                                       | VDD/24*<br>VDD/32 |                  | LSb<br>LSb | Low Range (VRR = 1)<br>High Range (VRR = 0) |  |

|           | Absolute Accuracy            | _                                                                       | _                 | ± 1/2*<br>± 1/2* | LSb<br>LSb | Low Range (VRR = 1)<br>High Range (VRR = 0) |  |

|           | Unit Resistor Value (R)      | _                                                                       | 2k*               | _                | Ω          |                                             |  |

|           | Settling Time <sup>(1)</sup> | _                                                                       | _                 | 10*              | μS         |                                             |  |

<sup>\*</sup> These parameters are characterized but not tested.

**Note 1:** Settling time measured while VRR = 1 and VR<3:0> transitions from 0000 to 1111.

NOTES:

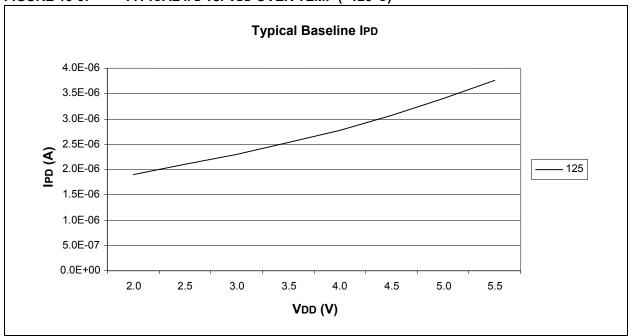

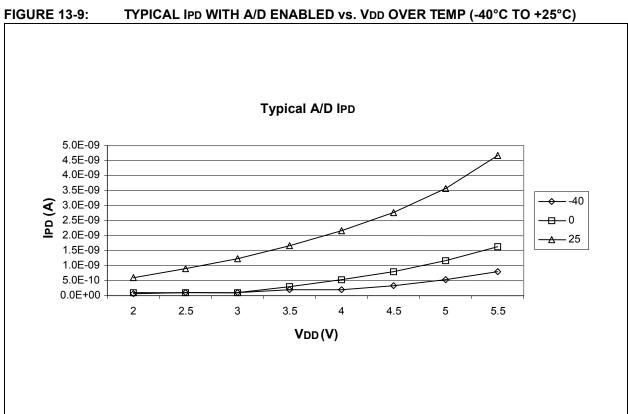

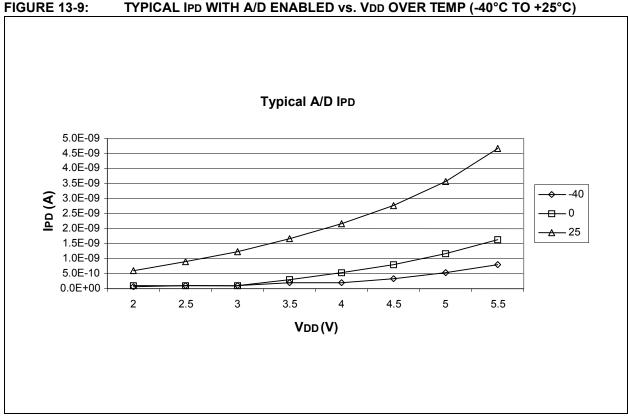

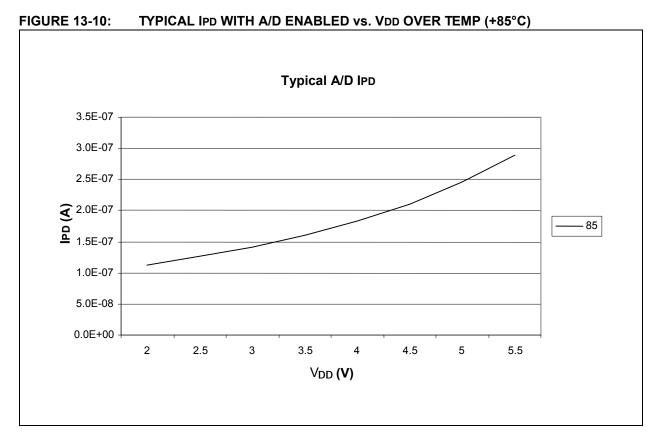

**FIGURE 13-3:** TYPICAL IPD vs. VDD OVER TEMP (+125°C)

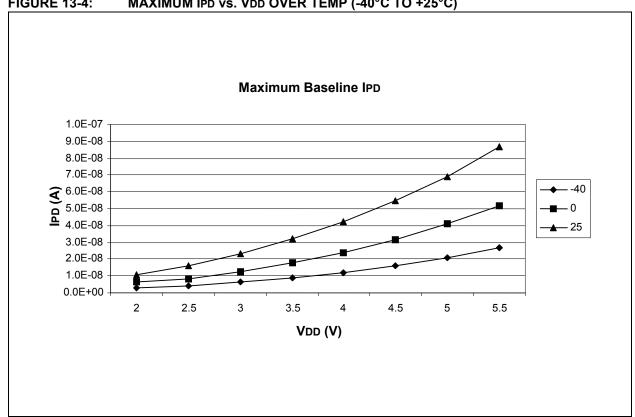

**FIGURE 13-4:** MAXIMUM IPD vs. VDD OVER TEMP (-40°C TO +25°C)

#### 14.0 PACKAGING INFORMATION

## 14.1 Package Marking Information

14-Lead PDIP (Skinny DIP)

14-Lead SOIC

14-Lead TSSOP

Example

Example

Example

**Legend:** XX...X Customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

(e3) Pb-free JEDEC designator for Matte Tin (Sn)

\* This package is Pb-free. The Pb-free JEDEC designator (e3) can be found on the outer packaging for this package.

**ote**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

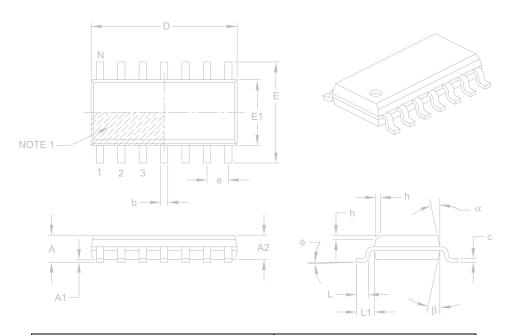

## 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            | MILLIMETERS |          |      |  |  |

|--------------------------|------------------|-------------|----------|------|--|--|

|                          | Dimension Limits | MIN         | NOM      | MAX  |  |  |

| Number of Pins           | N                |             | 14       |      |  |  |

| Pitch                    | е                |             | 1.27 BSC |      |  |  |

| Overall Height           | А                | _           | _        | 1.75 |  |  |

| Molded Package Thickness | A2               | 1.25        | _        | _    |  |  |

| Standoff §               | A1               | 0.10        | _        | 0.25 |  |  |

| Overall Width            | E                | 6.00 BSC    |          |      |  |  |

| Molded Package Width     | E1               | 3.90 BSC    |          |      |  |  |

| Overall Length           | D                | 8.65 BSC    |          |      |  |  |

| Chamfer (optional)       | h                | 0.25        | _        | 0.50 |  |  |

| Foot Length              | L                | 0.40        | _        | 1.27 |  |  |

| Footprint                | L1               | 1.04 REF    |          |      |  |  |

| Foot Angle               | ф                | 0°          | _        | 8°   |  |  |

| Lead Thickness           | С                | 0.17        | _        | 0.25 |  |  |

| Lead Width               | b                | 0.31        | _        | 0.51 |  |  |

| Mold Draft Angle Top     | α                | 5° – 15°    |          |      |  |  |

| Mold Draft Angle Bottom  | β                | 5°          | _        | 15°  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-065B