Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 12                                                                       |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 64 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                          |

| Supplier Device Package    | 14-TSSOP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f630-i-st |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0   | Device Overview                                           | 7     |

|-------|-----------------------------------------------------------|-------|

| 2.0   | Memory Organization                                       | 9     |

| 3.0   | Ports A and C                                             | 21    |

| 4.0   | Timer0 Module                                             | 31    |

| 5.0   | Timer1 Module with Gate Control                           | 34    |

| 6.0   | Comparator Module                                         | 39    |

| 7.0   | Analog-to-Digital Converter (A/D) Module (PIC16F676 only) | 45    |

| 8.0   | Data EEPROM Memory                                        | 51    |

| 9.0   | Special Features of the CPU                               | 55    |

| 10.0  | Instruction Set Summary                                   | 73    |

| 11.0  | Development Support                                       | 81    |

| 12.0  | Electrical Specifications                                 | 85    |

| 13.0  | DC and AC Characteristics Graphs and Tables               | . 107 |

| 14.0  | Packaging Information                                     | . 117 |

| Appe  | ndix A: Data Sheet Revision History                       | . 123 |

| Appe  | ndix B: Device Differences                                | . 123 |

| Appe  | ndix C: Device Migrations                                 | . 124 |

| Appe  | ndix D: Migrating from other PIC <sup>®</sup> Devices     | . 124 |

| Index |                                                           | . 125 |

| On-Li | ne Support                                                | . 129 |

| Syste | ms Information and Upgrade Hot Line                       | . 129 |

| Read  | er Response                                               | . 130 |

| Produ | ict Identification System                                 | . 131 |

|       |                                                           |       |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

NOTES:

#### **REGISTER 3-4:** IOCA — INTERRUPT-ON-CHANGE PORTA REGISTER (ADDRESS: 96h)

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | IOCA5 | IOCA4 | IOCA3 | IOCA2 | IOCA1 | IOCA0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

bit 7-6 Unimplemented: Read as '0'

bit 5-0

IOCA<5:0>: Interrupt-on-Change PORTA Control bits

1 = Interrupt-on-change enabled

0 = Interrupt-on-change disabled

**Note:** Global Interrupt Enable (GIE) must be enabled for individual interrupts to be recognized.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

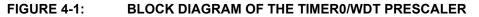

## 4.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

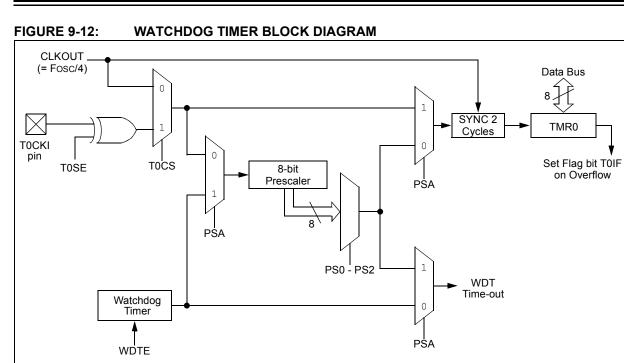

Figure 4-1 is a block diagram of the Timer0 module and the prescaler shared with the WDT.

| Note: | Additional                               | information | on | the | Timer0  |

|-------|------------------------------------------|-------------|----|-----|---------|

|       | module is available in the PIC® Mid-Rang |             |    |     | d-Range |

|       | Reference Manual, (DS33023).             |             |    |     |         |

#### 4.1 Timer0 Operation

Timer mode is selected by clearing the T0CS bit (OPTION\_REG<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If TMR0 is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting the T0CS bit (OPTION\_REG<5>). In this mode, the Timer0 module will increment either on every rising or falling edge of pin RA2/T0CKI. The incrementing edge is determined by the source edge (T0SE) control bit (OPTION\_REG<4>). Clearing the T0SE bit selects the rising edge.

| Note: | requirements.           | Additional | ic external clock<br>information on<br>lable in the PIC <sup>®</sup> |

|-------|-------------------------|------------|----------------------------------------------------------------------|

|       | Mid-Range<br>(DS33023). | Reference  | ce Manual,                                                           |

## 4.2 Timer0 Interrupt

A Timer0 interrupt is generated when the TMR0 register timer/counter overflows from FFh to 00h. This overflow sets the T0IF bit. The interrupt can be masked by clearing the T0IE bit (INTCON<5>). The T0IF bit (INTCON<2>) must be cleared in software by the Timer0 module Interrupt Service Routine before reenabling this interrupt. The Timer0 interrupt cannot wake the processor from Sleep since the timer is shut-off during Sleep.

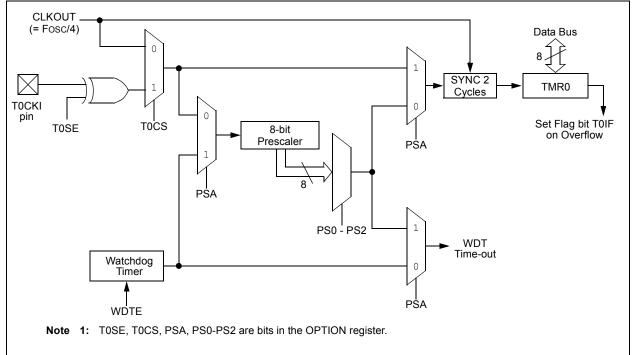

## 6.1 Comparator Operation

A single comparator is shown in Figure 6-1, along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 6-1 represent the uncertainty due to input offsets and response time.

| Note: | To use                                 | CIN+ and  | CIN-    | pins | as ana | alog |

|-------|----------------------------------------|-----------|---------|------|--------|------|

|       | inputs,                                | the appro | opriate | bits | must   | be   |

|       | programmed in the CMCON (19h) register |           |         |      | ster.  |      |

The polarity of the comparator output can be inverted by setting the CINV bit (CMCON<4>). Clearing CINV results in a non-inverted output. A complete table showing the output state versus input conditions and the polarity bit is shown in Table 6-1.

#### TABLE 6-1: OUTPUT STATE VS. INPUT CONDITIONS

| Input Conditions | CINV | COUT |

|------------------|------|------|

| VIN- > VIN+      | 0    | 0    |

| VIN- < VIN+      | 0    | 1    |

| VIN- > VIN+      | 1    | 1    |

| VIN- < VIN+      | 1    | 0    |

#### SINGLE COMPARATOR

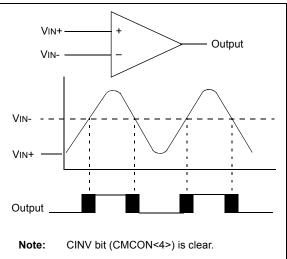

## 7.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE (PIC16F676 ONLY)

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit binary representation of that signal. The PIC16F676 has eight analog inputs, multiplexed into one sample and hold

## FIGURE 7-1: A/D BLOCK DIAGRAM

circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a binary result via successive approximation and stores the result in a 10-bit register. The voltage reference used in the conversion is software selectable to either VDD or a voltage applied by the VREF pin. Figure 7-1 shows the block diagram of the A/D on the PIC16F676.

## 7.1 A/D Configuration and Operation

There are three registers available to control the functionality of the A/D module:

- 1. ADCON0 (Register 7-1)

- 2. ADCON1 (Register 7-2)

- 3. ANSEL (Register 7-3)

#### 7.1.1 ANALOG PORT PINS

The ANS7:ANS0 bits (ANSEL<7:0>) and the TRISA bits control the operation of the A/D port pins. Set the corresponding TRISA bits to set the pin output driver to its high-impedance state. Likewise, set the corresponding ANS bit to disable the digital input buffer.

**Note:** Analog voltages on any pin that is defined as a digital input may cause the input buffer to conduct excess current.

#### 7.1.2 CHANNEL SELECTION

There are eight analog channels on the PIC16F676, AN0 through AN7. The CHS2:CHS0 bits (ADCON0<4:2>) control which channel is connected to the sample and hold circuit.

## 7.1.3 VOLTAGE REFERENCE

There are two options for the voltage reference to the A/D converter: either VDD is used, or an analog voltage applied to VREF is used. The VCFG bit (ADCON0<6>) controls the voltage reference selection. If VCFG is set, then the voltage on the VREF pin is the reference; otherwise, VDD is the reference.

## 7.1.4 CONVERSION CLOCK

The A/D conversion cycle requires 11 TAD. The source of the conversion clock is software selectable via the ADCS bits (ADCON1<6:4>). There are seven possible clock options:

- Fosc/2

- Fosc/4

- Fosc/8

- Fosc/16

- Fosc/32

- Fosc/64

- FRC (dedicated internal oscillator)

For correct conversion, the A/D conversion clock (1/TaD) must be selected to ensure a minimum TaD of 1.6  $\mu s.$  Table 7-1 shows a few TaD calculations for selected frequencies.

#### TABLE 7-1: TAD vs. DEVICE OPERATING FREQUENCIES

| A/D Clock | Source (TAD) | Device Frequency          |                           |                           |                           |  |

|-----------|--------------|---------------------------|---------------------------|---------------------------|---------------------------|--|

| Operation | ADCS2:ADCS0  | 20 MHz                    | 5 MHz                     | 4 MHz                     | 1.25 MHz                  |  |

| 2 Tosc    | 000          | 100 ns <sup>(2)</sup>     | 400 ns <sup>(2)</sup>     | 500 ns <sup>(2)</sup>     | 1.6 μs                    |  |

| 4 Tosc    | 100          | 200 ns <sup>(2)</sup>     | 800 ns <sup>(2)</sup>     | 1.0 μs <sup>(2)</sup>     | 3.2 μs                    |  |

| 8 Tosc    | 001          | 400 ns <sup>(2)</sup>     | 1.6 μs                    | 2.0 μs                    | 6.4 μs                    |  |

| 16 Tosc   | 101          | 800 ns <sup>(2)</sup>     | 3.2 μs                    | 4.0 μs                    | 12.8 μs <sup>(3)</sup>    |  |

| 32 Tosc   | 010          | 1.6 μs                    | 6.4 μs                    | 8.0 μs <sup>(3)</sup>     | 25.6 μs <sup>(3)</sup>    |  |

| 64 Tosc   | 110          | 3.2 μs                    | 12.8 μs <sup>(3)</sup>    | 16.0 μs <sup>(3)</sup>    | 51.2 μs <sup>(3)</sup>    |  |

| A/D RC    | x11          | 2 - 6 μs <sup>(1,4)</sup> |  |

Legend: Shaded cells are outside of recommended range.

Note 1: The A/D RC source has a typical TAD time of 4  $\mu$ s for VDD > 3.0V.

- 2: These values violate the minimum required TAD time.

- **3:** For faster conversion times, the selection of another clock source is recommended.

- 4: When the device frequency is greater than 1 MHz, the A/D RC clock source is only recommended if the conversion will be performed during Sleep.

## 7.1.5 STARTING A CONVERSION

The A/D conversion is initiated by setting the GO/DONE bit (ADCON0<1>). When the conversion is complete, the A/D module:

- Clears the GO/DONE bit

- Sets the ADIF flag (PIR1<6>)

- · Generates an interrupt (if enabled)

If the conversion must be aborted, the GO/DONE bit can be cleared in software. The ADRESH:ADRESL registers will not be updated with the partially complete A/D conversion sample. Instead, the ADRESH:ADRESL registers will retain the value of the previous conversion. After an aborted conversion, a 2 TAD delay is required before another acquisition can be initiated. Following the delay, an input acquisition is automatically started on the selected channel.

**Note:** The GO/DONE bit should not be set in the same instruction that turns on the A/D.

## 7.1.6 CONVERSION OUTPUT

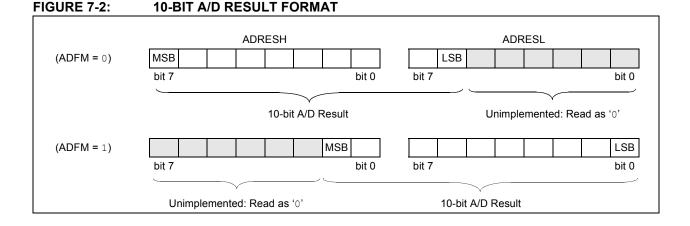

The A/D conversion can be supplied in two formats: left or right shifted. The ADFM bit (ADCON0<7>) controls the output format. Figure 7-2 shows the output formats.

## 9.3 Reset

The PIC16F630/676 differentiates between various kinds of Reset:

- a) Power-on Reset (POR)

- b) WDT Reset during normal operation

- c) WDT Reset during Sleep

- d) MCLR Reset during normal operation

- e) MCLR Reset during Sleep

- f) Brown-out Detect (BOD)

Some registers are not affected in any Reset condition; their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on:

- · Power-on Reset

- MCLR Reset

- WDT Reset

- WDT Reset during Sleep

- Brown-out Detect (BOD)

They are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation.  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are set or cleared differently in different Reset situations as indicated in Table 9-4. These bits are used in software to determine the nature of the Reset. See Table 9-7 for a full description of Reset states of all registers.

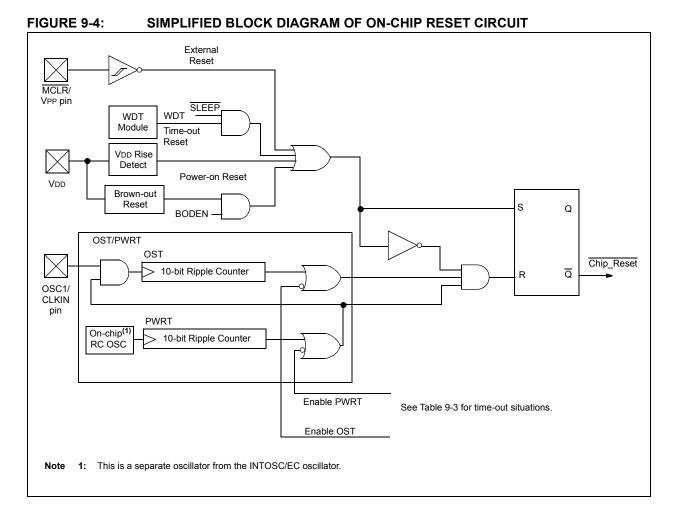

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 9-4.

The  $\overline{\text{MCLR}}$  Reset path has a noise filter to detect and ignore small pulses. See Table 12-4 in Electrical Specifications Section for pulse-width specification.

| Oscillator Configuration | Powe                 | er-up     | Brown-o              | Wake-up   |            |

|--------------------------|----------------------|-----------|----------------------|-----------|------------|

|                          | <b>PWRTE</b> = 0     | PWRTE = 1 | <b>PWRTE</b> = 0     | PWRTE = 1 | from Sleep |

| XT, HS, LP               | Tpwrt +<br>1024•Tosc | 1024•Tosc | Tpwrt +<br>1024•Tosc | 1024•Tosc | 1024•Tosc  |

| RC, EC, INTOSC           | TPWRT                | —         | TPWRT                | —         | —          |

#### TABLE 9-3: TIME-OUT IN VARIOUS SITUATIONS

#### TABLE 9-4: STATUS/PCON BITS AND THEIR SIGNIFICANCE

| POR | BOD | то | PD |                                    |

|-----|-----|----|----|------------------------------------|

| 0   | u   | 1  | 1  | Power-on Reset                     |

| 1   | 0   | 1  | 1  | Brown-out Detect                   |

| u   | u   | 0  | u  | WDT Reset                          |

| u   | u   | 0  | 0  | WDT Wake-up                        |

| u   | u   | u  | u  | MCLR Reset during normal operation |

| u   | u   | 1  | 0  | MCLR Reset during Sleep            |

Legend: u = unchanged, x = unknown

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOD | Value on all<br>other<br>Resets <sup>(1)</sup> |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|----------------------|------------------------------------------------|

| 03h     | STATUS | IRP   | RP1   | RPO   | TO    | PD    | Z     | DC    | С     | 0001 1xxx            | 000q quuu                                      |

| 8Eh     | PCON   | _     |       |       |       | _     | _     | POR   | BOD   | 0x                   | uq                                             |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

Note 1: Other (non Power-up) Resets include MCLR Reset, Brown-out Detect and Watchdog Timer Reset during normal operation.

#### TABLE 9-6: INITIALIZATION CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during Sleep            | 000h                  | 0001 Ouuu          | uu               |

| WDT Reset                          | 000h                  | 0000 uuuu          | uu               |

| WDT Wake-up                        | PC + 1                | սսս0 Օսսս          | uu               |

| Brown-out Detect                   | 000h                  | 0001 luuu          | 10               |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uu               |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and global enable bit GIE is set, the PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

| Address  | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Value on<br>POR, BOD | Value on all<br>other<br>Resets |

|----------|--------|-------|-------|-------|-------|-------|-------|-------|--------|----------------------|---------------------------------|

| 0Bh, 8Bh | INTCON | GIE   | PEIE  | T0IE  | INTE  | RAIE  | T0IF  | INTF  | RAIF   | 0000 0000            | 0000 000u                       |

| 0Ch      | PIR1   | EEIF  | ADIF  | _     | _     | CMIF  | _     | _     | TMR1IF | 00 00                | 00 00                           |

| 8Ch      | PIE1   | EEIE  | ADIE  | _     | _     | CMIE  | _     | _     | TMR1IE | 00 00                | 00 00                           |

#### TABLE 9-8: SUMMARY OF INTERRUPT REGISTERS

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends upon condition. Shaded cells are not used by the Interrupt module.

#### 9.5 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (e.g., W register and STATUS register). This must be implemented in software.

Example 9-2 stores and restores the STATUS and W registers. The user register, W\_TEMP, must be defined in both banks and must be defined at the same offset from the bank base address (i.e., W\_TEMP is defined at 0x20 in Bank 0 and it must also be defined at 0xA0 in Bank 1). The user register, STATUS\_TEMP, must be defined in Bank 0. The Example 9-2:

- · Stores the W register

- Stores the STATUS register in Bank 0

- · Executes the ISR code

- Restores the Status (and bank select bit register)

- · Restores the W register

#### EXAMPLE 9-2: SAVING THE STATUS AND W REGISTERS IN RAM

| MOVWF | W_TEMP       | ;copy W to temp register,<br>could be in either bank        |

|-------|--------------|-------------------------------------------------------------|

| SWAPF | STATUS,W     | ;swap status to be saved into W                             |

| BCF   | STATUS, RPO  | <pre>;change to bank 0 regardless of<br/>current bank</pre> |

| MOVWF | STATUS_TEMP  | ;save status to bank 0 register                             |

| :     |              |                                                             |

| : (   | ISR)         |                                                             |

| :     |              |                                                             |

| SWAPF | STATUS_TEMP, | W;swap STATUS_TEMP register into                            |

|       |              | W, sets bank to original state                              |

| MOVWF | STATUS       | ;move W into STATUS register                                |

| SWAPF | W_TEMP,F     | ;swap W_TEMP                                                |

| SWAPF | W_TEMP,W     | ;swap W_TEMP into W                                         |

## 9.6 Watchdog Timer (WDT)

The Watchdog Timer is a free running, on-chip RC oscillator, which requires no external components. This RC oscillator is separate from the external RC oscillator of the CLKIN pin. That means that the WDT will run, even if the clock on the OSC1 and OSC2 pins of the device has been stopped (for example, by execution of a SLEEP instruction). During normal operation, a WDT time-out generates a device Reset. If the device is in Sleep mode, a WDT time-out causes the device to wake-up and continue with normal operation. The WDT can be permanently disabled by programming the Configuration bit WDTE as clear (Section 9.1 "Configuration Bits").

#### 9.6.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms, (with no prescaler). The time-out periods vary with temperature, VDD and process variations from part to part (see DC specs). If longer time-out periods are desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION register. Thus, time-out periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the prescaler, if assigned to the WDT, and prevent it from timing out and generating a device Reset.

The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

#### 9.6.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worstcase conditions (i.e., VDD = Min., Temperature = Max., Max. WDT prescaler) it may take several seconds before a WDT time-out occurs.

Note 1: T0SE, T0CS, PSA, PS0-PS2 are bits in the OPTION register.

| TABLE 9-9: | SUMMARY OF WATCHDOG TIMER REGISTERS |

|------------|-------------------------------------|

|            |                                     |

| Address | Name         | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOD | Value on all<br>other<br>Resets |

|---------|--------------|-------|--------|-------|-------|-------|-------|-------|-------|----------------------|---------------------------------|

| 81h     | OPTION_REG   | RAPU  | INTEDG | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111            | 1111 1111                       |

| 2007h   | Config. bits | CP    | BODEN  | MCLRE | PWRTE | WDTE  | F0SC2 | F0SC1 | F0SC0 | uuuu uuuu            | uuuu uuuu                       |

Legend: u = Unchanged, shaded cells are not used by the Watchdog Timer.

NOTES:

## 11.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

## 11.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

## 11.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

## 11.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 11.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- · Rich directive set

- Flexible macro language

- · MPLAB IDE compatibility

## 12.5 DC Characteristics: PIC16F630/676-E (Extended)

|       | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le Ta \le +125^{\circ}C$ for extended |        |         |      |       |            |                                   |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------|--------|---------|------|-------|------------|-----------------------------------|--|

| Param | Device Characteristics                                                                                                            | Min    | Typ†    | Max  | Units | Conditions |                                   |  |

| No.   |                                                                                                                                   | NA1111 |         | WIAN |       | VDD        | Note                              |  |

| D020E | Power-down Base Current                                                                                                           | _      | 0.00099 | 3.5  | μΑ    | 2.0        | WDT, BOD, Comparators, VREF,      |  |

|       | (IPD)                                                                                                                             | _      | 0.0012  | 4.0  | μA    | 3.0        | and T1OSC disabled                |  |

|       |                                                                                                                                   | _      | 0.0029  | 8.0  | μA    | 5.0        |                                   |  |

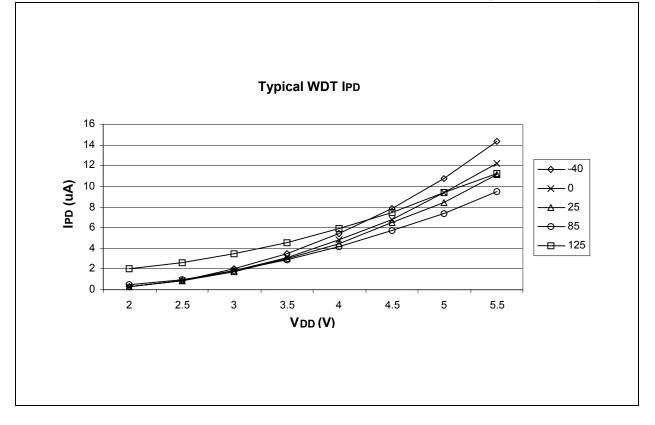

| D021E |                                                                                                                                   | _      | 0.3     | 6.0  | μA    | 2.0        | WDT Current <sup>(1)</sup>        |  |

|       |                                                                                                                                   | —      | 1.8     | 9.0  | μA    | 3.0        |                                   |  |

|       |                                                                                                                                   | _      | 8.4     | 20   | μΑ    | 5.0        | 7                                 |  |

| D022E |                                                                                                                                   | —      | 58      | 70   | μA    | 3.0        | BOD Current <sup>(1)</sup>        |  |

|       |                                                                                                                                   | _      | 109     | 130  | μA    | 5.0        |                                   |  |

| D023E |                                                                                                                                   | —      | 3.3     | 10   | μA    | 2.0        | Comparator Current <sup>(1)</sup> |  |

|       |                                                                                                                                   | _      | 6.1     | 13   | μA    | 3.0        |                                   |  |

|       |                                                                                                                                   | —      | 11.5    | 24   | μA    | 5.0        |                                   |  |

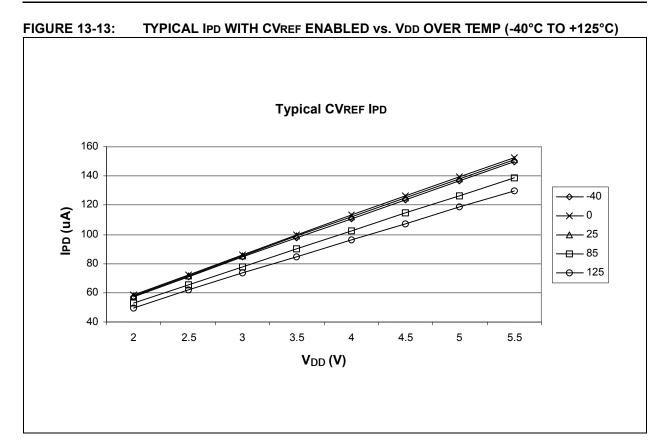

| D024E |                                                                                                                                   | _      | 58      | 70   | μA    | 2.0        | CVREF Current <sup>(1)</sup>      |  |

|       |                                                                                                                                   | _      | 85      | 100  | μA    | 3.0        |                                   |  |

|       |                                                                                                                                   | _      | 138     | 165  | μA    | 5.0        | 7                                 |  |

| D025E |                                                                                                                                   | _      | 4.0     | 10   | μA    | 2.0        | T1 Osc Current <sup>(1)</sup>     |  |

|       |                                                                                                                                   | _      | 4.6     | 12   | μA    | 3.0        |                                   |  |

|       |                                                                                                                                   | —      | 6.0     | 20   | μA    | 5.0        |                                   |  |

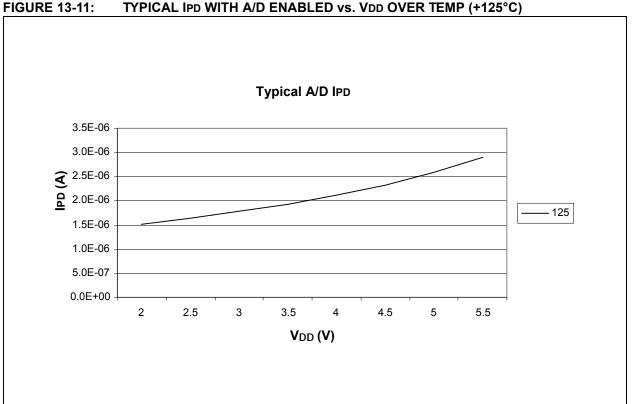

| D026E |                                                                                                                                   | _      | 0.0012  | 6.0  | μA    | 3.0        | A/D Current <sup>(1)</sup>        |  |

|       |                                                                                                                                   | —      | 0.0022  | 8.5  | μA    | 5.0        |                                   |  |

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral ∆ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

NOTES:

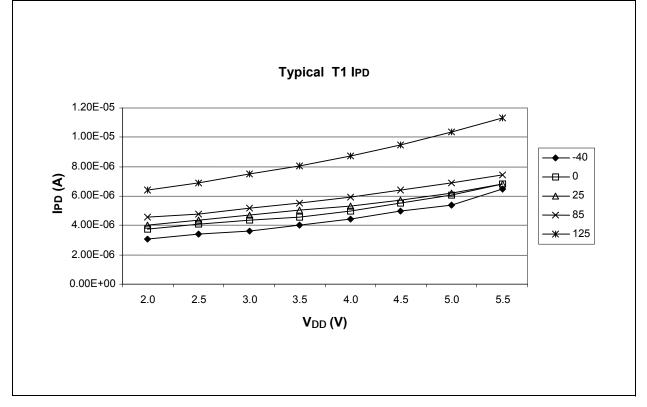

FIGURE 13-14: TYPICAL IPD WITH WDT ENABLED vs. VDD OVER TEMP (-40°C TO +125°C)

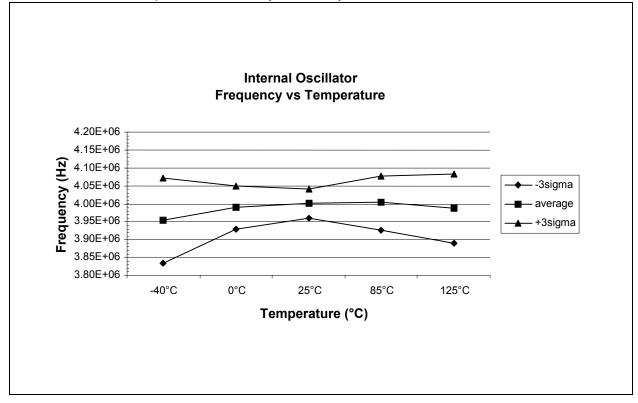

FIGURE 13-15: MAXIMUM AND MINIMUM INTOSC FREQ vs. TEMPERATURE WITH  $0.1\mu$ F AND  $0.01\mu$ F DECOUPLING (VDD = 3.5V)

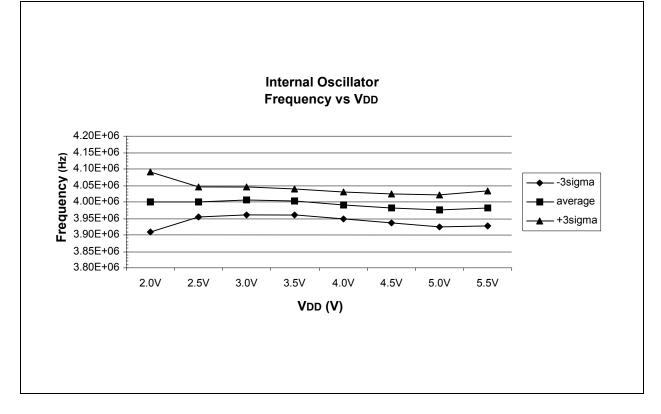

FIGURE 13-16: MAXIMUM AND MINIMUM INTOSC FREQ vs. VDD WITH  $0.1\mu$ F AND  $0.01\mu$ F DECOUPLING (+25°C)

## THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com, click on Customer Change Notification and follow the registration instructions.

## **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

- Development Systems Information Line

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://support.microchip.com

## **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.<br>Device 1 | X /XX XXX<br>       <br>Temperature Package Pattern                                         | Examples:<br>a) PIC16F630 – E/P 301 = Extended Temp., PDIP                                           |

|----------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

|                      | Range                                                                                       | package, 20 MHz, QTP pattern #301<br>b) PIC16F676 – I/SL = Industrial Temp., SOIC<br>package, 20 MHz |

| Device:              | : Standard VDD range<br>T: (Tape and Reel)                                                  |                                                                                                      |

| Temperature Range:   | $I = -40^{\circ}C \text{ to } +85^{\circ}C$<br>$E = -40^{\circ}C \text{ to } +125^{\circ}C$ |                                                                                                      |

| Package:             | P = PDIP<br>SL = SOIC (Gull wing, 3.90 mm body)<br>ST = TSSOP(4.4 mm)                       |                                                                                                      |

| Pattern:             | 3-Digit Pattern Code for QTP (blank otherwise)                                              |                                                                                                      |

\* JW Devices are UV erasable and can be programmed to any device configuration. JW Devices meet the electrical requirement of each oscillator type.