Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

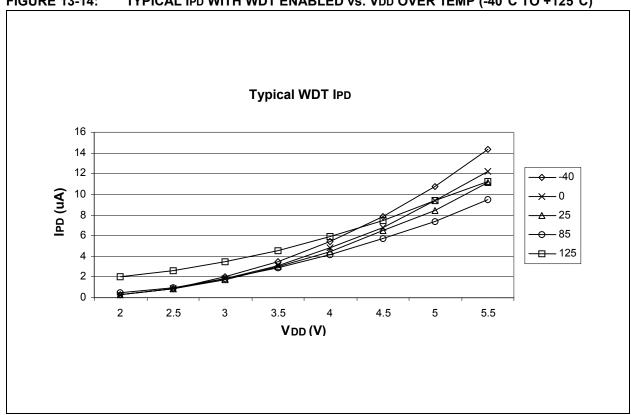

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 64 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                            |

| Supplier Device Package    | 14-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f630t-e-sl |

### 2.2.2.6 PCON Register

The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-on Reset (POR)

- · Brown-out Detect (BOD)

- Watchdog Timer Reset (WDT)

- External MCLR Reset

The PCON Register bits are shown in Register 2-6.

### REGISTER 2-6: PCON — POWER CONTROL REGISTER (ADDRESS: 8Eh)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-x |

|-------|-----|-----|-----|-----|-----|-------|-------|

| _     | _   | _   | _   | _   | _   | POR   | BOD   |

| bit 7 |     |     |     |     |     |       | bit 0 |

bit 7-2 Unimplemented: Read as '0'

bit 1 POR: Power-on Reset Status bit

1 = No Power-on Reset occurred

0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

bit 0 **BOD:** Brown-out Detect Status bit

1 = No Brown-out Detect occurred

0 = A Brown-out Detect occurred (must be set in software after a Brown-out Detect occurs)

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### 2.2.2.7 OSCCAL Register

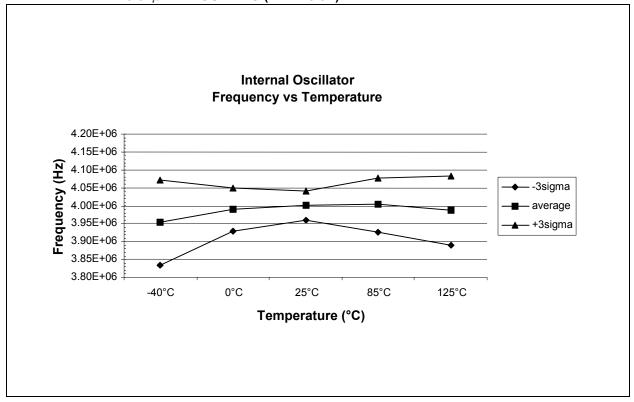

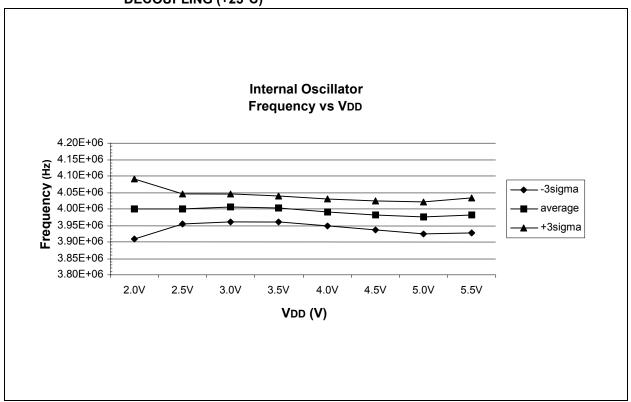

The Oscillator Calibration register (OSCCAL) is used to calibrate the internal 4 MHz oscillator. It contains 6 bits to adjust the frequency up or down to achieve 4 MHz.

The OSCCAL register bits are shown in Register 2-7.

### REGISTER 2-7: OSCCAL—INTERNALOSCILLATOR CALIBRATION REGISTER (ADDRESS: 90h)

| R/W-1 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0 | U-0   |

|-------|-------|-------|-------|-------|-------|-----|-------|

| CAL5  | CAL4  | CAL3  | CAL2  | CAL1  | CAL0  | _   | _     |

| bit 7 |       |       |       |       |       |     | bit 0 |

bit 7-2 CAL5:CAL0: 6-bit Signed Oscillator Calibration bits

111111 = Maximum frequency 100000 = Center frequency 000000 = Minimum frequency

bit 1-0 Unimplemented: Read as '0'

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### REGISTER 3-5: PORTC — PORTC REGISTER (ADDRESS: 07h)

| U-0   | U-0 | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|-------|-----|-------|-------|-------|-------|-------|-------|

| _     | _   | RC5   | RC4   | RC3   | RC2   | RC1   | RC0   |

| bit 7 |     |       |       |       |       |       | bit 0 |

bit 7-6: **Unimplemented**: Read as '0'

bit 5-0: **PORTC<5:0>**: General Purpose I/O pin bits

1 = Port pin is >VIH 0 = Port pin is <VIL

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### REGISTER 3-6: TRISC — PORTC TRI-STATE REGISTER (ADDRESS: 87h)

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | _   | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

bit 7-6: **Unimplemented**: Read as '0'

bit 5-0: TRISC<5:0>: PORTC Tri-State Control bits

1 = PORTC pin configured as an input (tri-stated)

0 = PORTC pin configured as an output

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### TABLE 3-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Address | Name                 | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOD | Value on all<br>other<br>Resets |

|---------|----------------------|-------|-------|--------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| 07h     | PORTC                | _     | _     | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | xx xxxx              | uu uuuu                         |

| 87h     | TRISC                | _     | _     | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 11 1111              | 11 1111                         |

| 91h     | ANSEL <sup>(1)</sup> | ANS7  | ANS6  | ANS5   | ANS4   | ANS3   | ANS2   | ANS1   | ANS0   | 1111 1111            | 1111 1111                       |

Note 1: PIC16F676 only.

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTC.

TABLE 7-1: TAD vs. DEVICE OPERATING FREQUENCIES

| A/D Clock | Source (TAD) | Device Frequency          |                           |                           |                           |  |  |  |  |

|-----------|--------------|---------------------------|---------------------------|---------------------------|---------------------------|--|--|--|--|

| Operation | ADCS2:ADCS0  | 20 MHz                    | 5 MHz                     | 4 MHz                     | 1.25 MHz                  |  |  |  |  |

| 2 Tosc    | 000          | 100 ns <sup>(2)</sup>     | 400 ns <sup>(2)</sup>     | 500 ns <sup>(2)</sup>     | 1.6 μs                    |  |  |  |  |

| 4 Tosc    | 100          | 200 ns <sup>(2)</sup>     | 800 ns <sup>(2)</sup>     | 1.0 μs <sup>(2)</sup>     | 3.2 μs                    |  |  |  |  |

| 8 Tosc    | 001          | 400 ns <sup>(2)</sup>     | 1.6 μs                    | 2.0 μs                    | 6.4 μs                    |  |  |  |  |

| 16 Tosc   | 101          | 800 ns <sup>(2)</sup>     | 3.2 μs                    | 4.0 μs                    | 12.8 μs <sup>(3)</sup>    |  |  |  |  |

| 32 Tosc   | 010          | 1.6 μs                    | 6.4 μs                    | 8.0 μs <sup>(3)</sup>     | 25.6 μs <sup>(3)</sup>    |  |  |  |  |

| 64 Tosc   | 110          | 3.2 μs                    | 12.8 μs <sup>(3)</sup>    | 16.0 μs <sup>(3)</sup>    | 51.2 μs <sup>(3)</sup>    |  |  |  |  |

| A/D RC    | x11          | 2 - 6 μs <sup>(1,4)</sup> |  |  |  |  |

Legend: Shaded cells are outside of recommended range.

- **Note 1:** The A/D RC source has a typical TAD time of 4  $\mu$ s for VDD > 3.0V.

- 2: These values violate the minimum required TAD time.

- 3: For faster conversion times, the selection of another clock source is recommended.

- **4:** When the device frequency is greater than 1 MHz, the A/D RC clock source is only recommended if the conversion will be performed during Sleep.

### 7.1.5 STARTING A CONVERSION

The A/D conversion is initiated by setting the GO/DONE bit (ADCON0<1>). When the conversion is complete, the A/D module:

- Clears the GO/DONE bit

- Sets the ADIF flag (PIR1<6>)

- · Generates an interrupt (if enabled)

If the conversion must be aborted, the GO/DONE bit can be cleared in software. The ADRESH:ADRESL registers will not be updated with the partially complete A/D conversion sample. Instead, the ADRESH:ADRESL registers will retain the value of the

previous conversion. After an aborted conversion, a 2 TAD delay is required before another acquisition can be initiated. Following the delay, an input acquisition is automatically started on the selected channel.

**Note:** The GO/DONE bit should not be set in the same instruction that turns on the A/D.

### 7.1.6 CONVERSION OUTPUT

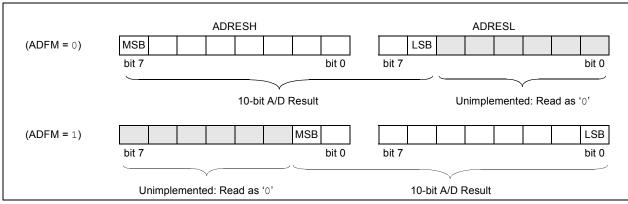

The A/D conversion can be supplied in two formats: left or right shifted. The ADFM bit (ADCON0<7>) controls the output format. Figure 7-2 shows the output formats.

FIGURE 7-2: 10-BIT A/D RESULT FORMAT

### 7.3 A/D Operation During Sleep

The A/D converter module can operate during Sleep. This requires the A/D clock source to be set to the internal oscillator. When the RC clock source is selected, the A/D waits one instruction before starting the conversion. This allows the SLEEP instruction to be executed, thus eliminating much of the switching noise from the conversion. When the conversion is complete, the GO/DONE bit is cleared, and the result is loaded into the ADRESH:ADRESL registers. If the A/D interrupt is enabled, the device awakens from Sleep. If the A/D interrupt is not enabled, the A/D module is turned off, although the ADON bit remains set.

When the A/D clock source is something other than RC, a SLEEP instruction causes the present conversion to be aborted, and the A/D module is turned off. The ADON bit remains set.

### 7.4 Effects of Reset

A device Reset forces all registers to their Reset state. Thus, the A/D module is turned off and any pending conversion is aborted. The ADRESH:ADRESL registers are unchanged.

TABLE 7-2: SUMMARY OF A/D REGISTERS

| Address  | Name   | Bit 7      | Bit 6          | Bit 5       | Bit 4       | Bit 3         | Bit 2         | Bit 1         | Bit 0     | Value on POR, BOD | Value on<br>all other<br>Resets |

|----------|--------|------------|----------------|-------------|-------------|---------------|---------------|---------------|-----------|-------------------|---------------------------------|

| 05h      | PORTA  | _          | _              | PORTA5      | PORTA4      | PORTA3        | PORTA2        | PORTA1        | PORTA0    | xx xxxx           | uu uuuu                         |

| 07h      | PORTC  | _          | _              | PORTC5      | PORTC4      | PORTC3        | PORTC2        | PORTC1        | PORTC0    | xx xxxx           | uu uuuu                         |

| 0Bh, 8Bh | INTCON | GIE        | PEIE           | T0IE        | INTE        | RAIE          | T0IF          | INTF          | RAIF      | 0000 0000         | 0000 000u                       |

| 0Ch      | PIR1   | EEIF       | ADIF           | _           | _           | CMIF          | _             | _             | TMR1IF    | 00 00             | 00 00                           |

| 1Eh      | ADRESH | Most Signi | ficant 8 bits  | of the Left | Shifted A/D | result or 2 l | bits of the R | Right Shifted | Result    | xxxx xxxx         | uuuu uuuu                       |

| 1Fh      | ADCON0 | ADFM       | VCFG           | _           | CHS2        | CHS1          | CHS0          | GO            | ADON      | 00-0 0000         | 00-0 0000                       |

| 85h      | TRISA  | _          | _              | TRISA5      | TRISA4      | TRISA3        | TRISA2        | TRISA1        | TRISA0    | 11 1111           | 11 1111                         |

| 87h      | TRISC  | _          | _              | TRISC5      | TRISC4      | TRISC3        | TRISC2        | TRISC1        | TRISC0    | 11 1111           | 11 1111                         |

| 8Ch      | PIE1   | EEIE       | ADIE           | _           | _           | CMIE          | _             | _             | TMR1IE    | 00 00             | 00 00                           |

| 91h      | ANSEL  | ANS7       | ANS6           | ANS5        | ANS4        | ANS3          | ANS2          | ANS1          | ANS0      | 1111 1111         | 1111 1111                       |

| 9Eh      | ADRESL | Least Sign | ificant 2 bits | of the Left | Shifted A/D | Result or 8   | B bits of the | Right Shifte  | ed Result | xxxx xxxx         | uuuu uuuu                       |

| 9Fh      | ADCON1 | _          | ADCS2          | ADCS1       | ADCS0       | _             | _             | _             | _         | -000              | -000                            |

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for A/D converter module.

# 8.7 DATA EEPROM OPERATION DURING CODE-PROTECT

Data memory can be code-protected by programming the CPD bit to '0'.

When the data memory is code-protected, the CPU is able to read and write data to the data EEPROM. It is recommended to code-protect the program memory when code protecting data memory. This prevents anyone from programming zeroes over the existing code (which will execute as NOPs) to reach an added routine, programmed in unused program memory, which outputs the contents of data memory. Programming unused locations to '0' will also help prevent data memory code protection from becoming breached.

TABLE 8-1: REGISTERS/BITS ASSOCIATED WITH DATA EEPROM

| Address | Name                  | Bit 7  | Bit 6               | Bit 5                   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Value on<br>POR, BOD | Value on all<br>other<br>Resets |

|---------|-----------------------|--------|---------------------|-------------------------|-------|-------|-------|-------|--------|----------------------|---------------------------------|

| 0Ch     | PIR1                  | EEIF   | ADIF                | _                       | _     | CMIF  |       | _     | TMR1IF | 00 00                | 00 00                           |

| 9Ah     | EEDATA                | EEPROM | EPROM Data Register |                         |       |       |       |       |        | 0000 0000            | 0000 0000                       |

| 9Bh     | EEADR                 | _      | EEPROM              | EEPROM Address Register |       |       |       |       |        | -000 0000            | -000 0000                       |

| 9Ch     | EECON1                | _      | _                   | _                       | _     | WRERR | WREN  | WR    | RD     | x000                 | q000                            |

| 9Dh     | EECON2 <sup>(1)</sup> | EEPROM | 1 Control F         | Register 2              |       |       |       |       |        |                      |                                 |

$\begin{tabular}{ll} \textbf{Legend:} & $x = $ unknown, $u = $ unchanged, $- = $ unimplemented read as `0', $q = $ value depends upon condition. \\ & Shaded cells are not used by the data EEPROM module. \\ \end{tabular}$

Note 1: EECON2 is not a physical register.

### 9.4 Interrupts

The PIC16F630/676 has 7 sources of interrupt:

- · External Interrupt RA2/INT

- · TMR0 Overflow Interrupt

- PORTA Change Interrupts

- Comparator Interrupt

- A/D Interrupt (PIC16F676 only)

- · TMR1 Overflow Interrupt

- · EEPROM Data Write Interrupt

The Interrupt Control register (INTCON) and Peripheral Interrupt register (PIR) record individual interrupt requests in flag bits. The INTCON register also has individual and Global Interrupt Enable bits.

A Global Interrupt Enable bit, GIE (INTCON<7>) enables (if set) all unmasked interrupts, or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in INTCON register and PIE register. GIE is cleared on Reset.

The return from interrupt instruction, RETFIE, exits interrupt routine, as well as sets the GIE bit, which reenables unmasked interrupts.

The following interrupt flags are contained in the INTCON register:

- · INT pin interrupt

- · PORTA change interrupt

- · TMR0 overflow interrupt

The peripheral interrupt flags are contained in the special register PIR1. The corresponding interrupt enable bit is contained in Special Register PIE1.

The following interrupt flags are contained in the PIR register:

- · EEPROM data write interrupt

- A/D interrupt

- · Comparator interrupt

- Timer1 overflow interrupt

When an interrupt is serviced:

- The GIE is cleared to disable any further interrupt

- · The return address is pushed onto the stack

- · The PC is loaded with 0004h

Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid RA2/INT recursive interrupts.

For external interrupt events, such as the INT pin, or PORTA change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends upon when the interrupt event occurs (see Figure 9-11). The latency is the same for one or two-cycle instructions. Once in the Interrupt Service Routine, the source(s) of the interrupt can be

determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests.

- Note 1: Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit or the GIE bit.

- 2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The interrupts which were ignored are still pending to be serviced when the GIE bit is set again.

### 9.8 Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

Note: The entire data EEPROM and Flash program memory will be erased when the code protection is turned off. The INTOSC calibration data is also erased. See PIC16F630/676 Programming Specification for more information.

### 9.9 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution but are readable and writable during Program/Verify. Only the Least Significant 7 bits of the ID locations are used.

### 9.10 In-Circuit Serial Programming

The PIC16F630/676 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for:

- power

- · ground

- · programming voltage

This allows customers to manufacture boards with unprogrammed devices and then program the micro-controller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

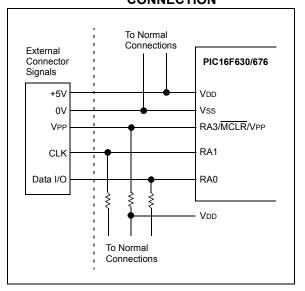

The device is placed into a Program/Verify mode by holding the RA0 and RA1 pins low, while raising the MCLR (VPP) pin from VIL to VIHH (see Programming Specification). RA0 becomes the programming data and RA1 becomes the programming clock. Both RA0 and RA1 are Schmitt Trigger inputs in this mode.

After Reset, to place the device into Programming/Verify mode, the program counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14 bits of program data are then supplied to or from the device, depending on whether the command was a load or a read. For complete details of serial programming, please refer to the PIC16F630/676 Programming Specification.

A typical In-Circuit Serial Programming connection is shown in Figure 9-14.

FIGURE 9-14: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

### 9.11 In-Circuit Debugger

Since in-circuit debugging requires the loss of clock, data and  $\overline{MCLR}$  pins, MPLAB® ICD 2 development with an 14-pin device is not practical. A special 20-pin PIC16F676-ICD device is used with MPLAB ICD 2 to provide separate clock, data and  $\overline{MCLR}$  pins and frees all normally available pins to the user.

This special ICD device is mounted on the top of the header and its signals are routed to the MPLAB ICD 2 connector. On the bottom of the header is an 14-pin socket that plugs into the user's target via the 14-pin stand-off connector.

When the  $\overline{\text{ICD}}$  pin on the PIC16F676-ICD device is held low, the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB ICD 2. When the microcontroller has this feature enabled, some of the resources are not available for general use. Table 9-10 shows which features are consumed by the background debugger:

TABLE 9-10: DEBUGGER RESOURCES

| I/O pins       | ICDCLK, ICDDATA                  |

|----------------|----------------------------------|

| Stack          | 1 level                          |

| Program Memory | Address 0h must be NOP 300h-3FEh |

For more information, see 14-Pin MPLAB ICD 2 Header Information Sheet (DS51292) available on Microchip's web site (www.microchip.com).

## 10.2 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                 |

|------------------|-------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [/abe/] ADDLW k                                                                                                   |

| Operands:        | $0 \leq k \leq 255$                                                                                               |

| Operation:       | $(W) + k \rightarrow (W)$                                                                                         |

| Status Affected: | C, DC, Z                                                                                                          |

| Description:     | The contents of the W register are added to the eight-bit literal 'k' and the result is placed in the W register. |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [label] BCF f,b                                                     |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| ADDWF            | Add W and f                                                                                                                                                        |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [/abe/] ADDWF f,d                                                                                                                                                  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                 |  |  |  |  |  |  |

| Operation:       | $(W) + (f) \rightarrow (destination)$                                                                                                                              |  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                           |  |  |  |  |  |  |

| Description:     | Add the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |  |  |  |  |  |  |

| BSF              | Bit Set f                            |

|------------------|--------------------------------------|

| Syntax:          | [/abe/] BSF f,b                      |

| Operands:        | $0 \le f \le 127$<br>$0 \le b \le 7$ |

| Operation:       | $1 \rightarrow (f < b >)$            |

| Status Affected: | None                                 |

| Description:     | Bit 'b' in register 'f' is set.      |

|                  |                                      |

| ANDLW            | AND Literal with W                                                                                            |

|------------------|---------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ANDLW k                                                                                               |

| Operands:        | $0 \leq k \leq 255$                                                                                           |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                               |

| Status Affected: | Z                                                                                                             |

| Description:     | The contents of W register are AND'ed with the eight-bit literal 'k'. The result is placed in the W register. |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] BTFSS f,b                                                                                                                                                                                 |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                                |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                              |

| Description:     | If bit 'b' in register 'f' is '0', the next instruction is executed.  If bit 'b' is '1', then the next instruction is discarded and a NOP is executed instead, making this a 2-cycle instruction. |

| ANDWF            | AND W with f                                                                                                                                       |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] ANDWF f,d                                                                                                                                  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                 |  |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                          |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                  |  |  |  |  |  |

| Description:     | AND the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |  |  |  |  |  |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] BTFSC f,b                                                                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                             |

| Operation:       | skip if $(f < b >) = 0$                                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                            |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.  If bit 'b', in register 'f', is '0', the next instruction is discarded, and a NOP is executed instead, making this a 2-cycle instruction. |

# 12.7 DC Characteristics: PIC16F630/676-I (Industrial), PIC16F630/676-E (Extended) (Cont.)

| DC CHARACTERISTICS |       |                                                                  |      | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |     |       |                                                                  |  |  |

|--------------------|-------|------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------------------------------------------------------------------|--|--|

| Param<br>No.       | Sym   | Characteristic                                                   | Min  | Typ† Max U                                                                                                                                                                                                                         |     | Units | Conditions                                                       |  |  |

|                    |       | Capacitive Loading Specs on Output Pins                          |      |                                                                                                                                                                                                                                    |     |       |                                                                  |  |  |

| D100               | Cosc2 | OSC2 pin                                                         | _    | _                                                                                                                                                                                                                                  | 15* | pF    | In XT, HS and LP modes when external clock is used to drive OSC1 |  |  |

| D101               | Сю    | All I/O pins                                                     | _    | _                                                                                                                                                                                                                                  | 50* | pF    |                                                                  |  |  |

|                    |       | Data EEPROM Memory                                               |      |                                                                                                                                                                                                                                    |     |       |                                                                  |  |  |

| D120               | ED    | Byte Endurance                                                   | 100K | 1M                                                                                                                                                                                                                                 | _   | E/W   | -40°C ≤ TA ≤ +85°C                                               |  |  |

| D120A              | ED    | Byte Endurance                                                   | 10K  | 100K                                                                                                                                                                                                                               | _   | E/W   | +85°C ≤ TA ≤ +125°C                                              |  |  |

| D121               | VDRW  | VDD for Read/Write                                               | VMIN | _                                                                                                                                                                                                                                  | 5.5 | V     | Using EECON to read/write VMIN = Minimum operating voltage       |  |  |

| D122               | TDEW  | Erase/Write cycle time                                           |      | 5                                                                                                                                                                                                                                  | 6   | ms    |                                                                  |  |  |

| D123               | TRETD | Characteristic Retention                                         | 40   | _                                                                                                                                                                                                                                  | _   | Year  | Provided no other specifications are violated                    |  |  |

| D124               | TREF  | Number of Total Erase/Write Cycles before Refresh <sup>(1)</sup> | 1M   | 10M                                                                                                                                                                                                                                | _   | E/W   | $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$      |  |  |

|                    |       | Program Flash Memory                                             |      |                                                                                                                                                                                                                                    |     |       |                                                                  |  |  |

| D130               | EP    | Cell Endurance                                                   | 10K  | 100K                                                                                                                                                                                                                               | _   | E/W   | $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$      |  |  |

| D130A              | ED    | Cell Endurance                                                   | 1K   | 10K                                                                                                                                                                                                                                | _   | E/W   | +85°C ≤ TA ≤ +125°C                                              |  |  |

| D131               | VPR   | VDD for Read                                                     | VMIN | _                                                                                                                                                                                                                                  | 5.5 | V     | Vмін = Minimum operating voltage                                 |  |  |

| D132               | VPEW  | VDD for Erase/Write                                              | 4.5  | _                                                                                                                                                                                                                                  | 5.5 | V     |                                                                  |  |  |

| D133               | TPEW  | Erase/Write cycle time                                           | _    | 2                                                                                                                                                                                                                                  | 2.5 | ms    |                                                                  |  |  |

| D134               | TRETD | Characteristic Retention                                         | 40   |                                                                                                                                                                                                                                    |     | Year  | Provided no other specifications are violated                    |  |  |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: See Section 8.5.1 for additional information.

<sup>†</sup> Data in 'Typ' column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

### 12.8 TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

io

Т

| F      | Frequency                             | Т   | Time     |

|--------|---------------------------------------|-----|----------|

| Lowerd | case letters (pp) and their meanings: |     |          |

| рр     |                                       |     |          |

| СС     | CCP1                                  | osc | OSC1     |

| ck     | CLKOUT                                | rd  | RD       |

| cs     | <del>CS</del>                         | rw  | RD or WR |

| di     | SDI                                   | sc  | SCK      |

| do     | SDO                                   | SS  | SS       |

| dt     | Data in                               | t0  | T0CKI    |

Uppercase letters and their meanings:

I/O port

MCLR

| S |                          |   |                |

|---|--------------------------|---|----------------|

| F | Fall                     | Р | Period         |

| Н | High                     | R | Rise           |

| 1 | Invalid (High-impedance) | V | Valid          |

| L | Low                      | Z | High-impedance |

t1

wr

T1CKI

$\overline{\text{WR}}$

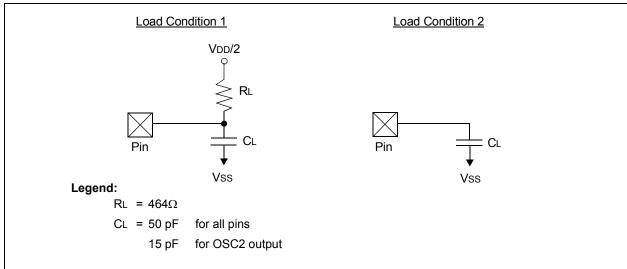

### FIGURE 12-4: LOAD CONDITIONS

TABLE 12-2: PRECISION INTERNAL OSCILLATOR PARAMETERS

| Param<br>No. | Sym   | Characteristic          | Freq<br>Tolerance | Min  | Typ† | Max  | Units | Conditions                                                                |

|--------------|-------|-------------------------|-------------------|------|------|------|-------|---------------------------------------------------------------------------|

| F10          | Fosc  | Internal Calibrated     | ±1                | 3.96 | 4.00 | 4.04 | MHz   | VDD = 3.5V, 25°C                                                          |

|              |       | INTOSC Frequency        | ±2                | 3.92 | 4.00 | 4.08 | MHz   | $2.5V \leq V_{DD} \leq 5.5V$                                              |

|              |       |                         |                   |      |      |      |       | $0^{\circ}C \leq TA \leq +85^{\circ}C$                                    |

|              |       |                         | ±5                | 3.80 | 4.00 | 4.20 | MHz   | $2.0V \leq V_{DD} \leq 5.5V$                                              |

|              |       |                         |                   |      |      |      |       | $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C} \text{ (IND)}$ |

|              |       |                         |                   |      |      |      |       | $-40^{\circ}$ C $\leq$ TA $\leq$ +125 $^{\circ}$ C (EXT)                  |

| F14          | Tiosc | Oscillator Wake-up from |                   | _    | 6    | 8    | μS    | $VDD = 2.0V, -40^{\circ}C \text{ to } +85^{\circ}C$                       |

|              | ST    | Sleep start-up time*    | _                 | _    | 4    | 6    | μS    | $VDD = 3.0V, -40^{\circ}C \text{ to } +85^{\circ}C$                       |

|              |       |                         | _                 | _    | 3    | 5    | μS    | $V_{DD} = 5.0V, -40^{\circ}C \text{ to } +85^{\circ}C$                    |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

TABLE 12-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER, AND BROWN-OUT DETECT REQUIREMENTS

| Param<br>No. | Sym   | Characteristic                                           | Min        | Typ†      | Max         | Units    | Conditions                                                   |

|--------------|-------|----------------------------------------------------------|------------|-----------|-------------|----------|--------------------------------------------------------------|

| 30           | TMCL  | MCLR Pulse Width (low)                                   | 2<br>11    | —<br>18   | _<br>24     | μs<br>ms | V <sub>DD</sub> = 5V, -40°C to +85°C<br>Extended temperature |

| 31           | TWDT  | Watchdog Timer Time-out<br>Period<br>(No Prescaler)      | 10<br>10   | 17<br>17  | 25<br>30    | ms<br>ms | VDD = 5V, -40°C to +85°C<br>Extended temperature             |

| 32           | Tost  | Oscillation Start-up Timer<br>Period                     | _          | 1024Tosc  | _           | _        | Tosc = OSC1 period                                           |

| 33*          | TPWRT | Power-up Timer Period                                    | 28*<br>TBD | 72<br>TBD | 132*<br>TBD | ms<br>ms | V <sub>DD</sub> = 5V, -40°C to +85°C<br>Extended Temperature |

| 34           | Tioz  | I/O High-impedance from MCLR Low or Watchdog Timer Reset | _          | _         | 2.0         | μS       |                                                              |

|              | BVDD  | Brown-out Detect Voltage                                 | 2.025      | _         | 2.175       | V        |                                                              |

|              |       | Brown-out Hysteresis                                     | TBD        | _         |             | _        |                                                              |

| 35           | TBOD  | Brown-out Detect Pulse Width                             | 100*       | _         | _           | μS       | VDD ≤ BVDD (D005)                                            |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

FIGURE 13-15: MAXIMUM AND MINIMUM INTOSC FREQ vs. TEMPERATURE WITH  $0.1\mu F$  AND  $0.01\mu F$  DECOUPLING (VDD = 3.5V)

FIGURE 13-16: MAXIMUM AND MINIMUM INTOSC FREQ vs. VDD WITH  $0.1\mu F$  AND  $0.01\mu F$  DECOUPLING (+25°C)

NOTES:

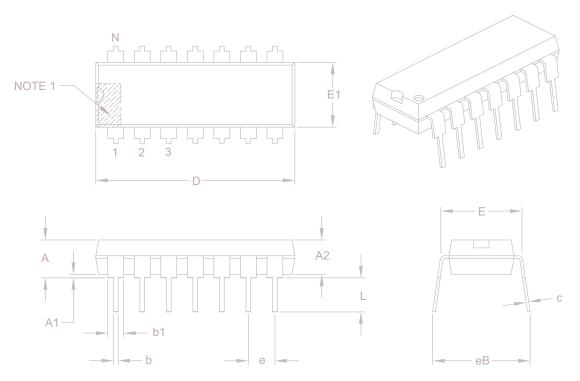

### 14.2 Package Details

The following sections give the technical details of the packages.

### 14-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**e:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | INCHES   |                |          |      |

|----------------------------|----------|----------------|----------|------|

| Dimension                  | n Limits | MIN            | NOM      | MAX  |

| Number of Pins             | N        |                | 14       |      |

| Pitch                      | е        |                | .100 BSC |      |

| Top to Seating Plane       | Α        | _              | _        | .210 |

| Molded Package Thickness   | A2       | .115           | .130     | .195 |

| Base to Seating Plane      | A1       | .015           | -        | -    |

| Shoulder to Shoulder Width | Е        | .290           | .310     | .325 |

| Molded Package Width       | E1       | .240 .250 .280 |          |      |

| Overall Length             | D        | .735           | .750     | .775 |

| Tip to Seating Plane       | L        | .115           | .130     | .150 |

| Lead Thickness             | С        | .008           | .010     | .015 |

| Upper Lead Width           | b1       | .045           | .060     | .070 |

| Lower Lead Width           | b        | .014           | .018     | .022 |

| Overall Row Spacing §      | eВ       | _              | _        | .430 |

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located with the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-005B

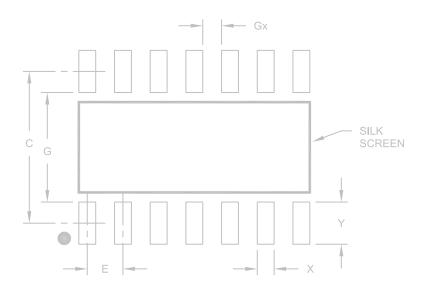

14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

| Units                 |    | MILLIMETERS |      |      |

|-----------------------|----|-------------|------|------|

| Dimension Limits      |    | MIN         | NOM  | MAX  |

| Contact Pitch         | Е  | 1.27 BSC    |      |      |

| Contact Pad Spacing   | С  |             | 5.40 |      |

| Contact Pad Width     | X  |             |      | 0.60 |

| Contact Pad Length    | Y  |             |      | 1.50 |

| Distance Between Pads | Gx | 0.67        |      |      |

| Distance Between Pads | G  | 3.90        |      |      |

### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2065A

| IORLW77                                              | Power-on Reset (POR)60               |

|------------------------------------------------------|--------------------------------------|

| IORWF77                                              | Power-up Timer (PWRT)60              |

| MOVF78                                               | Prescaler                            |

| MOVLW78                                              |                                      |

| MOVWF78                                              | Program Memory Organization          |

| NOP78                                                | 3, =                                 |

| RETFIE78                                             | R                                    |

| RETLW78                                              |                                      |

| RETURN79                                             | Reader Response                      |

| RLF79                                                | READ-MODIFY-WRITE OPERATIONS         |

| RRF79                                                | Registers                            |

| SLEEP79                                              | ADCONO (A/D Control)                 |

| SUBLW79                                              | ADCON1 4                             |

| SUBWF79                                              | CMCON (Comparator Control)           |

| SWAPF80                                              | CONFIG (Configuration Word)          |

| XORLW80                                              | FEADR (FEPROM Address) 5:            |

| XORWF80                                              | FECON1 (FERROM Control) 5            |

| Summary Table74                                      | FEDAT (FEPROM Data) 5                |

| Internal 4 MHz Oscillator58                          | INTCON (Interrupt Control)           |

| Internal Sampling Switch (Rss) Impedance49           | IOCA (Interrupt-on-Change POPTA)     |

| Internet Address129                                  | Mans                                 |

| Interrupts65                                         | DIC16E630 10                         |

| A/D Converter67                                      | DIC16F676 10                         |

| Comparator67                                         | OPTION REG (Ontion) 14 33            |

| Context Saving68                                     | OSCCAL (Oscillator Calibration) 18   |

| PORTA67                                              | PCON (Power Control)                 |

| RA2/INT67                                            | PIE1 (Peripheral Interrupt Enable 1) |

| Summary of Registers68                               | PIP1 (Peripheral Interrupt 1)        |

| TMR067                                               | PORTC                                |

| M                                                    | STATUS1;                             |

| MCLR60                                               |                                      |

| Memory Organization                                  | TRISC29                              |

| Data EEPROM Memory51                                 |                                      |

| Microchip Internet Web Site129                       |                                      |

| Migrating from other PICmicro Devices124             |                                      |

| MPLAB ASM30 Assembler, Linker, Librarian82           |                                      |

| MPLAB Integrated Development Environment Software 81 | •                                    |

| MPLAB PM3 Device Programmer84                        | •                                    |

| MPLAB REAL ICE In-Circuit Emulator System83          | Software Simulator (MPLAB SIM)       |

| MPLINK Object Linker/MPLIB Object Librarian82        | Special Features of the CPU          |

| 0                                                    | Special Function Registers           |

| OPCODE Field Descriptions73                          | T                                    |

| Oscillator Configurations57                          | , rime-out Sequence                  |

| Oscillator Start-up Timer (OST)60                    | Timeru3                              |

|                                                      | Associated Registers33               |

| P                                                    | External Clock                       |

| Packaging117                                         | Interrupt                            |

| Details118                                           | •                                    |

| Marking117                                           |                                      |

| PCL and PCLATH19                                     |                                      |

| Computed GOTO19                                      |                                      |

| Stack19                                              |                                      |

| Pinout Descriptions                                  | Reading and Writing3                 |

| PIC16F6308                                           |                                      |

| PIC16F6768                                           |                                      |

| PORTA                                                | Operation During SLEEP               |

| Additional Pin Functions21                           |                                      |

| Interrupt-on-Change22                                |                                      |

| Weak Pull-up21                                       |                                      |

| Associated Registers                                 |                                      |

| Pin Descriptions and Diagrams24                      |                                      |

| PORTA and TRISIO Registers21                         |                                      |

| PORTC28                                              |                                      |

| Associated Registers                                 |                                      |

| Power Control/Status Register (PCON)                 |                                      |

|                                                      |                                      |

NOTES:

## WORLDWIDE SALES AND SERVICE

### **AMERICAS**

Corporate Office 2355 West Chandler Blvd.

Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://support.microchip.com

Web Address: www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca. IL

Tel: 630-285-0071 Fax: 630-285-0075

Cleveland

Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

Dallas

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit

Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo

Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara

Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto

Mississauga, Ontario, Canada

Tel: 905-673-0699 Fax: 905-673-6509

### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2401-1200

Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing

Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Hong Kong SAR Tel: 852-2401-1200

Fax: 852-2401-3431

China - Nanjing

Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai

Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang

Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen

Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

China - Wuhan

Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xian

Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

China - Xiamen

Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040

Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore

Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi

Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune

Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

Japan - Yokohama

Tel: 81-45-471- 6166 Fax: 81-45-471-6122

Korea - Daegu

Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul

Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur

Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang

Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila

Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu

Tel: 886-3-6578-300 Fax: 886-3-6578-370

Taiwan - Kaohsiung Tel: 886-7-536-4818

Fax: 886-7-536-4803

Taiwan - Taipei

Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351

Fax: 66-2-694-1350

#### **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen

Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Munich

Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen

Tel: 31-416-690399 Fax: 31-416-690340

Spain - Madrid

Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

01/05/10