Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product StatusActiveCore ProcessorPICCore Size8-Bit                                    |

|----------------------------------------------------------------------------------------|

|                                                                                        |

| Core Size 8-Bit                                                                        |

|                                                                                        |

| Speed 20MHz                                                                            |

| Connectivity -                                                                         |

| Peripherals Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O 12                                                                       |

| Program Memory Size 1.75KB (1K x 14)                                                   |

| Program Memory Type FLASH                                                              |

| EEPROM Size128 x 8                                                                     |

| RAM Size64 x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) 2V ~ 5.5V                                                   |

| Data Converters -                                                                      |

| Oscillator Type Internal                                                               |

| Operating Temperature -40°C ~ 125°C (TA)                                               |

| Mounting Type Surface Mount                                                            |

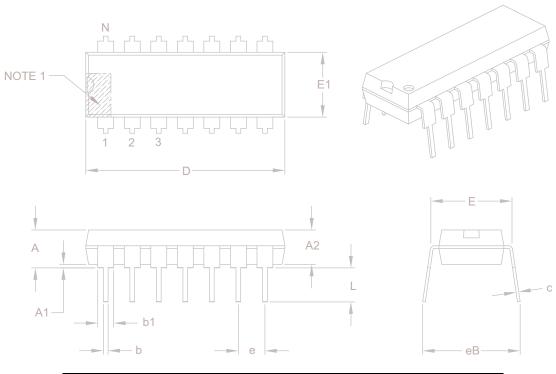

| Package / Case 14-TSSOP (0.173", 4.40mm Width)                                         |

| Supplier Device Package 14-TSSOP                                                       |

| Purchase URL https://www.e-xfl.com/product-detail/microchip-technology/pic16f630t-e-st |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Octopus, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2010, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

#### ISBN: 978-1-60932-173-4

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

NOTES:

# 2.0 MEMORY ORGANIZATION

# 2.1 Program Memory Organization

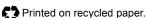

The PIC16F630/676 devices have a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 1K x 14 (0000h-03FFh) for the PIC16F630/676 devices is physically implemented. Accessing a location above these boundaries will cause a wrap around within the first 1K x 14 space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 2-1).

# 2.2 Data Memory Organization

The data memory (see Figure 2-2) is partitioned into two banks, which contain the General Purpose Registers and the Special Function Registers. The Special Function Registers are located in the first 32 locations of each bank. Register locations 20h-5Fh are General Purpose Registers, implemented as static RAM and are mapped across both banks. All other RAM is unimplemented and returns '0' when read. RP0 (STATUS<5>) is the bank select bit.

- RP0 = 0 Bank 0 is selected

- RP0 = 1 Bank 1 is selected

- Note: The IRP and RP1 bits STATUS<7:6> are reserved and should always be maintained as '0's.

- 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as 64 x 8 in the PIC16F630/676 devices. Each register is accessed, either directly or indirectly, through the File Select Register FSR (see Section 2.4 "Indirect Addressing, INDF and FSR Registers").

## 2.2.2.1 STATUS Register

The STATUS register, shown in Register 2-1, contains:

- the arithmetic status of the ALU

- · the Reset status

- the bank select bits for data memory (SRAM)

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits, see **Section 10.0 "Instruction Set Summary"**.

- **Note 1:** Bits IRP and RP1 (STATUS<7:6>) are not used by the PIC16F630/676 and should be maintained as clear. Use of these bits is not recommended, since this may affect upward compatibility with future products.

- 2: The <u>C</u> and <u>DC</u> bits operate as a Borrow and <u>Digit</u> Borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

| REGISTER 2-1: | STATUS — STATUS REGISTER (ADDRESS: 03h OR 83h) |

|---------------|------------------------------------------------|

|---------------|------------------------------------------------|

|       | Reserved                                                                                                                                                                                                                                                                                                                                                      | Reserved                         | R/W-0        | R-1          | R-1           | R/W-x                                        | R/W-x        | R/W-x |  |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--------------|--------------|---------------|----------------------------------------------|--------------|-------|--|--|

|       | IRP                                                                                                                                                                                                                                                                                                                                                           | RP1                              | RP0          | TO           | PD            | Z                                            | DC           | С     |  |  |

|       | bit 7                                                                                                                                                                                                                                                                                                                                                         |                                  |              |              |               |                                              |              | bit 0 |  |  |

|       |                                                                                                                                                                                                                                                                                                                                                               |                                  |              |              |               |                                              |              |       |  |  |

| bit 7 | IRP: This b                                                                                                                                                                                                                                                                                                                                                   | oit is reserve                   | d and shoul  | d be mainta  | ined as '0'   |                                              |              |       |  |  |

| bit 6 | RP1: This                                                                                                                                                                                                                                                                                                                                                     | bit is reserve                   | ed and shou  | ld be mainta | ained as '0'  |                                              |              |       |  |  |

| bit 5 | <b>RP0:</b> Register Bank Select bit (used for direct addressing)<br>1 = Bank 1 (80h-FFh)<br>0 = Bank 0 (00h-7Fh)                                                                                                                                                                                                                                             |                                  |              |              |               |                                              |              |       |  |  |

| bit 4 | <b>TO:</b> Time-out bit<br>1 = After power-up, CLRWDT instruction, or SLEEP instruction<br>0 = A WDT time-out occurred                                                                                                                                                                                                                                        |                                  |              |              |               |                                              |              |       |  |  |

| bit 3 | <b>PD</b> : Power-Down bit<br>1 = After power-up or by the CLRWDT instruction<br>0 = By execution of the SLEEP instruction                                                                                                                                                                                                                                    |                                  |              |              |               |                                              |              |       |  |  |

| bit 2 |                                                                                                                                                                                                                                                                                                                                                               | sult of an ari<br>sult of an ari |              | • •          |               | D                                            |              |       |  |  |

| bit 1 | <ul> <li>0 = The result of an arithmetic or logic operation is not zero</li> <li>DC: Digit carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)</li> <li>For borrow, the polarity is reversed.</li> <li>1 = A carry-out from the 4th low order bit of the result occurred</li> <li>0 = No carry-out from the 4th low order bit of the result</li> </ul> |                                  |              |              |               |                                              |              |       |  |  |

| bit 0 | <b>C</b> : Carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)<br>1 = A carry-out from the Most Significant bit of the result occurred<br>0 = No carry-out from the Most Significant bit of the result occurred                                                                                                                                        |                                  |              |              |               |                                              |              |       |  |  |

|       | Note:                                                                                                                                                                                                                                                                                                                                                         | complemen                        | t of the sec | ond operan   | d. For rotate | on is execut<br>e (RRF, RLF)<br>e source reg | instructions |       |  |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# 2.2.2.6 PCON Register

The Power Control (PCON) register contains flag bits to differentiate between a:

- · Power-on Reset (POR)

- Brown-out Detect (BOD)

- Watchdog Timer Reset (WDT)

- External MCLR Reset

The PCON Register bits are shown in Register 2-6.

## REGISTER 2-6: PCON — POWER CONTROL REGISTER (ADDRESS: 8Eh)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-x |

|-------|-----|-----|-----|-----|-----|-------|-------|

| _     | _   | _   | —   | _   | _   | POR   | BOD   |

| bit 7 |     |     |     |     |     |       | bit 0 |

bit 7-2 Unimplemented: Read as '0'

bit 1 **POR:** Power-on Reset Status bit

1 = No Power-on Reset occurred

0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

bit 0 BOD: Brown-out Detect Status bit

- 1 = No Brown-out Detect occurred

- 0 = A Brown-out Detect occurred (must be set in software after a Brown-out Detect occurs)

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# 2.2.2.7 OSCCAL Register

bit 7-2

bit 1-0

The Oscillator Calibration register (OSCCAL) is used to calibrate the internal 4 MHz oscillator. It contains 6 bits to adjust the frequency up or down to achieve 4 MHz.

The OSCCAL register bits are shown in Register 2-7.

## REGISTER 2-7: OSCCAL—INTERNALOSCILLATOR CALIBRATION REGISTER (ADDRESS: 90h)

|             |                                            |          |             |                                         |       |     | -   |  |

|-------------|--------------------------------------------|----------|-------------|-----------------------------------------|-------|-----|-----|--|

| R/W-1       | R/W-0                                      | R/W-0    | R/W-0       | R/W-0                                   | R/W-0 | U-0 | U-0 |  |

| CAL5        | CAL4                                       | CAL3     | CAL2        | CAL1                                    | CAL0  | _   | _   |  |

| bit 7       |                                            |          |             |                                         |       |     | bit |  |

| 100000 = 0  | Maximum fro<br>Center frequ<br>Minimum fre | iency    |             |                                         |       |     |     |  |

| Unimplem    | ented: Read                                | d as '0' |             |                                         |       |     |     |  |

| Legend:     |                                            |          |             |                                         |       |     |     |  |

| R = Reada   | ble bit                                    | W = W    | ritable bit | U = Unimplemented bit, read as '0'      |       |     |     |  |

| - n = Value | at POR                                     | '1' = B  | it is set   | '0' = Bit is cleared x = Bit is unknown |       |     |     |  |

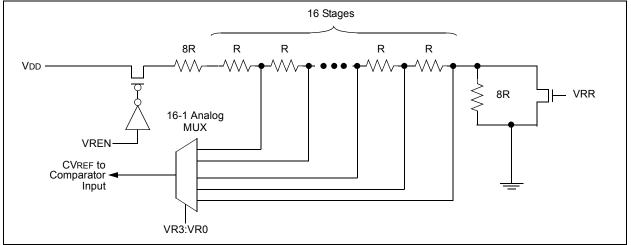

# 4.4 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer. For simplicity, this counter will be referred to as "prescaler" throughout this Data Sheet. The prescaler assignment is controlled in software by the control bit PSA (OPTION\_REG<3>). Clearing the PSA bit will assign the prescaler to Timer0. Prescale values are selectable via the PS2:PS0 bits (OPTION\_REG<2:0>).

The prescaler is not readable or writable. When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x...etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer.

### 4.4.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on the fly" during program execution). To avoid an unintended device Reset, the following instruction sequence (Example 4-1) must be executed when changing the prescaler assignment from Timer0 to WDT.

## EXAMPLE 4-1: CHANGING PRESCALER (TIMER0→WDT)

| BCF<br>CLRWDT | STATUS, RPO        | ;Bank 0<br>;Clear WDT |

|---------------|--------------------|-----------------------|

|               | <b>T</b> N (T) (1) | ,                     |

| CLRF          | TMR0               | ;Clear TMR0 and       |

|               |                    | ; prescaler           |

| BSF           | STATUS, RPO        | ;Bank 1               |

|               |                    |                       |

| MOVLW         | b'00101111'        | ;Required if desired  |

| MOVWF         | OPTION REG         | ; PS2:PS0 is          |

| CLRWDT        | _                  | ; 000 or 001          |

|               |                    | ;                     |

| MOVLW         | b'00101xxx'        | ;Set postscaler to    |

| MOVWF         | OPTION REG         | ; desired WDT rate    |

| BCF           | STATUS, RPO        | ;Bank 0               |

|               |                    |                       |

To change prescaler from the WDT to the TMR0 module, use the sequence shown in Example 4-2. This precaution must be taken even if the WDT is disabled.

## EXAMPLE 4-2: CHANGING PRESCALER (WDT→TIMER0)

| CLRWDT       |                          | ;Clear WDT and                                     |

|--------------|--------------------------|----------------------------------------------------|

| BSF          | STATUS, RPO              | ; postscaler<br>;Bank 1                            |

| MOVLW        | b'xxxx0xxx'              | ;Select TMR0,<br>; prescale, and<br>; clock source |

| MOVWF<br>BCF | OPTION_REG<br>STATUS,RPO | ;<br>;Bank O                                       |

## TABLE 4-1:REGISTERS ASSOCIATED WITH TIMER0

| Address | Name       | Bit 7    | Bit 6                 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOD | Value on<br>all other<br>Resets |

|---------|------------|----------|-----------------------|--------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| 01h     | TMR0       | Timer0 M | imer0 Module Register |        |        |        |        |        |        | XXXX XXXX            | uuuu uuuu                       |

| 0Bh/8Bh | INTCON     | GIE      | PEIE                  | T0IE   | INTE   | RAIE   | T0IF   | INTF   | RAIF   | 0000 0000            | 0000 000u                       |

| 81h     | OPTION_REG | RAPU     | INTEDG                | TOCS   | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111            | 1111 1111                       |

| 85h     | TRISA      | _        | —                     | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 11 1111              | 11 1111                         |

**Legend:** -= Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Timer0 module.

| GISTER 5-1: T1CON — TIMER1 CONTROL REGISTER (ADDRESS: 10h) |                                                                                                                       |                                |             |              |                |           |              |         |  |  |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------|--------------|----------------|-----------|--------------|---------|--|--|

|                                                            | U-0                                                                                                                   | R/W-0                          | R/W-0       | R/W-0        | R/W-0          | R/W-0     | R/W-0        | R/W-0   |  |  |

|                                                            | —                                                                                                                     | TMR1GE                         | T1CKPS1     | T1CKPS0      | T1OSCEN        | T1SYNC    | TMR1CS       | TMR10N  |  |  |

|                                                            | bit 7                                                                                                                 |                                |             |              |                |           |              | bit 0   |  |  |

| bit 7                                                      | Unimplem                                                                                                              | ented: Read                    | as '0'      |              |                |           |              |         |  |  |

| bit 6                                                      | -                                                                                                                     | Timer1 Gate                    |             |              |                |           |              |         |  |  |

|                                                            | If TMR10                                                                                                              |                                |             |              |                |           |              |         |  |  |

|                                                            | This bit is i<br>If TMR10N                                                                                            |                                |             |              |                |           |              |         |  |  |

|                                                            |                                                                                                                       | is on if T1G                   | pin is low  |              |                |           |              |         |  |  |

|                                                            | 0 = Timer1                                                                                                            |                                |             |              |                |           |              |         |  |  |

| bit 5-4                                                    |                                                                                                                       | :T1CKPS0: T                    | •           | t Clock Pres | scale Select I | oits      |              |         |  |  |

|                                                            | -                                                                                                                     | rescale Value<br>rescale Value |             |              |                |           |              |         |  |  |

|                                                            |                                                                                                                       | rescale Value                  |             |              |                |           |              |         |  |  |

|                                                            | 00 <b>= 1:1 P</b>                                                                                                     | rescale Value                  | 9           |              |                |           |              |         |  |  |

| bit 3                                                      | T1OSCEN: LP Oscillator Enable Control bit<br>If INTOSC without CLKOUT oscillator is active:                           |                                |             |              |                |           |              |         |  |  |

|                                                            |                                                                                                                       | illator is enat                |             |              | <u>).</u>      |           |              |         |  |  |

|                                                            |                                                                                                                       | illator is off                 |             |              |                |           |              |         |  |  |

|                                                            | <u>Else:</u><br>This hit is i                                                                                         | aparad                         |             |              |                |           |              |         |  |  |

| bit 2                                                      | This bit is i                                                                                                         | -                              | aal Clock I | nnut Synchr  | onization Co   | atrol bit |              |         |  |  |

| DIL Z                                                      | <b>T1SYNC:</b> Timer1 External Clock Input Synchronization Control bit<br><u>TMR1CS = 1:</u>                          |                                |             |              |                |           |              |         |  |  |

|                                                            | 1 = Do not synchronize external clock input                                                                           |                                |             |              |                |           |              |         |  |  |

|                                                            | 0 = Synchronize external clock input<br><u>TMR1CS = 0:</u>                                                            |                                |             |              |                |           |              |         |  |  |

|                                                            | This bit is ignored. Timer1 uses the internal clock.                                                                  |                                |             |              |                |           |              |         |  |  |

| bit 1                                                      | TMR1CS:                                                                                                               | Timer1 Clock                   | Source S    | elect bit    |                |           |              |         |  |  |

|                                                            | <ul> <li>1 = External clock from T1OSO/T1CKI pin (on the rising edge)</li> <li>0 = Internal clock (Fosc/4)</li> </ul> |                                |             |              |                |           |              |         |  |  |

| h# 0                                                       |                                                                                                                       | -                              | -           |              |                |           |              |         |  |  |

| bit 0                                                      | 1 = Enable                                                                                                            | Timer1 On b<br>s Timer1        | IL          |              |                |           |              |         |  |  |

|                                                            | 0 = Stops                                                                                                             | Timer1                         |             |              |                |           |              |         |  |  |

|                                                            | Legend:                                                                                                               |                                |             |              |                |           |              |         |  |  |

|                                                            | R = Reada                                                                                                             | able bit                       | VV = V      | Vritable bit | U = Unim       | plemented | bit, read as | '0'     |  |  |

|                                                            | - n = Value                                                                                                           | e at POR                       | '1' = E     | Bit is set   | '0' = Bit is   | s cleared | x = Bit is u | Inknown |  |  |

# REGISTER 5-1: T1CON — TIMER1 CONTROL REGISTER (ADDRESS: 10h)

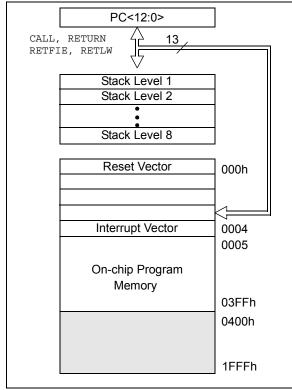

# 6.5 Comparator Reference

The comparator module also allows the selection of an internally generated voltage reference for one of the comparator inputs. The internal reference signal is used for four of the eight Comparator modes. The VRCON register, Register 6-2, controls the voltage reference module shown in Figure 6-5.

# 6.5.1 CONFIGURING THE VOLTAGE REFERENCE

The voltage reference can output 32 distinct voltage levels, 16 in a high range and 16 in a low range.

The following equations determine the output voltages:

| $VRR = 1$ (low range): $CVREF = (VR3:VR0 / 24) \times VDD$ |  |

|------------------------------------------------------------|--|

| VRR = 0 (high range): $CVREF = (VDD / 4) + (VR3:VR0 x)$    |  |

| VDD / 32)                                                  |  |

## 6.5.2 VOLTAGE REFERENCE ACCURACY/ERROR

The full range of VSS to VDD cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 6-5) keep CVREF from approaching VSS or VDD. The Voltage Reference is VDD derived and therefore, the CVREF output changes with fluctuations in VDD. The tested absolute accuracy of the Comparator Voltage Reference can be found in **Section 12.0 "Electrical Specifications"**.

# 6.6 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output is ensured to have a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs. Otherwise, the maximum delay of the comparators should be used (Table 12-7).

# 6.7 Operation During Sleep

Both the comparator and voltage reference, if enabled before entering Sleep mode, remain active during Sleep. This results in higher Sleep currents than shown in the power-down specifications. The additional current consumed by the comparator and the voltage reference is shown separately in the specifications. To minimize power consumption while in Sleep mode, turn off the comparator, CM2:CM0 = 111, and voltage reference, VRCON<7> = 0.

While the comparator is enabled during Sleep, an interrupt will wake-up the device. If the device wakes up from Sleep, the contents of the CMCON and VRCON registers are not affected.

# 6.8 Effects of a Reset

A device Reset forces the CMCON and VRCON registers to their Reset states. This forces the comparator module to be in the Comparator Reset mode, CM2:CM0 = 000 and the voltage reference to its off state. Thus, all potential inputs are analog inputs with the comparator and voltage reference disabled to consume the smallest current possible.

| REGISTER 7-3: | ANSEL — ANALOG SELECT REGISTER (ADRESS: 91h) (PIC16F676 ONLY) |

|---------------|---------------------------------------------------------------|

|---------------|---------------------------------------------------------------|

|   | R/W-1 |

|---|-------|-------|-------|-------|-------|-------|-------|-------|

|   | ANS7  | ANS6  | ANS5  | ANS4  | ANS3  | ANS2  | ANS1  | ANS0  |

| b | it 7  |       |       |       |       |       |       | bit 0 |

bit 7-0: **ANS<7:0>**: Analog Select between analog or digital function on pins AN<7:0>, respectively. 1 = Analog input. Pin is assigned as analog input.<sup>(1)</sup>

0 = Digital I/O. Pin is assigned to port or special function.

**Note 1:** Setting a pin to an analog input automatically disables the digital input circuitry, weak pull-ups, and interrupt-on-change if available. The corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 8.1 EEADR

The EEADR register can address up to a maximum of 128 bytes of data EEPROM. Only seven of the eight bits in the register (EEADR<6:0>) are required. The MSb (bit 7) is ignored.

The upper bit should always be '0' to remain upward compatible with devices that have more data EEPROM memory.

#### 8.2 EECON1 AND EECON2 REGISTERS

EECON1 is the control register with four low order bits physically implemented. The upper four bits are nonimplemented and read as '0's.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared in hardware at completion

- n = Value at POR

of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a MCLR Reset, or a WDT Time-out Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit. clear it. and rewrite the location. The data and address will be cleared, therefore, the EEDATA and EEADR registers will need to be re-initialized.

The Interrupt flag bit EEIF in the PIR1 register is set when the write is complete. This bit must be cleared in software.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the data EEPROM write sequence.

# REGISTE

| R 8-3:  | EECON1 -                                                                                                                                 | - EEPRO      |                                                | OL REGIS     | TER (ADD      | RESS: 9Ch      | ר)           |           |  |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------------------------------------|--------------|---------------|----------------|--------------|-----------|--|--|--|--|

|         | U-0                                                                                                                                      | U-0          | U-0                                            | U-0          | R/W-x         | R/W-0          | R/S-0        | R/S-0     |  |  |  |  |

|         | —                                                                                                                                        | —            | _                                              | _            | WRERR         | WREN           | WR           | RD        |  |  |  |  |

|         | bit 7                                                                                                                                    |              |                                                |              | ·             |                |              | bit 0     |  |  |  |  |

| oit 7-4 | Unimpleme                                                                                                                                | ented: Rea   | <b>d as</b> '0'                                |              |               |                |              |           |  |  |  |  |

| oit 3   | WRERR: E                                                                                                                                 | EPROM EI     | ror Flag bit                                   |              |               |                |              |           |  |  |  |  |

|         |                                                                                                                                          | operation o  | r BOD detec                                    |              | d (any MCLR   | Reset, any     | WDT Reset    | t during  |  |  |  |  |

| bit 2   |                                                                                                                                          |              | e Enable bit                                   | :            |               |                |              |           |  |  |  |  |

|         | 1 = Allows write cycles                                                                                                                  |              |                                                |              |               |                |              |           |  |  |  |  |

|         | 0 = Inhibits                                                                                                                             | write to the | data EEPR                                      | OM           |               |                |              |           |  |  |  |  |

| oit 1   | WR: Write (                                                                                                                              | Control bit  |                                                |              |               |                |              |           |  |  |  |  |

|         | can only                                                                                                                                 | be set, no   | tle (The bit is<br>t cleared, in<br>lata EEPRO | software.)   | / hardware or | nce write is o | complete. Ti | he WR bit |  |  |  |  |

| bit 0   | RD: Read C                                                                                                                               |              |                                                |              |               |                |              |           |  |  |  |  |

|         | 1 = Initiates an EEPROM read (Read takes one cycle. RD is cleared in hardware. The RD bit<br>can only be set, not cleared, in software.) |              |                                                |              |               |                |              |           |  |  |  |  |

|         | 0 = Does not initiate an EEPROM read                                                                                                     |              |                                                |              |               |                |              |           |  |  |  |  |

|         | Legend:                                                                                                                                  |              |                                                |              |               |                |              |           |  |  |  |  |

|         | S = Bit can                                                                                                                              | only be se   | t                                              |              |               |                |              |           |  |  |  |  |

|         | R = Readat                                                                                                                               | ole bit      | W = W                                          | /ritable bit | U = Unin      | nplemented     | bit, read as | '0'       |  |  |  |  |

|         |                                                                                                                                          |              | 141 0                                          |              | 101 011       |                | D.1.1        |           |  |  |  |  |

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

# 8.7 DATA EEPROM OPERATION DURING CODE-PROTECT

Data memory can be code-protected by programming the CPD bit to '0'.

When the data memory is code-protected, the CPU is able to read and write data to the data EEPROM. It is recommended to code-protect the program memory when code protecting data memory. This prevents anyone from programming zeroes over the existing code (which will execute as NOPS) to reach an added routine, programmed in unused program memory, which outputs the contents of data memory. Programming unused locations to '0' will also help prevent data memory code protection from becoming breached.

| Address | Name                  | Bit 7  | Bit 6                    | Bit 5     | Bit 4    | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Valu<br>POR, | e on | Value<br>oth<br>Res | ner  |

|---------|-----------------------|--------|--------------------------|-----------|----------|-------|-------|-------|--------|--------------|------|---------------------|------|

| 0Ch     | PIR1                  | EEIF   | ADIF                     | _         |          | CMIF  | _     | —     | TMR1IF | 00           | 00   | 00                  | 00   |

| 9Ah     | EEDATA                | EEPROM | EPROM Data Register      |           |          |       |       |       |        | 0000         | 0000 | 0000                | 0000 |

| 9Bh     | EEADR                 | _      | EEPRON                   | 1 Address | Register |       |       |       |        | -000         | 0000 | -000                | 0000 |

| 9Ch     | EECON1                | _      | —                        | —         | —        | WRERR | WREN  | WR    | RD     |              | x000 |                     | q000 |

| 9Dh     | EECON2 <sup>(1)</sup> | EEPROM | EPROM Control Register 2 |           |          |       |       |       |        |              |      |                     |      |

# TABLE 8-1: REGISTERS/BITS ASSOCIATED WITH DATA EEPROM

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends upon condition. Shaded cells are not used by the data EEPROM module.

Note 1: EECON2 is not a physical register.

# 9.1 Configuration Bits

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1') to select various device configurations, as shown in Register 9-1. These bits are mapped in program memory location 2007h.

**Note:** Address 2007h is beyond the user program memory space. It belongs to the special configuration memory space (2000h-3FFFh), which can be accessed only during programming. See PIC16F630/676 Programming Specification for more information.

# REGISTER 9-1: CONFIG — CONFIGURATION WORD (ADDRESS: 2007h)

| R/P-1 R/I     | P-1 U-0         | ) U-0                                                                                                                                                                                             | U-0 R/P-1                                | R/P-1      | R/P-1       | R/P-1       | R/P-1             | R/P-1     | R/P-1       | R/P-1      | R/P-1     |  |

|---------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------|-------------|-------------|-------------------|-----------|-------------|------------|-----------|--|

| BG1 B         | G0 —            | _                                                                                                                                                                                                 | - CPD                                    | CP         | BODEN       | MCLRE       | PWRTE             | WDTE      | F0SC2       | F0SC1      | F0SC0     |  |

| bit 13        |                 |                                                                                                                                                                                                   |                                          |            |             |             |                   |           |             |            | bit 0     |  |

|               |                 |                                                                                                                                                                                                   |                                          |            |             |             |                   |           |             |            |           |  |

| bit 13-12     |                 |                                                                                                                                                                                                   | p Calibration bits                       | for BOE    | and PO      | R voltage   | (1)               |           |             |            |           |  |

|               |                 | west bandg                                                                                                                                                                                        |                                          |            |             |             |                   |           |             |            |           |  |

|               | -               | 11 = Highest bandgap voltage                                                                                                                                                                      |                                          |            |             |             |                   |           |             |            |           |  |

| bit 11-9      |                 | emented: F                                                                                                                                                                                        |                                          |            |             |             |                   |           |             |            |           |  |

| bit 8         |                 |                                                                                                                                                                                                   | rotection bit <sup>(2)</sup>             |            |             |             |                   |           |             |            |           |  |

|               |                 |                                                                                                                                                                                                   | ode protection is                        |            |             |             |                   |           |             |            |           |  |

|               |                 |                                                                                                                                                                                                   | ode protection is                        | enabled    | 1           |             |                   |           |             |            |           |  |

| bit 7         |                 | le Protectio                                                                                                                                                                                      |                                          |            |             |             |                   |           |             |            |           |  |

|               |                 |                                                                                                                                                                                                   | ry code protection<br>ry code protection |            |             |             |                   |           |             |            |           |  |

| <b>h</b> :+ C |                 |                                                                                                                                                                                                   | t Detect Enable I                        |            | bieu        |             |                   |           |             |            |           |  |

| bit 6         |                 | : Brown-ou<br>) enabled                                                                                                                                                                           | Detect Enable i                          | DIL        |             |             |                   |           |             |            |           |  |

|               | -               | ) disabled                                                                                                                                                                                        |                                          |            |             |             |                   |           |             |            |           |  |

| bit 5         |                 |                                                                                                                                                                                                   | R pin function se                        | lect bit(5 | )           |             |                   |           |             |            |           |  |

| 5.00          |                 |                                                                                                                                                                                                   | function is MCLI                         |            |             |             |                   |           |             |            |           |  |

|               |                 |                                                                                                                                                                                                   | function is digita                       |            | CLR interr  | ally tied t | o Vdd             |           |             |            |           |  |

| bit 4         | PWRTE           | : Power-up                                                                                                                                                                                        | Timer Enable bi                          | t          |             |             |                   |           |             |            |           |  |

|               |                 | RT disabled                                                                                                                                                                                       |                                          |            |             |             |                   |           |             |            |           |  |

|               |                 | RT enabled                                                                                                                                                                                        |                                          |            |             |             |                   |           |             |            |           |  |

| bit 3         |                 |                                                                                                                                                                                                   | Timer Enable bit                         |            |             |             |                   |           |             |            |           |  |

|               |                 | Γ enabled<br>Γ disabled                                                                                                                                                                           |                                          |            |             |             |                   |           |             |            |           |  |

| bit 2-0       |                 |                                                                                                                                                                                                   | scillator Selection                      | , bite     |             |             |                   |           |             |            |           |  |

| DIL 2-0       |                 |                                                                                                                                                                                                   | : CLKOUT functi                          |            | A4/05C2     |             | nin PC            | on PA5    |             |            |           |  |

|               |                 |                                                                                                                                                                                                   | : I/O function on                        |            |             |             |                   |           |             |            |           |  |

|               |                 |                                                                                                                                                                                                   | llator: CLKOUT fu                        |            |             |             |                   |           |             | 5/OSC1/    | CLKIN     |  |

|               | 100 <b>= IN</b> | ITOSC osc                                                                                                                                                                                         | illator: I/O functio                     | on on RA   | 4/OSC2/     | CLKOUT      | pin, I/O fu       | unction o | on RA5/C    |            |           |  |

|               |                 |                                                                                                                                                                                                   | tion on RA4/OSC                          |            |             |             |                   |           |             |            |           |  |

|               |                 |                                                                                                                                                                                                   | : High speed cry                         |            |             |             |                   |           |             | 1/CLKI     | N         |  |

|               |                 |                                                                                                                                                                                                   | Crystal/resonat                          |            |             |             |                   |           |             |            |           |  |

|               | 000 <b>–</b> Li | r uscillator.                                                                                                                                                                                     | Low power crys                           |            | 44/0302/    | CLKOUT      |                   | 0301/     | CLNIN       |            |           |  |

|               | Note 1          | The Band                                                                                                                                                                                          | gap Calibration b                        | ite are fa | ctony prog  | rammed a    | and must b        | he read a | and save    | d prior to | erasina   |  |

|               | 1010 1.         |                                                                                                                                                                                                   | e as specified in the                    |            |             |             |                   |           |             |            |           |  |

|               |                 | in an expo                                                                                                                                                                                        | ort of the Configu                       | ation Wo   | ord. Microo | hip Devel   | opment T          | ools mai  | ntain all o | calibratio | n bits to |  |

|               |                 | factory se                                                                                                                                                                                        |                                          |            |             | -           |                   |           |             |            |           |  |

|               |                 |                                                                                                                                                                                                   | e data EEPROM                            |            |             |             |                   |           |             |            |           |  |

|               | 3:              | 3: The entire program memory will be erased, including OSCCAL value, when the code protection is                                                                                                  |                                          |            |             |             |                   |           | ection is   |            |           |  |

|               | 4.              | turned off.                                                                                                                                                                                       |                                          |            |             |             |                   |           |             |            |           |  |

|               |                 | <ul> <li>4: Enabling Brown-out Detect does not automatically enable Power-up Timer.</li> <li>5: When MCLR is asserted in INTOSC or RC mode, the internal clock oscillator is disabled.</li> </ul> |                                          |            |             |             |                   |           | ed.         |            |           |  |

|               | Legend          |                                                                                                                                                                                                   |                                          |            |             | .,          |                   |           |             |            |           |  |

|               |                 |                                                                                                                                                                                                   | sing ICSP™                               |            |             |             |                   |           |             |            |           |  |

|               |                 | adable bit                                                                                                                                                                                        | 0                                        | v = Writa  | ble bit     | U = I       | Unimplen          | nented b  | it, read a  | as '0'     |           |  |

|               |                 | ue at POR                                                                                                                                                                                         | 1                                        | = bit is s | set         |             | ,<br>bit is clear |           |             | t is unkr  | nown      |  |

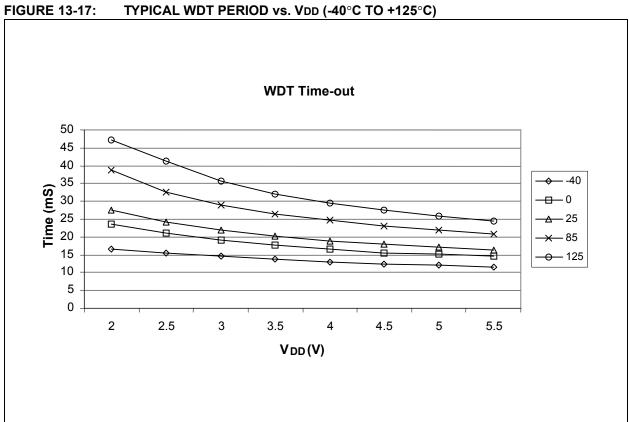

Note 1: T0SE, T0CS, PSA, PS0-PS2 are bits in the OPTION register.

## TABLE 9-9: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address | Name         | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOD | Value on all<br>other<br>Resets |

|---------|--------------|-------|--------|-------|-------|-------|-------|-------|-------|----------------------|---------------------------------|

| 81h     | OPTION_REG   | RAPU  | INTEDG | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111            | 1111 1111                       |

| 2007h   | Config. bits | CP    | BODEN  | MCLRE | PWRTE | WDTE  | F0SC2 | F0SC1 | F0SC0 | uuuu uuuu            | uuuu uuuu                       |

Legend: u = Unchanged, shaded cells are not used by the Watchdog Timer.

# 9.7 Power-Down Mode (Sleep)

The Power-down mode is entered by executing a SLEEP instruction.

If the Watchdog Timer is enabled:

- · WDT will be cleared but keeps running

- PD bit in the STATUS register is cleared

- TO bit is set

- · Oscillator driver is turned off

- I/O ports maintain the status they had before SLEEP was executed (driving high, low, or high-impedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD, or VSS, with no external circuitry drawing current from the I/O pin and the comparators and CVREF should be disabled. I/O pins that are high-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTA should be considered.

The  $\overline{\text{MCLR}}$  pin must be at a logic high level (VIHMC).

| Note: | It should be noted that a Reset generated |

|-------|-------------------------------------------|

|       | by a WDT time-out does not drive MCLR     |

|       | pin low.                                  |

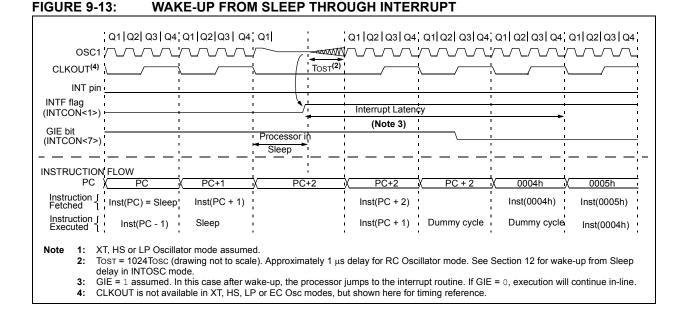

### 9.7.1 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin

- 2. Watchdog Timer Wake-up (if WDT was enabled)

- 3. Interrupt from RA2/INT pin, PORTA change, or a peripheral interrupt.

The first event will cause a device Reset. The two latter events are considered a continuation of program execution. The  $\overline{TO}$  and  $\overline{PD}$  bits in the STATUS register can be used to determine the cause of device Reset. The  $\overline{PD}$  bit, which is set on power-up, is cleared when Sleep is invoked.  $\overline{TO}$  bit is cleared if WDT Wake-up occurred.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction after the SLEEP instruction of the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have an NOP after the SLEEP instruction.

| If the global interrupts are disabled (GIE is |  |  |  |

|-----------------------------------------------|--|--|--|

| cleared), but any interrupt source has both   |  |  |  |

| its interrupt enable bit and the correspond-  |  |  |  |

| ing interrupt flag bits set, the device will  |  |  |  |

| immediately wake-up from Sleep. The           |  |  |  |

| SLEEP instruction is completely executed.     |  |  |  |

|                                               |  |  |  |

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

# 10.0 INSTRUCTION SET SUMMARY

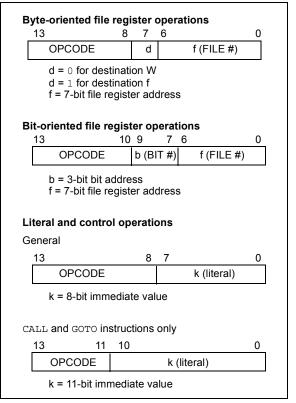

The PIC16F630/676 instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Each PIC16 instruction is a 14-bit word divided into an **opcode**, which specifies the instruction type, and one or more **operands**, which further specify the operation of the instruction. The formats for each of the categories is presented in Figure 10-1, while the various opcode fields are summarized in Table 10-1.

Table 10-2 lists the instructions recognized by the MPASM<sup>TM</sup> assembler. A complete description of each instruction is also available in the PIC<sup>®</sup> Mid-Range Reference Manual (DS33023).

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator, which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, **'k**' represents an 8-bit or 11-bit constant, or literal value

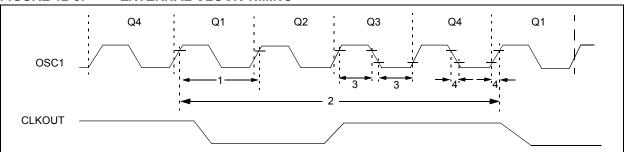

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a normal instruction execution time of 1  $\mu$ s. All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles, with the second cycle executed as a NOP.

| Note: | To maintain upward compatibility with  |  |  |  |  |

|-------|----------------------------------------|--|--|--|--|

|       | future products, do not use the OPTION |  |  |  |  |

|       | and TRIS instructions.                 |  |  |  |  |

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

# 10.1 READ-MODIFY-WRITE OPERATIONS

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register. For example, a CLRF PORTA instruction will read PORTA, clear all the data bits, then write the result back to PORTA. This example would have the unintended result of clearing the condition that set the RAIF flag.

# TABLE 10-1:OPCODE FIELD<br/>DESCRIPTIONS

| Field | Description                                                                                                                                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                                 |

| W     | Working register (accumulator)                                                                                                                                                       |

| b     | Bit address within an 8-bit file register                                                                                                                                            |

| k     | Literal field, constant data or label                                                                                                                                                |

| x     | Don't care location (= $0$ or $1$ ).<br>The assembler will generate code with x = $0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                                        |

| PC    | Program Counter                                                                                                                                                                      |

| то    | Time-out bit                                                                                                                                                                         |

| PD    | Power-down bit                                                                                                                                                                       |

# FIGURE 10-1: GENERAL FORMAT FOR INSTRUCTIONS

#### 10.2 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |

| Operation:       | $(W) + k \to (W)$                                                                                                          |

| Status Affected: | C, DC, Z                                                                                                                   |

| Description:     | The contents of the W register<br>are added to the eight-bit literal 'k'<br>and the result is placed in the W<br>register. |

| ADDWF            | Add W and f                                                                                                                                                                    |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                     |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                          |