# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 12                                                                       |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 64 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 16-VQFN Exposed Pad                                                      |

| Supplier Device Package    | 16-QFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f676-e-ml |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral functions for controlling the desired operation of the device (see Table 2-1). These registers are static RAM.

The special registers can be classified into two sets: core and peripheral. The Special Function Registers associated with the "core" are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

#### FIGURE 2-2: DATA MEMORY MAP OF THE PIC16F630/676

| THE PIC16F630/676                                                                |                 |                               |                |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------|-----------------|-------------------------------|----------------|--|--|--|--|--|--|--|

|                                                                                  | File<br>Address | A                             | File<br>ddress |  |  |  |  |  |  |  |

| Indirect addr. <sup>(1)</sup>                                                    | 00h             | Indirect addr. <sup>(1)</sup> | 80h            |  |  |  |  |  |  |  |

| TMR0                                                                             | 01h             | OPTION_REG                    | 81h            |  |  |  |  |  |  |  |

| PCL                                                                              | 02h             | PCL                           | 82h            |  |  |  |  |  |  |  |

| STATUS                                                                           | 03h             | STATUS                        | 83h            |  |  |  |  |  |  |  |

| FSR                                                                              | 04h             | FSR                           | 84h            |  |  |  |  |  |  |  |

| PORTA                                                                            | 05h             | TRISA                         | 85h            |  |  |  |  |  |  |  |

|                                                                                  | 06h             | -                             | 86h            |  |  |  |  |  |  |  |

| PORTC                                                                            | 07h             | TRISC                         | 87h            |  |  |  |  |  |  |  |

|                                                                                  | 08h             | -                             | 88h            |  |  |  |  |  |  |  |

|                                                                                  | 09h             |                               | 89h            |  |  |  |  |  |  |  |

| PCLATH                                                                           | 0Ah             | PCLATH                        | 8Ah            |  |  |  |  |  |  |  |

| INTCON                                                                           | 0Bh             | INTCON                        | 8Bh            |  |  |  |  |  |  |  |

| PIR1                                                                             | 0Ch             | PIE1                          | 8Ch            |  |  |  |  |  |  |  |

|                                                                                  | 0Dh             |                               | 8Dh            |  |  |  |  |  |  |  |

| TMR1L                                                                            | 0Eh             | PCON                          | 8Eh            |  |  |  |  |  |  |  |

| TMR1H                                                                            | 0Fh             |                               | 8Fh            |  |  |  |  |  |  |  |

| T1CON                                                                            | 10h             | OSCCAL                        | 90h            |  |  |  |  |  |  |  |

| TICON                                                                            | 11h             | ANSEL <sup>(2)</sup>          | 91h            |  |  |  |  |  |  |  |

|                                                                                  | 12h             | THOLE                         | 92h            |  |  |  |  |  |  |  |

|                                                                                  | 13h             | -                             | 93h            |  |  |  |  |  |  |  |

|                                                                                  | 14h             |                               | 94h            |  |  |  |  |  |  |  |

|                                                                                  | 15h             | WPUA                          | 95h            |  |  |  |  |  |  |  |

|                                                                                  | 16h             | IOCA                          | 96h            |  |  |  |  |  |  |  |

|                                                                                  | 17h             | IOCA                          | 97h            |  |  |  |  |  |  |  |

|                                                                                  | 18h             |                               | 98h            |  |  |  |  |  |  |  |

| CMCON                                                                            | 19h             | VRCON                         | 99h            |  |  |  |  |  |  |  |

| CINCON                                                                           | 1Ah             | EEDAT                         | 9Ah            |  |  |  |  |  |  |  |

|                                                                                  | 1Bh             | EEADR                         | 9Bh            |  |  |  |  |  |  |  |

|                                                                                  | 1Ch             | EECON1                        | 9Ch            |  |  |  |  |  |  |  |

|                                                                                  | 1Dh             | EECON2 <sup>(1)</sup>         | 9Dh            |  |  |  |  |  |  |  |

| ADRESH <sup>(2)</sup>                                                            | 1Eh             | ADRESL <sup>(2)</sup>         | 9Eh            |  |  |  |  |  |  |  |

| ADCON0 <sup>(2)</sup>                                                            | 1Fh             | ADCON1 <sup>(2)</sup>         | 9Fh            |  |  |  |  |  |  |  |

| ADCONU                                                                           | 20h             | ADCONT                        | A0h            |  |  |  |  |  |  |  |

| General<br>Purpose<br>Registers<br>64 Bytes                                      | 2011            | accesses<br>20h-5Fh           |                |  |  |  |  |  |  |  |

|                                                                                  | 5Fh             |                               | DFh            |  |  |  |  |  |  |  |

|                                                                                  | 60h             |                               | E0h            |  |  |  |  |  |  |  |

|                                                                                  | 001             |                               | Lon            |  |  |  |  |  |  |  |

|                                                                                  |                 |                               |                |  |  |  |  |  |  |  |

|                                                                                  |                 |                               |                |  |  |  |  |  |  |  |

|                                                                                  | 7Fh             | _                             | FFh            |  |  |  |  |  |  |  |

| Bank 0                                                                           |                 | Bank 1                        |                |  |  |  |  |  |  |  |

| <ul><li>Unimplemente</li><li>1: Not a physical</li><li>2: PIC16F676 on</li></ul> | register.       | mory locations, rea           | d as '0'.      |  |  |  |  |  |  |  |

#### 2.2.2.4 PIE1 Register

The PIE1 register contains the interrupt enable bits, as shown in Register 2-4.

- n = Value at POR

Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

#### **REGISTER 2-4:** PIE1 — PERIPHERAL INTERRUPT ENABLE REGISTER 1 (ADDRESS: 8Ch) R/W-0 R/W-0 U-0 R/W-0 U-0 R/W-0 U-0 U-0 EEIE ADIE CMIE TMR1IE bit 7 bit 0 bit 7 **EEIE:** EE Write Complete Interrupt Enable bit 1 = Enables the EE write complete interrupt 0 = Disables the EE write complete interrupt bit 6 ADIE: A/D Converter Interrupt Enable bit (PIC16F676 only) 1 = Enables the A/D converter interrupt 0 = Disables the A/D converter interrupt bit 5-4 Unimplemented: Read as '0' bit 3 CMIE: Comparator Interrupt Enable bit 1 = Enables the comparator interrupt 0 = Disables the comparator interrupt bit 2-1 Unimplemented: Read as '0' bit 0 TMR1IE: TMR1 Overflow Interrupt Enable bit 1 = Enables the TMR1 overflow interrupt 0 = Disables the TMR1 overflow interrupt Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

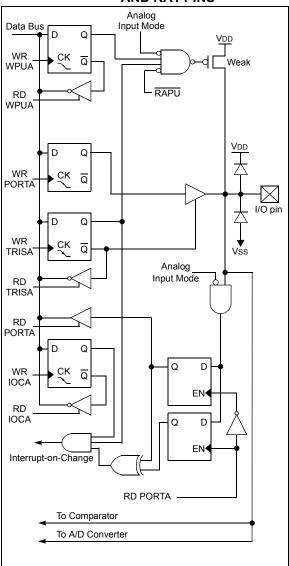

### 3.2.3 PIN DESCRIPTIONS AND DIAGRAMS

Each PORTA pin is multiplexed with other functions. The pins and their combined functions are briefly described here. For specific information about individual functions such as the comparator or the A/D, refer to the appropriate section in this Data Sheet.

#### 3.2.3.1 RA0/AN0/CIN+

Figure 3-1 shows the diagram for this pin. The RA0 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the A/D (PIC16F676 only)

- · an analog input to the comparator

#### 3.2.3.2 RA1/AN1/CIN-/VREF

Figure 3-1 shows the diagram for this pin. The RA1 pin is configurable to function as one of the following:

- as a general purpose I/O

- an analog input for the A/D (PIC16F676 only)

- an analog input to the comparator

- a voltage reference input for the A/D (PIC16F676 only)

#### FIGURE 3-1: BLOCK DIAGRAM OF RA0 AND RA1 PINS

| Address | Name                 | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOD | Value on<br>all other<br>Resets |

|---------|----------------------|-------|--------|--------|--------|--------|--------|--------|--------|-------------------------|---------------------------------|

| 05h     | PORTA                | _     | —      | RA5    | RA4    | RA3    | RA2    | RA1    | RA0    | xx xxxxx                | uu uuuu                         |

| 0Bh/8Bh | INTCON               | GIE   | PEIE   | T0IE   | INTE   | RAIE   | T0IF   | INTF   | RAIF   | 0000 0000               | 0000 000u                       |

| 19h     | CMCON                | _     | COUT   | _      | CINV   | CIS    | CM2    | CM1    | CM0    | -0-0 0000               | -0-0 0000                       |

| 81h     | OPTION_REG           | RAPU  | INTEDG | TOCS   | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111               | 1111 1111                       |

| 85h     | TRISA                | _     | _      | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 11 1111                 | 11 1111                         |

| 91h     | ANSEL <sup>(1)</sup> | ANS7  | ANS6   | ANS5   | ANS4   | ANS3   | ANS2   | ANS1   | ANS0   | 1111 1111               | 1111 1111                       |

| 95h     | WPUA                 | _     | _      | WPUA5  | WPUA4  | _      | WPUA2  | WPUA1  | WPUA0  | 11 -111                 | 11 -111                         |

| 96h     | IOCA                 | _     | _      | IOCA5  | IOCA4  | IOCA3  | IOCA2  | IOCA1  | IOCA0  | 00 0000                 | 00 0000                         |

Note 1: PIC16F676 only.

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

NOTES:

#### 4.4 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer. For simplicity, this counter will be referred to as "prescaler" throughout this Data Sheet. The prescaler assignment is controlled in software by the control bit PSA (OPTION\_REG<3>). Clearing the PSA bit will assign the prescaler to Timer0. Prescale values are selectable via the PS2:PS0 bits (OPTION\_REG<2:0>).

The prescaler is not readable or writable. When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x...etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer.

#### 4.4.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on the fly" during program execution). To avoid an unintended device Reset, the following instruction sequence (Example 4-1) must be executed when changing the prescaler assignment from Timer0 to WDT.

#### EXAMPLE 4-1: CHANGING PRESCALER (TIMER0→WDT)

| BCF<br>CLRWDT | STATUS, RPO        | ;Bank 0<br>;Clear WDT |

|---------------|--------------------|-----------------------|

|               | <b>T</b> N (T) (1) | ,                     |

| CLRF          | TMR0               | ;Clear TMR0 and       |

|               |                    | ; prescaler           |

| BSF           | STATUS, RPO        | ;Bank 1               |

|               |                    |                       |

| MOVLW         | b'00101111'        | ;Required if desired  |

| MOVWF         | OPTION REG         | ; PS2:PS0 is          |

| CLRWDT        | _                  | ; 000 or 001          |

|               |                    | ;                     |

| MOVLW         | b'00101xxx'        | ;Set postscaler to    |

| MOVWF         | OPTION REG         | ; desired WDT rate    |

| BCF           | STATUS, RPO        | ;Bank 0               |

|               |                    |                       |

To change prescaler from the WDT to the TMR0 module, use the sequence shown in Example 4-2. This precaution must be taken even if the WDT is disabled.

#### EXAMPLE 4-2: CHANGING PRESCALER (WDT→TIMER0)

| CLRWDT       |                          | ;Clear WDT and                                     |

|--------------|--------------------------|----------------------------------------------------|

| BSF          | STATUS, RPO              | ; postscaler<br>;Bank 1                            |

| MOVLW        | b'xxxx0xxx'              | ;Select TMR0,<br>; prescale, and<br>; clock source |

| MOVWF<br>BCF | OPTION_REG<br>STATUS,RPO | ;<br>;Bank O                                       |

#### TABLE 4-1:REGISTERS ASSOCIATED WITH TIMER0

| Address | Name       | Bit 7    | Bit 6                 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOD | Value on<br>all other<br>Resets |

|---------|------------|----------|-----------------------|--------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| 01h     | TMR0       | Timer0 M | imer0 Module Register |        |        |        |        |        |        |                      | uuuu uuuu                       |

| 0Bh/8Bh | INTCON     | GIE      | PEIE                  | T0IE   | INTE   | RAIE   | T0IF   | INTF   | RAIF   | 0000 0000            | 0000 000u                       |

| 81h     | OPTION_REG | RAPU     | INTEDG                | TOCS   | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111            | 1111 1111                       |

| 85h     | TRISA      | _        | —                     | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 11 1111              | 11 1111                         |

**Legend:** -= Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Timer0 module.

NOTES:

|         | <b>WROOM</b>                                  | <b>IOLIAO</b>                                                                                                                                                                                   |                 |              | NOL NEO     |            | DIVECC: 0    | 011)    |  |  |  |

|---------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------|-------------|------------|--------------|---------|--|--|--|

|         | R/W-0                                         | U-0                                                                                                                                                                                             | R/W-0           | R/W-0        | R/W-0       | R/W-0      | R/W-0        | R/W-0   |  |  |  |

|         | VREN                                          |                                                                                                                                                                                                 | VRR             | _            | VR3         | VR2        | VR1          | VR0     |  |  |  |

|         | bit 7                                         |                                                                                                                                                                                                 |                 |              |             |            |              | bit 0   |  |  |  |

| bit 7   | 1 = CVREF                                     | REF Enable<br>circuit powe<br>circuit powe                                                                                                                                                      |                 | no IDD drain |             |            |              |         |  |  |  |

| bit 6   | Unimplem                                      | Unimplemented: Read as '0'                                                                                                                                                                      |                 |              |             |            |              |         |  |  |  |

| bit 5   | <b>VRR:</b> CVR<br>1 = Low rat<br>0 = High ra | 0                                                                                                                                                                                               | election bit    |              |             |            |              |         |  |  |  |

| bit 4   | Unimplem                                      | ented: Rea                                                                                                                                                                                      | <b>d as</b> '0' |              |             |            |              |         |  |  |  |

| bit 3-0 | When VRR                                      | Unimplemented: Read as '0'<br>VR3:VR0: CVREF value selection bits $0 \le VR$ [3:0] $\le 15$<br>When VRR = 1: CVREF = (VR3:VR0 / 24) * VDD<br>When VRR = 0: CVREF = VDD/4 + (VR3:VR0 / 32) * VDD |                 |              |             |            |              |         |  |  |  |

|         | Legend:                                       |                                                                                                                                                                                                 |                 |              |             |            |              |         |  |  |  |

|         | R = Reada                                     | ble bit                                                                                                                                                                                         | W = W           | /ritable bit | U = Unim    | nplemented | bit, read as | '0'     |  |  |  |

|         | - n = Value                                   | at POR                                                                                                                                                                                          | '1' = B         | it is set    | '0' = Bit i | s cleared  | x = Bit is u | inknown |  |  |  |

#### REGISTER 6-2: VRCON — VOLTAGE REFERENCE CONTROL REGISTER (ADDRESS: 99h)

#### 6.9 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of the comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<6>, to determine the actual change that has occurred. The CMIF bit, PIR1<3>, is the comparator interrupt flag. This bit must be reset in software by clearing it to '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CMIE bit (PIE1<3>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are cleared, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON. This will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition and allow flag bit CMIF to be cleared.

| Address | Name   | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOD | Value on<br>all other<br>Resets |

|---------|--------|-------|-------|--------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| 0Bh/8Bh | INTCON | GIE   | PEIE  | T0IE   | INTE   | RAIE   | T0IF   | INTF   | RAIF   | 0000 0000            | 0000 000u                       |

| 0Ch     | PIR1   | EEIF  | ADIF  | —      | _      | CMIF   | _      | _      | TMR1IF | 00 00                | 00 00                           |

| 19h     | CMCON  | _     | COUT  | —      | CINV   | CIS    | CM2    | CM1    | CM0    | -0-0 0000            | -0-0 0000                       |

| 8Ch     | PIE1   | EEIE  | ADIE  | _      |        | CMIE   | _      | _      | TMR1IE | 00 00                | 00 00                           |

| 85h     | TRISA  | _     | _     | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 11 1111              | 11 1111                         |

| 99h     | VRCON  | VREN  | _     | VRR    | _      | VR3    | VR2    | VR1    | VR0    | 0-0- 0000            | 0-0- 0000                       |

#### TABLE 6-2: REGISTERS ASSOCIATED WITH COMPARATOR MODULE

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the comparator module.

Note: If a change in the CMCON register (COUT) should occur when a read operation is being executed (start of the Q2 cycle), then the CMIF (PIR1<3>) interrupt flag may not get set.

|                    | R/W-0                                                                                                                                                                   | R/W-0                                                                                                                                          | U-0                                                                              | R/W-0                                                                      | R/W-0                                       | R/W-0                     | R/W-0                              | R/W-0             |  |  |  |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------|---------------------------|------------------------------------|-------------------|--|--|--|

|                    | ADFM                                                                                                                                                                    | VCFG                                                                                                                                           | _                                                                                | CHS2                                                                       | CHS1                                        | CHS0                      | GO/DONE                            | ADON              |  |  |  |

|                    | bit 7                                                                                                                                                                   |                                                                                                                                                |                                                                                  |                                                                            |                                             |                           |                                    | bit 0             |  |  |  |

|                    |                                                                                                                                                                         |                                                                                                                                                |                                                                                  |                                                                            |                                             |                           |                                    |                   |  |  |  |

| bit 7              | <b>ADFM:</b> A/E<br>1 = Right ju<br>0 = Left jus                                                                                                                        |                                                                                                                                                | med Select                                                                       | bit                                                                        |                                             |                           |                                    |                   |  |  |  |

| bit 6              |                                                                                                                                                                         | VCFG: Voltage Reference bit<br>1 = VREF pin<br>0 = VDD                                                                                         |                                                                                  |                                                                            |                                             |                           |                                    |                   |  |  |  |

| bit 5              | Unimplem                                                                                                                                                                | ented: Rea                                                                                                                                     | d as zero                                                                        |                                                                            |                                             |                           |                                    |                   |  |  |  |

| bit 4-2            | 000 = Cha<br>001 = Cha<br>010 = Cha<br>011 = Cha<br>100 = Cha<br>101 = Cha<br>110 = Cha                                                                                 | 60: Analog (<br>annel 00 (AN<br>annel 01 (AN<br>annel 02 (AN<br>annel 03 (AN<br>annel 04 (AN<br>annel 05 (AN<br>annel 06 (AN<br>annel 07 (AN   | NO)<br>N1)<br>N2)<br>N3)<br>N4)<br>N5)<br>N6)                                    | ect bits                                                                   |                                             |                           |                                    |                   |  |  |  |

| bit 1              | GO/DONE<br>1 = A/D co<br>This bit                                                                                                                                       | A/D Conve                                                                                                                                      | rsion Status<br>cle in progre<br>cally cleared                                   | ss. Setting f<br>d by hardwa                                               |                                             |                           | nversion cycle<br>rsion has com    |                   |  |  |  |

| bit 0              | ADON: A/D Conversion Status bit<br>1 = A/D converter module is operating<br>0 = A/D converter is shut-off and consumes no operating current                             |                                                                                                                                                |                                                                                  |                                                                            |                                             |                           |                                    |                   |  |  |  |

|                    | Logond                                                                                                                                                                  |                                                                                                                                                |                                                                                  |                                                                            |                                             |                           |                                    |                   |  |  |  |

|                    | Legend:                                                                                                                                                                 | blo bit                                                                                                                                        | ۱۵/ – ۱۸                                                                         | <i>I</i> ritabla bit                                                       |                                             | nnlomontor                | hit road as '(                     | )'                |  |  |  |

|                    | R = Reada                                                                                                                                                               |                                                                                                                                                |                                                                                  | /ritable bit                                                               |                                             | •                         | l bit, read as '(                  |                   |  |  |  |

|                    | -                                                                                                                                                                       |                                                                                                                                                |                                                                                  | /ritable bit<br>it is set                                                  |                                             | nplemented<br>is cleared  | l bit, read as '(<br>x = Bit is ur |                   |  |  |  |

| REGISTER 7-2:      | R = Reada<br>- n = Value                                                                                                                                                | at POR                                                                                                                                         | '1' = B                                                                          | it is set                                                                  | '0' = Bit                                   | is cleared                |                                    |                   |  |  |  |

| REGISTER 7-2:      | R = Reada<br>- n = Value<br>ADCON1 ·                                                                                                                                    | at POR<br>— A/D CO                                                                                                                             | '1' = B                                                                          | it is set<br>EGISTER 1                                                     | '0' = Bit                                   | is cleared                | x = Bit is ur                      | iknown            |  |  |  |

| REGISTER 7-2:      | R = Reada<br>- n = Value                                                                                                                                                | at POR<br>— <b>A/D CO</b><br>R/W-0                                                                                                             | '1' = B<br>NTROL RE<br>R/W-0                                                     | it is set<br>EGISTER 1<br>R/W-0                                            | '0' = Bit                                   | is cleared                |                                    |                   |  |  |  |

| REGISTER 7-2:      | R = Reada<br>- n = Value<br>ADCON1 -<br>U-0<br>—                                                                                                                        | at POR<br>— A/D CO                                                                                                                             | '1' = B                                                                          | it is set<br>EGISTER 1                                                     | '0' = Bit                                   | is cleared                | x = Bit is ur                      | U-0               |  |  |  |

| REGISTER 7-2:      | R = Reada<br>- n = Value<br>ADCON1 ·                                                                                                                                    | at POR<br>— <b>A/D CO</b><br>R/W-0                                                                                                             | '1' = B<br>NTROL RE<br>R/W-0                                                     | it is set<br>EGISTER 1<br>R/W-0                                            | '0' = Bit                                   | is cleared                | x = Bit is ur                      | iknown            |  |  |  |

|                    | R = Reada<br>- n = Value<br>ADCON1 -<br>U-0<br>bit 7                                                                                                                    | at POR<br>— A/D CO<br>R/W-0<br>ADCS2                                                                                                           | '1' = B<br>NTROL RE<br>R/W-0<br>ADCS1                                            | it is set<br>EGISTER 1<br>R/W-0                                            | '0' = Bit                                   | is cleared                | x = Bit is ur                      | U-0               |  |  |  |

| bit 7:             | R = Reada<br>- n = Value<br>ADCON1 -<br>U-0<br>bit 7<br>Unimplem                                                                                                        | at POR<br>– A/D CO<br>R/W-0<br>ADCS2<br>ented: Rea                                                                                             | '1' = B<br>NTROL RI<br>R/W-0<br>ADCS1<br>d as '0'                                | it is set<br>EGISTER 1<br>R/W-0<br>ADCS0                                   | '0' = Bit i<br>I <b>(ADRESS</b><br>U-0<br>— | is cleared                | x = Bit is ur                      | U-0               |  |  |  |

|                    | R = Reada<br>- n = Value<br>ADCON1 -<br>U-0<br>bit 7<br>Unimplem<br>ADCS<2:0                                                                                            | at POR<br>— A/D CO<br>R/W-0<br>ADCS2<br>ented: Read                                                                                            | '1' = B<br>NTROL RI<br>R/W-0<br>ADCS1<br>d as '0'                                | it is set<br>EGISTER 1<br>R/W-0<br>ADCS0                                   | '0' = Bit i<br>I <b>(ADRESS</b><br>U-0<br>— | is cleared                | x = Bit is ur                      | U-0               |  |  |  |

| bit 7:             | R = Reada<br>- n = Value<br>ADCON1 -<br>U-0<br>bit 7<br>Unimplem                                                                                                        | at POR<br>— A/D CO<br>R/W-0<br>ADCS2<br>ented: Read<br>>: A/D Conv<br>c/2<br>c/8                                                               | '1' = B<br>NTROL RI<br>R/W-0<br>ADCS1<br>d as '0'                                | it is set<br>EGISTER 1<br>R/W-0<br>ADCS0                                   | '0' = Bit i<br>I <b>(ADRESS</b><br>U-0<br>— | is cleared                | x = Bit is ur                      | U-0               |  |  |  |

| bit 7:             | R = Reada<br>- n = Value<br>ADCON1 -<br>U-0<br>bit 7<br>Unimplem<br>ADCS<2:0<br>000 = Fos<br>001 = Fos<br>010 = Fos<br>x11 = FRC<br>100 = Fos                           | at POR<br>— A/D CO<br>R/W-0<br>ADCS2<br>ented: Read<br>>: A/D Conv<br>c/2<br>c/8<br>c/32<br>(clock derive<br>c/4<br>c/16                       | '1' = B<br>NTROL RI<br>R/W-0<br>ADCS1<br>d as '0'<br>version Cloc                | it is set<br>EGISTER 1<br>R/W-0<br>ADCS0                                   | '0' = Bit i<br>I <b>(ADRESS</b><br>U-0<br>— | <b>5: 9Fh)</b><br>U-0     | x = Bit is ur<br>U-0               | U-0               |  |  |  |

| bit 7:<br>bit 6-4: | R = Reada<br>- n = Value<br>ADCON1 -<br>U-0<br>bit 7<br>Unimplem<br>ADCS<2:0<br>000 = Fos<br>001 = Fos<br>010 = Fos<br>100 = Fos<br>101 = Fos                           | at POR<br>— A/D CO<br>R/W-0<br>ADCS2<br>ented: Read<br>>: A/D Conv<br>c/2<br>c/8<br>c/32<br>(clock deriv<br>c/4<br>c/16<br>c/64                | '1' = B<br>NTROL RI<br>R/W-0<br>ADCS1<br>d as '0'<br>version Cloc<br>ed from a d | it is set<br>EGISTER 1<br>R/W-0<br>ADCS0                                   | '0' = Bit i<br>I <b>(ADRESS</b><br>U-0<br>— | <b>5: 9Fh)</b><br>U-0     | x = Bit is ur<br>U-0               | U-0               |  |  |  |

| bit 7:             | R = Reada<br>- n = Value<br>ADCON1 -<br>U-0<br>bit 7<br>Unimplem<br>ADCS<2:0<br>000 = Fos<br>001 = Fos<br>010 = Fos<br>100 = Fos<br>101 = Fos                           | at POR<br>— A/D CO<br>R/W-0<br>ADCS2<br>ented: Read<br>>: A/D Conv<br>c/2<br>c/8<br>c/32<br>(clock derive<br>c/4<br>c/16                       | '1' = B<br>NTROL RI<br>R/W-0<br>ADCS1<br>d as '0'<br>version Cloc<br>ed from a d | it is set<br>EGISTER 1<br>R/W-0<br>ADCS0                                   | '0' = Bit i<br>I <b>(ADRESS</b><br>U-0<br>— | <b>5: 9Fh)</b><br>U-0     | x = Bit is ur<br>U-0               | U-0               |  |  |  |

| bit 7:<br>bit 6-4: | R = Reada<br>- n = Value<br>ADCON1 -<br>U-0<br>bit 7<br>Unimplem<br>ADCS<2:0<br>000 = Fos<br>010 = Fos<br>010 = Fos<br>110 = Fos<br>101 = Fos<br>110 = Fos              | at POR<br>— A/D CO<br>R/W-0<br>ADCS2<br>ented: Read<br>>: A/D Conv<br>c/2<br>c/8<br>c/32<br>(clock deriv<br>c/4<br>c/16<br>c/64                | '1' = B<br>NTROL RI<br>R/W-0<br>ADCS1<br>d as '0'<br>version Cloc<br>ed from a d | it is set<br>EGISTER 1<br>R/W-0<br>ADCS0                                   | '0' = Bit i<br>I <b>(ADRESS</b><br>U-0<br>— | <b>5: 9Fh)</b><br>U-0     | x = Bit is ur<br>U-0               | U-0               |  |  |  |

| bit 7:<br>bit 6-4: | R = Reada<br>- n = Value<br>ADCON1 -<br>U-0<br>bit 7<br>Unimplem<br>ADCS<2:0<br>000 = Fos<br>001 = Fos<br>010 = Fos<br>100 = Fos<br>101 = Fos<br>101 = Fos<br>101 = Fos | at POR<br>— A/D CO<br>R/W-0<br>ADCS2<br>ented: Read<br>>: A/D Conv<br>C/2<br>C/8<br>C/32<br>(clock deriv<br>C/4<br>C/16<br>C/64<br>ented: Read | '1' = B<br>NTROL RI<br>R/W-0<br>ADCS1<br>d as '0'<br>version Cloc<br>ed from a d | it is set<br>EGISTER 1<br>R/W-0<br>ADCS0                                   | '0' = Bit i<br>I (ADRESS<br>U-0<br>—        | s: 9Fh)<br>U-0            | x = Bit is ur<br>U-0<br>           | U-0               |  |  |  |

| bit 7:<br>bit 6-4: | R = Reada<br>- n = Value<br>ADCON1 -<br>U-0<br>bit 7<br>Unimplem<br>ADCS<2:0<br>000 = Fos<br>010 = Fos<br>010 = Fos<br>110 = Fos<br>101 = Fos<br>110 = Fos              | at POR<br>— A/D CO<br>R/W-0<br>ADCS2<br>ented: Read<br>>: A/D Conv<br>C/2<br>C/8<br>C/32<br>(clock deriv<br>C/4<br>C/16<br>C/64<br>ented: Read | '1' = B<br>NTROL RI<br>R/W-0<br>ADCS1<br>d as '0'<br>version Cloc<br>ed from a d | it is set<br>EGISTER 1<br>R/W-0<br>ADCS0<br>k Select bits<br>edicated inte | '0' = Bit i<br>I (ADRESS<br>U-0<br>—        | s: <b>9Fh)</b><br>U-0<br> | x = Bit is ur<br>U-0               | U-0<br>—<br>bit 0 |  |  |  |

### REGISTER 7-1: ADCON0 — A/D CONTROL REGISTER (ADDRESS: 1Fh)

| REGISTER 7-3: | ANSEL — ANALOG SELECT REGISTER (ADRESS: 91h) (PIC16F676 ONLY) |

|---------------|---------------------------------------------------------------|

|---------------|---------------------------------------------------------------|

|   | R/W-1 |

|---|-------|-------|-------|-------|-------|-------|-------|-------|

|   | ANS7  | ANS6  | ANS5  | ANS4  | ANS3  | ANS2  | ANS1  | ANS0  |

| b | it 7  |       |       |       |       |       |       | bit 0 |

bit 7-0: **ANS<7:0>**: Analog Select between analog or digital function on pins AN<7:0>, respectively. 1 = Analog input. Pin is assigned as analog input.<sup>(1)</sup>

0 = Digital I/O. Pin is assigned to port or special function.

**Note 1:** Setting a pin to an analog input automatically disables the digital input circuitry, weak pull-ups, and interrupt-on-change if available. The corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 9.2 Oscillator Configurations

#### 9.2.1 OSCILLATOR TYPES

The PIC16F630/676 can be operated in eight different Oscillator Option modes. The user can program three Configuration bits (FOSC2 through FOSC0) to select one of these eight modes:

- LP Low-Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC External Resistor/Capacitor (2 modes)

- · INTOSC Internal Oscillator (2 modes)

- EC External Clock In

| Note: | Additional information on oscillator config-<br>urations is available in the PIC <sup>®</sup> Mid-Range |

|-------|---------------------------------------------------------------------------------------------------------|

|       | Reference Manual, (DS33023).                                                                            |

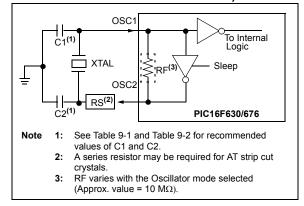

### 9.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

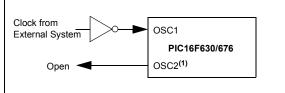

In XT, LP or HS modes a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation (see Figure 9-1). The PIC16F630/676 oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may yield a frequency outside of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1 pin (see Figure 9-2).

#### FIGURE 9-1: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (HS, XT OR LP OSC CONFIGURATION)

#### EXTERNAL CLOCK INPUT OPERATION (HS, XT, EC, OR LP OSC CONFIGURATION)

Note 1: Functions as RA4 in EC Osc mode.

### TABLE 9-1:CAPACITOR SELECTION FOR<br/>CERAMIC RESONATORS

| Ranges Characterized:                                                                                                                                                                                                                                                                                                          |                               |                                   |                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------------------|-----------------------------------|

| Mode                                                                                                                                                                                                                                                                                                                           | Freq                          | OSC1(C1)                          | OSC2(C2)                          |

| ХТ                                                                                                                                                                                                                                                                                                                             | 455 kHz<br>2.0 MHz<br>4.0 MHz | 68-100 pF<br>15-68 pF<br>15-68 pF | 68-100 pF<br>15-68 pF<br>15-68 pF |

| HS                                                                                                                                                                                                                                                                                                                             | 8.0 MHz<br>16.0 MHz           | 10-68 pF<br>10-22 pF              | 10-68 pF<br>10-22 pF              |

| Note 1: Higher capacitance increases the stability<br>of the oscillator but also increases the<br>start-up time. These values are for design<br>guidance only. Since each resonator has<br>its own characteristics, the user should<br>consult the resonator manufacturer for<br>appropriate values of external<br>components. |                               |                                   |                                   |

#### TABLE 9-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR

| Mode                                                      | Freq                      | OSC1(C1)                          | OSC2(C2)                           |

|-----------------------------------------------------------|---------------------------|-----------------------------------|------------------------------------|

| LP                                                        | 32 kHz                    | 68-100 pF                         | 68-100 pF                          |

| ХТ                                                        | 100 kHz<br>2 MHz<br>4 MHz | 68-150 pF<br>15-30 pF<br>15-30 pF | 150-200 pF<br>15-30 pF<br>15-30 pF |

| HS                                                        | 8 MHz<br>10 MHz<br>20 MHz | 15-30 pF<br>15-30 pF<br>15-30 pF  | 15-30 pF<br>15-30 pF<br>15-30 pF   |

| <b>Note 1:</b> Higher capacitance increases the stability |                           |                                   |                                    |

of the oscillator but also increases the start-up time. These values are for design guidance only. Rs may be required in HS mode as well as XT mode to avoid overdriving crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

#### 9.3 Reset

The PIC16F630/676 differentiates between various kinds of Reset:

- a) Power-on Reset (POR)

- b) WDT Reset during normal operation

- c) WDT Reset during Sleep

- d) MCLR Reset during normal operation

- e) MCLR Reset during Sleep

- f) Brown-out Detect (BOD)

Some registers are not affected in any Reset condition; their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on:

- · Power-on Reset

- MCLR Reset

- WDT Reset

- WDT Reset during Sleep

- Brown-out Detect (BOD)

They are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation.  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are set or cleared differently in different Reset situations as indicated in Table 9-4. These bits are used in software to determine the nature of the Reset. See Table 9-7 for a full description of Reset states of all registers.

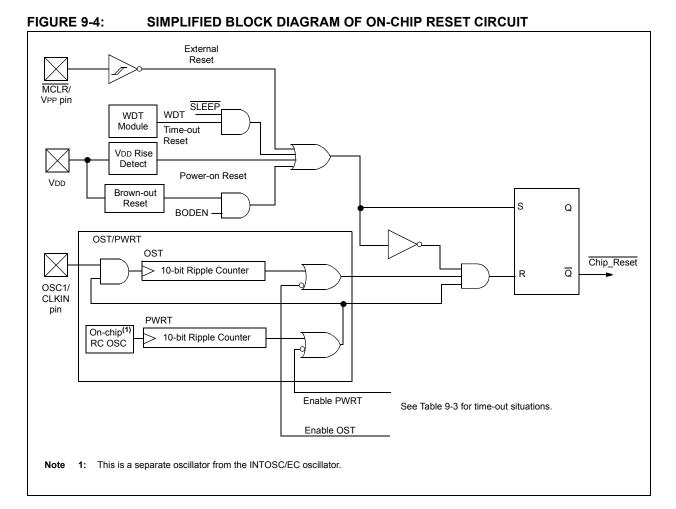

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 9-4.

The  $\overline{\text{MCLR}}$  Reset path has a noise filter to detect and ignore small pulses. See Table 12-4 in Electrical Specifications Section for pulse-width specification.

### 10.0 INSTRUCTION SET SUMMARY

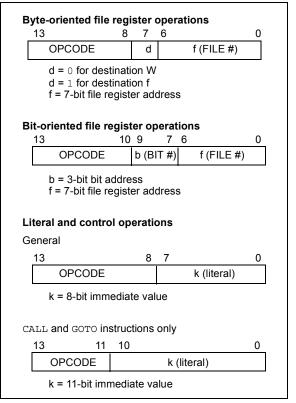

The PIC16F630/676 instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Each PIC16 instruction is a 14-bit word divided into an **opcode**, which specifies the instruction type, and one or more **operands**, which further specify the operation of the instruction. The formats for each of the categories is presented in Figure 10-1, while the various opcode fields are summarized in Table 10-1.

Table 10-2 lists the instructions recognized by the MPASM<sup>TM</sup> assembler. A complete description of each instruction is also available in the PIC<sup>®</sup> Mid-Range Reference Manual (DS33023).

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator, which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, **'k**' represents an 8-bit or 11-bit constant, or literal value

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a normal instruction execution time of 1  $\mu$ s. All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles, with the second cycle executed as a NOP.

| Note: | To maintain upward compatibility with  |

|-------|----------------------------------------|

|       | future products, do not use the OPTION |

|       | and TRIS instructions.                 |

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

#### 10.1 READ-MODIFY-WRITE OPERATIONS

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register. For example, a CLRF PORTA instruction will read PORTA, clear all the data bits, then write the result back to PORTA. This example would have the unintended result of clearing the condition that set the RAIF flag.

### TABLE 10-1:OPCODE FIELD<br/>DESCRIPTIONS

| Field | Description                                                                                                                                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                                 |

| W     | Working register (accumulator)                                                                                                                                                       |

| b     | Bit address within an 8-bit file register                                                                                                                                            |

| k     | Literal field, constant data or label                                                                                                                                                |

| x     | Don't care location (= $0$ or $1$ ).<br>The assembler will generate code with x = $0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                                        |

| PC    | Program Counter                                                                                                                                                                      |

| то    | Time-out bit                                                                                                                                                                         |

| PD    | Power-down bit                                                                                                                                                                       |

### FIGURE 10-1: GENERAL FORMAT FOR INSTRUCTIONS

#### 10.2 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |

| Operation:       | $(W) + k \to (W)$                                                                                                          |

| Status Affected: | C, DC, Z                                                                                                                   |

| Description:     | The contents of the W register<br>are added to the eight-bit literal 'k'<br>and the result is placed in the W<br>register. |

| ADDWF            | Add W and f                                                                                                                                                                    |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                     |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                |  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                          |  |

| Status Affected: | C, DC, Z                                                                                                                                                                       |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0, the<br>result is stored in the W register. If<br>'d' is 1, the result is stored back in<br>register 'f'. |  |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BCF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| ANDLW            | AND Literal with W                                                                                                     |

|------------------|------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                               |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                        |

| Status Affected: | Z                                                                                                                      |

| Description:     | The contents of W register are<br>AND'ed with the eight-bit literal<br>'k'. The result is placed in the W<br>register. |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BTFSS f,b                                                                                                                                                                                        |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b < 7 \end{array}$                                                                                                                                                  |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                              |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next instruc-<br>tion is discarded and a NOP is<br>executed instead, making this a<br>2-cycle instruction. |

| ANDWF            | AND W with f                                                                                                                                                |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                           |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                   |  |  |  |

| Status Affected: | Z                                                                                                                                                           |  |  |  |

| Description:     | AND the W register with register<br>'f'. If 'd' is 0, the result is stored in<br>the W register. If 'd' is 1, the result<br>is stored back in register 'f'. |  |  |  |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                                       |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [/abe/] BTFSC f,b                                                                                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                           |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                                       |

| Status Affected: | None                                                                                                                                                                                                                          |

| Description:     | If bit 'b' in register 'f' is '1', the next<br>instruction is executed.<br>If bit 'b', in register 'f', is '0', the<br>next instruction is discarded, and<br>a NOP is executed instead, making<br>this a 2-cycle instruction. |

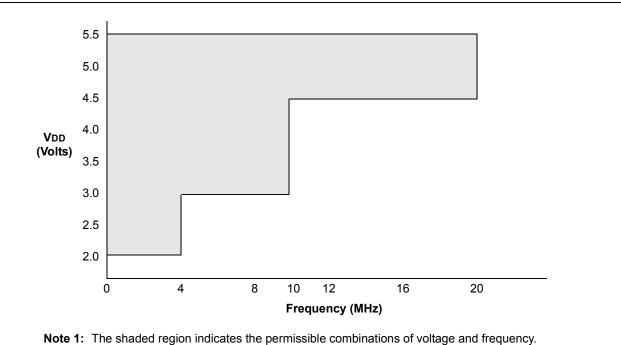

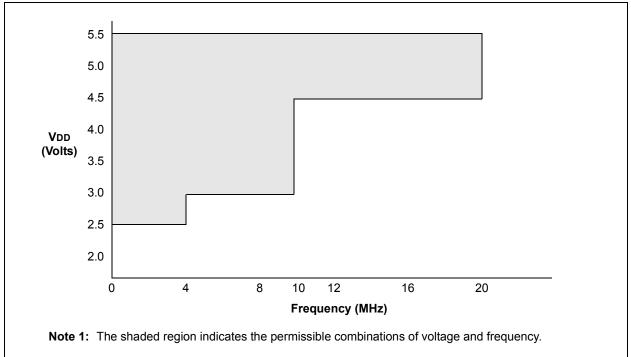

#### FIGURE 12-2: PIC16F676 WITH A/D ENABLED VOLTAGE-FREQUENCY GRAPH, $\textbf{-40^{\circ}C} \leq \textbf{TA} \leq \textbf{+125^{\circ}C}$

| Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le Ta \le +85^{\circ}C$ for industrial |                                           |      |     |       |            |     |                    |

|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------|-----|-------|------------|-----|--------------------|

| Param Device Characteristics                                                                                                       | Min                                       | Typ† | Мах | Units | Conditions |     |                    |

| No.                                                                                                                                | Device characteristics with Typ1 wax onto | onno | VDD | Note  |            |     |                    |

| D010                                                                                                                               | Supply Current (IDD)                      | -    | 9   | 16    | μA         | 2.0 | Fosc = 32 kHz      |

|                                                                                                                                    |                                           | —    | 18  | 28    | μA         | 3.0 | LP Oscillator Mode |

|                                                                                                                                    |                                           | —    | 35  | 54    | μA         | 5.0 |                    |

| D011                                                                                                                               |                                           | —    | 110 | 150   | μA         | 2.0 | Fosc = 1 MHz       |

|                                                                                                                                    |                                           | _    | 190 | 280   | μA         | 3.0 | XT Oscillator Mode |

|                                                                                                                                    |                                           | _    | 330 | 450   | μA         | 5.0 |                    |

| D012                                                                                                                               |                                           | _    | 220 | 280   | μA         | 2.0 | Fosc = 4 MHz       |

|                                                                                                                                    |                                           | _    | 370 | 650   | μA         | 3.0 | XT Oscillator Mode |

|                                                                                                                                    |                                           | _    | 0.6 | 1.4   | mA         | 5.0 |                    |

| D013                                                                                                                               |                                           | _    | 70  | 110   | μA         | 2.0 | Fosc = 1 MHz       |

|                                                                                                                                    |                                           | _    | 140 | 250   | μA         | 3.0 | EC Oscillator Mode |

|                                                                                                                                    |                                           | —    | 260 | 390   | μA         | 5.0 |                    |

| D014                                                                                                                               |                                           | —    | 180 | 250   | μA         | 2.0 | Fosc = 4 MHz       |

|                                                                                                                                    |                                           | _    | 320 | 470   | μA         | 3.0 | EC Oscillator Mode |

|                                                                                                                                    |                                           | _    | 580 | 850   | μA         | 5.0 |                    |

| D015                                                                                                                               |                                           | —    | 340 | 450   | μA         | 2.0 | Fosc = 4 MHz       |

|                                                                                                                                    |                                           | _    | 500 | 780   | μA         | 3.0 | INTOSC Mode        |

|                                                                                                                                    |                                           | _    | 0.8 | 1.1   | mA         | 5.0 |                    |

| D016                                                                                                                               |                                           | _    | 180 | 250   | μA         | 2.0 | Fosc = 4 MHz       |

|                                                                                                                                    |                                           |      | 320 | 450   | μA         | 3.0 | EXTRC Mode         |

|                                                                                                                                    |                                           | _    | 580 | 800   | μA         | 5.0 |                    |

| D017                                                                                                                               |                                           | _    | 2.1 | 2.95  | mA         | 4.5 | Fosc = 20 MHz      |

|                                                                                                                                    |                                           | _    | 2.4 | 3.0   | mA         | 5.0 | HS Oscillator Mode |

#### 12.2 DC Characteristics: PIC16F630/676-I (Industrial)

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in Active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

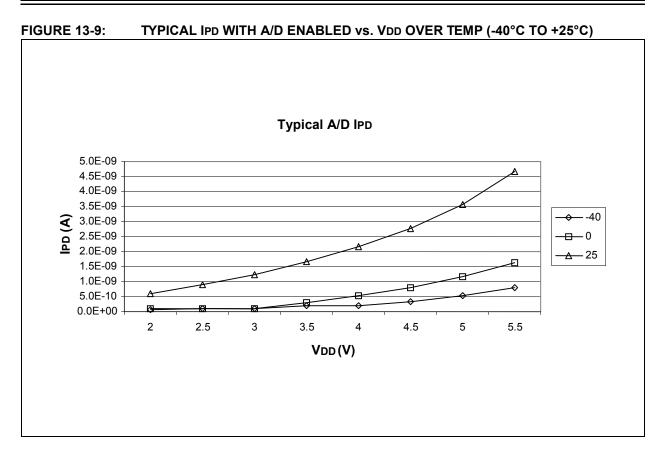

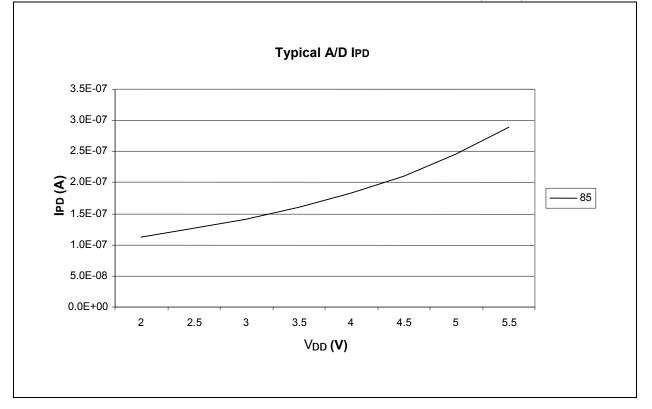

FIGURE 13-10: TYPICAL IPD WITH A/D ENABLED vs. VDD OVER TEMP (+85°C)

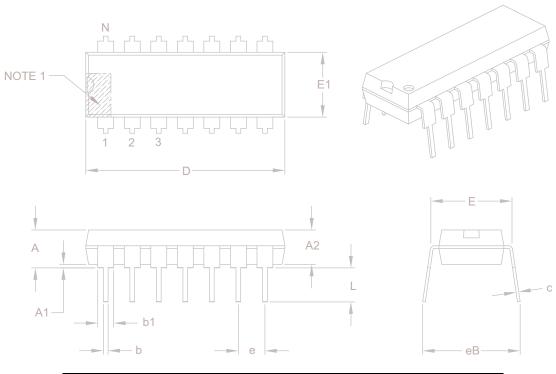

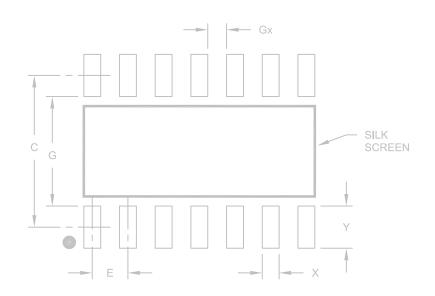

#### 14.2 Package Details

The following sections give the technical details of the packages.

#### 14-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            |          | INCHES |      |  |  |

|----------------------------|------------------|----------|--------|------|--|--|

| Dimensio                   | Dimension Limits |          | NOM    | MAX  |  |  |

| Number of Pins             | Ν                | 14       |        |      |  |  |

| Pitch                      | е                | .100 BSC |        |      |  |  |

| Top to Seating Plane       | Α                | -        | -      | .210 |  |  |

| Molded Package Thickness   | A2               | .115     | .130   | .195 |  |  |

| Base to Seating Plane      | A1               | .015     | -      | -    |  |  |

| Shoulder to Shoulder Width | Е                | .290     | .310   | .325 |  |  |

| Molded Package Width       | E1               | .240     | .250   | .280 |  |  |

| Overall Length             | D                | .735     | .750   | .775 |  |  |

| Tip to Seating Plane       | L                | .115     | .130   | .150 |  |  |

| Lead Thickness             | С                | .008     | .010   | .015 |  |  |

| Upper Lead Width           | b1               | .045     | .060   | .070 |  |  |

| Lower Lead Width           | b                | .014     | .018   | .022 |  |  |

| Overall Row Spacing §      | eB               | -        | -      | .430 |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located with the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-005B

14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]