Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 12                                                                       |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 64 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                           |

| Supplier Device Package    | 14-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f676-e-sl |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2.2 OPTION Register

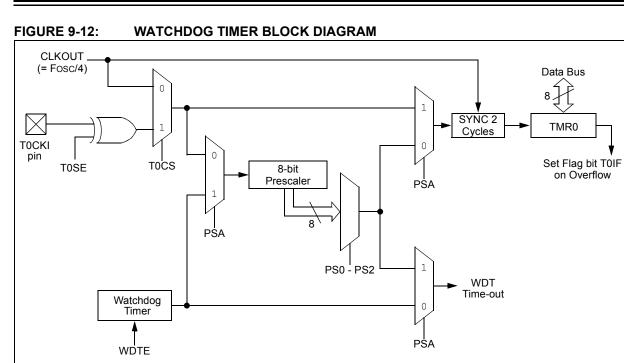

The OPTION register is a readable and writable register, which contains various control bits to configure:

- TMR0/WDT prescaler

- External RA2/INT interrupt

- TMR0

- Weak pull-ups on PORTA

#### REGISTER 2-2: OPTION\_REG — OPTION REGISTER (ADDRESS: 81h)

|         | R/W-1       | R/W-1         | R/W-1                         | R/W-1         | R/W-1       | R/W-1  | R/W-1 | R/W-1 |

|---------|-------------|---------------|-------------------------------|---------------|-------------|--------|-------|-------|

|         | RAPU        | INTEDG        | TOCS                          | T0SE          | PSA         | PS2    | PS1   | PS0   |

|         | bit 7       |               |                               |               |             |        |       | bit 0 |

|         |             |               |                               |               |             |        |       |       |

| bit 7   |             |               | ip Enable bit                 |               |             |        |       |       |

|         |             |               | are disabled<br>are enabled l | oy individual | PORT latch  | values |       |       |

| bit 6   |             | · ·           | lge Select bi                 | •             |             | Valueo |       |       |

| Site    |             |               | edge of RA                    |               |             |        |       |       |

|         | 0 = Interru | pt on falling | g edge of RA                  | 2/INT pin     |             |        |       |       |

| bit 5   |             |               | Source Selec                  | t bit         |             |        |       |       |

|         |             |               | 2/T0CKI pin<br>n cycle clock  |               |             |        |       |       |

| bit 4   |             |               | Edge Select                   | · ,           |             |        |       |       |

|         |             |               |                               | sition on RA2 | 2/T0CKI pin |        |       |       |

|         | 0 = Increm  | nent on low   | -to-high trans                | sition on RA2 | 2/T0CKI pin |        |       |       |

| bit 3   |             | scaler Assig  |                               |               |             |        |       |       |

|         |             |               | ned to the V<br>aned to the T | imer0 modul   | e           |        |       |       |

| bit 2-0 |             |               | Rate Select I                 |               | -           |        |       |       |

|         |             | Bit Value     | TMR0 Rate                     | WDT Rate      |             |        |       |       |

|         |             | 000           | 1:2                           | 1:1           |             |        |       |       |

|         |             | 001           | 1:4                           | 1:2           |             |        |       |       |

|         |             | 010           | 1:8                           | 1:4           |             |        |       |       |

|         |             | 011<br>100    | 1 : 16<br>1 : 32              | 1:8<br>1:16   |             |        |       |       |

|         |             | 101           | 1:64                          | 1:32          |             |        |       |       |

|         |             | 110           | 1 : 128                       | 1:64          |             |        |       |       |

|         |             | 111           | 1 : 256                       | 1 : 128       |             |        |       |       |

|         |             |               |                               |               |             |        |       |       |

|         | · ·         |               |                               |               |             |        |       | ]     |

|         | Legend:     |               |                               |               |             |        |       |       |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

Note: To achieve a 1:1 prescaler assignment for TMR0, assign the prescaler to the WDT by setting PSA bit to '1' (OPTION<3>). See Section 4.4 "Prescaler".

#### 3.2.3.3 RA2/AN2/T0CKI/INT/COUT

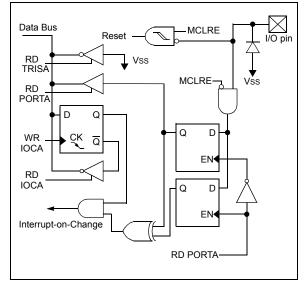

Figure 3-2 shows the diagram for this pin. The RA2 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the A/D (PIC16F676 only)

- · a digital output from the comparator

- the clock input for TMR0

- · an external edge triggered interrupt

#### **BLOCK DIAGRAM OF RA2** FIGURE 3-2: Analog Data Bus Input Mode Q D Vdd WR СК Q Weak WPUA RAPU RD WPUA Analog COUT Input Mode Enable Vdd D Q +WR СК Q COUT PORTA 1 $\times$ I/O pin Ż Q D WR **∀** Vss СК Q TRIS. Analog Input Mode RD Ч TRISA RD PORTA Q П D Q WR CK Q IOCA EN RD IOCA D Q EN Interrupt-on-Change **RD PORTA** To TMR0 To INT To A/D Converter

#### 3.2.3.4 RA3/MCLR/VPP

Figure 3-3 shows the diagram for this pin. The RA3 pin is configurable to function as one of the following:

- a general purpose input

- · as Master Clear Reset

#### FIGURE 3-3: BLOCK DIAGRAM OF RA3

| STER 5-1: | T1CON — TIMER1 CONTROL REGISTER (ADDRESS: 10h) |                                |              |                |                |           |              |         |  |

|-----------|------------------------------------------------|--------------------------------|--------------|----------------|----------------|-----------|--------------|---------|--|

|           | U-0                                            | R/W-0                          | R/W-0        | R/W-0          | R/W-0          | R/W-0     | R/W-0        | R/W-0   |  |

|           | —                                              | TMR1GE                         | T1CKPS1      | T1CKPS0        | T1OSCEN        | T1SYNC    | TMR1CS       | TMR10N  |  |

|           | bit 7                                          |                                |              |                |                |           |              | bit 0   |  |

| bit 7     | Unimplem                                       | ented: Read                    | as '0'       |                |                |           |              |         |  |

| bit 6     | -                                              | Timer1 Gate                    |              |                |                |           |              |         |  |

|           | If TMR10                                       |                                |              |                |                |           |              |         |  |

|           | This bit is i<br>If TMR10N                     |                                |              |                |                |           |              |         |  |

|           |                                                | is on if T1G                   | pin is low   |                |                |           |              |         |  |

|           | 0 = Timer1                                     |                                |              |                |                |           |              |         |  |

| bit 5-4   |                                                | :T1CKPS0: T                    | •            | t Clock Pres   | scale Select I | oits      |              |         |  |

|           | -                                              | rescale Value<br>rescale Value |              |                |                |           |              |         |  |

|           |                                                | rescale Value                  |              |                |                |           |              |         |  |

|           | 00 = 1:1 P                                     | rescale Value                  | 9            |                |                |           |              |         |  |

| bit 3     |                                                | : LP Oscillato                 |              |                |                |           |              |         |  |

|           |                                                | without CLK                    |              |                | <u>).</u>      |           |              |         |  |

|           |                                                | illator is off                 |              |                |                |           |              |         |  |

|           | <u>Else:</u><br>This hit is i                  | aparad                         |              |                |                |           |              |         |  |

| bit 2     | This bit is i                                  | ignored<br>Timer1 Exteri       | aal Clock I  | nnut Synchr    | onization Co   | atrol bit |              |         |  |

| DIL Z     | TMR1CS =                                       |                                |              | iiput Synchii  |                |           |              |         |  |

|           | 1 = Do not                                     | synchronize                    |              |                |                |           |              |         |  |

|           | 0 = Synchi<br><u>TMR1CS =</u>                  | ronize externa<br>             | al clock inp | but            |                |           |              |         |  |

|           |                                                | <u>gnored</u> . Time           | er1 uses th  | e internal clo | ock.           |           |              |         |  |

| bit 1     | TMR1CS:                                        | Timer1 Clock                   | Source S     | elect bit      |                |           |              |         |  |

|           |                                                | al clock from                  |              | 1CKI pin (on   | the rising ed  | lge)      |              |         |  |

| h# 0      |                                                | al clock (Fosc                 | -            |                |                |           |              |         |  |

| bit 0     | 1 = Enable                                     | Timer1 On b<br>s Timer1        | IL           |                |                |           |              |         |  |

|           | 0 = Stops                                      | Timer1                         |              |                |                |           |              |         |  |

|           | Legend:                                        |                                |              |                |                |           |              |         |  |

|           | R = Reada                                      | able bit                       | VV = V       | Vritable bit   | U = Unim       | plemented | bit, read as | '0'     |  |

|           | - n = Value                                    | e at POR                       | '1' = E      | Bit is set     | '0' = Bit is   | s cleared | x = Bit is u | Inknown |  |

### REGISTER 5-1: T1CON — TIMER1 CONTROL REGISTER (ADDRESS: 10h)

#### 5.4 Timer1 Operation in Asynchronous Counter Mode

If control bit  $\overline{T1SYNC}$  (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 5.4.1).

Note: The ANSEL (91h) and CMCON (19h) registers must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0'. The ANSEL register is defined for the PIC16F676.

## 5.4.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L, while the timer is running from an external asynchronous clock, will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Examples 12-2 and 12-3 in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023) show how to read and write Timer1 when it is running in Asynchronous mode.

### 5.5 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins OSC1 (input) and OSC2 (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator rated up to 32 kHz. It will continue to run during Sleep. It is primarily intended for a 32 kHz crystal. Table 9-2 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is shared with the system LP oscillator. Thus, Timer1 can use this mode only when the system clock is derived from the internal oscillator. As with the system LP oscillator, the user must provide a software time delay to ensure proper oscillator start-up.

TRISA5 and TRISA4 bits are set when the Timer1 oscillator is enabled. RA5 and RA4 read as '0' and TRISA5 and TRISA4 bits read as '1'.

Note: The oscillator requires a start-up and stabilization time before use. Thus, T1OSCEN should be set and a suitable delay observed prior to enabling Timer1.

### 5.6 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To setup the timer to wake the device:

- Timer1 must be on (T1CON<0>)

- TMR1IE bit (PIE1<0>) must be set

- PEIE bit (INTCON<6>) must be set

The device will wake-up on an overflow. If the GIE bit (INTCON<7>) is set, the device will wake-up and jump to the Interrupt Service Routine on an overflow.

| Address | Name   | Bit 7   | Bit 6                                                                       | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Value<br>POR, |      |      | e on<br>other<br>sets |

|---------|--------|---------|-----------------------------------------------------------------------------|---------|---------|---------|--------|--------|--------|---------------|------|------|-----------------------|

| 0Bh/8Bh | INTCON | GIE     | PEIE                                                                        | T0IE    | INTE    | RAIE    | T0IF   | INTF   | RAIF   | 0000          | 0000 | 0000 | 000u                  |

| 0Ch     | PIR1   | EEIF    | ADIF                                                                        |         | _       | CMIF    | —      | -      | TMR1IF | 00            | 00   | 00   | 00                    |

| 0Eh     | TMR1L  | Holding | lolding Register for the Least Significant Byte of the 16-bit TMR1 Register |         |         |         |        |        |        |               | XXXX | uuuu | uuuu                  |

| 0Fh     | TMR1H  | Holding | lolding Register for the Most Significant Byte of the 16-bit TMR1 Register  |         |         |         |        |        |        | uuuu          | uuuu |      |                       |

| 10h     | T1CON  | _       | TMR1GE                                                                      | T1CKPS1 | T1CKPS0 | T10SCEN | T1SYNC | TMR1CS | TMR10N | -000          | 0000 | -uuu | uuuu                  |

| 8Ch     | PIE1   | EEIE    | ADIE                                                                        | _       | _       | CMIE    | _      | _      | TMR1IE | 00            | 00   | 00   | 00                    |

TABLE 5-1:

REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

NOTES:

#### 6.0 **COMPARATOR MODULE**

The PIC16F630/676 devices have one analog comparator. The inputs to the comparator are multiplexed with the RA0 and RA1 pins. There is an on-chip Comparator Voltage Reference that can also be applied to an input of the comparator. In addition, RA2 can be configured as the comparator output. The Comparator Control Register (CMCON), shown in Register 6-1, contains the bits to control the comparator.

#### **REGISTER 6-1:** CMCON — COMPARATOR CONTROL REGISTER (ADDRESS: 19h)

|         | U-0                          | R-0         | U-0                     | R/W-0        | R/W-0     | R/W-0       | R/W-0       | R/W-0     |

|---------|------------------------------|-------------|-------------------------|--------------|-----------|-------------|-------------|-----------|

|         | —                            | COUT        | _                       | CINV         | CIS       | CM2         | CM1         | CM0       |

|         | bit 7                        |             |                         |              |           |             |             | bit 0     |

|         |                              |             |                         |              |           |             |             |           |

| bit 7   | Unimplem                     | ented: Rea  | <b>d as</b> '0'         |              |           |             |             |           |

| bit 6   | COUT: Con                    | nparator Ou | Itput bit               |              |           |             |             |           |

|         | When CIN\                    |             |                         |              |           |             |             |           |

|         | 1 = VIN+ > '<br>0 = VIN+ < ' |             |                         |              |           |             |             |           |

|         | U = VIN+ <<br>When CIN\      |             |                         |              |           |             |             |           |

|         | 1 = VIN+ < 1                 |             |                         |              |           |             |             |           |

|         | 0 = VIN+ >                   | Vin-        |                         |              |           |             |             |           |

| bit 5   | Unimplem                     | ented: Rea  | <b>d as</b> '0'         |              |           |             |             |           |

| bit 4   |                              |             | put Inversio            | n bit        |           |             |             |           |

|         | 1 = Output                   |             | ı                       |              |           |             |             |           |

| 1:10    | 0 = Output                   |             |                         |              |           |             |             |           |

| bit 3   | CIS: Compa<br>When CM2       |             |                         |              |           |             |             |           |

|         | 1 = VIN- COI                 |             |                         |              |           |             |             |           |

|         | 0 = VIN- COI                 | nnects to C | IN-                     |              |           |             |             |           |

| bit 2-0 | CM2:CM0:                     |             |                         |              |           |             |             |           |

|         | Figure 6-2                   | shows the C | Comparator              | modes and (  | CM2:CM0 b | it settings |             |           |

|         |                              |             |                         |              |           |             |             |           |

|         | Legend:                      |             |                         |              |           |             |             |           |

|         |                              | hla hit     | $\lambda A = \lambda A$ | /ritable bit |           | anlamantad  | hit road on | <u>o'</u> |

| Legenu.          |                     |                      |                    |

|------------------|---------------------|----------------------|--------------------|

| R = Readable bi  | t W = Writable bit  | U = Unimplemente     | d bit, read as '0' |

| - n = Value at P | OR '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

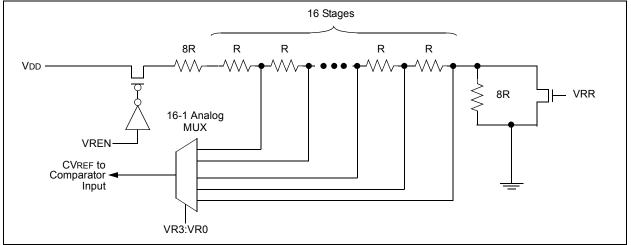

#### 6.5 Comparator Reference

The comparator module also allows the selection of an internally generated voltage reference for one of the comparator inputs. The internal reference signal is used for four of the eight Comparator modes. The VRCON register, Register 6-2, controls the voltage reference module shown in Figure 6-5.

## 6.5.1 CONFIGURING THE VOLTAGE REFERENCE

The voltage reference can output 32 distinct voltage levels, 16 in a high range and 16 in a low range.

The following equations determine the output voltages:

| $VRR = 1$ (low range): $CVREF = (VR3:VR0 / 24) \times VDD$ |  |

|------------------------------------------------------------|--|

| VRR = 0 (high range): $CVREF = (VDD / 4) + (VR3:VR0 x)$    |  |

| VDD / 32)                                                  |  |

#### 6.5.2 VOLTAGE REFERENCE ACCURACY/ERROR

The full range of VSS to VDD cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 6-5) keep CVREF from approaching VSS or VDD. The Voltage Reference is VDD derived and therefore, the CVREF output changes with fluctuations in VDD. The tested absolute accuracy of the Comparator Voltage Reference can be found in **Section 12.0 "Electrical Specifications"**.

### 6.6 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output is ensured to have a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs. Otherwise, the maximum delay of the comparators should be used (Table 12-7).

### 6.7 Operation During Sleep

Both the comparator and voltage reference, if enabled before entering Sleep mode, remain active during Sleep. This results in higher Sleep currents than shown in the power-down specifications. The additional current consumed by the comparator and the voltage reference is shown separately in the specifications. To minimize power consumption while in Sleep mode, turn off the comparator, CM2:CM0 = 111, and voltage reference, VRCON<7> = 0. While the comparator is enabled during Sleep, an interrupt will wake-up the device. If the device wakes up from Sleep, the contents of the CMCON and VRCON registers are not affected.

### 6.8 Effects of a Reset

A device Reset forces the CMCON and VRCON registers to their Reset states. This forces the comparator module to be in the Comparator Reset mode, CM2:CM0 = 000 and the voltage reference to its off state. Thus, all potential inputs are analog inputs with the comparator and voltage reference disabled to consume the smallest current possible.

| REGISTER 7-3: | ANSEL — ANALOG SELECT REGISTER (ADRESS: 91h) (PIC16F676 ONLY) |

|---------------|---------------------------------------------------------------|

|---------------|---------------------------------------------------------------|

|   | R/W-1 |

|---|-------|-------|-------|-------|-------|-------|-------|-------|

|   | ANS7  | ANS6  | ANS5  | ANS4  | ANS3  | ANS2  | ANS1  | ANS0  |

| b | it 7  |       |       |       |       |       |       | bit 0 |

bit 7-0: **ANS<7:0>**: Analog Select between analog or digital function on pins AN<7:0>, respectively. 1 = Analog input. Pin is assigned as analog input.<sup>(1)</sup>

0 = Digital I/O. Pin is assigned to port or special function.

**Note 1:** Setting a pin to an analog input automatically disables the digital input circuitry, weak pull-ups, and interrupt-on-change if available. The corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

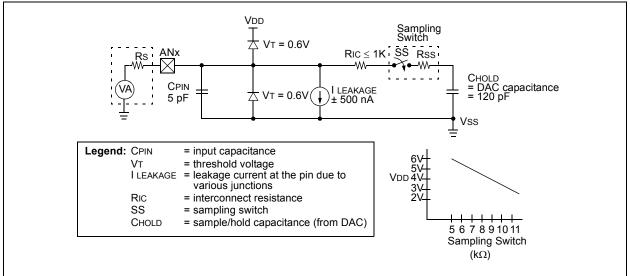

### 7.2 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 7-3. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 7-3. The maximum recommended impedance for analog sources is 10 k\Omega. As the impedance

#### EQUATION 7-1: ACQUISITION TIME

is decreased, the acquisition time may be decreased. After the analog input channel is selected (changed), this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 7-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

To calculate the minimum acquisition time, TACQ, see the PIC<sup>®</sup> Mid-Range Reference Manual (DS33023).

| TACQ | = Amplifier Settling Time +<br>Hold Capacitor Charging Time +<br>Temperature Coefficient                                                                                                      |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Тс   | = TAMP + TC + TCOFF<br>= $2\mu s$ + TC + [(Temperature -25°C)(0.05 $\mu s$ /°C)]<br>= CHOLD (RIC + RSS + RS) In(1/2047)<br>= -120pF (1k $\Omega$ + 7k $\Omega$ + 10k $\Omega$ ) In(0.0004885) |

| TACQ | = 16.47μs<br>= 2μs + 16.47μs + [(50°C -25°C)(0.05μs/°C)<br>= 19.72μs                                                                                                                          |

Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- **2:** The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is 10 kΩ. This is required to meet the pin leakage specification.

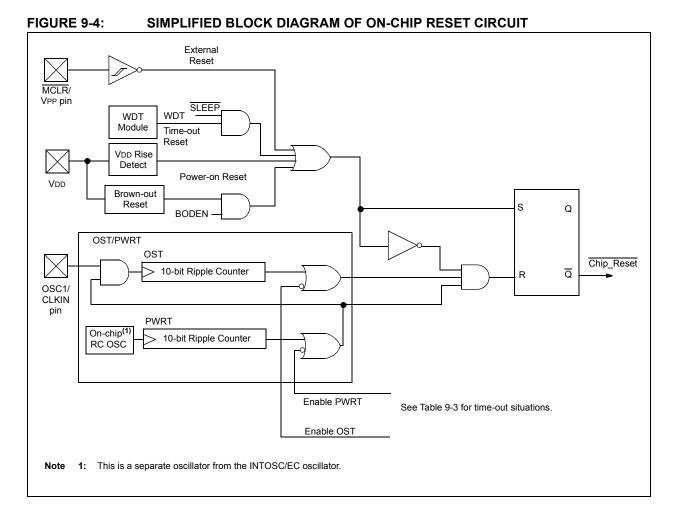

#### 9.3 Reset

The PIC16F630/676 differentiates between various kinds of Reset:

- a) Power-on Reset (POR)

- b) WDT Reset during normal operation

- c) WDT Reset during Sleep

- d) MCLR Reset during normal operation

- e) MCLR Reset during Sleep

- f) Brown-out Detect (BOD)

Some registers are not affected in any Reset condition; their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on:

- · Power-on Reset

- MCLR Reset

- WDT Reset

- WDT Reset during Sleep

- Brown-out Detect (BOD)

They are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation.  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are set or cleared differently in different Reset situations as indicated in Table 9-4. These bits are used in software to determine the nature of the Reset. See Table 9-7 for a full description of Reset states of all registers.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 9-4.

The  $\overline{\text{MCLR}}$  Reset path has a noise filter to detect and ignore small pulses. See Table 12-4 in Electrical Specifications Section for pulse-width specification.

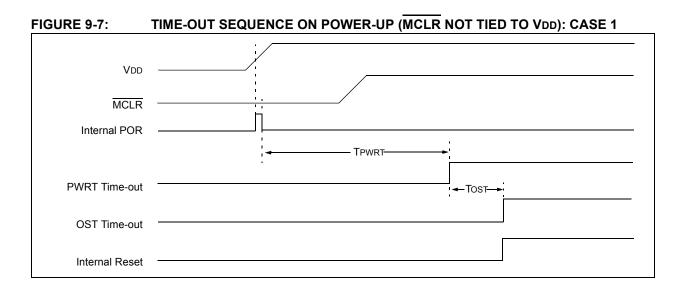

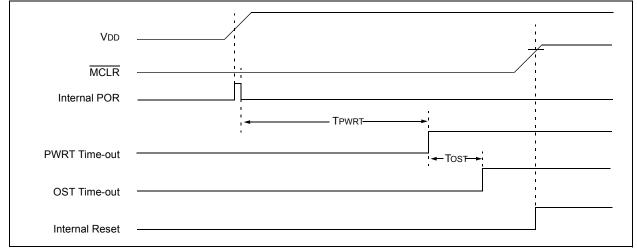

### FIGURE 9-8: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

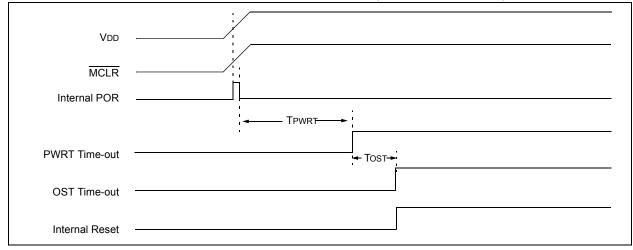

### FIGURE 9-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

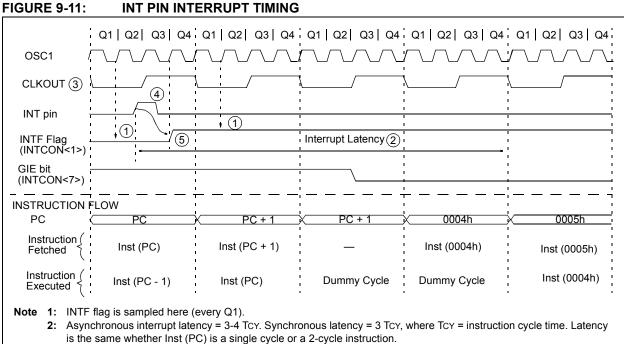

#### 9.4.1 **RA2/INT INTERRUPT**

External interrupt on RA2/INT pin is edge-triggered; either rising if INTEDG bit (OPTION<6>) is set, or falling, if INTEDG bit is clear. When a valid edge appears on the RA2/INT pin, the INTF bit (INTCON<1>) is set. This interrupt can be disabled by clearing the INTE control bit (INTCON<4>). The INTF bit must be cleared in software in the Interrupt Service Routine before re-enabling this interrupt. The RA2/INT interrupt can wake-up the processor from Sleep if the INTE bit was set prior to going into Sleep. The status of the GIE bit decides whether or not the processor branches to the interrupt vector following wake-up. See Section 9.7 "Power-Down Mode (Sleep)" for details on Sleep and Figure 9-13 for timing of wake-up from Sleep through RA2/INT interrupt.

Note: The ANSEL (91h) and CMCON (19h) registers must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0'. The ANSEL register is defined for the PIC16F676.

#### 9.4.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set the T0IF (INTCON<2>) bit. The interrupt can be enabled/disabled by setting/clearing T0IE (INTCON<5>) bit. For operation of the Timer0 module, see Section 4.0 "Timer0 Module".

#### 9.4.3 PORTA INTERRUPT

An input change on PORTA change sets the RAIF (INTCON<0>) bit. The interrupt can be enabled/ disabled by setting/clearing the RAIE (INTCON<3>) bit. Plus individual pins can be configured through the IOCA register.

| Note: | If a change on the I/O pin should occur       |

|-------|-----------------------------------------------|

|       | when the read operation is being executed     |

|       | (start of the Q2 cycle), then the RAIF inter- |

|       | rupt flag may not get set.                    |

#### 9.4.4 COMPARATOR INTERRUPT

See Section 6.9 "Comparator Interrupts" for description of comparator interrupt.

#### 9.4.5 A/D CONVERTER INTERRUPT

After a conversion is complete, the ADIF flag (PIR<6>) is set. The interrupt can be enabled/disabled by setting or clearing ADIE (PIE<6>).

See Section 7.0 "Analog-to-Digital Converter (A/D) Module (PIC16F676 only)" for operation of the A/D converter interrupt.

3: CLKOUT is available only in RC Oscillator mode.

- 4: For minimum width of INT pulse, refer to AC specs.

- 5: INTF is enabled to be set any time during the Q4-Q1 cycles.

Note 1: T0SE, T0CS, PSA, PS0-PS2 are bits in the OPTION register.

#### TABLE 9-9: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address | Name         | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOD | Value on all<br>other<br>Resets |

|---------|--------------|-------|--------|-------|-------|-------|-------|-------|-------|----------------------|---------------------------------|

| 81h     | OPTION_REG   | RAPU  | INTEDG | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111            | 1111 1111                       |

| 2007h   | Config. bits | CP    | BODEN  | MCLRE | PWRTE | WDTE  | F0SC2 | F0SC1 | F0SC0 | uuuu uuuu            | uuuu uuuu                       |

Legend: u = Unchanged, shaded cells are not used by the Watchdog Timer.

#### 10.2 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |

| Operation:       | $(W) + k \to (W)$                                                                                                          |

| Status Affected: | C, DC, Z                                                                                                                   |

| Description:     | The contents of the W register<br>are added to the eight-bit literal 'k'<br>and the result is placed in the W<br>register. |

| ADDWF            | Add W and f                                                                                                                                                                    |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                     |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                          |

| Status Affected: | C, DC, Z                                                                                                                                                                       |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0, the<br>result is stored in the W register. If<br>'d' is 1, the result is stored back in<br>register 'f'. |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BCF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| ANDLW            | AND Literal with W                                                                                                     |

|------------------|------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                               |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                        |

| Status Affected: | Z                                                                                                                      |

| Description:     | The contents of W register are<br>AND'ed with the eight-bit literal<br>'k'. The result is placed in the W<br>register. |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BTFSS f,b                                                                                                                                                                                        |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b < 7 \end{array}$                                                                                                                                                  |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                              |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next instruc-<br>tion is discarded and a NOP is<br>executed instead, making this a<br>2-cycle instruction. |

| ANDWF            | AND W with f                                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                           |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                   |

| Status Affected: | Z                                                                                                                                                           |

| Description:     | AND the W register with register<br>'f'. If 'd' is 0, the result is stored in<br>the W register. If 'd' is 1, the result<br>is stored back in register 'f'. |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [/abe/] BTFSC f,b                                                                                                                                                                                                 |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                               |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                              |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.<br>If bit 'b', in register 'f', is '0', the next instruction is discarded, and a NOP is executed instead, making this a 2-cycle instruction. |

| MOVF             | Move f                                                                                                                                                                                                                                                                            |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                         |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                       |

| Operation:       | (f) $\rightarrow$ (destination)                                                                                                                                                                                                                                                   |

| Status Affected: | Z                                                                                                                                                                                                                                                                                 |

| Description:     | The contents of register f are<br>moved to a destination dependant<br>upon the status of d. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register f itself.<br>d = 1 is useful to test a file register,<br>since status flag Z is affected. |

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| MOVLW            | Move Literal to W                                                                                |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                         |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                              |  |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                              |  |  |  |  |  |

| Status Affected: | None                                                                                             |  |  |  |  |  |

| Description:     | The eight-bit literal 'k' is loaded<br>into W register. The don't cares<br>will assemble as 0's. |  |  |  |  |  |

| RETFIE           | Return from Interrupt                        |  |  |  |  |

|------------------|----------------------------------------------|--|--|--|--|

| Syntax:          | [label] RETFIE                               |  |  |  |  |

| Operands:        | None                                         |  |  |  |  |

| Operation:       | TOS $\rightarrow$ PC,<br>1 $\rightarrow$ GIE |  |  |  |  |

| Status Affected: | None                                         |  |  |  |  |

| MOVWF            | Move W to f                                |  |  |  |  |  |

|------------------|--------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVWF f                   |  |  |  |  |  |

| Operands:        | $0 \leq f \leq 127$                        |  |  |  |  |  |

| Operation:       | $(W) \rightarrow (f)$                      |  |  |  |  |  |

| Status Affected: | None                                       |  |  |  |  |  |

| Description:     | Move data from W register to register 'f'. |  |  |  |  |  |

| RETLW            | Return with Literal in W                                                                                                                                                            |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                                 |  |  |  |  |  |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow PC$                                                                                                                                        |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                |  |  |  |  |  |

| Description:     | The W register is loaded with the<br>eight-bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a two-cycle instruction. |  |  |  |  |  |

## TABLE 12-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER,<br/>AND BROWN-OUT DETECT REQUIREMENTS

| Param<br>No. | Sym   | Characteristic                                                 | Min        | Тур†      | Max         | Units    | Conditions                                       |

|--------------|-------|----------------------------------------------------------------|------------|-----------|-------------|----------|--------------------------------------------------|

| 30           | TMCL  | MCLR Pulse Width (low)                                         | 2<br>11    | <br>18    | <br>24      | μs<br>ms | VDD = 5V, -40°C to +85°C<br>Extended temperature |

| 31           | Twdt  | Watchdog Timer Time-out<br>Period<br>(No Prescaler)            | 10<br>10   | 17<br>17  | 25<br>30    | ms<br>ms | VDD = 5V, -40°C to +85°C<br>Extended temperature |

| 32           | Тоѕт  | Oscillation Start-up Timer<br>Period                           | _          | 1024Tosc  | _           |          | Tosc = OSC1 period                               |

| 33*          | TPWRT | Power-up Timer Period                                          | 28*<br>TBD | 72<br>TBD | 132*<br>TBD | ms<br>ms | VDD = 5V, -40°C to +85°C<br>Extended Temperature |

| 34           | Tioz  | I/O High-impedance from<br>MCLR Low or Watchdog Timer<br>Reset | —          | _         | 2.0         | μS       |                                                  |

|              | BVDD  | Brown-out Detect Voltage                                       | 2.025      |           | 2.175       | V        |                                                  |

|              |       | Brown-out Hysteresis                                           | TBD        | —         |             | —        |                                                  |

| 35           | TBOD  | Brown-out Detect Pulse Width                                   | 100*       |           | —           | μS       | $VDD \le BVDD$ (D005)                            |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

| Param<br>No. | Sym       |                       | Characteristic                                  |                              | Min                                       | Тур† | Max     | Units | Conditions                         |

|--------------|-----------|-----------------------|-------------------------------------------------|------------------------------|-------------------------------------------|------|---------|-------|------------------------------------|

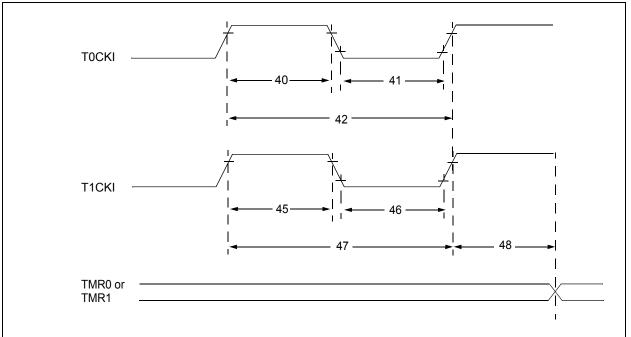

| 40*          | Tt0H      | T0CKI High Pulse      | Width                                           | No Prescaler                 | 0.5 Tcy + 20                              | -    | _       | ns    |                                    |

|              |           |                       |                                                 | With Prescaler               | 10                                        | —    |         | ns    |                                    |

| 41*          | TtOL      | T0CKI Low Pulse       | Width                                           | No Prescaler                 | 0.5 TCY + 20                              | —    | _       | ns    |                                    |

|              |           |                       |                                                 | With Prescaler               | 10                                        | —    | —       | ns    |                                    |

| 42*          | TtOP      | T0CKI Period          |                                                 |                              | Greater of:<br>20 or <u>Tcy + 40</u><br>N | _    | -       | ns    | N = prescale value<br>(2, 4,, 256) |

| 45*          | Tt1H      | T1CKI High Time       | Synchronous, No                                 | s, No Prescaler 0.5 Tcy + 20 |                                           | —    | _       | ns    |                                    |

|              |           |                       | Synchronous,<br>with Prescaler                  |                              | 15                                        | -    |         | ns    |                                    |

|              |           |                       | Asynchronous                                    |                              | 30                                        | —    |         | ns    |                                    |

| 46*          | Tt1L      | L T1CKI Low Time      | Synchronous, No                                 | Prescaler                    | 0.5 Tcy + 20                              | —    | _       | ns    |                                    |

|              |           |                       | Synchronous, with Prescaler                     |                              | 15                                        | -    |         | ns    |                                    |

|              |           |                       | Asynchronous                                    |                              | 30                                        | —    | _       | ns    |                                    |

| 47*          | Tt1P      | T1CKI Input<br>Period | Synchronous                                     |                              | Greater of:<br>30 or <u>Tcy + 40</u><br>N | —    | _       | ns    | N = prescale value<br>(1, 2, 4, 8) |

|              |           |                       | Asynchronous                                    |                              | 60                                        | —    | —       | ns    |                                    |

|              | Ft1       |                       | nput frequency range<br>by setting bit T1OSCEN) |                              | DC                                        | —    | 200*    | kHz   |                                    |

| 48           | TCKEZtmr1 | Delay from externa    | ternal clock edge to timer increment            |                              | 2 Tosc*                                   | —    | 7 Tosc* | _     |                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

NOTES:

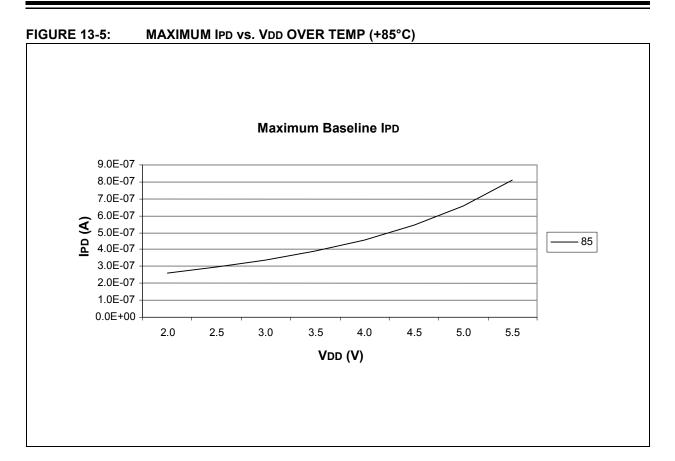

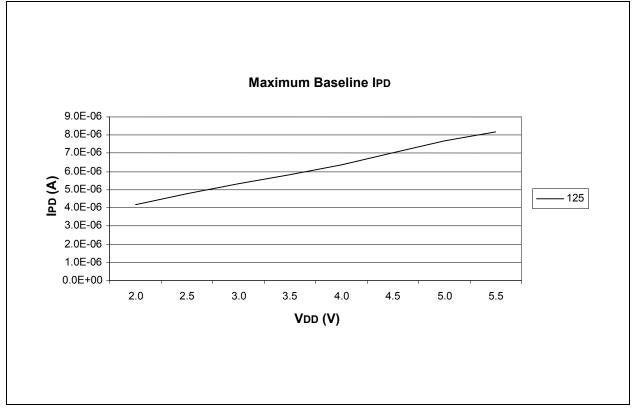

FIGURE 13-6: MAXIMUM IPD vs. VDD OVER TEMP (+125°C)

| RESET, Watchdog Timer, Oscillator Start-up Timer and Power-up Timer |

|---------------------------------------------------------------------|

| Time-out Sequence on Power-up (MCLR not Tied to                     |

| VDD)/                                                               |

| Case 1 64                                                           |

| Case 2                                                              |

| Time-out Sequence on Power-up (MCLR Tied                            |

| to VDD)64                                                           |

| Timer0 and Timer1 External Clock 101                                |

| Timer1 Incrementing Edge35                                          |

| Timing Parameter Symbology95                                        |

| TRISIO Registers                                                    |

| V                                                                   |

| Voltage Reference Accuracy/Error43                                  |

| W                                                                   |

| Watchdog Timer                                                      |

| Summary of Registers                                                |

| Watchdog Timer (WDT) 68                                             |

| WWW Address                                                         |

| WWW, On-Line Support5                                               |